Устройство для перевода выражений в польскую инверсную запись

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

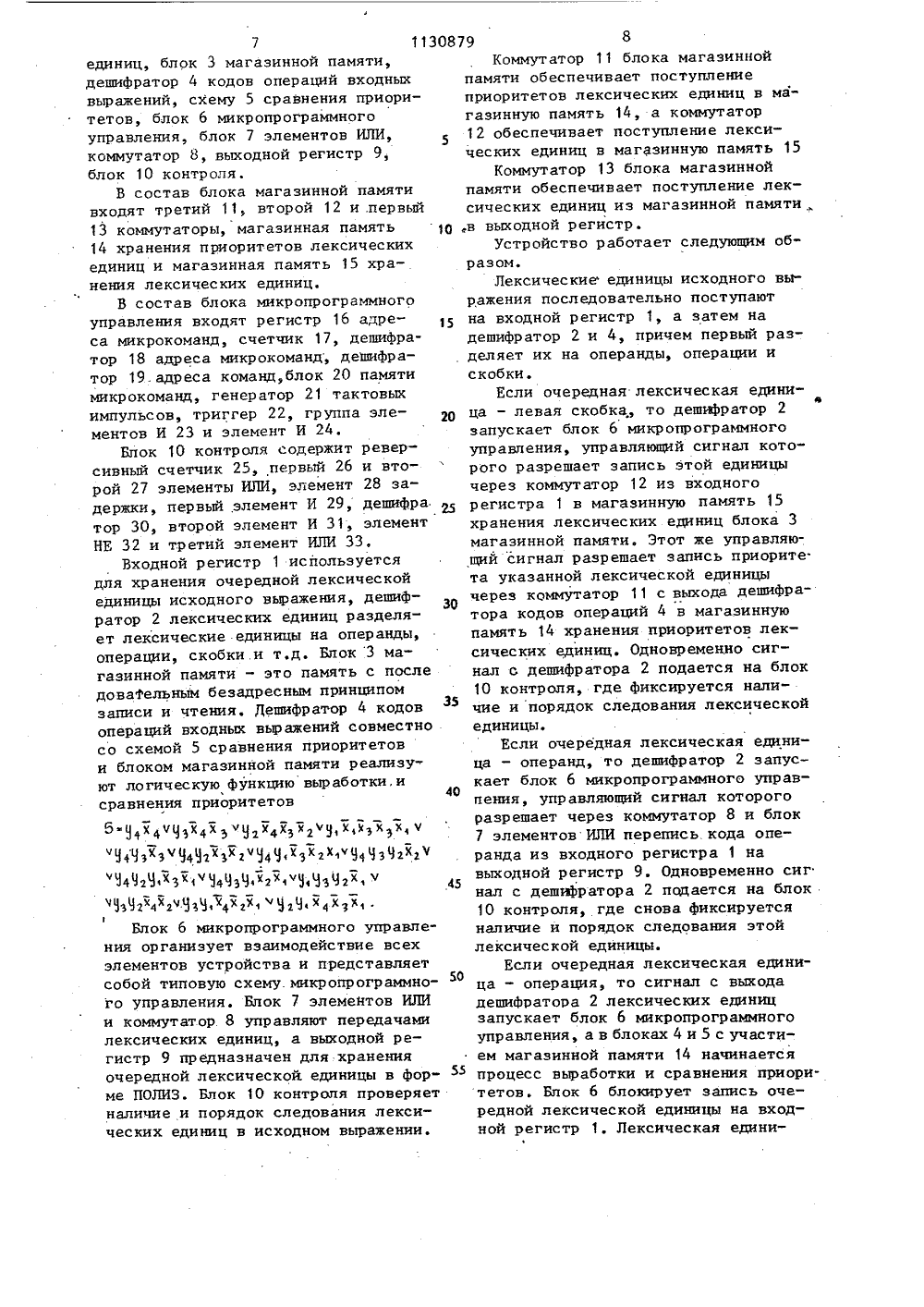

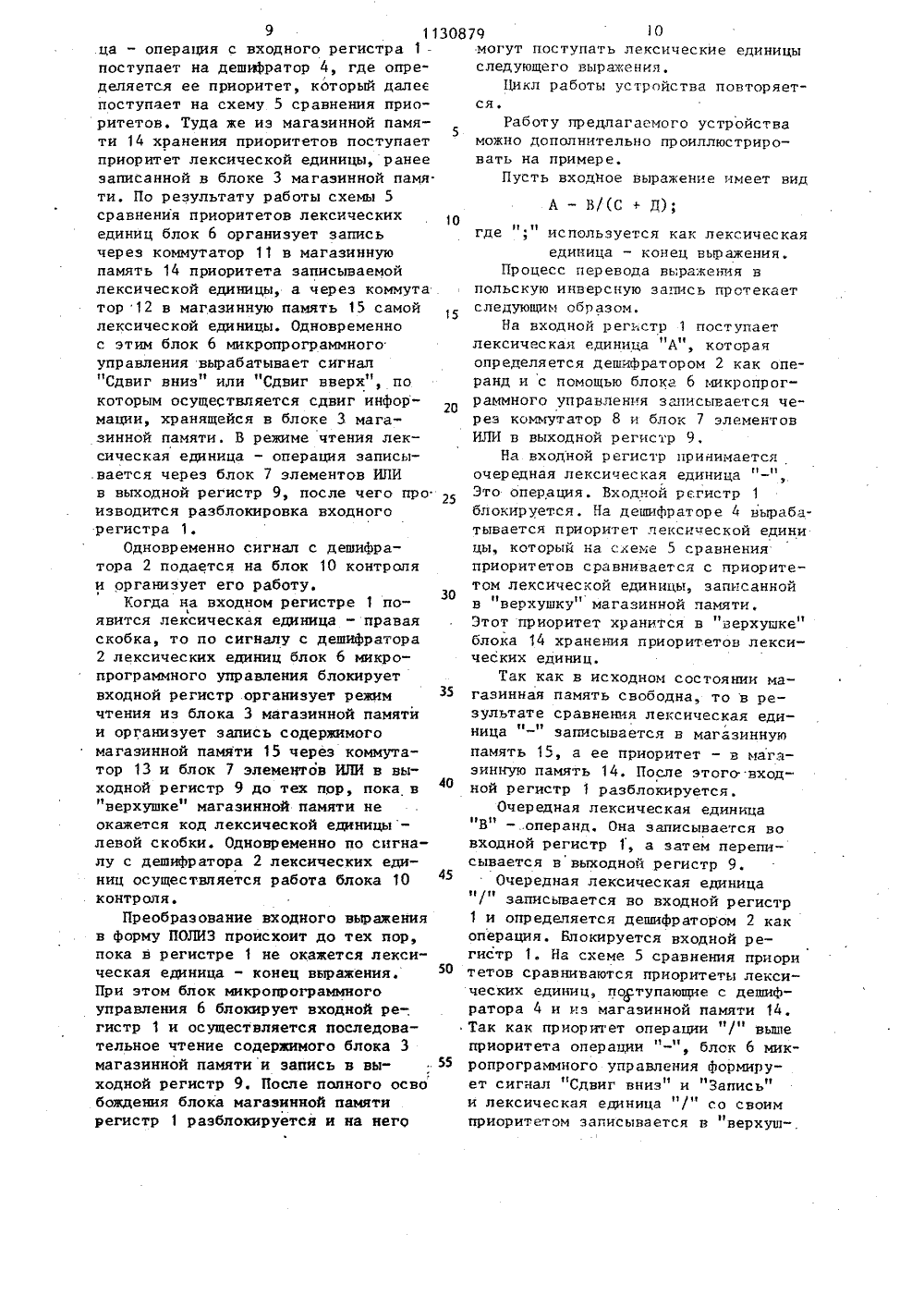

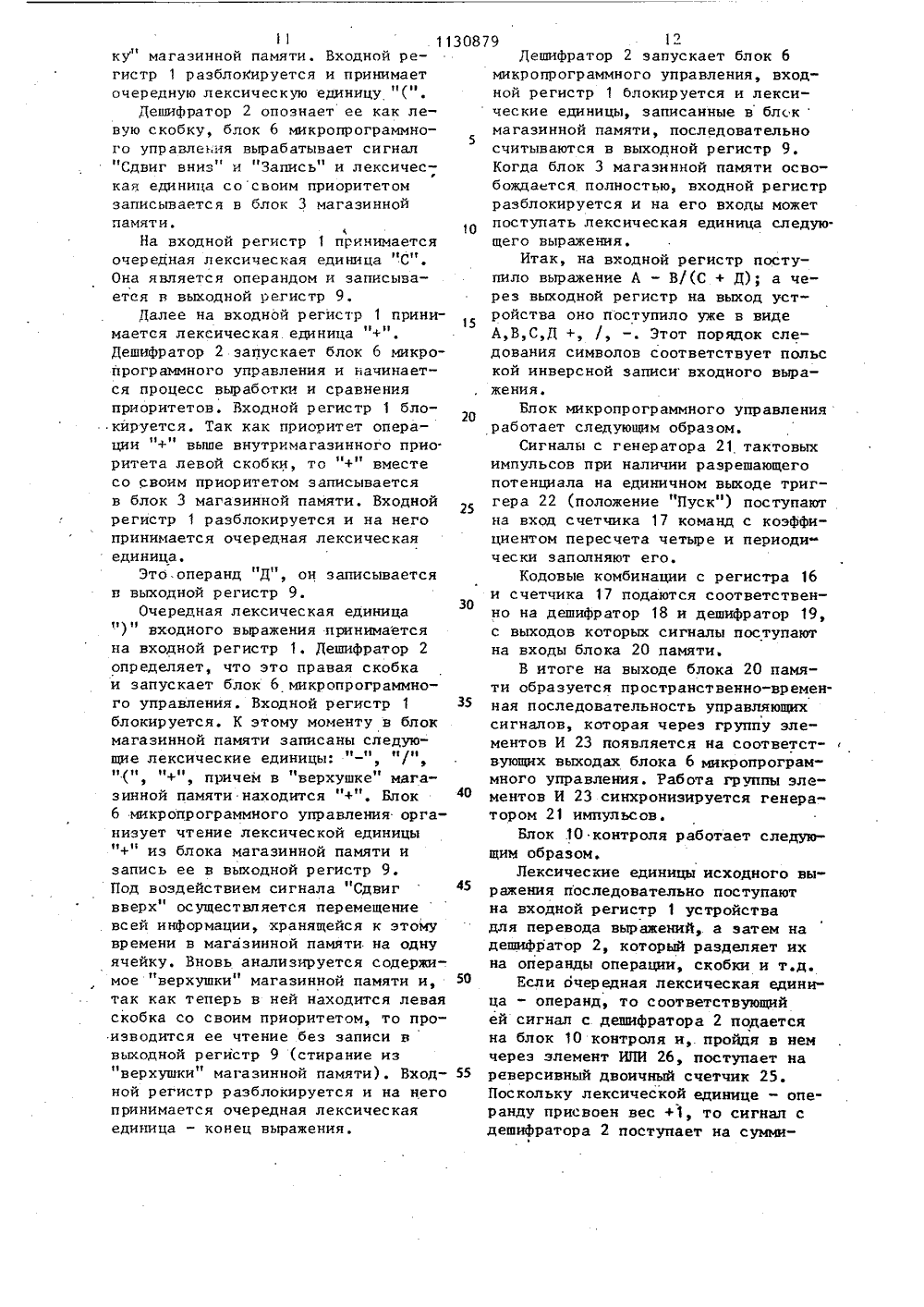

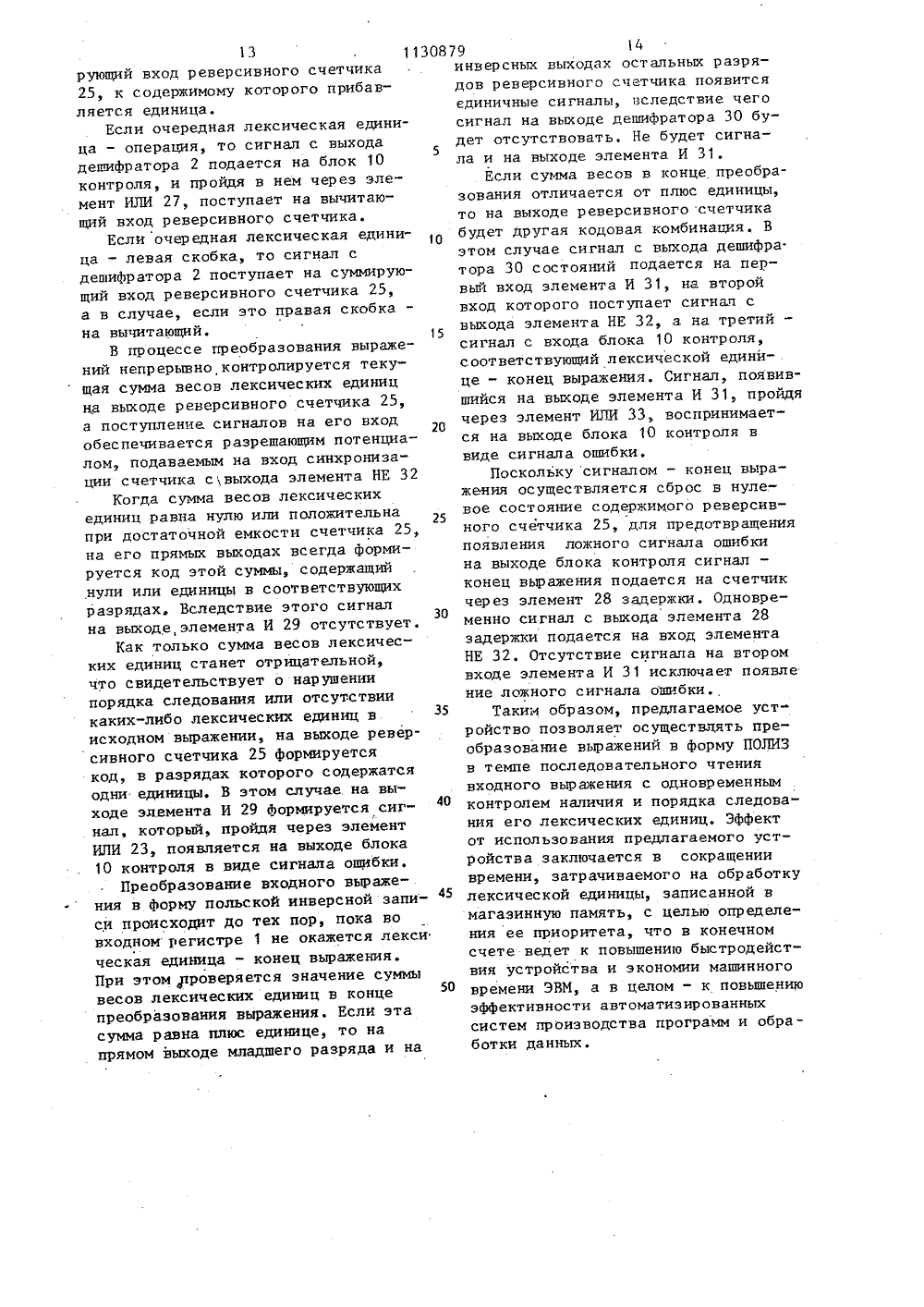

(56) 1. АвторВ 890403, кл.2. Авторскпо заявке У 3тип). Бюл, Р 47ов, А.А.Булгаков,А.Калмыков и В.В,К е ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 088,8)кое свидетельство ССС С 06 Р 15/38.е свидетельство СССР 17931/18-24 (прото(54)(57) 1. УСТРОЙСТВО ДЛЯ ПЕРЕВОДА ВЫРА 1 НЕНИЙ В ПОЛЬСКУЮ ИНВЕРСНУЮ ЗАПИСЬ, содержащее входной регистр, дешифратор лексических единиц дешифратор кодов операций входных выражений, схему сравнения приоритетов, коммутатор, блок элементов ИЛИ, выходной регистр, блок магазинной памяти, блок контроля и блок микропрограммного управления, состоящий из регистра адреса микрокоманд, дешифратора адреса микрокоманд, блока памяти микрокоманд, счетчика, дешифратора адреса команд, элемента И, генератора тактовых импульсов, триггера и группы элементов И, первые входы элементов И группы соединены с выходом элемента И и со счетным входом счетчика группа информацион)ных выходов которого соединена с группой входов дешифратора адреса команд, группа выходов которого соединена с группой адресных входов старших разрядов блока памяти микро- команд, группа адресных входов младших разрядов которого соединена с группой выходов дешифратора адреса микрокоманд, группа входов которого соединена с группой выходов регистраадреса микрокоманд, первый и второйвходы элемента И соединены соответственно с выходом генератора тактовыхимпульсов и с выходом триггера, входустановки в "0" которого соединен свыходом первого элемента И группы,вторые входы элементов И группы соединены с информационными выходамиблока памяти микрокоманд, выходывторого, третьего, четвертого и пятого элементов И группы соединенысоответственно с входом записи входного регистра, с управляющим входомкоммутатора, с входом записи блокамагазинной памяти и с входом чтенияблока магазинной памяти, перваягруппа информационных входов регист"ра адреса микрокоманд соединена сгруппой выходов дешифратора лексических единиц и с группой входов.блока контроля, вторая группа информационных входов регистра микрокоманд соединена с группой выходов схемы сравнения приоритетов, вход установки в "1" триггера соединен с входом пуска устройства, первая группавходов схемы сравнения приоритетовсоединена с группой выходов дешифратора кодов операций входных выражений, первая группа входов блокамагазинной памяти соединена с группа.ми входов дешифратора лексическихединиц, дешифратора кодов операцийвходных выражений и коммутатора, атакже с группой выходов входного регистра, первая группа выходов блокамагазинной памяти соединена с первой группой входов блока элементовИЛИ, вторая группа входов и группавыходов которого соединена соотв т 1130879г1 гр лла Юханз еаиРРагц 3 да у ю 8 олеауии 2 грулла РхаоИЮ ЬдЮЮ 20регистра )1130879 итель Ю.Пан Т.Фанта ост бручар Редактор С.Патрушева оррек о Зак ал ППП "Патент", г. Ужгород, ул. Проектная, 4 9 б 12/36 Тираж 698ВНИИПИ Государственногопо делам изобретений и 113035, Москва, Ж, Раушская Подомитета СССРоткрытийнаб., д. 4/5879 1130 ственно с группой выходов коммутато-, ра и с группой информационных входов выходного регистра, группа выходов которого соединена с группой выходов устройства, группа информационных входов входного регистра и выход блока контроля соединены соответст- . венно с группой входов и выходом ошибки устройства, о т л и ч а ю - щ е е с я тем, что, с целью повыше.ния быстродействия, вторая группа входов схемы сравнения приоритетов и третья группа информационных входов регистра микрокоманд соединены с второй группой выходов блока магазинной памяти, вторая группа входов которого соединена с группой выходов дешифратора кода.операций входных выражений, вход сдвига "вниз" и вход сдвига "вверх" блока магазинной памяти соединены соответственно с выхо дом шестого элемента И группы и с выходом седьмого элемента И группы. 2, Устройство по и. 1, о т л и - ч а ю щ е е с я тем, что блок магазинной памяти содержит первый, второй и третий коммутаторы, магазинную память хранения приоритетов лексических единиц и магазинную память хранения лексических единиц, группа выходов которой соединена с группойвходов первого коммутатора, группавыходов которого соединена с первойгруппой выходов блока, управляющийвход первого коммутатора соединен свходом чтения блока, управляющиевходы второго и третьего коммутатора соединены с входом записи блока,входы сдвига "вниз" и "вверх" блокасоединены соответственно с входамисдвига "вниз" и "вверх" магазиннойпамяти хранения приоритетов лекси 1ческих единиц и магазинной памяти хранения лексических единиц, группа входов которой соединена с группойвыходов второго коммутатора, группа входов которого соединена с первойгруппой входов блока, а вторая группа входов блока соединена .с .группой входов третьего коммутатора, группавыходов которого соединена с группойвходов магазинной памяти хранения приоритетов лексических единиц, группа выходов которой соединена с второй группой выходов блока.Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки данных и производства про. грамм для ЭВМ.Известно устройство для перевода выражений в польскую инверсную запись, Оно может быть использовано в автоматизированных системах производства программ для ускорения процесса трансляции 11.Недостатком его является отсутствие контроля наличия и порядка следования лексических единиц в исходном выражении.Наиболее близким к изобретению техническим решением является устройство для перевода выражений в польскую. инверсную запись, содержащее входной регистр, дешифратор лексических единиц, дешифратор кодов операций входных выражений, регистр ,кодов операций и дешифратор кодов 5 1 О 15 20 операций магазинной памяти,.схему сравнения приоритетов, магазинную память, блок управления, блок контроля, выходной регистр, четыре группы элементов И,и группу элементов ИЛИ, причем группа входов входного регистра является входом устройства, а,группа входов дешифратора лекси" ческих единиц, дешифратора кодов. операций выражений и элементов И первой и второй групп объединены и подключены к соответствующим выходам входного регистра, группа выходов дешифратора лексических единиц подключена к первой группе входов блока управления и группе входов блока.Оконтроля, выход которого является выходом сигнала ошибки; группа выходов дешифратора кодов операций выражений соединена с группой входов схемы сравнения приоритетов 1 выходы элементов И первой группы подключе-ны соответственно к первым входамгруппы элементов ИЛИ, вторые входыкоторых подключены к выходам соответствующих элементов И третьейгруппы, а выходы - к группе входоввыходного регистра, группа выходовкоторого является выходом устройства; выхоцы элементов И второй группыподключены к группе входов магазинной памяти, первая группа выходовкоторой годключена к первым входамсоответствукнцих элементов И третьейгруппы, вторая группа выходов магазинной памяти подключена к первымвходам соответствующих элементовИ четвертой группы, выходы которойподключены к группе соответствующихвходов регистра кодов операций магазинной памяти, группа выходов которого подключена к группе соответствующих входов дешифратора кодов операций магазинной памяти, а группаего выходов - к второй группе входов схемы сравнений приоритетов ик второй группе входов блока управления, выход схемы сравнения приоритетов соединен с третьей группойвходов блока управлениями первый,второй, третий, четвертый, пятый,шестой и седьмой выходы блока управления подключены соответственно квходам "Чтение" и "Запись" магазинной памяти, к вторым входам элементов И четвертой, второй, третьейи первой групп соответственно куправляющему входу входного регистра. Блок управления .содержит регистркоманд,счетчик команд, дешифратор,команд, дешифратор микрокоманд,микропрограммную память, генераторимпульсов, триггер, группу элементовИ, элемент И, причем входы регистраявляются соответственно первой, второй и, третьей группой входов блокауправления, вход счетчика командсоединен с выходом элемента И, первый вход которого соединен с выходом генератора импульсов, а второй - с единичным выходом триггера,нулевой вход которого соединен свыходом первого элемента И группыа единичный является входом "Пуск"блока управления, выходы регистра исчетчика команд соединены соответственнос входами дешифратора микрокоманд и дешифратора команд, выходыкоторых соединены соответственно садресными входами первой и второйгрупп микропрограммной памяти, ин 50 55 ражений в польскую инверсную запись, содержащее входной регистр, дешифратор лексических единиц, дешифратор кодов операций входных выражений,схему сравнения приоритетов, коммутатор, блок элементов ИЛИ, выходнойрегистр, блок магазинной памяти,блок контроля и блок микропрограммного управления, состоящий из регистРа адреса микрокоманд, дешифратора адреса микрокоманд, блока памяти микрокоманд, счетчика, дешифратора формационные выходы которой соедине"ны с первыми входами соответствующнхэлементов И группы, вторые входыкоторых объединены и подключены к 5 выходу элемента И а выходы являютсявыходами блока управления с первогопо седьмой. Блок контроля содержитреверсивный счетчик, первый, второйи третий элементы ИЛИ, первый и вто-рой элементы .И, элемент НЕ, дешифра-,тор состояния, элемент задержки,причем первый и второй входы первогои второго элементов ИЛИ, первыйвход первого элемента И и вход эле мента задержки соединены с соответствующими выходами дешифратора лексических единиц, выходы первого и второго элементов ИЛИ подключены соответственно к входам сложения и вычита ния реверсивного счетчика, установочный вход которого подключен к выходу элемента задержки и к входуэлемента НЕ, а выход последнего подключен к входу синхронизации реверсивного счетчика и ко второму входупервого элемента И, третий вход кото.рого подключен к выходу дешифраторасостояний, выходы первого и второгоэлементов И подключены соответствен но к первому и второму входам третьего элемента ИЛИ, выход которого является выходом "Ошибка" устройства,входы второго элемента И подключенык соответствующим выходам реверсивного счетчика, входы дешифратора состояний подключены к соответствующиминверсным выходам реверсивного счетчика 2 .Недостатком устройства является 40 сложность и избыточность его схемы,что в конечном счете снижает быстродействие устройства.Цель изобретения - повышениебыстродействия устройства.45 Поставленная цель достигается тем,что в устройство для перевода вы15 3 11308 адреса команд, элемента И, генератора тактовых импульсов, триггера и группы элементов И, первые входы элементов И группы соединены с выходом элемента И и со счетным входом счетчика, группа информационных выходов которого соединена с группой входов дешифратора адреса команд, группа выходов которого соединена с группой адресных входов старших разрядов блока памяти микрокоманд, группа адресных входов младших разрядов которого соединена с группой выходов дешифратора адреса микро- команд, группа входов которого соединена с группой выходов регистра адреса микрокоманд, первый и второй входы элемента И соединены соответственно с выходом генератора тактовых импульсов и с выходом триггера, вход установки в "О" которого соединен с выходом первого элемента И группы, вторые входы элементов И группы соединены с информационными выходами блока памяти микрокоманд, выходы второго, третьего, четвертого и пятого элементов И группы соединены соответственно с входом записи входного регистра, с управляющим входом коммутатор.а, с входом записиЗО блока магазинной памяти и с входом чтения блока магазинной памяти, первая группа информационных входов регистра адреса микрокоманд соединена с группой выходов дешифратора лексических единиц и с группой входов блока контроля, вторая группа информационных входов регистра микрокоманд соединена с группой выходов схемы сравнения приоритетов, вход установки в "1" триггера. соединен с входом пуска устройства, первая группа входов схемы сравненияприоритетов соединена с группой выходов дешифратора кодов операций входных выражений, первая группа45 входов блока магазинной памяти соеди нека с группами входов дешифратора.лексических единиц, дешифраторакодов операций входных выражений и коммутатора, а также с группой выходов входного регистра, первая группа выходов блока магазинной памяти соединена с первой группой входов блока элементов ИЛИ, вторая группа входов и группа выходов которого соединена соответственно с группой выходов коммутатора и с группой информационных входов выходного регистра, групФ 79 бпа выходов которого соединена с группой выходов устройства, группа информационных входов входного регистра и выход блока контроля соединены соответственно с группой входов и выходом ошибки устройства, введены вторая группа входов схемы сравнения приоритетов и третья группа информационных входов регистра микрокоманд соединены с второй группой выхо. дов блока магазинной памяти, первая группа входов которого соединена с группой выходов дешифратора кода операций входных выражений, вход сдвига "вниз" и вход сдвига "вверх" блока магазинной памяти соединены соответственно с выходом шестого элемента И группы и с выходом седьмого элемента И группы.. Кроме того, блок магазинной памяти содержит первый, второй и третий коммутаторы, магазинную память хранения приоритетов лексических единиц и магазинную память хранения лексических единиц, группа выходов которой соединена с группой входов первого коммутатора, группа выходов которого соединена с второй группой выходов блока, управляющий вход первого коммутатора соединен с входом чтения блока, управляющие входы второго и третьего коммутатора соединены с входом записи блока, входы сдвига "вниз" и "вверх" блока соединены соответственно с входами сдвига "вниз" и "вверх" магазинной памяти хранения приоритетов лексических единиц и магазинной памяти хранения лексических единиц, группа входов которой соединена с группой выходов второго коммутатора, группа входов которого соединена с первой группой входов блока, а вторая группа входов блока соединена с группой входов третьего коммутатора, группа выходов которого соединена с группой входов магазинной памяти хранения приоритетов лексических единиц, груп. па выходов которой соединена с первой группой выходов блока.На фиг. 1 представлена структурная схема устройтва, на фиг. 2 - структурная схема блока магазинной памяти; на фиг. 3 - структурная схема блока микропрограммного управления; на фиг. 4 - структурная схема блока контроля,Устройство содержит входной регистр 1, дешифратор 2 лексических0879 10,в выходной регистр20 ЗО 35 40 45 0 55 7 113единиц, блок 3 магазинной памяти,дешифратор 4 кодов операций входныхвыражений, схему 5 сравнения приоритетов, блок 6 микропрограммногоуправления, блок 7 элементов ИЛИ,коммутатор 8, выходной регистр 9,блок 10 контроля.В состав блока магазинной памятивходят третий 11, второй 12 и .первый13 коммутаторы, магазинная память14 хранения приоритетов лексическихединиц и магазинная память 15 хранения лексических единиц.В состав блока микропрограммногоуправления входят регистр 16 адреса микрокоманд, счетчик 17, дешифратор 18 адреса микрокоманд, дешифратор 19.адреса команд, блок 20 памятимикрокоманд, генератор 21 тактовыхимпульсов, триггер 22, группа элементов И 23 и элемент И 24,Блок 10 контроля содержит реверсивный счетчик 25, первый 26 и второй 27 элементы ИЛИ, элемент 28 задержки, первый элемент И 29, дешифра.тор 30, второй элемент И 31, элементНЕ 32 и третий элемент ИЛИ 33,Входной регистр 1 используетсядля хранения очередной лексическойединицы исходного выражения, дешифратор 2 лексических единиц разделяет лексические единицы на операнды,операции, скобки.и т.д. Блок 3 магазинной памяти - это память с последова 1 ельным безадресным принципомзаписи и чтения, Дешифратор 4 кодовопераций входных выражений совместносо схемой 5 сравнения приоритетови блоком магазинной памяти реализуют логическую функцию выработки.исравнения приоритетовЦ 4 4 ЦЭХ 4 Х 5 ЦХ 4 Х ХЧЦ ХХКЗХ ЧУ+Чзэч Ч 4 Чхзх л "14 каккчц 4 Ч Цх,чЧ 4 Ч 29 КЗ" " Ч 4 ЧЗЧХ 2 "ЧЧЗЧ 2"ЦЦх 4 ХЧЯЧХ 4 ХХ Ц 1 Ч "4 ХХБлок 6 микропрограммного управления организует взаимодействие всехэлементов устройства и представляетсобой типовую схему. микропрограммного управления. Блок 7 элементов ИЛИи коммутатор. 8 управляют передачамилексических единиц, а выходной регистр 9 предназначен для храненияочередной лексической единицы в форме ПОЛИЗ. Блок 10 контроля проверяетналичие и порядок следования лексических единиц в исходном выражении. 8Коммутатор 11 блока магазинной памяти обеспечивает поступление приоритетов лексических единиц в магазинную память 14, а коммутатор 12 обеспечивает поступление лексических единиц в магазинную память 15Коммутатор 13 блока магазинной памяти обеспечивает поступление лексических единиц из магазинной памяти Устройство работает следующим образом. Лексические единицы исходного выражения последовательно поступают на входной регистр 1, а затем надешифратор 2 и 4, причем первый разделяет их на операнды, операции искобки,Если очередная лексическая единица - левая скобка то дешифратор 2 запускает блок 6 микропрограммного управпения, управляющий сигнал которого разрешает запись этой единицычерез коммутатор 12 из входногорегистра 1 в магазинную память 15хранения лексических единиц блока 3магазинной памяти. Этот же управляющий сигнал разрешает запись приорите. та указанной лексической единицы через коммутатор 11 с выхода дешифратора кодов операций 4 в магазинную память 14 хранения приоритетов лексических единиц. Одновременно сигнал с дешифратора 2 подается на блок 10 контроля, где Фиксируется наличие и порядок следования лексической единицы.Если очередная лексическая единица - операнд, то дешифратор 2 запускает блок 6 микропрограммного управ- пения, управляющий сигнал которого разрешает через коммутатор 8 и блок 7 элементов ИЛИ перепись кода операнда из входного регистра 1 на выходной регистр 9. Одновременно сиг нал с деширатора 2 подается на блок 10 контроля, где снова фиксируется наличие и порядок следования этой лексической единицы.Если очередная лексическая единица - операция, то сигнал с выхода дешифратора 2 лексических единиц запускает блок 6 микропрограммного управления, а в блоках 4 и 5 с участием магазинной памяти 14 начинается процесс выработки и сравнения приоритетов. Блок 6 блокирует запись очередной лексической единицы на входной регистр 1. Лексическая единиА - В/(С + Д); 9 1 ца - операция с входного регистра 1- поступает на дешифратор 4, где определяется ее приоритет, который далее поступает на схему 5 сравнения приоритетов. Туда же иэ магазинной памяти 14 хранения приоритетов поступает приоритет лексической единицы, ранее записанной в блоке 3 магазинной памя ти. По результату работы схемы 5 сравнения приоритетов лексических единиц блок 6 организует запись через коммутатор 11 в магазинную память 14 приоритета записываемой лексической единицы, а через коммута тор 12 в магазинную память 15 самой лексической единицы. Одновременно с этим блок 6 микропрограммного управления вырабатывает сигнал "Сдвиг вниз" или "Сдвиг вверх", по которым осуществляется сдвиг информации, хранящейся в блоке 3 магазинной памяти. В режиме чтения лексическая единица - операция записы.вается через блок 7 элементов ИЛИ в выходной регистр 9, после чего про изводится разблокировка входного регистра 1.Одновременно сигнал с дешифратора 2 подается на блок 10 контроля и организует его работу.Когда на входном регистре 1 появится лексическая единица - правая скобка, то по сигналу с дешифратора 2 лексических единиц блок 6 микропрограммного управления блокирует входной регистр организует режим чтения из блока 3 магазинной памяти и организует зались содержимого магазинной памяти 15 через коммутатор 13 и блок 7 элементов ИЛИ в выходной регистр 9 до тех пор, пока в "верхушке" магазинной памяти не окажется код лексической единицы - левой скобки. Одновременно по сигналу с дешифратора 2 лексических единиц осуществляется работа блока 1 О контроля.Преобразование входного выражения в форму ПОЛИЗ происхоит до тех пор, пока в регистре 1 не окажется лекси" ческая единица - конец виражения. При этом блок микропрограммного управления 6 блокирует входной ре-, гистр 1 и осуществляется последовательное чтение содержимого блока 3 магазинной памяти и запись в выходной регистр 9. После полного осво бождения блока магазинной памяти регистр 1 разблокируется и на него 130879 омогут поступать лексические единицыследующего выражения,Цикл работы устройства повторяется.5Работу предлагаемого устройстваможно дополнительно проиллюстрировать на примере.Пусть входное выражение имеет вид 1 О,где ; используется ка к л ексич ес каяединица - конец выражения .Процесс перевода выраже ни я впольскую инверсную запись протекаетследующим образом .Н а вход ной р егь стр 1 поступаетлексическая единица "А" , кот ор а яопределяется д ешиф ра т ор ом 2 как операнд и с помощью блока 6 микр опр ог 20 р аммного управления записывается чер еэ коммутатор 8 и блок 7 элементовИЛИ в выходной р егис тр 9 ,На входной регистр принимаетсяочередная лексическая единицаЭто операция . Вх одной р е гис тр 1блокируется. На дешифраторе 4 вырабатывается приоритет лексической единицы, который на салеме 5 сравненияприоритетов сравнивается с приоритетом лексической единицы, записаннойв "верхушку" магазинной памяти,Этот приоритет хранится в "верхушке"блока 14 хранеяя приоритетов лексических единиц.Так как в исходном состоянии ма 35 газинная память свободна, то в результате сравнения лексическая единица - записывается в маг аэиннуюпамять 1 5 , а ее приоритет - в маг аэинную память 1 4 . После этого вход 40ной р е гистр 1 разблокируется .Очередная лексическая единицаВ - операнд . Она записывается вовходной регистр 1, а затем переписывается ввыходной регистр 9 .45Очередная лексическая единица// записывается во входной регистр1 и определяется дешифратором 2 какоперация, Бпокируется входной регистр 1. На схеме 5 сравнения приори50 тетов сравниваются приоритеты лексических единиц, поступающие с дешифратора 4 и из магазинной памяти 14.Так как приоритет операции "/" вышеприоритета операции "-", блок 6 мик 55 ропрограммного управления формиру"ет сигнал Сдвиг вниз" и Записьи лексическая единица "/" со своимприоритетом записывается в верхуш-,1130879 10 11ку магазинной памяти. Входной регистр 1 разблокируется и принимает очередную лексическую единицу "("Дешифратор 2 опознает ее как левую скобку, блок 6 микропрограммного управления вырабатывает сигнал "Сдвиг вниз" и "Запись" и лексичесР кая единица со своим приоритетом записывается в блок 3 магазинной памяти.сНа входной регистр 1 принимаетсяочередная лексическая единица С.Она является операндом и записывается в выходной регистр 9.Далее на входной регистр 1 принимается лексическая. единица "+",Дешифратор 2 запускает блок 6 микропрограммного управления и начинается процесс выработки и сравненияприоритетов. Входной регистр 1 блокируется. Так как приоритет операции "+" выше внутримагазинного прис.ритета левой скобки, то "+" вместесо своим приоритетом записываетсяв блок 3 магазинной памяти. Входнойрегистр 1 разблокируется и на негопринимается очередная лексическаяединица.,Это,операнд "Д", он записываетсяв выходной регистр 9.Очередная лексическая единица")" входного выражения принимаетсяна входной регистр 1. Дешифратор 2определяет, что это правая скобкаи запускает блок б микропрограммного управления. Входной регистр 1блокируется. К этому моменту в блокмагазинной памяти записаны следующие лексические единицы: "-", "/","(", "+", причем в "верхушке" магазинной памяти находится "+", Блок6 микропрограммного управления организует чтение лексической единицы"+" из блока магазинной памяти изапись ее в выходной регистр 9.Под воздействием сигнала "Сдвигвверх" осуществляется перемещение. всей информации, хранящейся к этомувремени в магазинной памяти на однуячейку. Вновь анализируется содержи-.мое "верхушки" магазинной памяти и,так как теперь в ней находится леваяскобка со своим приоритетом, то производится ее чтение без записи ввыходной регистр 9 (стирание из"верхушки магазинной памяти). Входной регистр разблокируется и на негопринимается очередная лексическаяединица - конец выражения. 15 20 25 30 35 40 45 50 55ЭДешифратор 2 запускает блок 6 микропрограммного управления, входной регистр 1 блокируется и лекси ческие единицы, записанные в блокмагазинной памяти, последовательно считываются в выходной регистр 9. Когда блок 3 магазинной памяти освобождается полностью, входной регистр разблокируется и на его входы может поступать лексическая единица следующего выражения.Итак, на входной регистр поступило выражение А - В/(С + Д); а через выходной регистр на выход устройства оно поступило уже в виде А,В,С,Д +, /, в . Этот порядок следования символов соответствует польс кой инверсной записи входного выражения.Блок микропрограммного управления работает следующим образом.Сигналы с генератора 21 тактовых импульсов при наличии разрешающего потенциала на единичном выходе триггера 22 (положение "Пуск" ) поступают на вход счетчика 17 команд с коэффициентом пересчета четыре и периодически заполняют его.Кодовые комбинации с регистра 16 и счетчика 17 подаются соответственно на дешифратор 18 и дешифратор 19, с выходов которых сигналы поступают на входы блока 20 памяти.В итоге на выходе блока 20 памяти образуется пространственно-временная последовательность управляющих сигналов, которая через группу элементов И 23 появляется на соответст" вующих выходах блока 6 микропрограммного управления. Работа группы элементов И 23 синхрониэируется генератором 21 импульсов.Блок .10 контроля работает следующим образом.Лексические единицы исходного выражения последовательно поступают на входной регистр 1 устройства для перевода выражений, а затем на дешифратор 2, который разделяет их на операнды операции, скобки и т.д.Если очередная лексическая единица - операнд, то соответствующийей сигнал с дешифратора 2 подаетсяна блок 10 контроля и,.пройдя в нем через элемент ИПИ 26, поступает на реверсивный двоичный счетчик 25. Поскольку лексической единице - операнду присвоен вес +1, то сигнал с дешифратора 2 поступает на сумми 13 , 11 рующий вход реверсивного счетчика 25, к содержимому которого прибавляется единица.Если очередная лексическая единица - операция, то сигнал с выхода дешифратора 2 подается на блок 10 контроля, и пройдя в нем через элемент ИЛИ 27, поступает на вычитающий вход реверсивного счетчика.Если очередная лексическая единица - левая скобка, то сигнал с дешифратора 2 поступает на суммирующий вход реверсивного счетчика 25, а в случае, если это правая скобка - на вычитающий.В процессе преобразования выражений непрерывно контролируется текущая сумма весов лексических единиц на выходе реверсивного счетчика 25, а поступление сигналов на его вход обеспечивается разрешающим потенциалом, подаваемым на вход синхронизации счетчика свыхода элемента НЕ 32Когда сумма весов лексических единиц равна нулю или положительна при достаточной емкости счетчика 25, на его прямых выходах всегда формируется код этой суммы, содержащий нули или единицы в соответствующих разрядах, Вследствие этого сигнал на выходе, элемента И 29 отсутствует.Как только сумма весов лексических единиц станет отрицательной, что свидетельствует о нарушении порядка следования или отсутствии каких-либо лексических единиц в исходном выражении, на выходе реверсивного счетчика 25 формируется код, в разрядах которого содержатся одни единицы. В этом случае на выходе элемента И 29 формируется сигнал, который, пройдя через элемент ИЛИ 23, появляется на выходе блока 10 контроля в виде сигнала ошибки.Преобразование входного выражения в форму польской инверсной записи происходит до тех пор, пока во входном регистре 1 не окажется лекси ческая единица - конец выражения. При этом проверяется значение суммы весов лексических единиц в конце преобразования выражения. Если эта сумма равна плюс единице, то на прямом выходе младшего разряда и на30879 1 Й 5 10 15 20 25 30 35 40 45 50 инверсных выходах остальных разрядов реверсивного счетчика появитсяединичные сигналы, вследствие чегосигнал на выходе дешифратора 30 будет отсутствовать, Не будет сигнала и на выходе элемента И 31,Если сумма весов в конце преобразования отличается от плюс единицы,то на выходе реверсивного счетчикабудет другая кодовая комбинация, Вэтом случае сигнал с выхода дешифратора 30 состояний подается на первьп вход элемента И 31, на второйвход которого поступает сигнал свыхода элемента НЕ 32, а на третий -сигнал с входа блока 10 контроля,соответствующий лексической единице - конец выражения. Сигнал, появившийся на выходе элемента И 31, пройдячерез элемент ИЛИ 33, воспринимается на выходе блока 10 контроля ввиде сигнала ошибки,Поскольку сигналом - конец выражения осуществляется сброс в нулевое состояние содержимого реверсивного счетчика 25, для предотвращенияпоявления ложного сигнала ошибкина выходе блока контроля сигнал -конец выражения подается на счетчикчерез элемент 28 задержки. Одновременно сигнал с выхода элемента 28задержки подается на вход элементаНЕ 32, Отсутствие сигнала на второмвходе элемента И 31 исключает появление ложного сигнала ошибки.Таким образом, предлагаемое устройство позволяет осуществлять преобразование выражений в форму ПОЛИЗв темпе последовательного чтениявходного выражения с одновременнымконтролем наличия и порядка следования его лексических единиц. Эффектот использования предлагаемого устройства заключается в сокращениивремени, затрачиваемого на обработкулексической единицы, записанной вмагазинную память, с целью определения ее приоритета, что в конечномсчете ведет к повышению быстродействия устройства и экономии машинноговремени ЭВМ, а в целом - к повьппениюэффективности автоматизированныхсистем производства программ и обработки данных,

СмотретьЗаявка

3471240, 15.07.1982

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

БРЯКАЛОВ ГЕННАДИЙ АЛЕКСЕЕВИЧ, БУЛГАКОВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, ЗАХАРОВ АНАТОЛИЙ ИВАНОВИЧ, КАЛМЫКОВ НИКОЛАЙ АНДРЕЕВИЧ, КОВАЛЕВ ВИКТОР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 17/27

Метки: выражений, запись, инверсную, перевода, польскую

Опубликовано: 23.12.1984

Код ссылки

<a href="https://patents.su/12-1130879-ustrojjstvo-dlya-perevoda-vyrazhenijj-v-polskuyu-inversnuyu-zapis.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для перевода выражений в польскую инверсную запись</a>

Предыдущий патент: Устройство для определения энтропийных характеристик случайных сигналов

Следующий патент: Устройство для контроля электрического монтажа

Случайный патент: Способ мелиорации песчаных и супесчаных почв и грунтов