Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1100624

Авторы: Литвиненко, Тимонькин, Ткаченко, Харченко

Текст

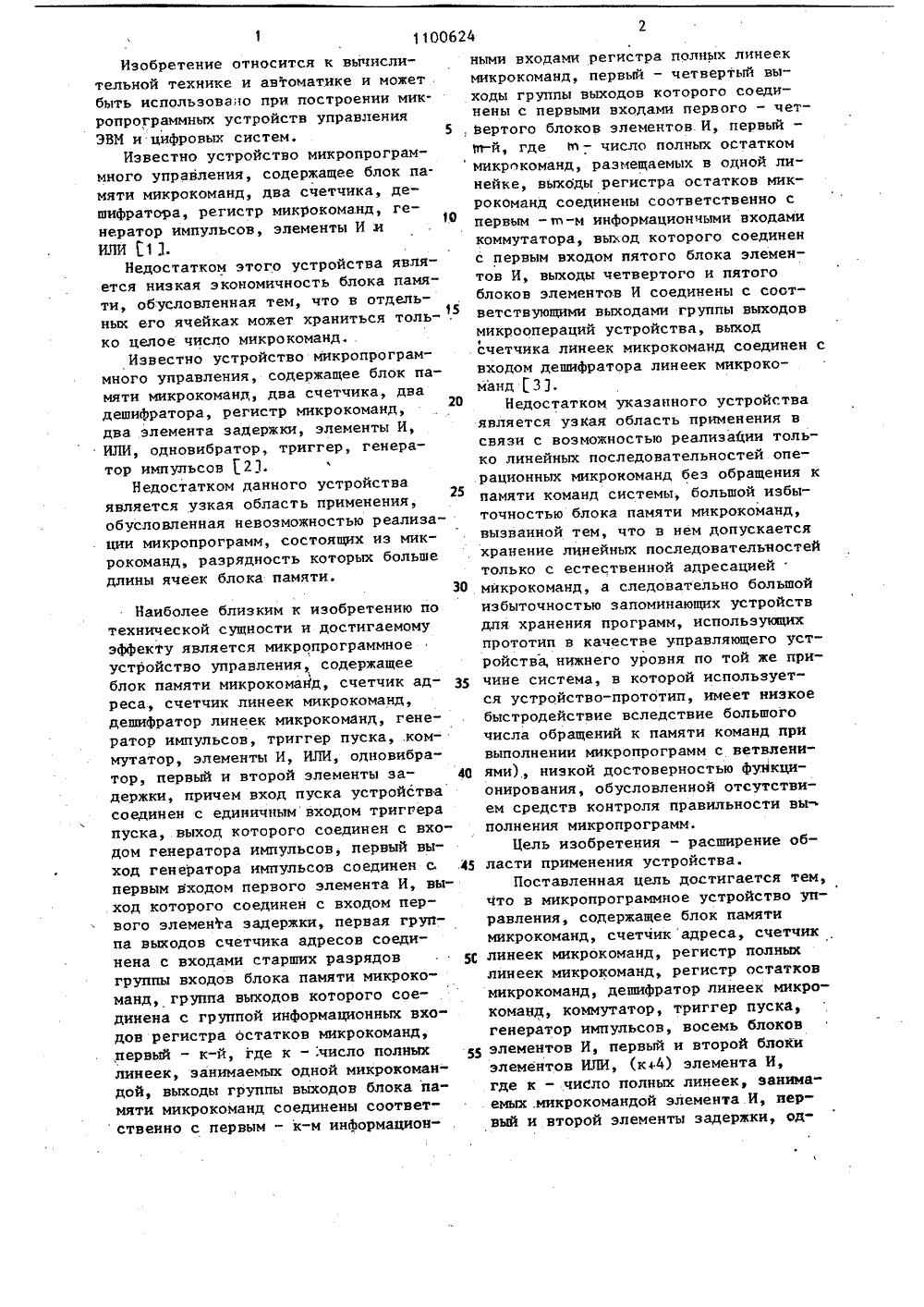

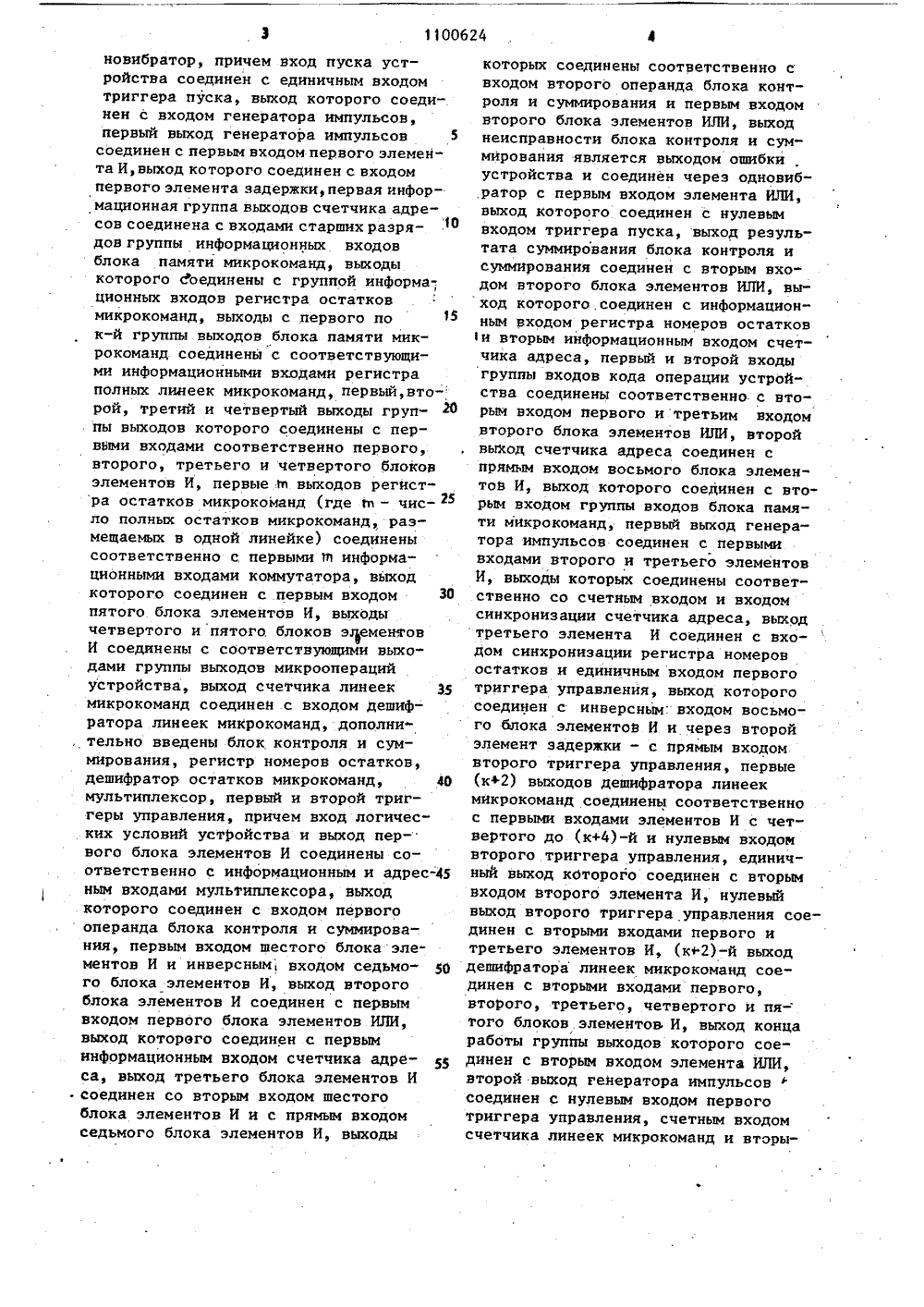

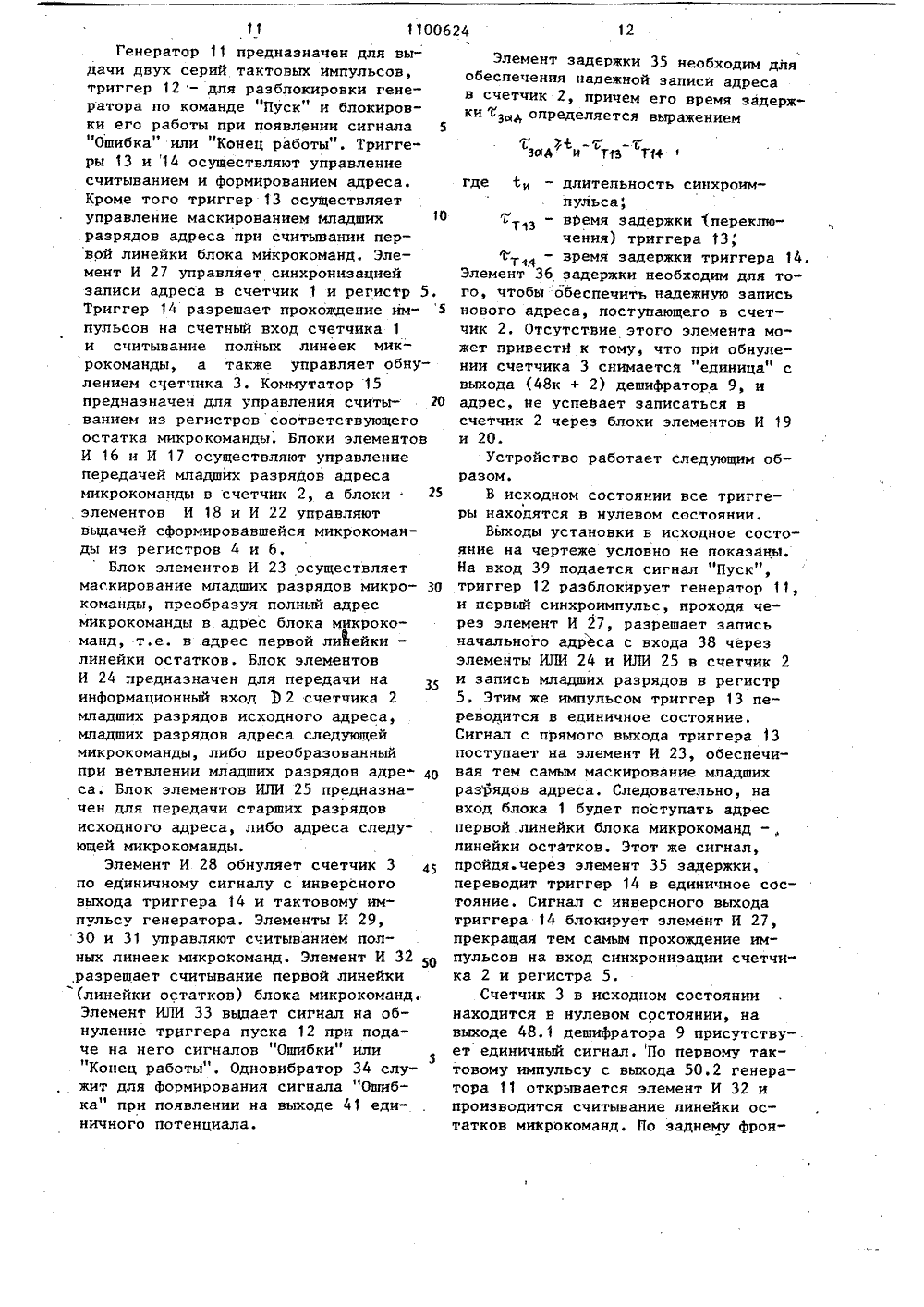

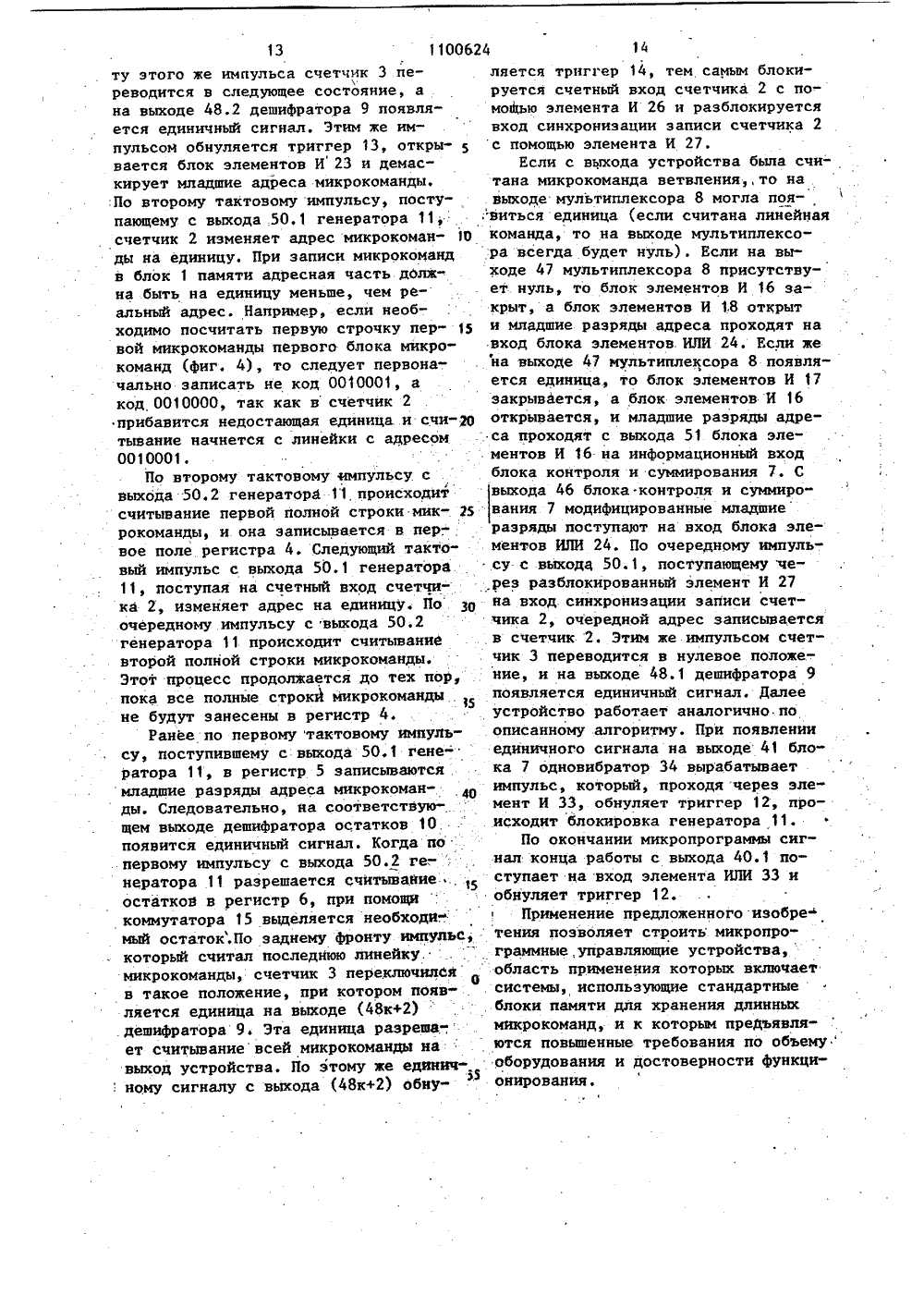

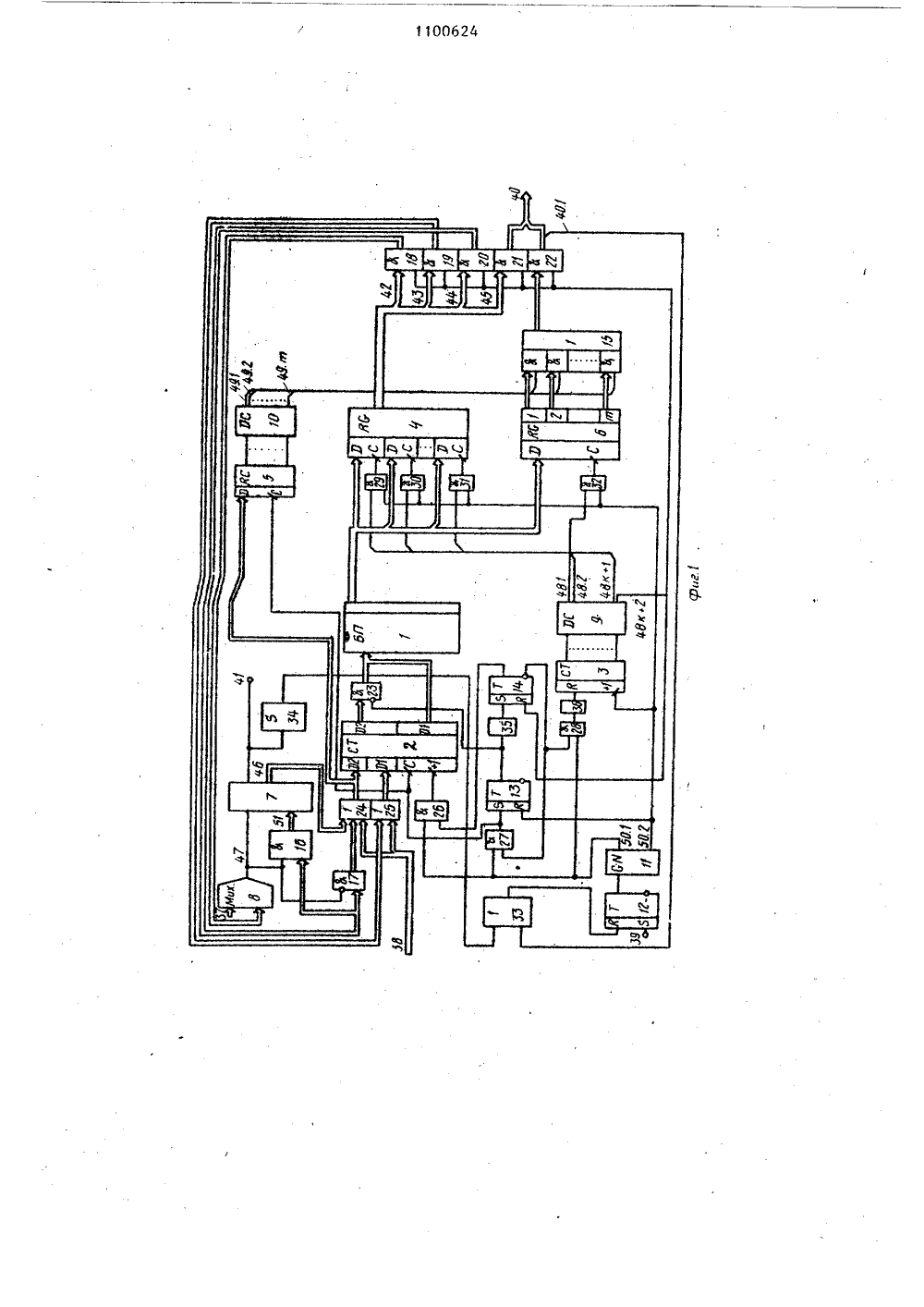

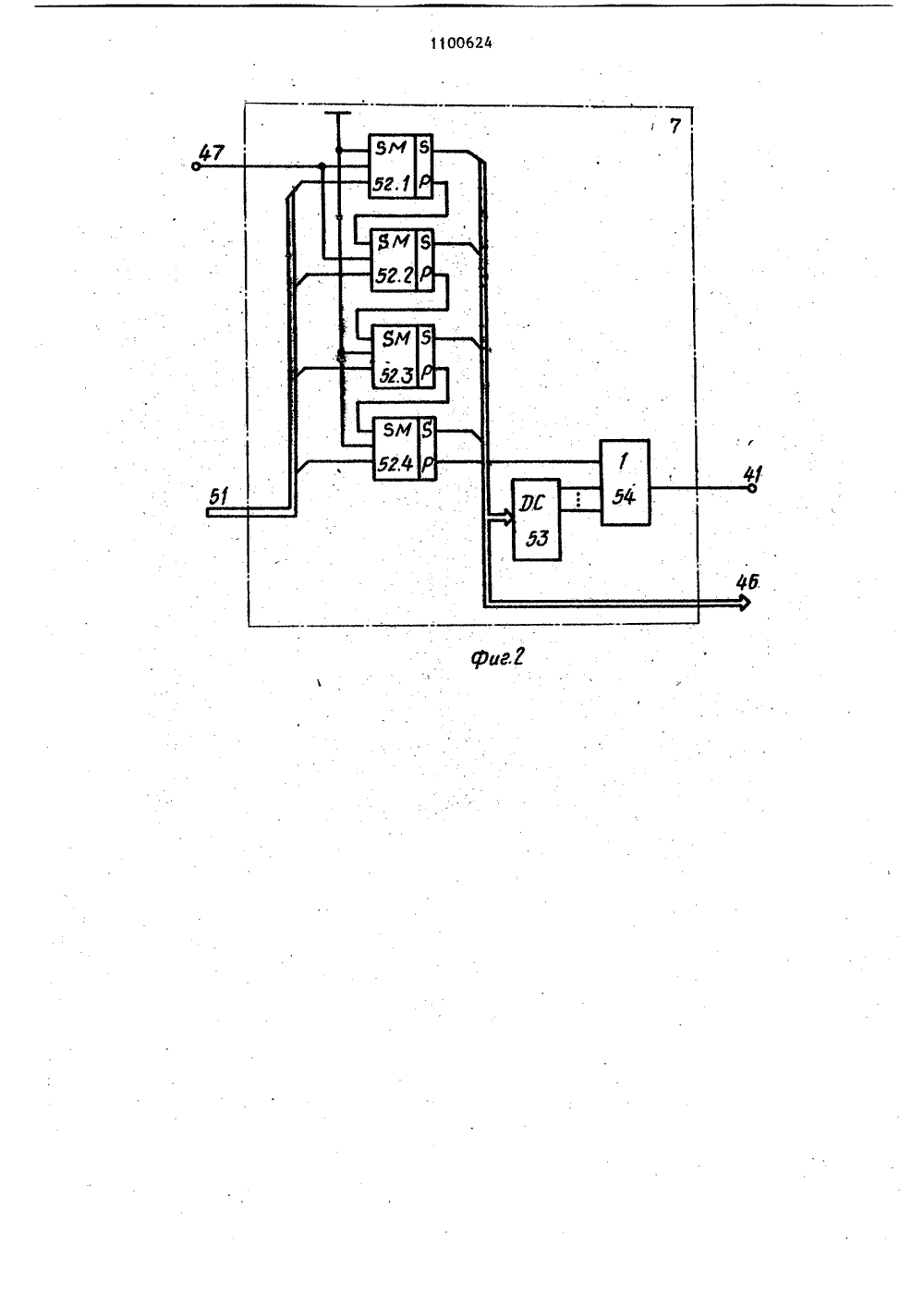

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН ОПИСАНК АВТОРСКОМУ БРЕТЕНИЯ СВ ЕЛЬСТВ(56) 1. Авторское свидетельство СССРУ 928356, кл. С 01 К 9/22,1980,2. Авторское свидетельство СССРВ. 928357, кл. С 06 Р 9/22,. 1980.3, Авторское свидетельство СССРпо заявке У 3310259/18-24,кл, С 01 Р 9/22, 02.07.81 (прототип).(54)(57) 1, МИКРОПРОГРАМИНОЕ УСТРОИСТВО УПРАВЛЕНИЯ, содержащее блок памятимикрокоманд, счетчик ацреса, счетчик.линеек микрокоманд, регистр линеекмикрокоманд, регистр остатков микрокоманд, дешифратор линеек микрокоманд,коммутатор, триггер пуска, генераторимпульсов, восемь блоков элементов И,первый и второй блоки элементов ИЛИ,(к+4) элемента И, где к - число полных линеек, занимаемых микрокомандой,первый и второй элементы задержки,одновибратор, причем вход пуска уст- .ройства соединен с единичным входомтриггера пуска, выход которого соединен с входом генератора импульсов,первый выход генератора импульсовсоединен с первым входом первого элФмента И, выход которого соединен свходом первого элемента задержки,первая информационная группа выходовсчетчика адресов соединена с входамистарших разрядов группы информацион-,.ных входов блока памяги микрокоманд,выходы которого соединены с группой. информационных входов регистра остат.ков микрокоманд, выходы с первого(21 (22 (46 первтов ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И 9 ТНРЫТИ,80, 1100624 ЗОЗ С 0 6 У 9/02 С 06 Р 11/О по к-й группы выходов блока памяти микрокоманд соединены с соответствующими информационными входами регистра полных линеек микрокоманд, первый, второй, третий и четвертый выходы группы выходов которого соединены с первыми входами соответственно первого, второго, третьего и четвертого блоков элементов И, первые 1 п выходов регистра остатков микрокоманд, где в- число полных остатков микро- команд, .размещаемых в одной линейке, соединены соответственно с первыми т информационными входами коммутатора, выход которого соединен с первым входом пятого блока элементов И, выходы четвертого и пятого блоков .элементов И соединены с соответствующими выходами группы выходов микро- операций устройства, выход счетчика линеек микрокоманд соединен с входом дешифратора линеек микрокоманд, о тл и ч а ю щ е е с я тем, что, с целью расширения области применения, ,в устройство введены блок контроля и суммирования, регистр номеров остатков, дешифратор остатков микрокоманд, . мультиплексор, первый и второй триггеры управления, причем вход логических условий устройства и выход первого блока элементов И соединены соответственно с информационным и адресным. входами мультиплексора, выход которого соединен с входом первого операнда блока контроля и суммирования, первым входом шестого бло.ка элементов И и инверсным входом седьмого блока элементов И, выход :второго блока элементов И соединен сым входом первого блока элемен- ИЛИ, выход которого соединен сСгтрсии )ЮО.М)РУФЬ/ ФжЖиик раэруРы мк ОР ОО 00 мк д 710 Составитель И. СигалТехред Т. Дубинчак Редактор К, Во Корректор М, Демчик Заказ 4582/38 Тираж ВНИИПИ Госу но делам 3035, Москваилиад ППП "Патент", г. Ужгород, ул. Проектная РУ 01Ью Р 010 РОМ ОЮО2 ик 01 И 011 О 0111 699 Подписноарственного комитета СССРзобретений и открытийЖ, Раушская наб., д. 4первым информационным входом счетчика адреса, выход третьего блока элементов И соединен со вторым входомшестого блока элементов И и прямымвходом седьмого блока элементов И,выходы которых соединены соответственно с входом второго операнда блокаконтроля и суммирования и первымвходом второго блока элементов ИЛИ,выход неисправности блока контроляи суммирования является выходомошибки устройства и соединен черезодновибратор с первым входом элементаИЛИ, выход которого соединен с нулевым входом триггера пуска, выходрезультата суммирования блока контроля и суммирования соединен с вторым входом второго блока элементовИЛИ, выход которого соединен с информационным входом регистра номеровостатков и вторым информационнымвходом счетчика адреса, первый,второй входы группы входов .кода опера"ций устройства соединены соответственно с вторым входом первого итретьим входом второго блоков элементов ИЛИ, второй выход счетчика адреса соединен с прямым входом восьмого блока элементов И, выход которого соединен с вторым. входом группы входов блока памяти микрокоманд,первый выход генератора импульсовсоединен с пе 1 выми входами второгои третьего элементов И, выходы которых соединены соответственно сосчетным входом и входом синхронизации счетчика адреса, выход третьего элемента И соединен с входомсинхронизации регистра номеров остатков и единичным входом первого триггера управления, выход которого сое"динен с инверсным входом восьмогоблока элементов И и через второйэлемент задержки - с прямым входомвторого триггера управления, первые (к+2) выходов дешифратора линеек микрокоманд соединены соответственно с первыми входами элементов Ис четвертого до (к+4)-й и нулевымвходом второго триггера управления,единичный выход которого соединен свторым входом второго элемента И,нулевой выход второго триггера управления соединен с вторыми входамипервого и третьего элементов И,(к+2)-й выход дешифратора линеекмикрокоманд соединен с вторыми входами первого, второго, третьего, четвертого и пятого блоков элементов И,выход конца работы группы выходовкоторого соединен с вторым входомэлемента ИЛИ, второй выход генератора импульсов соединен с нулевымвходом первого триггера управления,счетным входом счетчика линеек микрокоманд и с вторыми входами элементовИ с четвертого до (к+4)-й, выходыкоторых соединены соответственно свходом синхронизации регистра остат-.ков микрокоманд и входами синхронизации регистра полных линеек микрокоманд, выход регистра номеров остатков соединен с входом дешифратораостатков микрокоманд, выходы которого соединены с соответствующими уп.равляющими входами коммутатора. 2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок контроля и суммирования содержит четыре одноразрядных сумматора, дешифратор и элемент ИЛИ, причем вход первого операнда блока соединен с входами первого операнда первого и второго одноразрядных сумматоров, входы. второго операнда блока соединены с входами второго операнда первого и второго одноразрядных сумматоров и с входами первого операнда третьего и четвертого одноразрядных сумматоров, входы переноса первого, третьего и четвертого одноразрядных сумматоров соединены С шиной нулевого потенциала, выход переноса первого одноразрядного сумматора соединен с входом переноса второго одноразрядного сумматора, выходы переноса второго, третьего и четвертого однЬ- разрядных сумматоров соединены соответственно с входами второго операнда третьего и четвертого одноразрядных сумматоров и с входом элемента ИЛИ, выход которого является выходом неисправности блока, выходы суммы всех одноражрядных сумматоров соединены с входами дешифратора и образуют выход результата суммирования блока, группы. выходов дешифратора соединены с группой входов элемен.та ИЛИ.1 1100624Изобретение относится к вычисли- ными входами регистра полных линеектельной технике и автоматике и может микрокоманд, первый - четвертыи выбыть использовано при построении мик- ходы группы выходов которого соедиропрограммных устройств управления нены с первыми входами первого - четЭВМ и цифровых систем. 5, тертого блоков элементов. И, первый -1 п-й где м - число полных остаткомИзвестно устройство микропрограм п й гдмного управления, содержащее лок па.жащее блок па. микрокоманд, размещаемых в одной линейке, выхбды регистра остатков микмяти микрокоманд, два счетчика, дешифратора, регистр микрокоманд, ге- рокоманд соединены соответственно сИ 10 первым в -м информационными входаминератор импульсов, элементы И иИЛИ 1 1 коммутатора, вььод которого соединентва явля- с первым входом пятого блока элеменНедостатком этого устроиства является низкая экономичность локчность блока памя- тов И, выходы четвертого и пятогов дл блоков элементов И соединены с состти, обусловленная тем, что в отдельных его ячеиках может хранитьмикроопераций устройства, выходко целое число микрокоманд.счетчика линеек микрокоманд соединен сИзвестно устройство микропрограммного управления, содержащее лок паее блок па- входом дешифратора линеек микрокомяти микрокоманд, два счетчика, дваманд Г 33,Недостатком указанного устройстваадержки элементы И является узкая область применения всвязи с возможностью реализации тольИЛИ, одновибратор, триггер, генерако линейных последовательностей опетор импульсов23.рационных микрокоманд без обращения кНедостатком данного устройствапамяти команд системы, большой избыявляется узкая область применения,точностью блока памяти микрокоманд,обусловленная невозможностью реализая ,х и к вызванной тем, что в нем допускаетсяции микропрограмм, состоящих из микрокоманд, разрядность которых ольшеб ше хранение линейных последовательиостейтолько с естественной адресациейдлины ячеек блока памяти.30 микрокоманд, а следовательно большойНаиболее близким к изобретению по избыточностью запоминающих устройствтехнической сущности и достигаемому для хранения программ, использукицихэффекту является микропрограммное прототип в качестве управляющего устустройство управления, содержащее ройства,нижнего уровня по той же приблок памяти микрокомайд, счетчик ад чине система, в которой используетреса, счетчик линеек микрокоманд, ся устройство-прототип, имеет низкоедешифратор линеек микрокоманд, гене- . быстродействие вследствие большогоратор импульсов, триггер пуска, ком- числа обращений к памяти команд примутатор, элементы И, ИЛИ, одновибра- выполнении микропрограмм с ветвленитор, первый и второй элементы за ями), низкой достоверностью фуйкцидержки, причем вход пуска устройства онирования, обусловленной отсутствисоединен с единичным входом триггера ем средств контроля правильности выпуска, выход которого соединен с вхо- полнения микропрограмм.дом генератора импульсов, первый вы- Цель изобретения - расширение обход генератора импульсов соединен с. 45 ласти применения устройства.первым входом первого элемента И, вы- Поставленная цель достигается тем,ход которого соединен с входом пер- что в микропрограммное устройство упвого элемента задержки, первая груп- равления, содержащее блок памятипа выходов счетчика адресов соеди- микрокоманд, счетчик адреса, счетчикиена с входами старших разрядов 5 С линеек микрокоманд, регистр полныхгруппы входов блока памяти микроко- линеек микрокоманд, регистр остатковманд, группа выходов которого сое- микрокоманд, дешифратор линеек микродинена с группой информационных вхо" команд, коммутатор, триггер пуска,дов регистра остатков микрокоманд, генератор импульсов, восемь блоков,первый - к-й, где к - ,число полных 55 элементов И, первый и второй локилинеек, занимаемых одной микрокоман- элементов ИЛИ, (к 4) элементл мента Идой, выходы группы выходов блока па- где к - чиСло полных линеек, занимамяти микрокоманд соединены соответ- емых .микрокомандой элемента И, нерственно с первым - к-м информациои- вый и второй элементы задержки, одновибратор, причем вход пуска устройства соединен с единичным входомтриггера пуска, выход которого соединен с входом генератора импульсов,первый выход генератора импульсов 5соединен с первым входом первого элемента И, выход которого соединен с входомпервого элемента задержки, первая информационная группа выходов счетчика адресов соединена с входами старших разрядов группы информационных входовблока памяти микрокоманд, выходыкоторого соединены с группой информа;.ционных входов регистра остатковмикрокоманд, выходы с первого пок-й группы выходов блока памяти микрокоманд соединены с соответствующими информационными входами регистраполных линеек микрокоманд, первый,вто-рой, третий и четвертый выходы группы выходов которого соединены с первыми входами соответственно первого,второго, третьего и четвертого блоковэлементов И, первые:в выходов регистра остатков микрокоманд (где в - число полных остатков микрокоманд, размещаемьп в одной линейке) соединенысоответственно с первыми В информационными входами коммутатора, выходкоторого соединен с первым входом З 0пятого блока элементов И, выходычетвертого и пятого. блоков эгемен;говИ соединены с соответствующими выходами группы выходов микрооперацийустройства, выход счетчика линеек З 5микрокоманд соединен с входом дешифратора линеек микрокоманд, дополнительно введены блок контроля и суммирования, регистр номеров остатков,дешифратор остатков микрокоманд, 40мультиплексор, первый и второй триггеры управления, причем вход логических условий устройства и выход первого блока элементов И соединены соответственно с информационным и адрес ным входами мультиплексора, выходкоторого соединен с входом первогооперанда блока контроля и суммирова-.ния, первым входом шестого блока элементов И и инверсным, входом седьмого блока элементов И, выход второгоблока элементов И соединен с первымвходом первого блока элементов ИЛИ,выход которого соединен с первыминформационным входом счетчика адреса, выход третьего блока элементов Исоединен со вторым входом шестогоблока элементов И и с прямым входомседьмого блока элементов И, выходы которых соединены соответственно свходом второго операнда блока контроля и суммирования и первым входомвторого блока элементов ИЛИ, выходнеисправности блока контроля и суммирования является выходом ошибкиустройства и соединен через одновиб",ратор с первым входом элемента ИЛИ,выход которого соединен с нулевымвходом триггера пуска, выход результата суммирования блока контроля исуммирования соединен с вторым входом второго блока элементов ИЛИ, выход которого. соединен с информацион"ным входом регистра номеров остатков1 и вторым информационным входом счетчика адреса, первый и второй входыгруппы входов кода операции устройства соединены соответственно с вторым входом первого и третьим входомвторого блока элементов ИЛИ, второйвыход счетчика адреса соединен спрямым входом восьмого блока элементов И, выход которого соединен с вторым входом группы входов блока памяти микрокоманд, первый выход генератора импульсов соединен с первымивходами второго и третьего элементовИ, выходы которых соединены соответственно со счетным входом и входомсинхронизации счетчика адреса, выходтретьего элемента И соединен с входом синхронизации регистра номеровостатков и единичным входом первоготриггера управления, выход которогосоединен с инверсным входом восьмого блока элементов И и через второйэлемент задержки - с прямым входомвторого триггера управления, первые(к+2) выходов дешифратора линеекмикрокоманд соединены соответственнос первыми входами элементов И с четвертого до (к+4)-й и нулевым входоивторого триггера управления, единичный выход кОторого соединен с вторымвходом второго элемента И, нулевыйвыход второго триггера управления соединен с вторыми входами первого итретьего элементов И, (к.2)-й выходдешифратора линеек микрокоманд соединен с вторыми входами первого,второго, третьего, четвертого и пя-того блоков элементов И, выход концаработы группы выходов которого соединен с вторым входом элемента ИЛИ,второй выход генератора импульсовсоединен с нулевым входом первоготриггера управления, счетным входомсчетчика линеек микрокоманд и вторы:ми входами элементов И, с четвертогодо (к+4)-й, выходы которых соединенысоответственно с входом синхронизациирегистра остатков микрокоманд и входами синхронизации регистра полныхлинеек микрокоманд, выход регистраномеров остатков соединен с входомдешифратора остатков микрокоманд,выходы, которого соединены с соответствующими управляющими входами коммутатора,Кроме того, блок контроля и суммирования содержит четыре одноразрядных сумматора, дешифратор и элементИЛИФ причем вход первого операнда 15блока соединен с входом первого операнда первого и второго одноразрядных сумматоров, выходы второго операнда блока соединены с входами второгооперанда первого и второго однораз Орядных сумматоров и входами первогооперанда третьего и четвертого одноразрядных сумматоров, входы переносапервого, третьего и четвертого одноразрядных сумматоров соединены с шиной нулевого потенциала, выход переноса первого одноразрядного сумматора.соединен с входом переноса второгоодноразрядного сумматора, выходы переноса второго, третьего и четверто- ЭОго одноразрядных сумматоров соединенысоответственно с входами второго опе"ранда третьего и четвертого одноразрядных сумматоров и с входом элемента ИЛИ, выход которогоявляется выходом неисправности блока, выходысуммы всех одноразрядных сумматоровсоединены с. входами дешифратора иобразуют выход результата суммирования блока, группы выходов дешифрато- щра соединены с группой входов элемента ИЛИ. Сущность изобретения состоит врасширении области применения путем,организации условных и бузусловных .,йереходов в микропрограммах,состоящихиз микропрограмм, разрядность которых превышает разрядность линеекблока памяти без использования про-,10граммных средств, а также организацийконтроля правильности переходов вмикропрограммах на основе проверкисоответствия сформированного кодаадреса очередной микрокоманды задан.ным требованиям,В блоке памяти микрокоманды располагаются поблочно. Каждый блок сос"тоит из (в%+1)-й линейки (где кчисло полных линеек, занимаемых одной микрокомандой, т,е. к = 1 М -(1),с ь и г - разрядность микрокоманды и линейки блока, памяти соответственно), в - число полных остатков микрокоманд,. раз зщенных в одной линейке, т. е.п 1= 1 М -Каждый блок микрокоманд имеет следующую структуру: в первой линейкеблока располагаются остатки микрохоманд, причем их размещение слева направо по 5 =-12 разрядов соответствует номеру микрокоманды в блоке, вовторой - (к+1)-й линейках располагается целая часть первой микрокомандыблока, в (к+2)-й - (2 к+1)-й - целаячасть второй микрокоманды и т,д. В(щ) к+2 (вМ+1) -й линейкахблокарасполагается целая часть в-й микрокоманды.Микрокоманды, размещаемые в бло-.ке памяти, содержат как операционную,так и адресную части, в том числе иполе кода логических условий. Каждый адрес состоит из двух частей:старшие разряды указывают номер блока мнкрокоманд, к которому необходимо перейти, а младшие - задают номерпервой линейки в блоке, в которой записана начальная часть очередной микрокоманды,В мнкрокомандах ветвления в полекода логических условий задается номер проверяемого логического условия.При ветвлении происходит модификациятолько младших разрядов адреса, т.е.микрокоманды, следующие за ветвлением,размещаются в одном блоке. Функция .,модификации определяется внутреннейструктурой блока контроля и суммирования. В рассмотренном ниже примереконкретного выполнения этого узламодификация младших разрядов осуществляется только при единичном значении проверяемого условия путем суммирования их с константой, равной к.При таком варианте модификации микрокоманды, следующие за ветвлением,располагаются в соседних группах ли",неек блока, состоящих из к линеек.Считывание микрокоманд осуществляетСя за (к+1) такт. Сначала считывается линейка остатков (при этоммладшие разряды адреса маскируются),а затем последовательно считываются1100624 8 1ментов И, второй блок 24,элементовИЛИ, первый блок 25 элементов ИЛИ,второй элемент 26 И, третий элемент27 И, первый элемент 28 И, пятый 29,шестой 30 и (к+4)-й 31 элементы Исоответственно, четвертый элемент32 И, элемент 33 ИЛИ, одновибратор34, первый элемент 35 задержки, второй элемент 36. задержки, вход 37 логических условий устройства, вход 38кода операции устройства, вход 39пуска устройства, группу входов 40микрооперацнй устройства, выход 40.1микрооперацни "Конец работы", выход41 ошибки устройства, выход 42 кода разрядов адресной части микрокоманд (адреса блока, микрокоманд), выход 44 младших разрядов адресной части микрокоманд (адреса микрокоманды в блоке микрокоманд), выход 45 операционной части микрокоманд регистра 4, информационный выход 46 блока контроля и суммирования, выход 47 мультиплексора, выходы 48,1 - (48. к+2)-й дешифратора линеек мнкрокоманд, выходы 49.1 - 49 п дешифратора остатков микрокоманд, первый 50.1 и второй 50.2 выходы генератора импульсов 11 соответственно, выход 51 блока элемента И.На фиг. 2 обозначено." первый 52.11 второй 52.2, третий 52.3 и четвертый 52.4 одноразрядные комбинационные сумматоры соответственно, дешифратор 53 адреса, блок 54 элементов ИЛИ.Блок 1 памяти микрокоманд предназначен для хранения микрокоманд. В микрокоманде поля расположены следующим образом: поле логических услорес микрокоманды в блоке, микроопе.-ф каждая иэ которых занимает к полных мер размещения микрокоманд приведенна фиг. 4 для щ= 3, к = 3,части микрокоманд, хранящиеся в линейках с 01 +2) -й по 1.(1+1) (к+1)3 -ю(1=О, в);Принцип контроля, реализованный впредлагаемом устройстве, основан на 5том положении, что при ветвлении неможет быть сформирован адрес, прикотором осуществляется переход к другому блоку микрокоманд, т.е. есличисло, соответствующее младшим разрядам исполнительного адреса микрокоманды ветвления, превышает величину п 1(к)+2 -, это означает, чтопроизошел сбой или устойчивый отказв адресных цепях устройства, включаяи соответствующие ячейки блока па-логических условий, выход 43 старшихмяти.Введение блока контроля и суммирования позволяет осуществлять модификацию адреса и проверять правильность функционирования адресных цепей устройства. Регистр номеров остатков и дешифратор остатков микрокоманд управляют выбором разрядовкода остатков, соответствующих считываемой микрокоманде, мультиплексоробеспечивает выбор значения логического условия в соответствии с кодом,задаваемым в формате микрокоманды.Первый и второй триггеры управления ЗОуправляют занесением информации всчетчик адреса и.маскированиум младших разрядов адреса.На фиг. 1 представлена функциональная схема микропрограммного 35устройства, управления; на фиг. 2 блок контроля и суммирования, нафиг. 3 - пример размещения микрокоманд в блоке памяти,Схема микропрограммного устройства 140содержит блок 1 памяти микрокоманд, вии, адРесная часть, разбитая на двесчетчик 2 адреса, счетчик 3 линеек . части: адрес блока микрокоманд н адмикрокоманд, регистр 4 полных линеек микрокоманд, регистр 5 номеров45остатков, регистр 6 остатков. микрокоманд, блок 7 контроля и суммирования, мультиплексор 8, дешифратор 9линеек. Таким образом, число линеек влинеек микрокоманд, дешифратор 10 остатков микрокоманд, генератор 11 имблоке микрокоманд равно (пФ). П иР д равно ЬФ 11 Припульсов, триггер 12 пуска, первыйтриггер 13 управления, второй триггер14 управления, коммутатор 1,5, шестой Счетчик 2 предназначен для записиблок 16 элементов И, седьмой блок 17 и хранения адреса очередной линейкиэлементов И, первый блок 18 элемен", блока 1 памяти микрокоманд. Он иметов И; второй блок 19 элементов И, 55 ет два информационных поля Р 1 и Р 2.третий блок 20 элементов И, четвер- Поле 3 2 предназначено для записитый блок 21 элементов И, пятый блок адреса микрокоманды в блоке (млад 22 элементов И, восьмой блок 23 эле- ших разрядов адреса), Р 1 - для за1 О 110 ОЬ 24 0001 010 100 писи адреса блока микрококанд, т.е,адреса линейки с записанными в нееостатками микрокоманд. Счетчик 3 применяется для управления считыванияполных линеек микрокоманды, образующнх ее целую часть, регистр 4 - дляхранения полных линеек считываемыхмикрокоманд, регистр 5 " для хранения адреса микрокоманды в блоке,регистр 6 - длязаписи и храненияостатков всех микрокоманд, входящихв данный блок микрокоманд,Пример выполнения схемы блокаконтооля и суммирования 7 представлен на Фиг. 2, Он необходим для изменения адреса микрокоманды в блокекогда на выходе 47 мультиплексора 8появится единичный. сигнал, соответствующий единичному значению логического условия. В этом случае к дан- Юному адресу микрокоманды прибавляется. константа, равная числу полных линеек микрокоманды. Иикрокоманды, следующие после ветвления, расположенырядом в одном блоке, т,е. у них отличаются только младшие разряды адресаРассмотрим работу блока 7 на при-,:мере. Если на выходе 47 мультиплексора 8 появилась 1, то к младшим. разрядам адреса микрокоманды прибав- ЗОляется константа, равная к, т.е, число полных линеек микрокоманды. Этаоперация осуществляется с помощьюсумматоров 52.1 - 52.4. Если послепервой микрокоманды, которая являет- Зся микрокомандой ветвления (фиг,3),должен быть осуществлен переход поединичному значению логического условия, к младшим разрядам адреснойчасти этой микрокоманды 0100 необхо".4 Одимо прибавить код 0011 (к = 3).Тогда произойдет переход от первоймикрокоманды к третьей, а не ко второй (переход ко второй осуществляется при нулевом значении логического, 4условия) Если на выходе четвертогосумматора 52.4 появится единичныйсигнал, этоозначает, что в устройстве произошла ошибка, Поскольку длязаписи младших разрядов адреса ис-,пользуется в 1 с + 1)-я комбинация .двоичных символов, то это приводит .кпоявлению збыточных комбинаций. Таким образом,се наборы, для которых выполняется равенство ьО являются следствием ошибки.В данном случае гп%+ 1 = 10, следовательно появление на выходах сумматоров 52.1 - 52,4 двоичных кодов, соответствующих числам 11, 12, 13, 14, 15, свидетельствует об ошибке в. работе устройства. Тогда дешифратор 53 имеет четыре входа и пять выходов, на которых дешифрируются кодовые комбинации 1011,1100, 1.101, 1110 и 1111 соответственно. При их появлении на входе дешифратора.53 или,появлении сигнала переполнения на выходе сумматора 52.4 Формируется сигнал ошибки на выходе элементаМультиплексор 8 предназначен для выделения значения логического условия, соответствующего заданному току, который поступает с выхода устройства. Мультиплексор 8,.выполняет следующую логическую функцию+ аааз асх+где а;, 1 =г, - значение 1-го разрядакода проверяемого логического условия,х ,1=,г - значение 1-го логического условия, поступающего от объекта управления.Дешифратор 9 линеек микрокоманды единичным сигналом на выходе 48.1 разрешает считывание первой линейки остатков блока микрокоманд, при появлении "единицы" на каждом следующем выходе, кроме 48 к + 2, осуществляется последовательное считывание полных линеек микрокоманды.Дешифратор 10 остатков микрокоманды служит для выбора нужного ос-татка микрокоманды. Рассмотрим его работу на примере, приведенном на фиг. 4. Если считана вторая микро- команда по адресу 0100, то из первой линейки необходимо выбрать второй остаток, Работу дешифратора можно описать следующей таблицей:11 11006Генератор 11 предназначен для выдачи двух серий тактовых импульсов,триггер 12 - для разблокировки генератора по команде "Пуск" и блокировки его работы при появлении сигнала 5"Ошибка" или "Конец работы". Триггеры 13 и 14 осуществляют управлениесчитыванием и формированием адреса.Кроме того триггер 13 осуществляетуправление маскированием младших 10разрядов адреса при считывании первой линейки блока микрокоманд, Элемент И 27 управляет синхронизациейзаписи адреса в счетчик 1 и регистр 5.Триггер 14 разрешает прохождение импульсов на счетный вход счетчика 1и считывание полных линеек микрокоманды, а также управляет обнулением счетчика 3. Коммутатор 15предназначен для управления считыванием из регистров соответствующегоостатка микрокоманды. Блоки элементовИ 16 и И 17 осуществляют управлениепередачей младших разрядов адресамикрокоманды в счетчик 2, а блоки 5элементов И 18 и И 22 управляютвыдачей сформировавшейся микрокоманды из регистров 4 и 6,Блок элементов И 23 осуществляетмаскирование младших разрядов микрокоманды, преобразуя полный адресмикрокоманды в адрес блока микрокоманд, т,е, в адрес первой лийейки -линейки остатков. Блок элементовИ 24 предназначен для передачи наинформационный вход Э 2 счетчика 2младших разрядов исходного адреса,младших разрядов адреса следующеймикрокоманды, либо преобразованныйпри ветвлении младших разрядов адреса. Блок элементов ИЛИ 25 предназначен для передачи старших разрядовисходного адреса, либо адреса следующей микрокоманды.Элемент И 28 обнуляет счетчик 3 45по единичному сигналу с инверсноговыхода триггера 14 и тактовому импульсу генератора. Элементы И 29,30 и 31 управляют считыванием полных линеек микрокоманд. Элемент И 32 0,разрешает считывание первой линейки1 линейки остатков) блока микрокоманд.Элемент ИЛИ 33 выдает сигнал на обнуление триггера пуска 12 при подаче на него сигналов "Ошибки" или"Конец работы". Одновибратор 34 служит для формирования сигнала "Ошибка" при появлении на выходе 41 единичного потенциала. 1224Элемент задержки 35 необходим для обеспечения надежной записи адреса в счетчик 2, причем его время задержки з определяется выражениемюад и тИ тигде С - длительность синхроимпульса,ь з - вРемя задержки переклю"чения) триггера 13,ьт - время задержки триггера 14.Элемент 36 задержки необходим для того, чтобы обеспечить надежную записьнового адреса, поступающего в счетчик 2, Отсутствие этого элемента может привестИ к тому, что при обнулении счетчика 3 снимается "единица" свыхода (48 к + 2) дешифратора 9, иадрес, не успевает записаться всчетчик 2 через блоки элементов И 19и 20.Устройство работает следующим образом.В исходном состоянии все триггеры находятся в нулевом состоянии.Выходы установки в исходное состояние на чертеже условно не показаны.На вход 39 подается сигнал "Пуск",триггер 12 разблокирует генератор 11,и первый синхроимпульс, проходя через элемент И 27, разрешает записьначального адреса с входа 38 черезэлементы ИЛИ 24 и ИЛИ 25 в счетчик 2и запись младших разрядов в регистр5, Этим же импульсом триггер 13 переводится в единичное состояние,Сигнал с прямого выхода триггера 13поступает на элемент И 23, обеспечивая тем самым маскирование младшихразрядов адреса, Следовательно, навход блока 1 будет поступать адреспервой линейки блока микрокоманд -линейки остатков. Этот же сигнал,пройдя. через элемент 35 задержки,переводит триггер 14 в единичное состояние. Сигнал с инверсного выходатриггера 14 блокирует элемент И 27,прекращая тем самым прохождение импульсов на вход синхронизации счетчи"ка 2 и регистра 5.Счетчик 3 в исходном состояниинаходится в нулевом состоянии, навыходе 48.1 дешифратора 9 присутствует единичный сигнал. По первому тактовому импульсу с выхода 50,2 генератора 11 открывается элемент И 32 ипроизводится считывание линейки остатков микрокоманд. По заднему фрон13 1100624 14ту этого же импульса счетчик 3 пе- ляется триггер 14, тем самым блокиреводится в следующее состояние, а руется счетный вход счетчика 2 с пока выходе 48.2 дешифратора 9 появля- мощью элемента И 26 и разблокируется ется единичный сигнал. Этим же им- вход синхронизации записи счетчика 2 пульсом обнуляется триггер 13, откры с помощью элемента И 2. вается блок элементов И 23 и демас- Если с выхода устройства была счикирует младшие адреса микрокоманды. тана микрокоманда ветвлениято на .По второму тактовому импульсу, посту- выходе мультиплексора 8 могла пояпающему с выхода 50.1 генератора 11,: "виться единица (если считана линейная счетчик 2 изменяет адрес микрокоман О команда, то на выходе мультиплексоды на единицу. При записи микрокоманд Ра всегда бУдет нуль). Если на выв блок 1 памяти адресная часть долж- ходе 47 мультиплексора 8 присутствуна быть на единицу меньше, чем ре- ет нуль, то блок элементов И 16 заальный адрес. Например, если необ- крыт, а блок элементов И 1,8 открыт ходимо посчитать первую строчку пер и младшие Разряды адреса проходят на вой микрокоманды первого блока микро- вход блока элементов ИЛИ 24, Если же команд (фиг, 4), то следует первона- . на выходе 47 мультиплексора 8 появлячально записать не код 0010001, а ется единица, то блок элементов И 17 код 0010000, так как в счетчик 2 закрывйется, а блок элементов И 16прибавится недостающая единица и счиоткрывается, и младшие разряды адретывание начнется с линейки с адресом са проходят с выхода 51 блока эле, ментов И 16 на информационный входПо второму тактовому импульсу с блока контроля и суммирования 7. С выхода 50,2 генератора 11 происходит выхода 46 блока контроля и суммиро" считывание первой полной строки мик ванин 7 модифицированные младшие рокоманды, и она записывается в пер". Разряды поступают на вход блока элевое поле регистра 4. Следующий такто- ментов ИЛИ 24. По очередному импульвый импульс с выхода 50.1 генератора су с выхода 50.1, поступающему че, поступая на счетный вход счетчи- реэ разблокированный элемент И 27 ка 2, изменяет адрес на единицу. По Зо на вход синхронизации записи счет- очередному импульсу с выхода 50,2 чща 2, очередной адрес записывается генератора 11 происходит считывание в счетчик 2. Этим же импульсом счет- второй полной строки микрокоманды, чик 3 переводится в нулевое положе-. Этот процесс продолжается до тех пор, ние, и на выходе 48.1 дешифратора 9 пока все полные строки микрокоманды появляется единичный сигнал. далее15не будут занесены в регистр 4. Устройство работает аналогично.поРанее по первому тактовому импуль- .описанному алгоритму. При появлении су, поступившему с выхода 50,1 гене- единичного сигнала на выходе 41 блоратора 11, в регистр 5 записываются . ка 7 одновибратор 34 вырабатывает младшие разряды адреса микрокоман О импульс, который, проходя через эледы. Следовательно, на соответствую- мент И 33, обнуляет триггер 12, прощем выходе дешифратора остатков 10. . исходит блокировка генератора 11.появится единичный сигнал. Когда по По окончании микропрограммы сигпервому импульсу с выхода 50.2 ге; : , нал конца работы с выхода 40. 1 понератора 11 разрешается считывание 15 ступает на вход элемента ИЛИ 33 и остатков в регистр 6, при помощи .обнуляет триггер 12,Применение предложенного изобрекоммутатора 15 выделяется необходи.мый остаток,По заднему фронту импульс, тения позволяет строить микропрокоторый считал последнюю линейку. ". Граммные.управляющие устройства, микрокоманды, счетчик 3 переключился. область применения которых включаетав такое положение, при котором появ- . системы, использующие стандартные ляется единица на выходе (48 к+2) блоки памяти для хранения длинныхмикрокоманд, и к которым предьявлядешифратора 9. Эта единица разреша-,ются повышенные требования по обьемует считывание всей микрокоманды навыход устройства. По этому же единич- оборудования и достоверности функци 5,5

СмотретьЗаявка

3569844, 29.03.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ЛИТВИНЕНКО ВАДИМ ГЕОРГИЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 30.06.1984

Код ссылки

<a href="https://patents.su/12-1100624-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для распределения заданий вычислительной системе

Следующий патент: Микропрограммное устройство управления

Случайный патент: Способ получения карбоксиметилцеллюлозы