Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

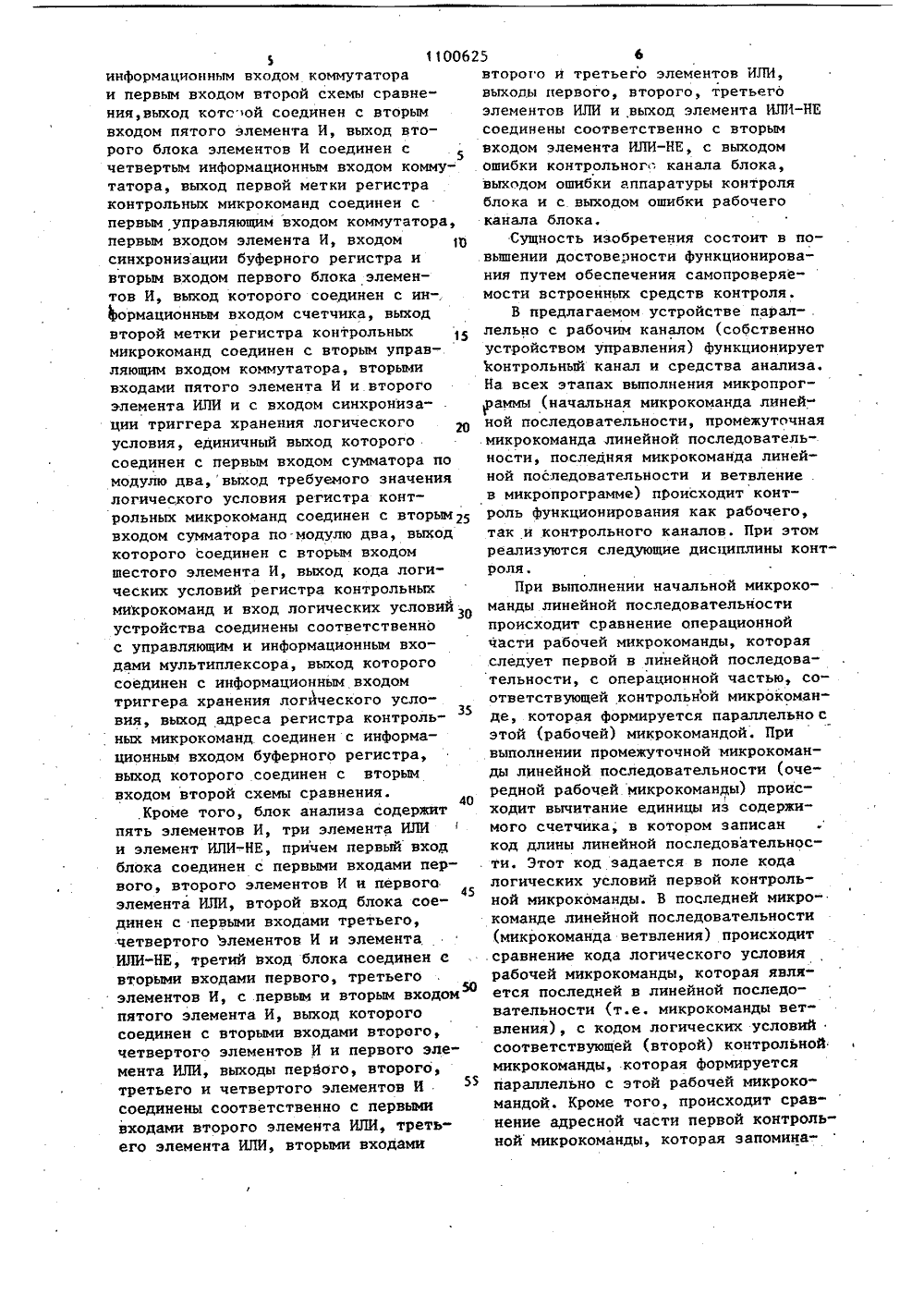

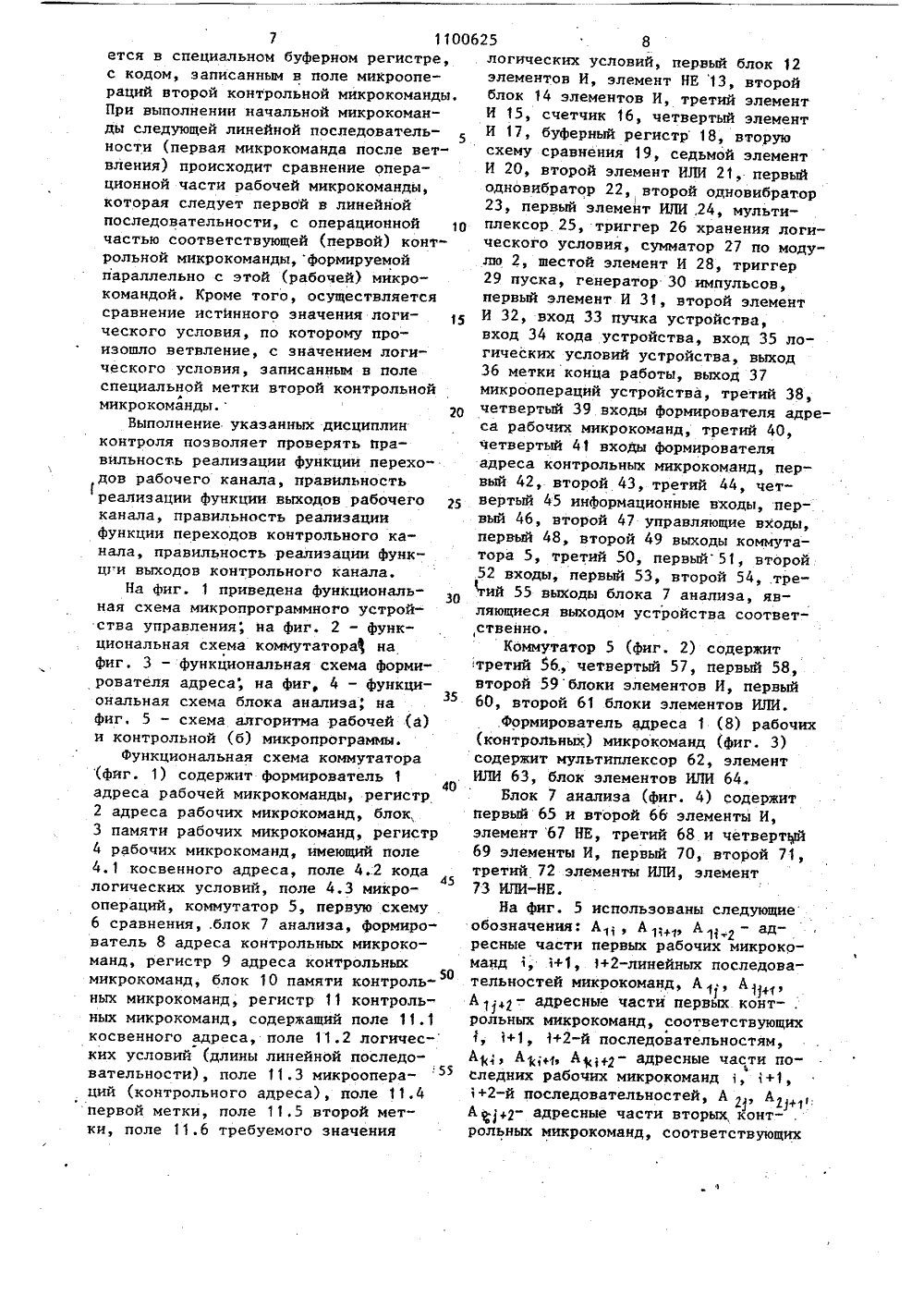

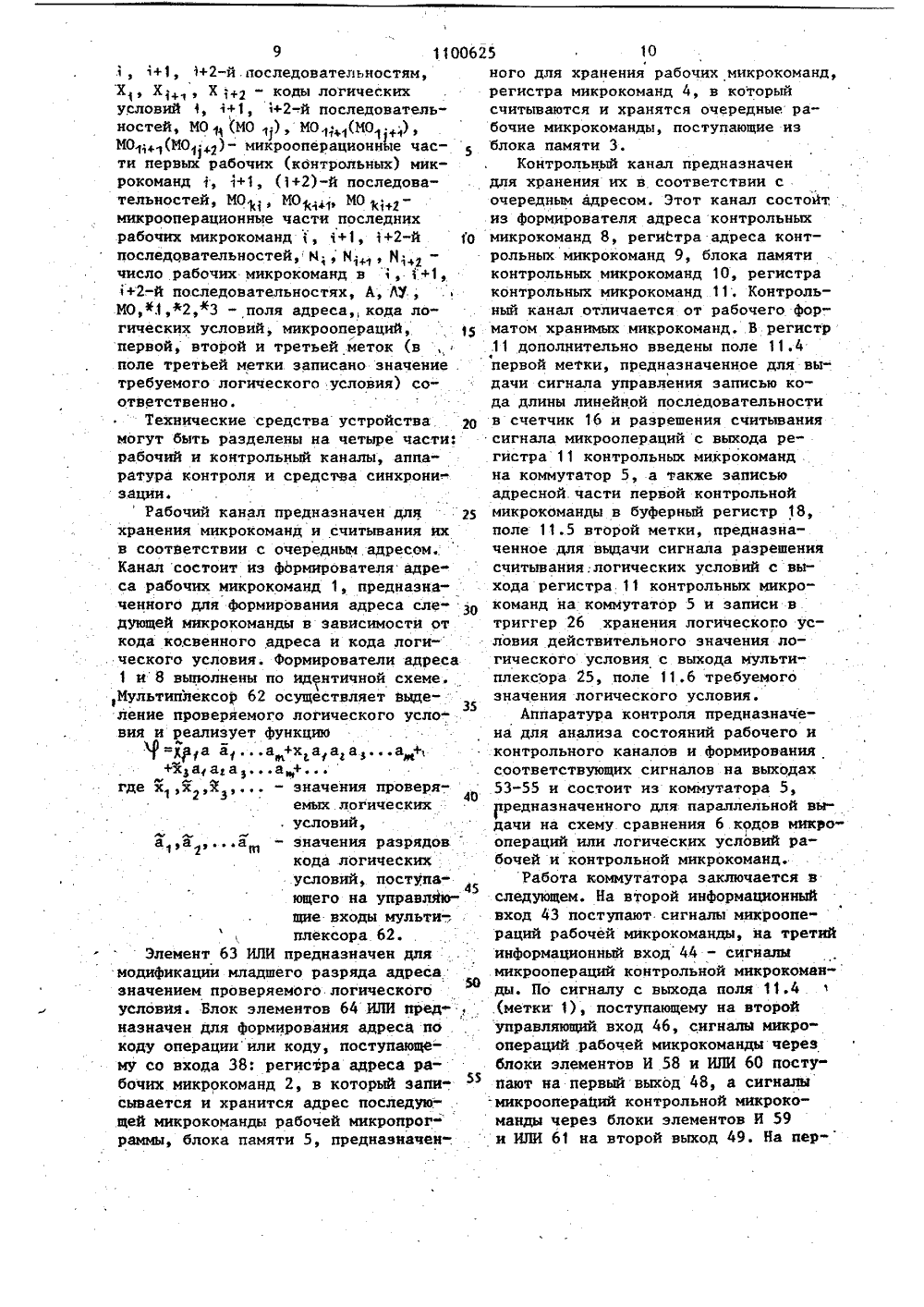

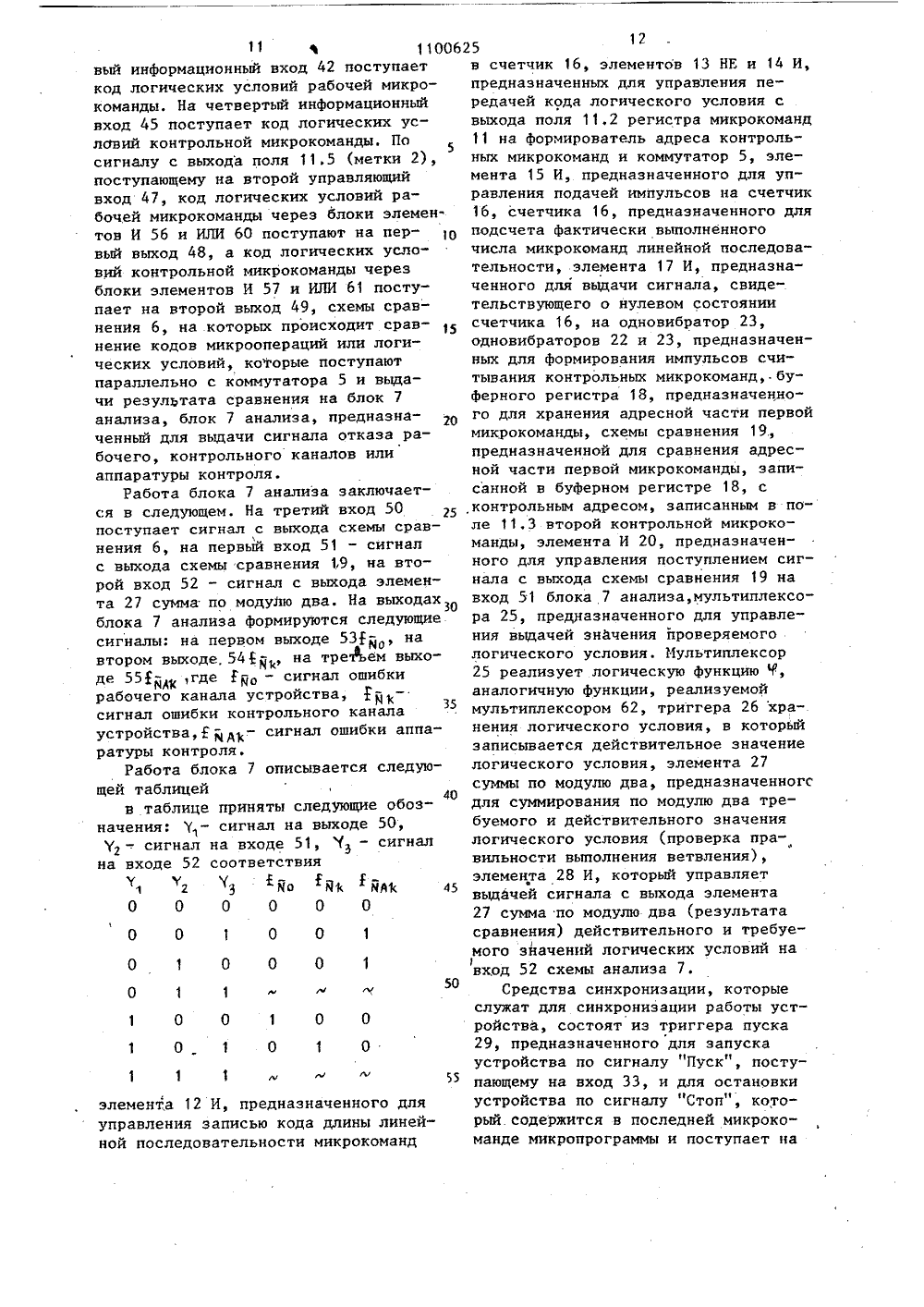

е свидетельство 06 Р 11/00, 197 свидетельство С 06 Р 9/22, 1979 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРГ О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ(54) (57) 1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее формировательадреса рабочих микрокоманд, формирователь адреса контрольных микрокоманд,регистр адреса рабочих микрокоманд регистр адреса контрольных микрокоманд блок памяти рабочих микрокоманд,блокпамяти контрольных микрокоманд, регистр рабочих микрокоманд, регистрконтрольных микрокоманд, генератортактовых импульсов, блок анализа,счетчик, триггер пуска, первый и второй блоки элементов И, шесть элементов И, первый элемент ИЛИ и элемент НЕ,причем вход кода операции устройствасоединен с первыми входами формирова.телей адреса рабочих и контрольных микрокоманд соответственно, выходы которых соединены с входами регистров адреса рабочих и контрольных микрокоманд соответственно, вход логических услоф вий устройства соединен с вторыми входами формирователей адреса рабочих и контрольных микрокомаяд,выходыад реса кода логических условий микроопераций и метки конца работы регистра рабочих микрокоманд соединены соответственно с третьим и четвертым,80, 1100625 входами формирователя аДреса рабочих микрокоманд, выходом микроопераций устройства и нулевым выходом триггера пуска, выход которого соединен с первым входом первого элемента И, вход пуска устройства и выход генератора тактовых импульсов соединены соответственно с единичным входом триггера пуска и вторым входом первого элемента И, выход которого соединен с первым входом второго элемента И и входом считывания блока памяти рабочих микрокоманд, выход регистра адреса рабочих микрокоманд соединен с адресным входом блока памяти рабочих микрокоманд, выход которого соединен с информационным входом регистра рабочих микрокоманд, выход первого элемента ИЛИ соединен с вторым входом, второго элемента И, выход которого соединен с входом считывания блока памяти конт- рольных микрокоманд, выход регистра адреса контрольных микрокоманд соеди нен с адресным входом блока памяти кон- , трольных микрокоманд, выход которого . соединен с входом регистра контрольньпц микрокоманд, выход адреса регистра контрольных миерокоманд соединен с третьим входом формирователя адреса контрольных микрокоманд, выход кода логических условий регистра контрольных микрокоманд соединен с первыми входами первого и второго блоков элементов И, выход второго блока элементов И соединен с четвертым входом формирователя адреса контрольных микрокоманд, выход первой метки регистра контрольных микрокоманд соединен с первым входом третьего элемента И и через элемент НЕ с вторым входом второго блока элементов И, выход треть11006 15При этом контролируется правильность перехода от первой ко второйконтрольной микрокоманде, а следовательно, работоспособность контрольного канала. С выхода поля 11.5 сигнал поступает на коммутатор 5 и разрешает параллельное поступление кодовлогических условий рабочей и контрольной микрокоманд на схему сравнения 6, где происходит их сравнение, 10результат которого поступает на блок7 анализа. Этот же сигнал через элемент ИЛИ 21 поступает на одновибратор22, который формирует импульс считывания следующей первой после ветвле Зния контрольной микрокоманды,Прохождение рабочих и контрольныхмикрокоманд происходит аналогичноописанному. Кроме того, сигнал с выхода поля 11.4, поступая на элемент 20И 28, разрешает прохождение сигналас элемента 27 сумматора по модулю два,который сравнивает истинное значение25 16 логического условия, зафиксированного триггером 26, с требуемым его зна- . чением, записанным в поле 11.6, на блок 7 анализа, что позволяет проверить правильность ветвления в микро- грамме и обнаруживать сбой. Дальнейшая работа происходит по алгоритму, описанному вьппе.По микрооперации "Стопц, которая содержится в последней микрокоманде микропрограммы, сигнал с выхода 36 поля 4.3 регистра мнкрокоманд 4 поступает на Р -вход 36 триггера пуска 29 и устанавливает его в нулевое состояние, тем самым запрещая прохождение синхроимпульсов с генератора 30 через элемент И 31 на входы считывания блоков памяти.Применение предлагаемого технического решения позволит проектировать надежные микропрограммные управляющие устройства с высокой достовер-. ностью функционирования.100 б 25 1 его элемента И соединен со счетным входом счетчика, инверсные выходы которого соединены с входами четвертого элемента И, выходы пятого и шесто" го элементов И соединены соответственно с первым и вторым входами блока анализа, первый выход которого является выходом ошибки рабочего канала устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности функционирования, в устройство дополнительно введены буферный регистр, коммутатор, первая и вторая схемы сравнения, мультиплексор, триггер хранения логического условия, сумматор по модулю два, первый и второй одновибраторы, второй элемент ИЛИ, причем вход пуска устройства соединен с первым. входом второго элемента ИЛИ, выход которого через первый одновибратор соединен с первым входом первого элемента ИЛИ, выход четвертого элемента И через второй одновибратор соединен с вторым входом первого элемента ИЛИ, выходы кода логических условий и микроопераций регистра рабочих микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым входами первой схемы сравнения, выход первой схемы сравнения соединен с третьим входом блока анализа, второй и третий выходы которого соединены с выходами ошибок контрольного канала и ошибки средств контроля устройства соответственно, выход микроопераций регистра контрольных микрокоманд соединен с третьим информационным ,входом коммутатора и первым входом второй схемы сравнения, выход которой соединен с вторым входом пятого элемента И, выход второго блока элементов И соединен с четвертым информационным входом коммутатора, выход первой метки регистра контрольных микрокоманд соединен с первым управляющим входом коммутатора, первым входом шестого элемента И, входом синхронизации буферного регистра и вторым входом первого блока элементов И, выход которого соединен с информационныи входом счетчика, выход второй метки регистра контрольных микрокоманд соединен с вторым управляющим входом коммутатора, вторымивходами пятого элемента И и второгоэлемента ИЛИ и с входом синхронизации триггера хранения логическогоусловия, единичный вьмод которогосоединен с первым входом сумматорапо модулю два, выход требуемого значения логического условия регистраконтрольных микрокоманд соединен свторым входом сумматора по модулюдва, выход которого соединен с вторымвходом шестого элемента И, выход кода логических условий регистра контрольных микрокоманд и вход логических условий устройства соединенысоответственно с управляющим и информационным выходом мультиплексора,вьмод которого соединен с информационным входом триггера хранения ло"гического условия, выход адреса регистра контрольных микрокоманд соеди"нен с информационным входом буферногОрегистра, выход которого соединен свторым входом второй схемы сравнения. 2. Устройство по п. 1,.о т л ич а ю щ е с я тем, что блок анализа содержит пять элементов И, три элемента ИЛИ и элемент ИЛИ-НЕ, причем первый вход блока соединен с первыми входами первого, второго.,элементов И и первого элемента ИЛИ, второй вхОд блока соединен с первыми входами третьего, четвертого элементов И и элемента ИЛИ-НЕ, третий вход блока соединен с вторыми входами первого, третьего элементов И, с первым и вторым входом пятого элемента И, выход которого соединен с вторыми входами второго, четвертого элементов И и первого элемента ИЛИ, выходы первого, второго, третьего и четвертого ф элементов И соединены соответственно с первьвчи входами второго элемента ИЛИ, третьего элемента ИЛИ, вторыми входами второго и третьего элементов ИЛИ, выходы первого, второго, третьего элементов ИЛИ и выход элемента ИЛИ-НЕ соединены соответственно с вторым входом элемента ИЛИ-НЕ, с выходом ошибки контрольного канала блока, выходом ошибки аппаратуры контроля блока и с выходом ошибки рабочего канала блока.1100625 , 2Изобретение относится к автоматике . мирователя адреса микрокоманд соедии вычислительной технике и может нен с первым выходом регистра микро- быть использов:но при построении са- команд, третий выход которого соеднмопроверяемых микропрограммных уп- нен с вторым входом формирователя равляющнх устройств с высокой досто- адреса микрокоманд, выход которого верностью функционирования. соединен с вторым входом регистраИзвестно микропроГраммное устрой-: адреса микрокоманд, третий вход форство управления с самоконтролем, со- . мироваеля адреса микрокоманд соедидержащее регистр команд, регистр ад-нен с вторым входом устройства и ресов микрокоманд, дешифратор адресов 1 О первым входом формирователя .адреса микрокоманд, сч:тчик микрошагов,. контрольных микрокоманд, второй вход блок памяти микрокоманд, блок памяти которого подключен ко второму выхоконтрольных микрокоманд, регистр ду регистра контрольных микрокоманд, контрольных микрокоманд, блок форми- четвертый выход которого через элерования ошибки,. блок разрешения конт мент .НЕ подключен ко входу первого роля 13. элемента И управляемого третьимНедостатком данного устройства яв- входом устройства, и к,первому входу ляются низкие функциональные возмож- второго элемента И, второй вход коности, обусловленные невозможностью торого подключен к третьему выходу идентификации сбоя между ветвлением 2 О регистра контрольных микрокоманд и и линией последовательностью микро- первому входу третьего элемента И, команд, возможностью использования управляемого четвертым выходом ре микрокоманд с одной и той же операци- гистра контрольных микрокоманд, выход онной частью в качестве первой микро- третьего элемента И подключен к перкоманды только в одной линейной по вому входу счетчика микрошагов, а следовательности требованием, что- выход второго элемента И подключен к бы логические условия не входили в третьему входу формирователя адреса распределение сдвигов ни одной мик- контрольных,микрокоманд выход ко" рокоманды линейной последователь- . ,торого подключен ко второму входу ности, кроме первой. регистра адреса контрольных микрокоНаиболее близким по техническойманд, первый вход которого подключен сущности к изобретению является са- ко второму выходу регистра команд, а моконтролируемое микропрограммное . выход - к первому входу дешифратора устройство управления, содержащееадреса контрольных микрокоманд, а регистр адреса контрольных микроко- второй вход подключен к выходу элеманд, дешифратор (формирователь) ад- мента КЙИ, первый вход которого под 35реса контрольных микрокоманд, первый- ключен к выходу первого элемента И, четвертый элементы И, элемент ИЛИ, , а второй вход подключен к выходу элемент НЕ, формирователь адреса мик- четвертого элемента И, первый вход рокомаид и последовательно соединен- которого соединен с выходом дешифра 40ные блок памяти контрольных микроко- тора микрошагов, а второй вход подмаид, первый выход которого подклю-: ключен ко второму входу дешифраторачен к первому входу блока формирования адреса микрокоманд, третьему входу ошибки (схемы анализа), выод кото- устройства, второму входу счетчика рого является выходом устройства, микрошагов и второму входу первого второй вход подключен к выходу бло- , элемента И и третьему входу блока4ка разрешения контроля, первый вход разрешения контроля 2 1. которого черкез дешифратор микрьшагов , Недостатком указанного устройства подключен к выходу, счетчика микроша-является низкая достоверность Функгов, второй вход блока разрешенияционирования и, как следствие, низкая контроля (группа элементов),подключен надежность, поскольку средства контк первому входу устройства и черезроля в нем не являются самопроверяпоследовательно включенные регистремыми, а их отказ или идентифицикоманд, регистр адресов микрокомаид, .руется как отказ контролируемого дешифратор адресов микрокоманд, блок микропрограммного устройства или припамяти микрокоманд ко входу регистра 55 водит к тому, что действительный от- микрокоманд, второй выход которого каз проверяемой части не обиаруживаподключен к третьему входу блока ется. Так как объем средств контроля формирования ошибки, первый вход Фор-в прототипе составляет 20-257 и на- дежность их элементов сравнима с надежностью элементов рабочего (контролируемого). оборудования, то отсутствие свойств самопроверяемости усредств контроля существенно снижает;достоверность функционирования уст 5ройства в целом.Цель изобретения - повышение надежности устройства.Поставленная цель достигается тем,1что микропрограммное устройство управления, содержащее формировательадреса рабочих микрокоманд, формирователь адреса контрольных микрокоманд,регистр адреса рабочих микрокоманд,75регистра адреса контрольных микрдкоманд, блок памяти рабочих микрокоманд,блок памяти контрольных микрокоманд,регистр рабочих микрокоманд, регистрЗконтрольных микрокоманд, генератортактовых импульсов, блок анализа,счетчик, триггер пуска, первый и второй блоки элементов И, шесть элемен-тов И, первый элемент ИЛИ и элементНЕ, причем вход кода операции устрой"25ства соединен с первыми входами формирователей адреса рабочих и контрольных.микрокоманд соответственно,выходы которых соединены с входамирегистров адреса рабочих и контрольных мнкрокоманд соответственно,ЗОвход логических условий устройствасоединен с вторыми входами формирователей адреса рабочих и контрольных микрокоманд, выходы адреса кодалогических условий микроопераций иметки конца работы регистра рабочих микрокоманд соединены соответственно с третьим и четвертым входамиформирователя адреса рабочих микрокоманд, выходом микроопераций устройства и нулевым выходом триггерапуска, выход которого соединен спервым входом первого элемента И,вход пуска устройства и выход генератора тактовых импульсов соединенысоответственно с единичным входомтриггера пуска и вторым входом первого элемента И, выход которого соединен с первым входом второго. элемента И и входом считывания блока намяти рабочих микрокоманд, выход регистра адреса рабочих микрокомандсоединен с адресным входом блокапамяти рабочих микрокоманд, выходкоторого соединен с информационнымвходом регистра рабочих микрокоманд,выход первого элемента ИЛИ соединенс вторым входом второго элемента И. 625 4выход которого соединен с входом считывания блока памяти контрольных микрокоманд, выход регистра адреса контрольных микрокоманд соединен с адресным входом блока памяти контрольных микрокоманд, выход которого соединен с входом регистра контрольных микрокоманд, выход адреса регистра контрольных микрокоманд соединен с третьим входом формирователя адреса контрольных микрокоманд, выход кода логических условий регистра контрольных микрокоманд соединен с первыми входами первого и второго блоков элементов И, выход второго блока элементов И соединен с четвертым входом формирователя адреса контрольных микрокоманд, выход первой метки регистра контрольных микрокоманд соединен с первым входом третьего элемента И и через элемент НЕ с вторым входом второго блока элементов И, выход третьего элемента И соединен со счетным входом счетчика, инверсные выходы которого соединены с входами четвертого элемента И, выходы пятого и шестого элементов И соединены соответственно с первым и вторым входами блока анализа, первый выход которого является выходом ошибки рабочего канала устройства, дополнительно введены буферный регистр, коммутатор, первая и вторая схемы сравнения, мультиплексор, триггер логического условия, сумматор по модулю два, первый и второй одновибраторы, второй элемент ИЛИ, причем вход пуска устройства соединен с первым входом второго элемента ИЛИ, выход которого через первый одновибратор соединен с первым входом первого элемента ИЛИ, выход четвертого элемента И через второй одновибратор соединен с вторым входом первого элемента ИЛИ, выходы кода логических условий и микроопераций регистра рабочих микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым входами первой схемы сравнения, выход первой схемы, сравнения соединен с третьим входом блока анализа, второй и третий выходы которого соединены с выходами ошибок контрольного канала и ошибки средств контроля устройства соответственно, выход микроопераций регистра контрольных микрокоманд соединен с третьим,5 110062 информационным входом коммутатора и первым входом второй схемы сравнения,выход котс ой соединен с вторым входом пятого элемента И, выход второго блока элементов И соединен с четвертым информационным входом коммутатора, выход первой метки регистра контрольных микрокоманд соединен с первым управляющим входом коммутатора, первым входом элемента И, входом 10 синхронизации буферного регистра и вторым входом первого блока элементов И, выход которого соединен с ин-. формационным входом счетчика, выход второй метки регистра контрольных микрокоманд соединен с вторым управляющим входом коммутатора, вторыми входами пятого элемента И и второго элемента ИЛИ и с входом синхронизации триггера хранения логического условия, единичный выход которого соединен с первым входом сумматора по модулю два,выход требуемого значения логического условия регистра контрольных микрокоманд соединен с вторым 25 входом сумматора по модулю два, выход которого соединен с вторым входом шестого элемента И, выход кода логических условий регистра контрольных микрокоманд и вход логических условий устройства соединены соответственно с управляющим и информационным входами мультиплексора, выход которого соединен с информационным входам триггера хранения логического усло 35 вия, выход адреса регистра контрольных микрокоманд соединен с информационным входом буферного регистра, выход которого .соединен с вторым входом второй схемы сравнения.Кроме того, блок анализа содержит пять элементов И, три элемента ИЛИ и элемент ИЛИ-НЕ, причем первый вход блока соединен с первыми входами первого, второго элементов И и первого элемента ИЛИ, второй вход блока соединен с первыми входами третьего, четвертого элементов И и элемента ИЛИ-НЕ, третий вход блока соединен е вторыми входами первого, третьего50 элементов И, с первым и вторым входом пятого элемента И, выход которого соединен с вторыми входами второго, четвертого элементов И и первого элемента ИЛИ, выходы первого, второго, третьего и четвертого элементов И55 соединены соответственно с первыми входами второго элемента ИЛИ, третьего элемента ИЛИ, вторыми входами 5 6второго и третьего элементов ИЛИ,выходы первого, второго, третьегоэлементов ИЛИ и выход элемента ИЛИ-НЕсоединены соответственно с вторымвходом элемента ИЛИ-НЕ, с выходомошибки контрольногд канала блока,выходом ошибки аппаратуры контроляблока и с выходом ошибки рабочегоканала блока.Сущность изобретения состоит в повышении достоверности функционирования путем обеспечения самопроверяемости встроенных средств контроля.В предлагаемом устройстве парал- .лельно с рабочим каналом (собственноустройством управления) функционируетконтрольный канал и средства анализа.На всех этапах выполнения микропрограммы (начальная микрокоманда линейной последовательности, промежуточнаямикрокоманда линейной последователь"ности, последняя микрокоманда линейной последовательности и ветвление .в микропрограмме) происходит контроль функционирования как рабочего,так и контрольного каналов. При этомреализуются следующие дисциплины контроля,При выполнении начальной микрокоманды линейной последовательностипроисходит сравнение операционнойчасти рабочей микрокоманды, котораяследует первой в линейной последовательности, с операционной частью, соответствующей контрольной микрокоманде, которая формируется параллельно сэтой (рабочей) микрокомандой. Привыполнении промежуточной микрокоманды линейной последовательности (очередной рабочей микрокоманды) происходит вычитание единицы из содержимого счетчика; в котором записанкод длины линейной последовательности. Этот код задается в поле кодалогических условий первой контрольной микрокоманды. В последней микрокоманде линейной последовательности.сравнение кода логического условиярабочей микрокоманды, которая явля"ется последней в линейной последовательности (т.е. микрокоманды ветвления), с кодом логических условийсоответствующей (второй) контрольноймикрокоманды, которая формируетсяпараллельно с этой рабочей микрокомандой. Кроме того, происходит сравнение адресной части первой контрольноймикрокоманды, которая запомииа7 1100 ется в специальном буферном регистре, с кодом, записанным в поле микроопераций второй контрольной микрокоманды, При выполнении начальной микрокоманды следующей линейной последователь 5 ности (первая микрокоманда после ветвления) происходит сравнение операционной части рабочей микрокоманды, которая следует первой в линейной последовательности, с операционной О частью соответствующей (первой) контрольной микрокомандш,формируемой параллельно с этой (рабочей) микро- командой. Кроме того, осуществляется сравнение истйнного значения логического условия, по которому произошло ветвление, с значением логического условия, записанным в поле специальной метки второй контрольнойФмикрокоманды. 20Выполнение указанных дисциплин контроля позволяет проверять правильность реализации функции переходов рабочего канала, правильность реализации функции выходов рабочего 25 канала, правильность реализации функции переходов контрольного канала, правильность реализации Функцги выходов контрольного канала.На фиг. 1 приведена функциональная схема микропрограммного устройства управления, на фиг. 2 - функциональная схема коммутаторами на Фиг. 3 - функциональная схема формирователя адреса, на фиг, 4 - функциональная схема блока анализа, на фиг. 5 - схема алгоритма рабочей (а) и контрольной (б) микропрограммы.Функциональная схема коммутатора (фиг. 1) содержит формирователь40 адреса рабочей микрокоманды, регистр 2 адреса рабочих микрокоманд, блок, 3 памяти рабочих микрокоманд, регистр 4 рабочих микрокоманд, имеющий поле 4.1 косвенного адреса, поле 4,.2 кода45 логических условий, поле 4.3 микро- операций, коммутатор 5, первую схему б сравненияблок 7 анализа, формирователь 8 адреса контрольных микрокоманд, регистр 9 адреса контрольных микрокоманд, блок 10 памяти контрольных микрокоманд, регистр 11 контрольных микрокоманд, содержащий поле 11.1 косвенного адреса, поле 11.2 логичес- ких условий (длины линейной последовательности), поле 11.3 микроопераций (контрольного адреса), поле 11.4 первой метки, поле 115 второй мет" ки, поле 11.6 требуемого значения 625 8логических условий, первый блок 12элементов И, элемент НЕ 13, второйблок 14 элементов И, третий элементИ 15, счетчик 16, четвертый элементИ 17, буферный регистр 8, вторуюсхему сравнения 19, седьмой элементИ 20, второй элемент ИЛИ 21, первыйодновибратор 22, второй одновибратор23, первый элемент ИЛИ,24, мультиплексор 25, триггер 26 хранения логи"ческого условия, сумматор 27 по модулю 2, шестой элемент И 28, триггер29 пуска, генератор 30 импульсов,первый элемент И 31, второй элементИ 32, вход ЗЗ пучка устройства,вход 34 кода устройства, вход 35 логических условий устройства, выход36 метки конца работы, выход 37микроопераций устройства, третий 38,четвертый 39 входы формирователя адреса рабочих микрокоманд, третий 40,четвертый 41 вхоДы формирователяадреса контрольных микрокоманд, первый 42, второй 43, третий 44, четвертый 45 информационные входы, первый 46, второй 47 управляющие входы,первый 48, второй 49 выходы коммутатора 5, третий 50, первый 51, второй52 входы, первый 53, второй 54, .третий 55 выходы блока 7 анализа, являющиеся выходом устройства соответ,ственно,Коммутатор 5 (фиг. 2) содержиттретий 56., четвертый 57, первый 58,второй 59 блоки элементов И, первый60, второй 61 блоки элементов ИЛИ.Формирователь адреса 1 (8) рабочих(контрольных) микрокоманд (фиг. 3)содержит мультиплексор 62, элементИЛИ 63, блок элементов ИЛИ 64,Блок 7 анализа (фиг. 4) содержитпервый 65 и второй 66 элементы И,элемент 67 НЕ, третий 68 и четвертной69 элементы И, первый 70, второй 71,третий 72 элементы ИЛИ, элемент73 ИЛИ-НЕ.На фиг. 5 использованы следующиеобозначения: А;, А;+, А 1 - адресные части первых рабочих микрокоманд 1, 1+1, +2-линейных последовательностей микрокоманд, А 1, А"1 МА 1 р 2 - адресные части первых конт- .рольных микрокоманд, соответствующих+1, +2-й последовательностям,А 1 А 1;11 А 1,;+2- адресные части последних рабочих микрокоманд 1, +1,1+2-й последовательностей, А 2, А21+1А 12- адресные части вторых конт- .рольных микрокоманд, соответствующих+1, +2-й.последовательностям,Х Х;+, Х;+ - коды логическихусловий 1, 4+1, 1+2-.й последовательностей, МО 1 (МО 11), МО 1+1(МО 11+) фМО, (МО,. )- мнкрооперационные час-.ти первых рабочих (контрольных) микрокоманд 1, +1, (1+2)-й последовательностей, МО 1, МО 1,441 ф МО 11+микрооперационные части последнихрабочих микрокоманд 1, 1+1, 1+2-й 1 опоследовательностей, М;, й+ М+ -число рабочих микрокоманд в , 1+1,+2.-й последовательностях, А, АУ,МО,ф 1,+2,3 - поля адреса кода логических условий, микроопераций, . 15первой, второй и третьей меток (вполе третЬей метки записано значениетребуемого логического условия) соответственно,Технические средства устройства. 2 рмогут быть разделены на четыре части:рабочий и контрольный каналы, аппаратура контроля и средства синхронизации.Рабочий канал предназначен для рхранения микрокоманд и считывания ихв соответствии с очередным адресом.:Канал состоит из ФЬрмирователя адреса рабочих микрокоманд 1, предназначенного для формирования адреса следующей микрокоманды в зависимости откода косвенного адреса и кода логического условия. формирователи адреса1 и 8 вьпюлнены по идентичной схеме.,Мультиплексор 62 осуществляет выделение проверяемого логического условия и реализует функциюМ=л. условий,а,а ,а, - значения разрядовкода логическихусловий, поступающего на управляющие входы мульти-, .плексора 62.Элемент 63 ИЛИ предназначен длямодификации младшего разряда адресазначением проверяемого логического50условия. Блок элементов 64 ИЛИ пред":,назначен для формирования адреса по .коду операцииили коду, поступающему со входа 38: регистра адреса рабочих микрокоманд 2, в который записывается и хранится адрес последую:щей микрокоманды рабочей микропрограммы, блока памяти 5, предназначен-. 5 10ного для хранения рабочих микрокоманд, регистра мнкрокоманд 4, в который считываются и хранятся очередные рабочие микрокоманды, поступающие из блока памяти 3.Контрольный канал предназначен для хранения их в соответствии с очередным адресом. Этот канал состойт, из Формирователя адреса контрольных микрокоманд 8, регистра адреса контрольных микрокоманд 9, блока памяти контрольных микрокоманд 10, регистра контрольных микрокоманд 11, Контрольный канал отличается от рабочего форматом хранимых микрокоманд, В регистр 11 дополнительно введены поле 11.4 первой метки, предназначенное для выдачи сигнала управления записью кода длины линейной последовательности в счетчик 16 и разрешения считывания сигнала микроопераций с выхода регистра 11 контрольных микрокоманд на коммутатор 5, а также записью адресной. части первой контрольной микрокоманды в буферный регистр 18, поле 11.5 второй метки, предназначенное для выдачи сигнала разрешения считывания;логических условий с выхода регистра. 11 контрольных микро- команд на коммутатор 5 и записи в триггер 26 хранения логического услоция действительного значения логического условия с вьиода мультиплексора 25, поле 11,6 требуемого значения логического условия.Аппаратура контроля предназначена для анализа состояний рабочего и контрольного каналов и Формирования соответствующих сигналов на выходах 53-55 и состоит нз коммутатора 5, предназначенного для параллельной выдачи на схему сравнения 6 кодов микро- операций или логических условий рабочей и контрольной микрокоманц.Работа коммутатора заключается в следующем, На второй информационный вход 43 поступают сигналы микроопераций рабочей микрокоманды, на третий информационный вход 44 - сигналы микроопераций контрольной микрокоман- ды. По сигналу с выхода поля 11.4 1 .(метки 1), поступающему на второй управляющий вход 46, сигналы микрооперацнй рабочей микрокоманды через блоки элементов И 58 и ИЛИ 60 поступают на первый выход 48, а сигналы -микроопераций контрольной микрокоманды через блоки элементов И 59 и ИЛИ 61 на второй выход 49. На пер11 11006 вый информационный вход 42 поступает код логических условий рабочей микро- команды. На четвертый информационный вход 45 поступает код логических условий контрольной микрокоманды. По сигналу с выхода поля 11.5 (метки 2), поступающему на второй управляющий вход 47, код логических условий рабочей микрокоманды через блоки элементов И 56 и ИЛИ 60 поступают на первый выход 48, а код логических условий контрольной микрокоманды через блоки элементов И 57 и ИЛИ 61 поступает на второй выход 49, схемы сравнения 6, на которых происходит сравнение кодов микроопераций или логических условий, которые поступают параллельно с коммутатора 5 и выдачи результата сравнения на блок 7 анализа, блок 7 анализа, предназначенный для выдачи сигнала отказа рабочего, контрольного каналов или аппаратуры контроля.Работа блока 7 анализа заключается в следующем. На третий вход 50 поступает сигнал с выхода схемы сравнения 6, на первый вход 51 - сигнал с выхода схемы сравнения 1,9, на второй вход 52 - сигнал с выхода элемента 27 сумма по модулю два. На выходах блока 7 анализа формируются следующие сигналы: на первом выходе 531 , на втором выходе. 54 1 на треАем выходе 55-1 1 где Гро - сигнал ошибкиЮМрабочего канала устройства, 7 М 1, -35 сигнал ошибки контрольного канала устройства, Е д 1,- сигнал ошибки аппаратуры контроля.Работа блока 7 описывается следующей таблицейв таблице приняты следующие обозначения: У- сигнал на выходе 50, У 2 - сигнал на входе 51, Ч - сигнал на входе 52 соответствияНо йаива 40 0 0 0 0 00 0 1 0 00 1 0 0 0 10 1 11 0 0 1 0 01 0. 1 0 1 01 1 1л15элемента 12 И, предназначенного для управления записью кода длины линейной последовательности микрокоманд 2512в счетчик 16, элементов 13 НЕ и 14 И, предназначенных для управления передачей кода логического условия с выхода поля 11,2 регистра микрокоманд 11 на формирователь адреса контрольных микрокоманд и коммутатор 5, элемента 15 И, предназначенного для управления подачей импульсов на счетчик 16, счетчика 16, предназначенного для подсчета фактически выполненного числа микрокоманд линейной последовательности, элемента 17 И, предназначенного для выдачи сигнала, свидетельствующего о нулевом состоянии счетчика 16, на одновибратор 23, одновибраторов 22 и 23, предназначенных для формирования импульсов считывания контрольных микрокоманд,. буферного регистра 18, предназначенного для хранения адресной части первой микрокоманды, схемы сравнения 19., предназначенной для сравнения адресной части первой микрокоманды, записанной в буферном регистре 18, с ,контрольным адресом, записанным в поле 11,3 второй контрольной микрокоманды, элемента И 20, предназначенного для управления поступлением сигнала с выхода схемы сравнения 19 на вход 51 блока 7 анализа,мультиплексора 25, предназначенного для управления выдачей значения проверяемого логического условия. Мультиплексор 25 реализует логическую функцию Ю, аналогичную функции, реализуемой мультиплексором 62, триггера 26 хранения логического условия, в который записывается действительное значение логического условия, элемента 27 суммы по модулю два, предназначенногс для суммирования по модулю два требуемого и действительного значения логического условия (проверка правильности выполнения ветвления), элемента 28 И, который управляет выдачей сигнала с выхода элемента 27 сумма по модулю два (результата сравнения) действительного и требуемого значений логических условий на вход 52 схемы анализа 7.Средства синхронизации, которые служат для синхронизации работы устройства, состоят из триггера пуска 29, предназначенного для запуска устройства по сигналу "Пуск", поступающему на вход 33, и для остановки устройства по сигналу "Стоп", который.содержится в последней микрокоманде микропрограммы и поступает на-вход триггера пуска 29 с выхода36 регистра 4, генератора импульсов30, который вырабатывает синхроим-пульсы, элементов 31 И и 32 И, предназначенных для управления прохожде 5нием синхроимпульсов в рабочий и контрольный каналы.Устройство работает следующим об"разом.,В исходном состоянии все элементы 10памяти установлены в нуль. С входа33 сигнал пуска поступает на вход Втриггера пуска "29 и через элементИЛИ 21 на одновибратор 22. Сигналпуска устанавливает триггер пуска29 в единичное состояние. Сигнал свыхода триггера пуска 29 поступаетна элемент И 31, на второй вход ко-торого поступает сигнал с выхода ге,нератора импульсов 30. Через элементИ 31,открытый сигналом с выхода триггера пуска 29, синхроимпульс поступа-ет на вход регистра адреса микрокоманд 25.По сигналу "Пуск" триггер 29 ус- р 5танавливается в единичное состояние,а одновибратор 22 формирует импульс,который через элемент ИЛИ 24 поступает на вход элемента И 32. На второй вход этого элемента поступаетсинхроимпульс с выхода элемента И 31.Синхроимпульс проходит через элементИ 32 на вход считывания блока памяти контрольных микрокоманд 10. Одновременно по первому синхроимпульсу с выхода элемента И 31, поступа 35ющему на вход блока 3 памяти рабочихмикрокоманд, через регистр 2 адресамикрокоманд и блок памяти 3 в регистрмикрокоманд 4 считывается первая рабочая микрокьманда.С выхода поля 4.1 через формирователь адреса 1 в регистр адреса 2записывается адрес следующей микрокоманды. С выхода поля 4,3 сигналымикроопераций поступают на вход 37устройстваи на коммутатор 5, Посинхроимпульсу с выхода элемента32 И в регистр 11 .считывается перваяконтрольная микрокоманда. С выходаполя 11.1 адрес первой микрокоманды50поступает на вход формирователя 8, вкотором формируется адрес следующей.(второй) контрольной микрокомандь 1, атакже заносится в буферный регистр18. С выхода поля 11.2 через элемент 55И 12, открытый сигнал с выхода поля11,4, в счетчик 16 записывается коддлины линейной последовательности 5 14микрокоманд равный Н, где Й - число микрокоманд в линейной последовательности.С выхода поля 11.3 код микроопераций поступает на коммутатор 5. С выхода поля первой метки 11,4 сигнал поступает на вход буферного регистра 18 и разрешает запись в него адреса первой контрольной микрокоманды, Этот же сигнал поступает на коммутатор 5 и разрешает параллельное поступление микроопераций рабочей и контрольной микрокоманд на схему сравнения 6, где происходит сравнение этих кодов микроопераций, результат которого поступает на блок 7 анализа.По каждому синхроимпульсу происходит считывание следующих рабочих микрокоманд аналогично описанному выше, а от содержимого счетчика 16 вычитается единица, Считывание контрольных микрокоманд блокируется элементом 32.И. При считывании (М)-й рабочей микрокоманды счетчик 16 устанавливается в нуль. Сигнал с выхода элемента И 17 (при обнулении счетчика 16) поступает на одновибратор 23, который формирует импульс, открывающий элемент И 32 и разрешающий считывание второй контрольной микрокоманды. По адресу, записанному в регистр 9, из блока памяти микро- команд 10 считывается вторая контрольная микрокоманда (микрокоманда ветвления).С выхода поля 11.1 адрес микрокоманды поступает на вход формирователя адреса 8, в котором формируется адрес следующей микрокоманды (первой контрольной мнкрокоманды). С выхода поля 11.2 код логических условий через блок элементов И 14, открытый сигналом с элемента НЕ 13, поступает на формирователь адреса контрольных микрокоманд 8, коммутатор 5, а также на мультиплексор 25. Сигнал с выхода мультиплексора 25 поступает на Р"вход триггера хранения логического условия 26. По сигналу, поступающему с выхода поля 11.5 на С-вход тригге- . ра 26, действительное значение логического условия запоминаетсяв триг-гере 26.С выхода поля 11.3 контрольный адрес поступает на схему сравнения 19, где происхоДит его сравнение с.адресом первой микрокоманды, записанным ранее в буферный регистр 18.

СмотретьЗаявка

3549949, 08.02.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ЗАНЬКО АЛЕКСАНДР ИВАНОВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 30.06.1984

Код ссылки

<a href="https://patents.su/12-1100625-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для контроля параллельного кода на четность

Случайный патент: Корригирующее приспособление при вальгусном отклонении первого пальца стопы