Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

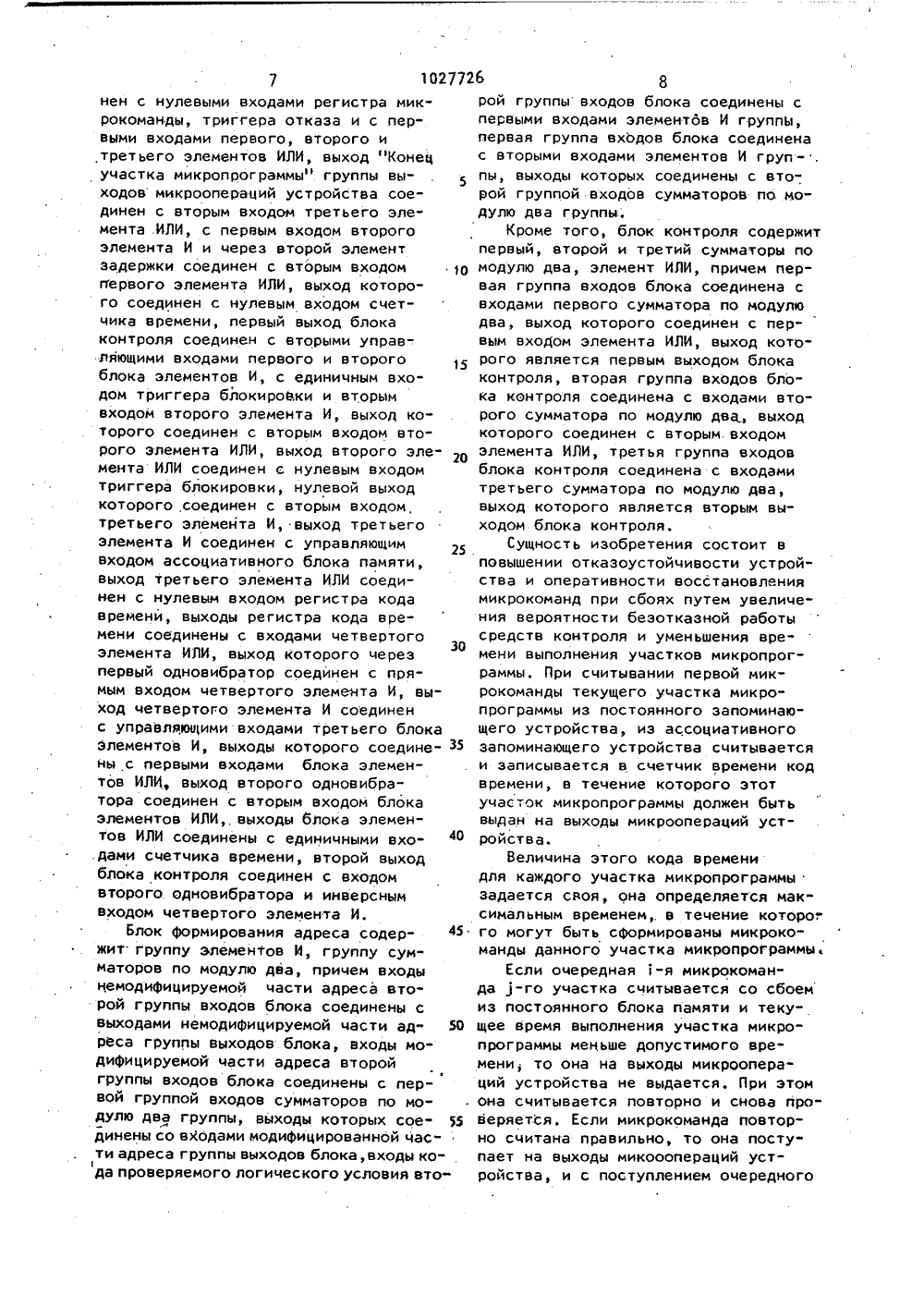

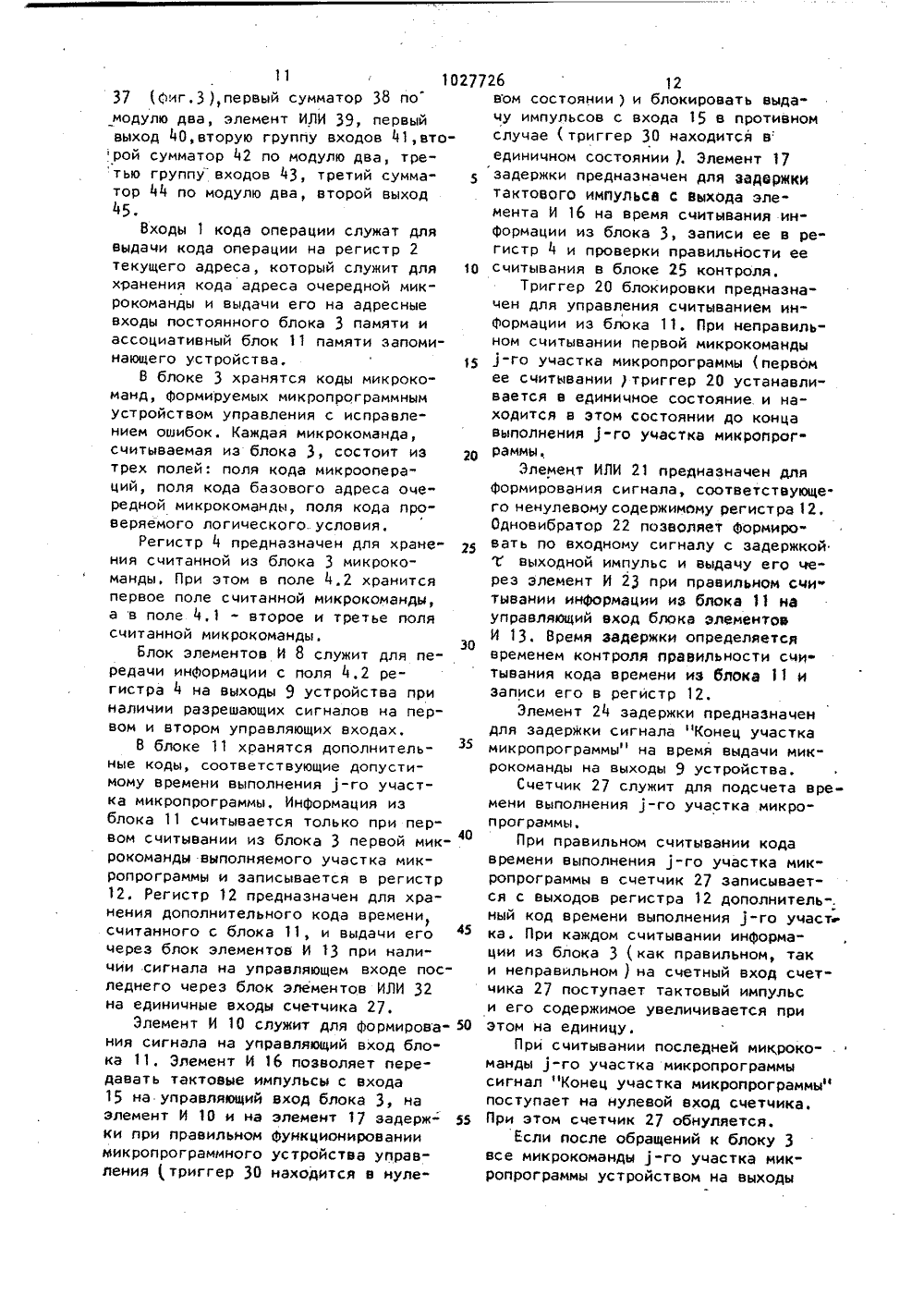

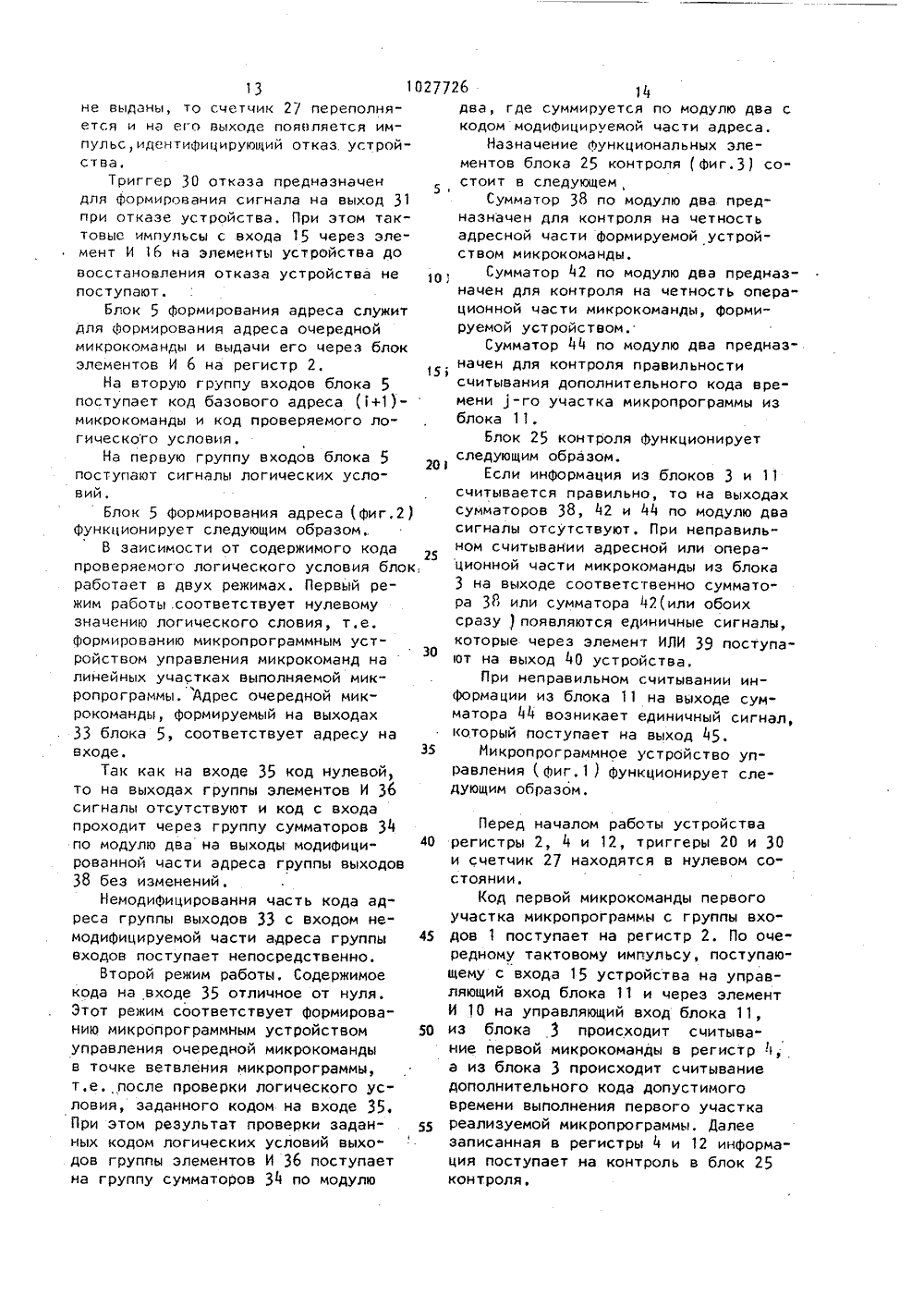

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИН ЯО 10277 А С 06 Г 9/22; С 11/О ОСУДАРСТ 8 ЕННЫЙ НО О ДЕЛАМ ИЗОБРЕТЕН ТЕТ СССРИ ОТНРЫТИИ р РГ(56) 1, Авторское свидетельство СССРУ 470806, кл. С 06 Р 9/16, 1975.2. Авторское свидетельство СССРЮ 741267, кл. С 06 Г 9/16,а 06 Г 11/00, 1980 (прототип).(54)(57) 1. МИКРОПРОГРАИИНОЕ УСТРОИСТВО УПРАВЛЕНИЯ, содержащее постоянный и ассоциативный блоки памяти,регистр текущего адреса, регистрмикрокоманды, регистр кода времени,счетчик времени, триггер отказа,блок контроля, первый, второй и третий блоки элементов И, первый и втоРой элементы И, блок формированияадреса, причем входы кода операцииустройства соединены с первой группой входов регистра текущего адреса, входы сигналов проверяемых логических условий соединены с .первойгруппой входов блока формированияадреса, выходы которого соединеныс информационными входами первогоблока элементов И, выходы первогоблока элементов И соединены с второй группой входов регистра текущего адреса, выходы которого соединенцс информационными входами ассоциативного блока памяти и с адресными вхо-дами постоянного блока памяти, выходы постоянного блока памяти соединены с информационными входами регистра микрокоманды, выходы первого поля которого соединены с второй группой входов блока формирова.ния адреса и с первой группой вхо" дов блока контроля, выходы второго поля регистра микрокоманды соединены с второй группой входов блока контроля и с информационными входами второго блока элементов И, выходы второго блока элементов И явля" ются выходами микроопераций устройства, выходц ассоциативного блока памяти соединены с информационными входами регистра кода времени, выходы которого соединены с третьей группой входов блока контроля и с информационными входами третьего блока элементов И, счетный вход счетчика времени соединен с первымие управляющими входами первого и вто" рого блоков элементов И, единичный выход триггера отказа соединен с вы" ходом сигнала отказа устройства, а нулевой выход триггера отказа сое" динен с первым входом первого элемен та И, второй вход которого соединен с входом тактовых импульсов устройства, выход первого элемента И соединен с управляющим входом постоянного блока памяти, о т л ич а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены первый и второй элементы задержки, первый, второй, третий и четвертый элементы ИЛИ, пер" вый и второй одновибраторы, третий и четвертый элементы И, триггер блоки- ровки и блок элементов ИЛИ, причем выход первого элемента И соединен с первым входом третьего элемента И и через первый элемент задержки соединен с первыми управляющими входами первого и второго блоков элементов И и со счетным входом счетчика вре1027726 17команды записывается с выходов блока формирования адреса 5 в регистр2, Далее по описанному выше алгоритму осуществляется формирование очередных микрокоманд участка.Если же повторно микрокомандасчитывается со сбоем из блока 3, то,сигнал на первом выходе блока 25 контроля не исчезает и устройство функ" 1 Оционирует далее аналогично функционированию после первого считываниясо сбоем данной микрокоманды. Если при повторных считываниях первоймикрокоманды сбой не исчезает за время, определяемое допустимым временемвыполнения данного участка, то счет-.чик 27 переполняется и на его выходе "появляется импульс, Этот импульс устанавливает триггер 30 в единичноесостояние. При этом на выход 31 устройства поступает. сигнал возникнове"ния отказа устройства и блокируетсяпрохождение тактовых импульсов черезэлемент И 16,25Если сбой произошел при считывании -й микрокоманды 1-го участкамикропрограммы, то устройство функционирует аналогично описанному выше алгоритму, Если после повторныхсчитываний Р-й микрокоманды 1-гоучастка микропрограммы сбой не исчезает, то фиксируется отказ устройства,Если при формировании всех микрокоманд 1-го участка микропрограммы общее время выполнения участкаменьше, чем допустимое время, то отказ устройства не фиксируется и онопереходит к формированию микрокоманд(1+1)-го участка микропрограммы.Функционирование устройства втретьем режиме,18Если при считывании первой микрокоманды 1-го участка микропрограммы информация с блока 11 считывается со сбоем, то на втором выходе блока 25 контроля формируется сигнал,Этот сигнал закрывает по инверсномувходу элемент И 23 и запускает одновибратор 28. Импульс с выхода одновибратора 28 через соответствующиеэлементы ИЛИ блока элементов ИЛИ 32устанавливает в счетчике 27 дополни"тельный код минимально допустимоговремени выполнения участка микропрограммы.Далее устройство функционируетаналогично первого режиму работы.функционирование устройства вчетвертом режиме.При считывании первой микрокоманды -го участка микропрограммыи записи ее в регистр 4, а когдадопустимого времени в регистр 12 напервом и втором выходах блока контроля 25 появляются сигналы,При этом в счетчик 27, по описанному для третьего режима работыалгоритму, записывается дополнительный код числа допустимого времени,Далее устройство функционируетаналогично второму режиму работы,После восстановления отказа устройства на вход 29 подается сигналначальной установки, При этом регистры 4 и 12, триггеры 20 и 30,и счетчик 27 устанавпиваются в нулевое состояние. Данное устройствофункционирует аналогично описанномувыше алгоритму.Расчеты показывают, что изобретение обеспечивает повышение надежности ( почти в два раза ) и оперативность восстановления1027726 Составитель И.Сигало хред С.Мигунова Ко Редактор Н.Гришанова Бутяаказ 4742/54 Тираж 706 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д. 4/5 тФилиал ППП "Патент", г, Ужгород, ул, Проектная,27726 10 мени, выход которого соединен с единичным входом триггера отказа, вход установки нацального состояния устройства соединен с нулевыми входами регистра микрокоманды, триггера отказа и с первыми входами первого, второго и третьего элементов ИЛИ, выход "Конец участка микропрограммы" группы выходов микроопераций устройства соединен с вторым входом третьего элемента ИЛИ, с первым входом второго элемента И и через второй элемент задержки соединен с вторым входом первого элемента ИЛИ, выход которого соединен с нулевым входом сцетцика времени, первый выход блока контроля соединен с вторыми управляющими входами первого и второго блоков элементов И, с единичным входом триггера блокировки и вторым входом второго элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с нулевым входом триггера блокировки, нулевой выход которого соединен с вторым входом третьего элемента И, выход третьего элемента И соединен с управляющим входом ассоциативного блока памяти, выход третьего элемента ИЛИ соединен с нулевым входом регистра кода времени, выходы регистра кода времени соединены с входами четвертого элемента ИЛИ, выход которого через первый одновибратор соединен с прямым входом чет" вертого элемента И, выход четвертого элемента И соединен с управляющими входами третьего блока элементов И, выходы которого соединены с первыми входами блока элементов ИЛИ, выход второго одновибратора соединен с вторым входом блока элементов ИЛИ, выходы блока элементов ИЛИ соединены с единичным входами счетчика времени, второй выход блока контроля соединен с входом второго одновибратора и инверсным входом четвертого элемента И. 2. Устройство по и.1, о т л и " ч а ю щ е е с я тем, что блок формирования адреса содержит группу элементов И и группу сумматоров по модулю два, причем входы немодифицируемой цасти адреса второй группы входов блока соединены с выходами немодифицируемой части адресагруйпы выходов блока, входы модифицируемой части адреса второй группы входов блока соединены с первойгруппой входов сумматоров по модулю два группы, выходы которых соединены с входами модифицированной части адреса группы входов блока, входы кода проверяемого логического условия второй грУппы входов блока соединены с первыми входами элементовИ группы, первая группа входов блока соединена с вторыми входами элементов И группы, выходы которых соединены с второй группой входов сумматоров по модулю два группы. 3, Устройство по п.1, о т л иц а ю щ е е с я тем, что блок контроля содержит первый, второй и третий сумматора по модулю два и элементИЛИ,причем первая группа входов блока соединена с входами первого сумматора по модулю два, выход которого соединен с первым входомэлемента ИЛИ, выход которого является первым выходом блока контроля, вторая группа входов блокаконтроля соединена с входами второго сумматора по модулю два, выходкоторого соединен с вторым входомэлемента ИЛИ, третья группа выходовблока контроля соединена с входамитретьего сумматора по модулю. два,выход которого является вторымвыходом блока контроля, 1Изобретение относится к вычислительной технике и может быть использовано при проектировании микропрограммных управляющих устройств электронных вычислительных машин. 2Известно микропрограммное устройство управления, содержащее запоминающие устройства, регистры адресов и микрокоманды, счетчик, элементы И, а также блок контроля 1.1 .264первого элемента И, второй вход которого соединен с входом тактовых импульсов устройства,. а выход .соединен с управляющим входом постоянного запоминающего устройства).Недостатками данного устройства являются низкие отказоустоичиеость, оперативность восстановления сбоев и как следствие, низкая надежность.Низкая отказоустойчивость функционирования устройства обусловлена частым обращением к ассоциативному блоку памяти в процессе его функционирования.В случае возникновения сбоя при считывании очередной микрокоманды из постоянного блока памяти, в устройстве - прототипе происходит повтор ное считывание кода времени из ассо- циативного блока памяти по коду ад" реса первой микракоманды. реализуемого участка микропрограммы. Если .сбой произошел при выполнейии -й микро" команды выполняемого участка микро" программы, то обращение к ассоциативному блоку памяти будет осуществляться по адресу первой микрокоманды этого участка микропрограммы до момен" та устранения сбоя. Если сбой не исчезнет ( т.е наступил отказ устройства , то обращение к ассоциативному блоку памятй будет осущест" вляться е течение всего допустимого, времени, код которого записан в счетчик времени. Вероятность еоз" никновения сбоя при считывании информации из ассоциативного блока памяти с увеличением числа обращений к нему увеличивается, Число, искажений считываемого из ассоциативного блока памяти кода допустимого времени еы" полнения участка микропрограммы, не- обнаруживаемых блоком контроля, при этом возрастает. Возможны два вида необнаруживаемых искажений кода до" пустимого времени выполнения: искаженное значение кода допустимого времени выполнения больше допустимого значения; искаженное значение кода допустимого времени выполнения меньше допустимого значения.При первом виде искажения отказ микропрограммного устройства управления Фиксируется .с задержкой. При этом время исправного действия устройства-прототипа уменьшается.При втором виде искажений отказ устройства - прототипа может быть сформирован раньше, чем окончится 3 30277Недостатком указанных устройствявляется низкая отказоустойчивость,обусловленная тем, что число повторовреализации соответствующих участковмикропрограммы в случае сбоя фиксировано. Это обстоятельство не позволяет гибко использовать временнуюизбыточность, устройства.Наиболее близким по техническойсущности и достигаемому эффекту кЮ . предлагаемому является микропрог.раммное устройство управления, содер.жащее постоянный и ассоциативный запоминающие блоки, регистр текуще.Го адреса, регистр микрокоманды, регистр кода времени, счетчик времени, триггер отказа, блок контроля,первый, второй и третий блоки элементов И, первый и второй элементыИ, блок Формирования адреса причем входы кода операции устройствасоединены с первой группой входоврегистра:текущего адреса, входы сигналов проверяемых логических усло.вий соединены с первой группой вхо,дов блока Формирования адреса, вы"ходы. которого соединены с информа.ционными входами первого блока элементов И, выходы которых соединены.со второй группой входов регистратекущего адреса, .выходы которого30соединены с .адресными входами ассо-:.циативного блока памяти и ц адрес. ными входами постоянного блока па"мяти, выходы которого соединены синфориацйоннымй.,входами регистра иикрокоманды, выходы первого поля которогосоединейы с второй группой..входов блока формировайия .адреса ис первой группой входов блока контроля, .выходы .второго поля - регист- ф : ра микрокоманды соединены с второйгруппой аходов блока контроля и синформационными еходамй второгоблока элементов И, выходы которых являются выходами микроопераций уст" 45.ройства, выходы ассоциативного блоке памяти соединены с информационныии:входами регистра кода времени, вы"ходы которого соединены с. третьейгруппой емодое блока контроля и с 50информационными входами третьегоблока элементов И, счетный вход счетчика времени соединен с первыми управляющими входами первого и второгоблоков элементов И, единичный выход 55триггера отказа соединен с выходом . сигнала отказа устройства, а нулевой выход соединен с первым входоммикрокоманды сравнимо с минимальным числом тактов работы устройствапо формированию микрокоманд -гоучастка микропрограммы, Это обуславливает низкую оперативность восстановления сбоев,Таким образом, указанные недостатки снижают надежность устрой"стеа и оперативность восстановления микрокоманд при сбоях.Цель изобретения - повышение надежности микропрограммного устройства управления,Поставленная цель достигаетсятем, что е микропрограммное устройство управления, содержащее постоянный и ассоциативный блоки памяти,регистр текущего адреса, регистрмикрокоманды, регистр кода времени,счетчик времени, триггер отказа,блок контроля, первый, второй и третий блоки элементов И, первый ивторой элементы И, блок формирования адреса, причем входы кода операции устройства соединены с первойгруппой входов регистра текущего 35 40 время выполнения участка микропро" граммы, в то время как для восстановления сбоев микрокоманд и завершения выполнения участка микропрограмм можно былобы использовать дополнительные такты работы устройства.Следовательно, надежность известного микропрограммного устройства управления является низкой из-за большого числа обращений к ассоциа тивному блоку памятипри каждом считывании микрокоманд со сбоем из постоянного блока памяти и при считывании первой микрокоманды каждого участка микропрограммы).15Кроме того, в устройстве-прототипе с возникновением сбоя при считывании и-й микрокоманды-го участка микропрограммы осуществляется повторное выполнение "го участка 20 микропрограммы, начиная с первой микрокоманды. При этом вероятность возникновения сбоев в работе устройства увеличивается, что также снижает отказоустойчивость устройства-про- д 5 тотипа.Так как при восстановлении считанной со сбоем и-й микрокоманды в устройстве-прототипе осуществляется повторное считывание микрокоманд-го участка микропрограммы, то число тактов работы устройства по восстановлению считанной со сбоем адреса, входы сигналов проверяемыхлогических условий соединены с первой группой входов блока формирования адреса, выходы которого соединены с информационными входами первого блока элементов И, выходы первого блока элементов И соединены свторой группой входов регистра теку"щего адреса, выходы которого соединены с информационными входами ассоциативного блока памяти и с адресными входами постоянного блока памяти,выходы постоянного блока памяти соединены с информационными входами регистра микрокоманды, выходы первогополя которого соединены с второйгруппой входов блока формированияадреса и с первой группой входовблока контроля, выходы второго полярегистра микрокоманды соединены с второй группой входов блока контроля ис информационными входами второгоблока элементов И, выходы второгоблока элементов И являются выходамимикроопераций устройства, выходыассоциативного блока памяти соединены с информационными входами регистра кода времени, выходы которогосоединены с третьей группой входовблока контроля и с информационнымивходами третьего блока элементов И,счетный вход счетчика времени соединен с первыми управляющими входамипервого и второго блоков элементов И,единичный выход триггера отказасоединен с выходом сигнала отказаустройства, а нулевой выход триггера отказа соединен с первым входом первого элемента И, второйвход которого соединен с входомтактовых импульсов устройства, выход первого элемента И соединенс управляющим входом постоянногоблока памяти, введены первый и второй элементы задержки, первый, второй, третий и четвертый элементыИЛИ, первый и второй одновйбраторы,третий и четвертый элементы И,триггер блокировки, блок элементовИЛИ, причем выход первого элементаИ соединен с первым входом третьего.элемента И и через первый элементзадержки соединен с первыми управляющими входами первого и второгоблоков элементов И и со счетнымвходом счетчика времени, выход которого соединен с единичным входомтриггера отказа, вход установки начального состояния устройства соединен с нулевыми входами регистра микрокоманды, триггера отказа и с первыми входами первого, второго и третьего элементов ИЛИ, выход "Конец участка микропрограммы" группы выходов микроопераций устройства соединен с вторым входом третьего элемента ИЛИ, с первым входом второго элемента И и церез второй элемент задержки соединен с вторым входом 1 О первого элемента ИЛИ, выход которого соединен с нулевым входом счетчика времени, первый выход блока контроля соединен с вторыми управляющими входами первого и второго блока элементов И, с единичным входом триггера блокировки и вторым входом второго элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход второго эле- о мента ИЛИ соединен а нулевым входом триггера блокировки, нулевой выход которого соединен с вторым входом, третьего элемента И, выход третьего элемента И соединен с управляющим входом ассоциативного блока памяти, выход третьего элемента ИЛИ соединен с нулевым входом регистра кода времени, выходы регистра кода времени соединены с входами четвертого элемента ИЛИ, выход которого церез30 первый одновибратор соединен с прямым входом четвертого элемента И, выход четвертого элемента И соединен с управляющими входами третьего блока Элементов И, выходы которого соедине- З 5 ны с первыми входами блока элементов ИЛИ, выход второго одновибратора соединен с вторым входом блока элементов ИЛИ, выходы блока элементов ИЛИ соединены с единичными вхо О .дами счетчика времени, второй выход блока контроля соединен с входом второго одновибратора и инверсным входом четвертого элемента И.Блок формирования адреса содер жит группу элементов И, группу сумматоров по модулю даа, причем входы немодифицируемой части адреса второй группы входов блока соединены с выходами немодифицируемой части ад реса группы выходов блока, входы модифицируемой части адреса второйгруппы входов блока соединены с первой группой входов сумматоров по модулю два группы, выходы которых сое динены со входами модифицированной части адреса группы выходов блока, входы кода проверяемого логического условия второй группы входов блока соединены с первыми входами элементов И группы, первая группа вхддов блока соединенас вторыми входами элементов И группы, выходы которых соединень 1 с второй группой входов сумматоров по модулю два группы.Кроме того, блок контроля содержит первый, второй и третий сумматоры по модулю два, элемент ИЛИ, причем первая группа входов блока соединена с входами первого сумматора по модула два, выход которого соединен с первым вхоДом элемента ИЛИ, выход которого является первым выходом блока контроля, вторая группа входов блока контроля соединена с входами второго сумматора по модулю два, выход которого соединен с вторым, входом элемента ИЛИ, третья группа входов блока контроля соединена с входамитретьего сумматора по модулю два, выход которого является вторым выходом блока контроля.Сущность изобретения состоит в повышении отказоустойчивости устройства и оперативности восстановления микрокоманд при сбоях путем увеличения вероятности безотказной работы средств контроля и уменьшения времени выполнения участков микропрограммы. При считывании первой микрокоманды текущего участка микропрограммы из постоянного запоминающего устройства, из ассоциативногозапоминающего устройства считывается и записывается в счетчик времени кодвремени, в течение которого этот участок микропрограммы должен быть выдан на выходы микроопераций устройства.Величина этого кода времени для каждого участка микропрограммы задается своя, она определяется максимальным временем,. в течение которо-.го могут быть сформированы микрокоманды данного участка микропрограммы,Если очередная 1-я микрокоманда -го участка считывается со сбоемиз постоянного блока памяти и текущее время выполнения участка микропрограммы меньше допустимого времени; то она на выходы микроопераций устройства не выдается. При этомона считывается повторно и снова проверяется. Если микрокоманда повторно считана правильно, то она поступает на выходы микооопераций устройства, и с поступлением очередного40 9 1027тактового импульса формируется (+1)ямикрокоманда 1-го участка микропрограммы. Если же повторно микрокоманда считывается со сбоем и время,отведенное на ее выполнение, не кон 5чилось, то она аналогично описанному выше алгоритму считывается третий раз и проверяется,Если после и повторных считываний1-й микрокоманды (тактов )сбой неисчезнет и допустимое время отведенное на ее выполнениевышло, то фиксируется отказ микройрограммногоустройства управления.Отказ устройства фиксируется ипри выполнении Р-й микрокомандц 1-гоучастка если время на выполнение все"го 0-го участка кончилось, а участок остался невыполненным,Код допустиго интервала временсчитывается одновременно со считыванием первой микрокоманды 1-го участка микропрограммы, записывается всчетчик времени и хранится в нем доокончания выполнения )-го участкамикропрограммы.Введение третьего элемента И иобусловленных им связей позволяетформировать сигнал на управляющийвход ассоциативного блока памяти.Введение третьего элемента ИЛИ иобусловленных им связей позволяетформировать сигнал на нулевой входрегистра кода времени.Введение первого элемента за"держки позволяет формировать сиг- З 5налы на первые управляющие входыпервого и второго блоков элементовИ и на счетный вход счетчика времени,Введение второго элемента ИЛИи обусловленных им связей позволяетформировать сигнал на нулевой входтриггера блокировки,Введение триггера блокировки иобусловленных им связей позволяет 45управлять считыванием информации изассоциативного блока памяти,Введение четвертого элемента ИЛИ,первого одновибратора, четвертогоэлемента И и обусловленных ими свя Озей позволяет управлять выдачей кода времени из регистра кода временина счетчик времени через блок элементов ИЛИ. 55Введение второго элемента задержки, первого элемента ИЛИ и обусловленных ими связей позволяет фор 726 10мировать сигнал на нулевой входсчетчика времени.Введение второго одновибратора иобусловленных им связей позволяетформировать сигнал соответствующийдополнительному коду минимальноговремени выполнения участка микропрограммы и выдачи его на вторыевходы соответствующих элементов ИЛИблока элементов ИЛИ,Введение блока элементов ИЛИ иобусловленных им связей позволяет пе.редавать на единичные входы счетчика времени дополнительный код допустимого времени выполнения-го участка микропрограммы.Соединение выходов регистра текущего адреса с адресными входамиассоциативного блока памяти позволяет считывать по адресу первой микрокоманды )-го участка микропрограммы дополнительный код времени выполнения участка микропрограммы.На фиг. 1 представлена функциональная схема микропрограммного устройства управления с исправлениемошибок; на фиг.2 - функциональнаясхема блока формирования адреса;на фиг, 3 - блока контроля,Устройство содержит ( фиг.1) входы 1 кода операции, регистр 2 текущего адреса, постоянный блок 3 памяти, регистр 4 микрокоманды с первымполем 4.1 и вторым полем 4,2, блок5 формирования адреса, первый блокэлементов И 6, входы 7 сигналов логических условий, второй блок элементов И 8, выходы 9 микрооперацийустройства, третий элемент И 1 О,ассоциативный блок 1 памяти, регистр12 кода времени, третий блок эле"ментов И 13, третий элемент ИЛИ 14,вход 15 тактовых импульсов, первыйэлемент И 16, первый элемент 17 задержки, второй элемент И 18, второйэлемент ИЛИ 19, триггер 20 блокировки, четвертый элемент ИЛИ 21,первый одновибратор 22, четвертый элемент И 23, второй элемент 24 задержки, блок 25 контроля, первый элемент ИЛИ 26, счетчик 27 времени,второй одновибратор 28, вход 29установки устройства в начальное состояние, триггер 30 отказа, выход31 сигнала отказа, блок элементовИЛИ 32, группу выходов 33 (фиг.2),группу сумматоров 34 по модулю два,группу входов 35, группу элементовИ 36, а также первую группу входов27726 12 5 О 15 20 11 1037 (Фиг,3),первый сумматор 38 помодулю два, элемент ИЛИ 39, первыйвыход 40,вторую группу входов 41,второй сумматор 42 по модулю два, третью группу входов 43, третий сумматор 44 по модулю два, второй выходВходы 1 кода операции служат длявыдачи кода операции на регистр 2текущего адреса, который служит дляхранения кода адреса очередной микрокоманды и выдачи его на адресныевходы постоянного блока 3 памяти иассоциативный блок 11 памяти запоминающего устройства,В блоке 3 хранятся коды микрокоманд, формируемых микропрограммнымустройством управления с исправлением ошибок. Каждая микрокоманда,считываемая из блока 3, состоит изтрех полей: поля кода микроопера"ций, поля кода базового адреса очередной микрокоманды, поля кода проверяемого логического. условия,Регистр 4 предназначен для хранения считанной из блока 3 микрокоманды. При этом в поле 4.2 хранитсяпервое поле считанной микрокоманды,а в поле 4.1 - второе и третье полясчитанной микрокоманды.Блок элементов И 8 служит для передачи информации с поля 4.2 регистра 4 на выходы 9 устройства приналичии разрешающих сигналов на первом и втором управляющих входах,В блоке 11 хранятся дополнительные коды, соответствующие допустимому времени выполнения -го участка микропрограммы, Информация изблока 11 считывается только при первом считывании из блока 3 первой микрокоманды выполняемого участка микропрограммы и записывается в регистр12. Регистр 12 предназначен для хранения дополнительного кода времени,считанного с блока 11, и выдачи егочерез блок элементов И 13 при наличии сигнала на управляющем входе последнего через блок элементов ИЛИ 32на единичные входы счетчика 27.Элемент И 10 служит для формирования сигнала на управляющий вход блока 11, Элемент И 16 позволяет передавать тактовые импульсы с входа15 на управляющий вход блока 3, наэлемент И 10 и на элемент 17 задерж-ки при правильном функционированиимикропрограммного устройства управления 1,триггер 30 находится в нуле" 25 30 35 40 45 50 55 вом состоянии ) и блокировать выдачу импульсов с входа 15 в противномслучае ( триггер 30 находится вединичном состоянии ). Элемент 17задержки предназначен для ЗадяРжкитактового импульса с выхода элемента И 1 б на время считывания ин"формации из блока 3, записи ее в регистр 4 и проверки правильности еесчитывания в блоке 25 контроля. Триггер 20 блокировки предназначен для управления считыванием инФормации из блока 11. При неправильном считывании первой микрокоманды )-го участка микропрограммы ( первом ее считывании ) триггер 20 устанавливается в единичное состояние. и находится в этом состоянии до конца выполнения )-го участка микропрограммы. Элемент ИЛИ 21 предназначен дляформирования сигнала, соответствующе.го ненулевому содержимому регистра 12,Одновибратор 22 позволяет формиро"вать по входному сигналу с задержкойвыходной импульс и выдачу его через элемент и 23 при правильном счи"тывании информации из блока 1 науправляющий вход блока элементовИ 13, Время задержки определяетсявременем контроля правильности считывания кода времени из блокаизаписи его в регистр 12.Элемент 24 задержки предназначендля задержки сигнала "Конец участкамикропрограммы" на время выдачи мик"рокоманды на выходы 9 устройства.Счетчик 27 служит для подсчета времени выполнения -го участка микропрограммы,При правильном считывании кодавремени выполнения )-го участка микропрограммы в счетчик 27 записывается с выходов регистра 12 дополнитель-.ный код времени выполнения )-го участка, При каждом считывании информа"ции из блока 3 ( как правильном, таки неправильном ) на счетный вход счетчика 27 поступает тактовый импульси его содержимое увеличивается приэтом на единицу.При считывании последней микрокоманды -го участка микропрограммысигнал "Конец участка микропрограммы"поступает на нулевой вход счетчика.При этом счетчик 27 обнуляется,Если после обращений к блоку 3все микрокоманды-го участка микропрограммы устройством на выходы13 1027не выданы, то счетчик 2/ переполняется и на его выходе появляется импульс, идентифицирующий отказ. устройства.Триггер 30 отказа предназначендля формирования сигнала на выход 31при отказе устройства, При этом тактовые импульсы с входа 5 через элемент И 16 на элементы устройства довосстановления отказа устройства непоступают.Блок 5 формирования адреса служитдля формирования адреса очередноймикрокоманды и выдачи его через блокэлементов И 6 на регистр 2.15На вторую группу входов блока 5поступает код базового адреса (+1)"микрокоманды и код проверяемого логического условия.На первую группу входов блока 5поступают сигналы логических условий.Блок 5 формирования адреса ( фиг.2)функционирует следующим образом,.В заисимости от содержимого кодапроверяемого логического условия блок,работает в двух режимах, Первый режим работы .соответствует нулевомузначению логического словия, т.е.формированию микропрограммным устройством управления микрокоманд на30линейных уцастках выполняемой микропрограммы. Адрес очередной микрокоманды, формируемый на выходах33 блока 5, соответствует адресу навходе.35Так как на входе 35 код нулевой,то на выходах группы элементов И 36сигналы отсутствуют и код с входапроходит через группу сумматоров 34по модулю два на выходы модифицированной части адреса группы выходов38 без изменений,Немодифицировання часть кода адреса группы выходов 33 с входом немодифицируемой части адреса группы 45входов поступает непосредственно,Второй режим работы. Содержимоекода на входе 35 отличное от нуля.Этот режим соответствует формированию микропрограммным устройством 50управления очередной микрокомандыв точке ветвления микропрограммы,т,е. после проверки логического условия, заданного кодом на входе 35,При этом результат проверки заданных кодом логических условий выходов группы элементов И 36 поступаетна группу сумматоров 34 по модулю 726 14два, где суммируется по модулю два скодом модифицируемой части адреса.Назначение функциональных элементов блока 25 контроля ( Фиг3) состоит в следующем,Сумматор 38 по модулю два предназначен для контроля на четностьадресной части формируемой устройством микрокоманды,Сумматор 42 по модулю два предназначен для контроля на четность опера"ционной части микрокоманды, Формируемой устройством.Сумматор 44 по модулю два предназ. начен для контроля правильности1считывания дополнитепьного кода времени-го участка микропрограммы изблока 11.Блок 25 контроля Функционируетследующим образом.Если информация из блоков 3 и 11считывается правильно, то на выходахсумматоров 38, 42 и 44 по модулю двасигналы отсутствуют, При неправильном считывании адресной или операционной части микрокоманды из блока3 на выходе соответственно сумматора 38 или сумматора 42(или обоихсразу ) появляются единичные сигналы,которые через элемент ИЛИ 39 поступают на выход 40 устройства.При неправильном считывании информации из блока 11 на выходе сумматора 44 возникает единичный сигнал,который поступает на выход 45,Микропрограммное устройство управления ( фиг,1) функционирует следующим образом. Перед началом работы устройстварегистры 2, 4 и 12, триггеры 20 и 30и счетчик 27 находятся в нулевом состоянии,Код первой микрокоманды первогоучастка микропрограммы с группы входов 1 поступает на регистр 2. По очередному тактовому импульсу, поступающему с входа 15 устройства на управляющий вход блока 11 и через элементИ 10 на управляющий вход блока 11,из блока 3 происходит считывание первой микрокоманды в регистр 1,а из блока 3 происходит считываниедополнительного кода допустимоговремени выполнения первого участкареализуемой микропрограммы. Далеезаписанная в регистры 4 и 12 информация поступает на контроль в блок 25контроля.1027726 15Далее в зависимости от результатовконтроля устройство функционирует водном из четырех режимов.Первый режим. Правильное считывание информации из блоков 3 и 11.Второй режим. Правильное считывание информации с блока 11 и сбой присчитывании информации с блока 3.Третий режим. Правильное считывание информации с блока 3 и сбой присчитывании информации с блока 11.Четвертый режим. Сбой при считывании информациии с блоков 11 и 3.функционирование устройства впервом режиме,При правильном считывании информации из блоков 3 и 11 сигналы на первом и втором выходах блока 25 конт-роля 25 отсутствуют. Так как содержимое регистра 12 не равно нулю, то навыходе элемента ИЛИ 21 появляетсясигнал,Задержанный одновибратором 22 сигнал с выхода элемента ИЛИ 21 не воздействует на управляющий вход блокаэлементов И 13, Дополнительный кодвремени с регистра 12 поступает через блок элементов И 13 на счетчик27 времени. Тактовый импульс, задержанный элементом 17 задержки на время, поступает на первые управляющиевходы блоков элементов И 6 и 8 ина счетный вход счетчика 27.При этом адрес очередной микрокоманды с выходов блока 5 формиро-.вания адреса через блок элементовИ 6 поступает на регистр 2, операционная часть микрокоманды с поля 4,2регистра 4 через блок элементов И 8поступает на выходы микрооперацийустройства и содержимое счетчика 27увеличивается на единицу,С поступлением очередного и последующих тактовых импульсов на вход15 устройства осуществляется формирование второй и последующих микрокоманд первого участка микропрограммы по описанному выше алгоритму, Особенностью функционированияустройства при этом будет то, чтопри считывании второй и последующихмикрокоманд первого участка микропрограммы информация из блока 11 врегистр 12 считываться не будет,так как в нему возможно обращение поадресам первых микрокоманд выполняемых участков микропрограмм, При формировании последней микрокоманды пер-.вого участка микропрограммы на соот 16ветствующем выходе "Конец участка программы" группы выходов 9 появится единичный сигнал. Этот сигнал установит в нулевое состояние регистр 12 через элемент ИЛИ 14, через элемент 24 задержки и элемент ИЛИ 26 установит в нулевое состояние счетчик 27, через элемент И 18 и элемент ИЛИ 19 подтвердит нулевое состояние триггера 20.Адрес первой микрокоманды второго участка микропрограммы с поля 41 регистра 4, пройдя через блок 5 и блок элементов И 6, записывается в регистр 2, Далее микропрограммное 51 О15 устройство управления функционируетаналогично описанному вцве алгоритму.,функционирование устройства во 8 тором режиме.При считывании из блока 3 кода первой микрокоманды первого участкамикропрограммы со сбоем на первом выходе блока 25 контроля появляется единичный сигнал. При этом триггер 20 устанавливается в единичное состояние, а блоки элементов И 6 и 8 зак"рываются по второму управляющему входу. Тактовым импульсом, задержаннцм элементом 17 задержки, микрокомандас поля 4.2 регистра 4 на выходы 9 устройства через блок элементов И 8 невыдается, адрес очередной микрокоманды в регистр 2 не записывает"ся, содержимое счетчика 27 увеличивается на единицу.35 С приходом очередного тактовогоимпульса на вход 15 устройства изблока 3 осуществляется повторноесчитывание первой микрокомандц,Так как триггер 20 находится в еди ничном состоянии, то на управляющийвход блока 11 импульс не поступаетинформация из блока 11 считывается. при Формировании микрокоманд 1"гоучастка микропрограммы один раз, 45 а именно при формировании его перВой микрокомднды)Если при повторном считываниипервая микрокоманда записывается врегистр 4 без сбоясигнал на первом выходе блока контроля исчезает ),то тактовый импульс, задержанныйэлементом 17 задержки, открывает попервому. управляющему входу блокиэлементов И 6 и 8 и увеличивает со держимое счетчика 27 на единицу.При этом код микрокоманды с поля4.2 регистра 4 поступает на выходы 9устройства, а адрес очередной микро

СмотретьЗаявка

3409218, 23.03.1982

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БЛАГОДАРНЫЙ НИКОЛАЙ ПЕТРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, САМАРСКИЙ ВИКТОР БОРИСОВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 07.07.1983

Код ссылки

<a href="https://patents.su/12-1027726-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Цифровой интегратор

Следующий патент: Приоритетное устройство

Случайный патент: Дешифратор адреса