Сумматор -ичных чисел с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1134942

Автор: Евстигнеев

Текст

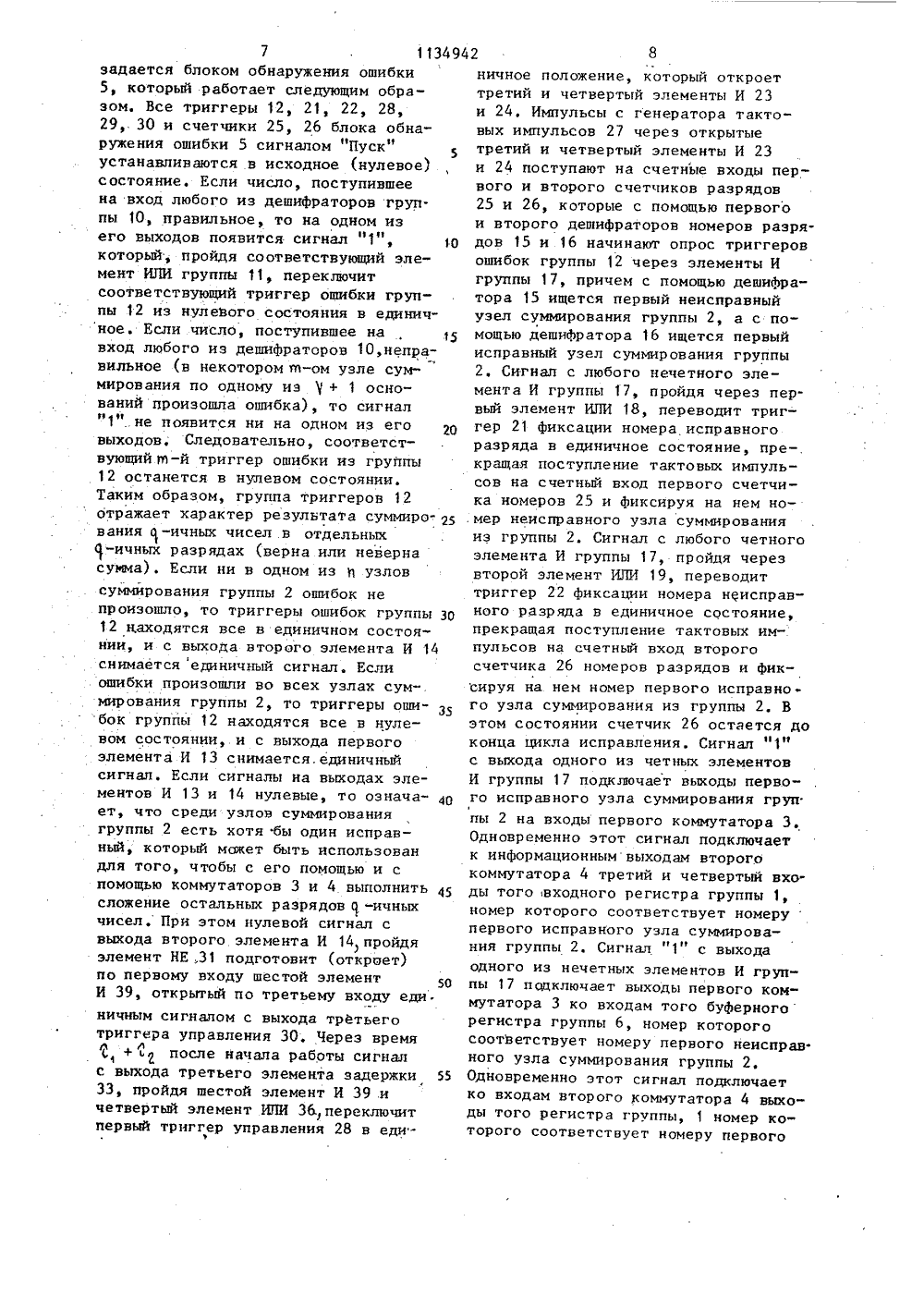

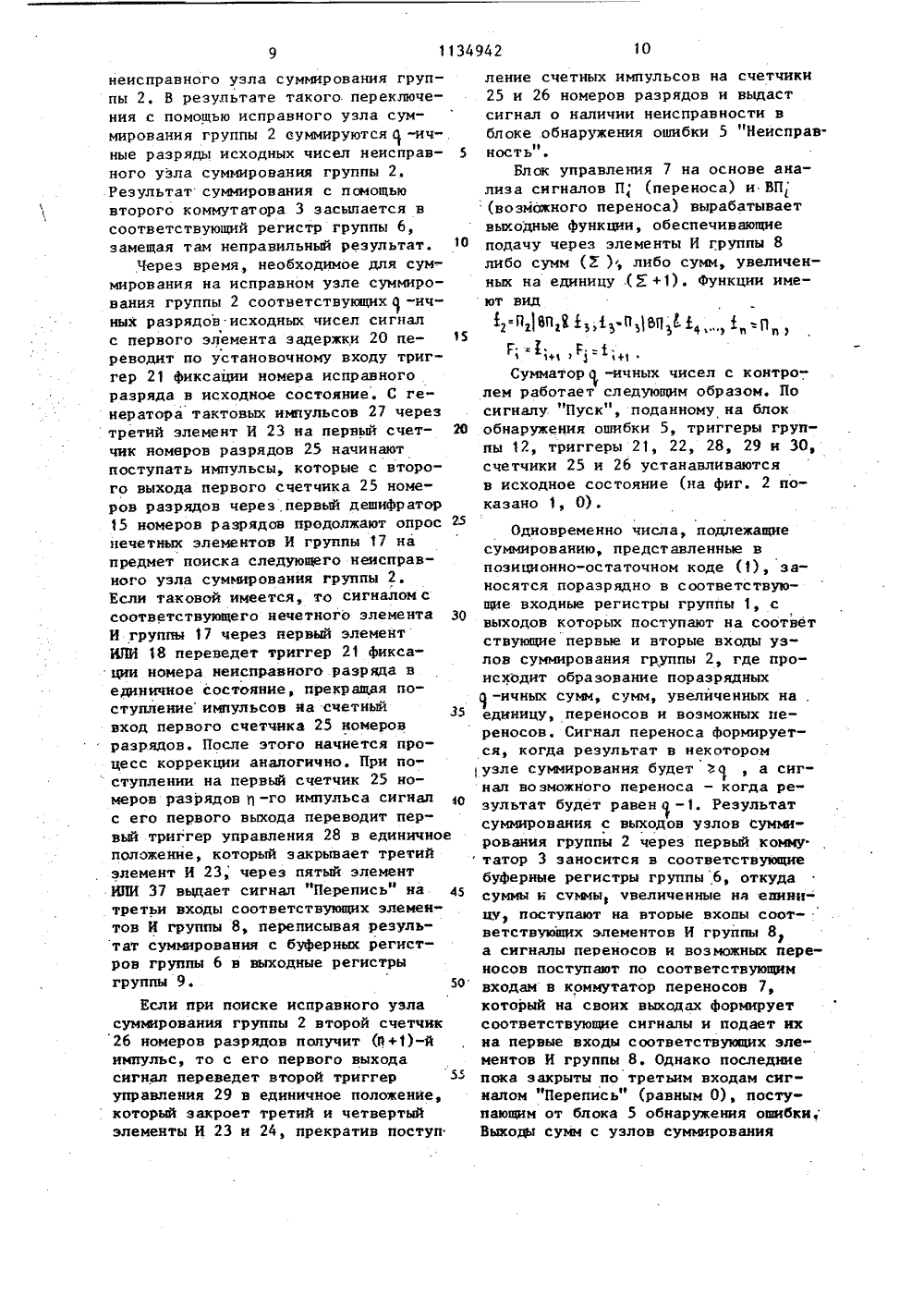

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУВЛИН КОМИТЕТ СССР ИЙ И (ЛНРЫТИ УДФРСТВЕКО ЛАМ И ОПИСАНИЕ ИЭОБРЕТЕНИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ут инженеров(7 1) Московский инститгражданской авиации(56) 1. Авторское свидетельство СССР В 575649, кл. С 06 Р 7/50, 1977.2. Авторское свидетельство СССР Ф 478304, кл. С 06 Р 7/385, 1975 (прототип)(54)(57) 1.СУММАТОР ) -ИЧНЫХ ЧИСЕЛ С КОНТРОЛЕМ, содержащий группу входных регистров, входы которых являются входами сумматора, группу узлов суммирования, группу элементов И, коммутатор переносов, выходы которого соединены с первыми входами соответствующих элементов И группы,. группу выходных регистров, входы которых соединены с выходами элементов И группы, выходы входных регистров группы соединены со входами слагаемых узлов суммирования группы, о тл и ч а ю щ и й с я тем, что, с целью новишения достоверности суммирования, в него введены первый и второй коммутаторы, блок обнаружения ошибки, группа буферных регистров, входы которых подключены соответственно к информационным выходам первого коммутатора, информационные входы которого подключены соответственно к выходам сумм, суммы, увеличенной ка единицу, переноса и возможного переноса узлов суммирования группы, выходы суммы которых подключены к оответствующим информационным входамблока обнаружения ошибки, группа 4(51) С Об Р 11/10, а Об Г 7/72 управляющих входов первого коммутатора соответственно объединена с группой управляющих входов второго коммутатора и подключена к группе выходов блока обнаружения ошибки, группа. информационных входов второго коммутатора подключена соответственно к выходам входных регистров группы, а группа информационных выходов - к соответствунщим входам входных регистров группы, первые выходы буферных регистров группы, начиная со второго, соединены с группой входов коммутатора переносов, первый и второй выходы первого и вторые входы остальных буферных регистров группы соединены со вторыми входами элементов И группы, третьи, входа которых соединены с выходом "Перепись" блока обнаружения ошибки, выход "Контроль" которого соединен с управляющим входом первого коммутатора, выходы "Неисправность" и "Ошибка во всех разрядах" и вход "Пуск" сумматора соединены с одноименными выходами и входом блока обнаружения ошибки.2. Сумматор по п.1, о т л и ч ае щ и й с я тем, что блок обнаружения ошибки содержит группу дешнфраторов када системы остаточных классов (СОК), первую группу элементов ИПИ, группу триггеров ошибок, эле- мент НЕ, пять элементов ИПИсемь элементов И, два дешифратора номеров разрядов, группу элементов И, четыре элемента задержки, триггеры фиксации номера ошибочного и исправного разряда, первый и второй счетчики номеров разрядов, генератор тактовых импульсов, три триггерауправления, причем входы дешифраторов кода СОК группы являются 1",руппойинформационных входов блока, выходыкаждого из дешифраторов кода ООКгруппы подключены ко входам соответствующих элементов ИЛИ первой группы,выходыкоторых подключены к единичным входам соответствующих триггеровошибок группы установочные входыкоторых объединены и являются входом "Пуск" блока, единичные выходытриггеров ошибок группы подключенык перщпч входам соответствующих нечетных элементов И группы и ко входам,первого элемента И, нулевые выходытриггеров ошибок группы подключенык первым входам соответствующихчетных элементов И группы и ко входам второго элемента И, вторые входы нечетных и четных элементов Игруппы подключены к соответствующимвыходам первого ивторого дешифраторов номеров разрядов, входы которыхподключены соответственио к выходампервого и второго счетчиков номеровразрядов, выходы нечетных и четныхэлементов И группы подключены ковходам соответственно первого и второго элементов ИЛИ и являются группой выходов блока, выходы первогои второго элементов ИЛИ подключенысоответственно к единичным входамтриггеров фиксации номеров ошибочного и исправного разрядов, первыйвход третьего элемента ИЛИ,объединенс установочными входами триггеровошибок группы, триггера фиксации,номера исправного разряда, первогои второго счетчиков номеров разрядов,первого, второго и третьего триггеров управления и является входом"Пуск" блока, второй вход третьегоэлемента ИЛИ подключен к выходу первого элемента задержки, вход которого подключен к выходу первого элемента ИЧИ, выход третьего элемента ИЛИподключен к установочному входутриггера фиксации номера ошибочногоразряда, единичные выходы триггеровфиксации номеров ошибочного и исправ.ного разрядов подключены к первымвходам соответственно третьего ичетвертого элеменгсв И, вторые входыкоторых подключены к выходу генератора тактовых импульсов, а третьи и четвертые входы - соответственно к нулевому и единичному выходам первого и.второго триггеров управления, первый вход пятого элемента И подключен к выходу первого элемента И, второй вход - к выходу второго элемента задержки, а выход - к единичному входу третьего триггера управления, выход второго элемента И подключен ко входу элемента НЕ, выход которого подключен к первому входу шестого элемента И, второй вход которого подключен к выходу третьего элемента задержки, вход которого подключен к выходу второго элемента задержки, третий вход шестого элемента И подключен к единичному выходу третьего триггера управления, нулевой выход которого является выходом "Ошибка во всех разрядах" блока, выход шестого элемента И подклю-. чен к первому входу четвертого элемента ИЛИ, второй вход которого подключен к первому выходу первого счетчика номеров разрядов, а выход подключен к единичному входу первого триггера управления единичный выход которого подключен к первому входу седьмого элемента И и является выходом "Контроль" блока, второй вход седьмого элемента И подключен к единичному выходу третьего триггера управления третий вход - к выходу четвертого элемента задержки, вход которого подключен к выходу третье-: го элемента задержки, выход седьмого элемента И подключен к первому входу пятого элемента ИЛИ, второй вход которого подключен к первому выходу первого счетчика номеров разрядов, а выход является выходом "Перекись блока, счетные входы первого и второго счетчиков номеров разрядов подключены к выходам соответственно третьего и четвертого элементов И, первый выход второго счетчика номеров разрядов подключен к единичному входу второго триггера управления, нулевой выход которого является выходом "Неисправность" блока, вторые выходы первого и второго счетчиков номеров разрядов подключены соответственно ко входам первого и второго дешифраторов номеров разрядов.1134942 Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих арифметических устройств сов-, ременных цифровых вычислительных машин.Известен сумматор а-разрядных 1 -ичных чисел, содержащий в групп по й суммирующих блоков, коммутаторы, входные регистры, выходные регистры, О . блоки обнаружения ошибок кратности +1, индикаторы неисправности, блок разрешения обмена, блок перебора сочетаний и соответствующие связи 11,Недостатком данного устройства 15 является невысокое быстродействие, связанное с громоздкостью алгоритма обнаружения и исправления ошибок.Наиболее близким к предлагаемому техническим решением является матрич" 2 О ныйсумматор, содержащий сумматоры групп разрядов суммируемых чисел, выходы которых соединены соответственно со входами регистров групп разрядов сумматора, причем выходы 25 регистров групп разрядов суюаруемых чисел соединены со входами матриц аиачений сумм, увеличенных на единицу разряда данной группы, и матриц признаков возможности переносов, выходы которых совместно с выходамн матриц переносов подключены ко входам управляющей матрицы, выходы которой связаны соответственно со вто, рь 1 ми входами схем И и со вторыми вхо. дами дополнительных схем И, первые входы которых соединены соответствен но с выходами матриц значений сумм, увеличенных на единицу разряда групп, а выходы - с соответствующими входами выходного регистра групп разрядов сумматора 21. Недостатком известного устройстваявляется низкая достоверность егоработы, связанная с отсутствием конт.роля эа работой сумматора.Цель изобретения - повышениедбстоверности суммирования. Поставленная цель достигается 50 тем, что в сумматор -ичнцх чисел с контролем, содержащий группу входных регистров, входы которых .являются входами сумматора, группу узлов суммирования, группу элементов 55 И, коькутатор переносов, выходы которого соединены с первыми входами1 соответствующих элементов И группы,2группу выходных регистров, входы ко".торых соединены с выходами элементов И групнц, выходы входных регистров группы соединены со входами слагаемьас узлов суммирования группы,введены первый и второй. коммутаторы,блок обнаружения ошибки, группа буферных регистров, входы которых подключены соответственно к информационным выходам первого. коммутатора,информационные входы которого подключены соответственно к выходам сумеее,сумю, увеличенной на единицу, пере- .носа и возможного переноса узловсуммирования группы, выходы суминкоторых подключены к соответствующиминформационным входам блока обнарукения ошибки, группа управляющих: входоапервого коммутатора соответственно .объединена с группой управляющих входов второго коммутатораи подключена к группе выходов блока обнаруженияошибки, группа информационных входоввторого коммутатора подключена соответственно к выходам входных регистров группы, а группа информацион.ных выходов - к соответствук 3 цим входам входных регистров группы, первые выходы буферных регистров группы,начиная со второго, соединены сгруппой входов коммутатора переносов,первый и второй выходы первого ивторые входы остальных буферных ре - ,гистров группы соединены со вторьмвходами элементов И группы, третьивходы которых соединены с выходом"Перепись" блока обнаружения ошибки,выход "Контроль" которого соединенс управляющим входом первого коммутатора, выходы "Неисправность" и "Ошибка во всех разрядах" и вход ф 1 Пуск"сумматора соединены с одноименнымивыходами н входом блока обнаруженияошибки,Блок обнаружения опебки содержит группу дешифраторов кода СОК, первую группу элементов ИЛИ, группу . триггеров ошибок, элемент НЕ, пять элементов ИЛИ, семь элементов И, два дешифратора номеров разрядов, группу элементов И, четыре элемента задержки, триггеры фиксации номера ошибочного и исправного разряда, первый и второй счетчики номеров. разрядов, генератор тактовых импульсов, три триггера управления, причем входы дешифраторов кода СОК группы являются группой информационных вхо3 113494 ,дов блока, выходы каждого из дешиф. раторов кода СОК группы подключены ко входам соответствующих элементов ИЛИ первой группы, выходы которых подключены к единичным входам соответствующих триггеров ошибок группы, установочные входы которых объединены и являются входом "Пуск" блока, единичные выходы триггеров ошибок группы подключены к первым входам соответствующих нечетных элементов И группы и ко входам первого элемента И, нулевые выходы триггеров ошибок группы подключены к первым входам соответствукяцих четных элементов 5 И группы и ко входам второго элемента И, вторые. входы нечетных и четных элементов И группы подключены к соответствующим. выходам первого и второго дешифраторов номеров раз рядов, входы которых подключены соответственно к выходам первого и второго счетчиков номеров разрядов, выходы нечетных и четных элементов И группы подключены ко входам соот-.ветственно первого и второго элементов ИЛИ и являются группой выходов блока, выходы первого и второго элементов ИЛИ подключены соответственно к единичным входам триггеров фикса-ции номеров ошибочного и исправного разрядов, первый вход третьего элемента ИЛИ объединен с устанозочными входами триггеров ошибок группы, триггера фиксации номера исправного 35 разряда, первого и второго счетчиков номеров разрядов, первого, второго и третьего триггеров управления и является входом "Пуск" блока, второй вход третьего элемента ИЛИ подклю чен к выходу первого элемента задержки, вход которого подключен к выходу первого элемента ИПИ, выход третьего элемента ИЛИ подключен к установоч.ному входу триггера фиксации номера 45 ошибочного разряда, единичные выходы триггеров фиксации номеров ошибочного и исправного разрядов подключены к первым входам соответственно третьего и четвертого элемен тов И, вторые входы которык подклю" чены к. выходу генератора тактовых импульсов, а третьи и четвертые входы - соответственно к нулевому и единичному выходам Первого и вто рого триггеров управления, первый вход пятого элемента И подключен к выходу первого элемента И, второй вход - к выходу второго элемента задержки, а выход - к единичному входу третьего триггера управления, выход второго элемента И подключен ко входу элемента НЕ, выход которого подключен к первому входу шестого элемента И, второй вход которого подкЛючен к выходу третьего эле- мента задержки, вход которого подключен к выходу второго элементазадержки, третий вход шестого элемента И подключен к единичному выходутретьего триггера управления, нуле-вой выход которого является выходом"Ошибка во всех разрядах" блока, выход шестого элемента И подключен к первому входу четвертого элемента ИЛИ, второй вход которого подключенк первому выходу первого счетчиканомеров разрядов, а выход подключенк единичному входу первого триггерауправления, единичный выход которого подключен к первому входу седьмого элемента И, и является выходом"Контроль" .блока, второй вход седьмо"го элемента И подключен к единичному выходу третьего триггера управления, третий вход - к выходу четвертого элемента задержки, вход которого подключен к выходу третьего элемента задержки, выход седьмого элемента И подключен к первому входу пятого элемента ИЛИ, второй входкоторого подключен к первому выходу первого счетчика номеров разрядов, а выкод является выходом "Перепись" блока счетные входы первого и второго счетчиков номеров разрядов подключены к выходам соответственно третьего и четвертого элементов И, первый выход второго счетчика номеров разрядов подключен к единичномувходу второго триггера управления,нулевой выход которого является выходом "Неисправность" блока, вторыевыходы первого и второго счетчиков номеров разрядов подключены соответственно ко входам первого и второгодешифраторов номеров разрядов. На фиг. 1 представлена функциональная схема сумматора-ичнык.чисел с контролем, на которой обозначено: группа 1 входных регистров, группа 2 узлов суммирования, первый 3 и второй 4 коммутаторы, блок 5 обнаружения ошибки, группа 6 буферных регистров, коммутатор 7 переносов, группа 8 элементов И, группа713494 задается блоком обнаружения ошибки 5, который работает следующим образом. Все триггеры 12, 21, 22, 28, 29, 30 и счетчики 25, 26 блока обнаружения ошибки 5 сигналом "Пуск" устанавливаются в исходное (нулевое) состояние. Если число, поступившее на вход любого из дешифраторов группы 10, правильное, то на одном из его выходов появится сигнал "1", о который, пройдя соответствующий элемент ИЛИ группы 11, переключит соответствующий триггер ошибки группы 12 из нулевого состояния в единичное. Если число поступившее на вход любого из дешифратаров 10,неправильное (в некотором е-ом узле суммирования по одному из+ 1 оснований произошла ошибка), то сигнал .не появится ни на одном из его выходов, Следовательно, соответствующий щ-й триггер ошибки из группы 12 останется в нулевом состоянии. Таким образом, группа триггеров 12 отражает характер результата суммира вания а -ичных чисел в отдельных -ичных разрядах (верна или неверна сумма). Если ни в одном из 1 узлов суммйрования группы 2 ошибок не произошло, то триггеры ошибок группы ЗО 12 находятся все в единичном состоянии, и с выхода второго элемента И 4 снимается единичный сигнал . Если ошибки произошли во всех узлах сум-, мирования группы 2, то триггеры оши- З 5 бок группы 12 находятся все в нулевом состоянии, и с выхода первого элемента И 13 снимается. единичный сигнал. Если сигналы на выходах элементов И 13 и 14 нулевые, то означа- о ет, что среди узлов суммирования группы 2 есть хотя бы один исправньй, который мажет быть использован для того, чтобы с его помощью и с помощью коммутаторов 3 и 4 выполнить 45 сложение остальных разрядов а -ичных чисел, При этом нулевой сигнал с выхода второго элемента И 14 пройдя элемент НЕ,31 подготовит (откршет) по первому входу шестой элемент И 39, открытый по третьему входу еди.ничным сигналом с выхода третьеготриггера управления 30, Через времял+ ь 2 после начала работы сигнал с выхода третьего элемента задержки 55 33, пройдя шестой элемент И 39.и четвертый элемент ИПИ 36. переключитпервый триггер управления 28 в еди 2 8ничное положение, который откроет третий и четвертый элементы И 23 и 24. Импульсы с генератора тактовых импульсов 27 через открытые третий и четвертый элементы И 23 и 24 поступают на счетные входы первого и второго счетчиков разрядов 25 и 26, которые с помощью первого и второго дешифраторов номеров разрядов 15 и 16 начинают опрос триггеров ошибок группы 12 через элементы И группы 17, причем с помощью дешифра" тора 15 ищется первый неисправный узел суммирования группы 2, а с помощью дешифратора 16 ищется первый исправный узел суммирования группы 2, Сигнал с любого нечетного элемента И группы 17, пройдя через первый элемент ИЛИ 18, переводит триггер 21 фиксации номера исправного разряда в единичное состояние, пре-. кращая поступление тактовых импульсов на счетный вход первого счетчика номеров 25 и Фиксируя на нем но,мер неисправного узла суммирования иэ группы 2, Сигнал с любого четного элемента И группы 17, пройдя через второй элемент ИЛИ 19, переводит триггер 22 фиксации номера неисправного разряда в единичное состояние, прекращая поступление тактовых импульсов на счетный вход второго счетчика 26 номеров разрядов и фиксируя на нем номер первого исправного узла суммирования иэ группы 2. В этом состоянии счетчик 26 остается до конца цикла исправления. Сигнал "1" с выхода одного из четных элементов И группы 17 подключает выходы первого исправного узла суммирования груп пы 2 на входы первого коммутатора 3. Одновременно этот сигнал подключает к информационным выходам второго коммутатора 4 третий и четвертый входы того входного регистра группы 1, номер которого соответствует номерупервого исправного узла суммирования группы 2. Сигнал "1" с выходаодного из нечетных элементов И группы 17 подключает выходы первого коммутатора 3 ко входам того буферногорегистра группы 6, номер которогосоответствует номеру первого неисправ.ного узла суммирования группы 2.Одновременно этот сигнал подключаетко входам второго коммутатора 4 выходы того регистра группы, 1 номер которого соответствует номеру первого55 неисправного узла суммирования группы 2, В результате такого переключения с помощью исправного узла суммирования группы 2 еуммируются-ичные разряды исходных чисел неисправ ного узла суммирования группы 2. Результат суммирования с помощью второго коммутатора 3 засылается в соответствующий регистр группы 6, замещая там неправильный результат, 1 ОЧерез время, необходимое для суммирования на исправном узле суммирования группы 2 соответствующих-ичных разрядов. исходных чисел сигнал с первого элемента задержки 20 пе реводит по установочному входу триггер 21 фиксации номера исправного разряда в исходное состояние. С генератора тактовых импульсов 27 через третий элемент И 23 на первый счет чик номеров разрядов 25 начинают поступать импульсы, которые с второго выхода первого счетчика 25 номеров разрядов через, первый дешифратор 15 номеров разрядов продолжают опрос 25 нечетных элементов И группы 17 на предмет поиска следующего неисправного узла суммирования группы 2, Если таковой имеется, то сигналом с соответствующего нечетного элемента ЗО И группы 17 через нервый элемент ИЛИ 18 переведет триггер 21 фиксации номера неисправного разряда в единичное состояние, прекращая поступлениеимпульсов на счетный35 вход первого счетчика 25 номеров разрядов. После этого начнется процесс коррекции аналогично, При поступлении на первый счетчик 25 номеров разрядов П -го импульса сигнал с его первого выхода переводит первый триггер управления 28 в единичное положение, который закрывает третий элемент И 23; через пятый элемент ИЛИ 37 выдает сигнал Перепись на 45 третьи входы соответствующих элемеи тов И группы 8, переписывая результат суммирования с буферных регистров группы 6 в выходные регистры группы 9.50Если при поиске исправного узла суммирования группы 2 второй счетчик 26 номеров разрядов получит 01+1)-й ивотульс, то с его первого выхода сигнал переведет второй триггер управления 29 в единичное положение, который закроет третий и четвертый элементы И 23 и 24, прекратив поступ ление счетных импульсов на счетчики25 и 26 номеров разрядов и выдастсигнал о наличии неисправности вблоке обнаружения ошибки 5 "Неисправность".Блок управления 7 на основе анализа сигналов П; (переноса) и ВП(возможного переноса) вырабатываетвыходные функции, обеспечивающиеподачу через элементы И группы 8либо сумм (1 ), либо сумм, увеличенных на единицу,(Я+1). Функции имеют вид2 Чфь 33 4 ВП Ф " ) л Пй )г 1 Г,1Сумматор-ичных чисел с контролем работает следующим образом. Посигналу, "Пуск", поданному на блокобнаружения ошибки 5, триггеры группы 12, триггеры 21, 22, 28, 29 и 30,счетчики 25 н 26 устанавливаютсяв исходное состояние (на фиг. 2 показано 1, О),Одновременно числа, подлежащие суммированию, представленные в позиционно-остаточном коде (1), заносятся поразрядно в соответствующие входные регистры группы 1, с выходов которых поступают на соответ ствующие первые и вторые входы узлов суммирования группы 2, где происходит образование поразрядных-ичных сумм, сумм, увеличенных на . единицу, переносов и возможных переносов. Сигнал переноса формируется, когда результат в некотором узле суммирования будет 3 , а сигнал возможного переноса - когда результат будет равен- 1, Результат суммирования с выходов узлов суммирования группы 2 через первый комму. татор 3 заносится в соответствующие буферные регистры группы 6, откуда суммы и счммы чвеличенные на единицу поступают на вторые входы соответствующих элементов И группы 8 а сигналы переносов и возможных йереносов поступают по соответствующим входам в коммутатор переносов 7, который на своих выходах формирует соответствующие сигналы и подает их на первые входы соответствукицих элементов И группы 8. Однако последние пока закрыты по третьим входам сигналом "Перепись" (равным О), поступающим от блока 5 обнаружения ошибки, Выходы сумм с узлов суммирования1 113494группы 2 поступают на соответствующие входы блока обнаружения ошибки5, в котором с помощью дешифраторовгруппы 10 анализируются на наличиещпибок. Если некоторая-я сумма5(ошибки нет), то соответствующийдешифратор группы 10 на одном из Чвыходов выдаст сигнал, который, пройдя соответствующий элемент ИЛИ 1 Огруппы 11, переведет соответствующий триггер группы 12 в единичноесостояние (О, 1),Если ни в одном изузлов суммирования группы 2 ошибки не произош. 15ло, все триггеры группы 12 перейдутв единичное состояние, так что навыходе первого элемента И 13 будетсигнал О, а на выходе второго элемента И 14 будет сигнал 1. В результате шестой элемент И 39 по первымдвум входам будет закрыт (на нихбудет комбинация 1, О).Если ошибки произойдут во всех1 узлах суммирования группы 2, все 25триггеры группы 12 останутся в нулевом состоянии (1, О), тогда на выходе первого элемента И 13 будет сигнал 1, а на выходе второго элемента И 14 будет сигнал О.Вестой элемент И 39 по первымдвум входам будет закрыт (на них будет комбинация О, 1),Если ошибки произошли не во всехузлах суммирования группы 2, то часть35триггеров группы 12 останется внулевом состоянии (1, О), а частьбудет переведена в единичное состояние (О, 1). В результате на выходахпервого и второго элементов И 13 и14 будут нулевые сигналы, а шестойэлемент И 39 по первым двум входамбудет открыт (на них будет комбинация (1, 1),Через время, необходимое длялсрабатывания сумматоров группы 2,дешифраторов группы 10, элементовИЛИ группы 11, триггеров группы 12и элементов И 13, 14, сигнал "Пуск",задержанный вторым элементом задержки 32, поступает на второй вход пятого элемента И 38.Если к этому моменту пятый элемент И 38 закрыт по первому входу (во всех узлах суммирования группы 55 2 имеются ошибки), то сигнал с выхода пятого элемента И 38 перебрасывает третий триггер управления 30. в При этом запускаются первый и вто рой счетчики номеров разрядов 25 и 26, осуществляющие поиск первого неисправного и первого исправного узлов суммирования в группе 2. Если при этом счетчик 26 просчитал 1+1 импульсов, то из блока обнаружения ошибки 5 формируется сигнал "Неисправ ность", свидетельствующий о том, что по каким-либо причинам исправный узел суммирования группе 2 не обнаружен (хотя его наличие предпо13 1134942 14лагалось). При нормальной работе суммирования засыпается в соатветстблока обнаружения ошибки 5 счетчик вующий буферный регистр, группы 6, со останавливается, просчитав не, держимое которого предполагалось более л импульсов, фиксируя тем неправильньм. После завершения иссамым номер первого встретившегосяправления результата суммирования исправного узла суммирования в груп. блок обнаружения ошибки 5 останавлине 2, Тем временем счетчик 25, оста- вается, а исправленный результат с новившись, также фиксирует номер .буферных регистров группы 6 по сигодного из узлов суммирования в груп- налу "Перепись" перепишется в выходпе 2, но уже неисправного. Выходы 10 ные регистры группы 9, откуда он мопервой и второй групп блока обнару- жет быть считая.жения ошибки 5, воздействуя на первый 3 и второй 4 коммутаторы, под- Таким образом, введение в состав ключают поочередно входные регистры . устройства первого и второго коммутагруппы 1 неисправных узлов сумчиро-торов, блока обнаружения ошибки, вания группы 2 к исправному (эту .группы буферных регистров и соответочередйость задает счетчик 25 обнару ствующих связей позволяет повысить жения.ошибки 5), При этом результат достоверность суммирования.

СмотретьЗаявка

3636203, 14.06.1983

МОСКОВСКИЙ ИНСТИТУТ ИНЖЕНЕРОВ ГРАЖДАНСКОЙ АВИАЦИИ

ЕВСТИГНЕЕВ ВЛАДИМИР ГАВРИЛОВИЧ

МПК / Метки

МПК: G06F 11/10, G06F 7/72

Метки: ичных, контролем, сумматор, чисел

Опубликовано: 15.01.1985

Код ссылки

<a href="https://patents.su/11-1134942-summator-ichnykh-chisel-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор -ичных чисел с контролем</a>

Предыдущий патент: Устройство для обнаружения и исправления ошибок в непозиционном коде

Следующий патент: Устройство для функционального контроля вычислительных машин

Случайный патент: Машина для сшивания сетного полотна