Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

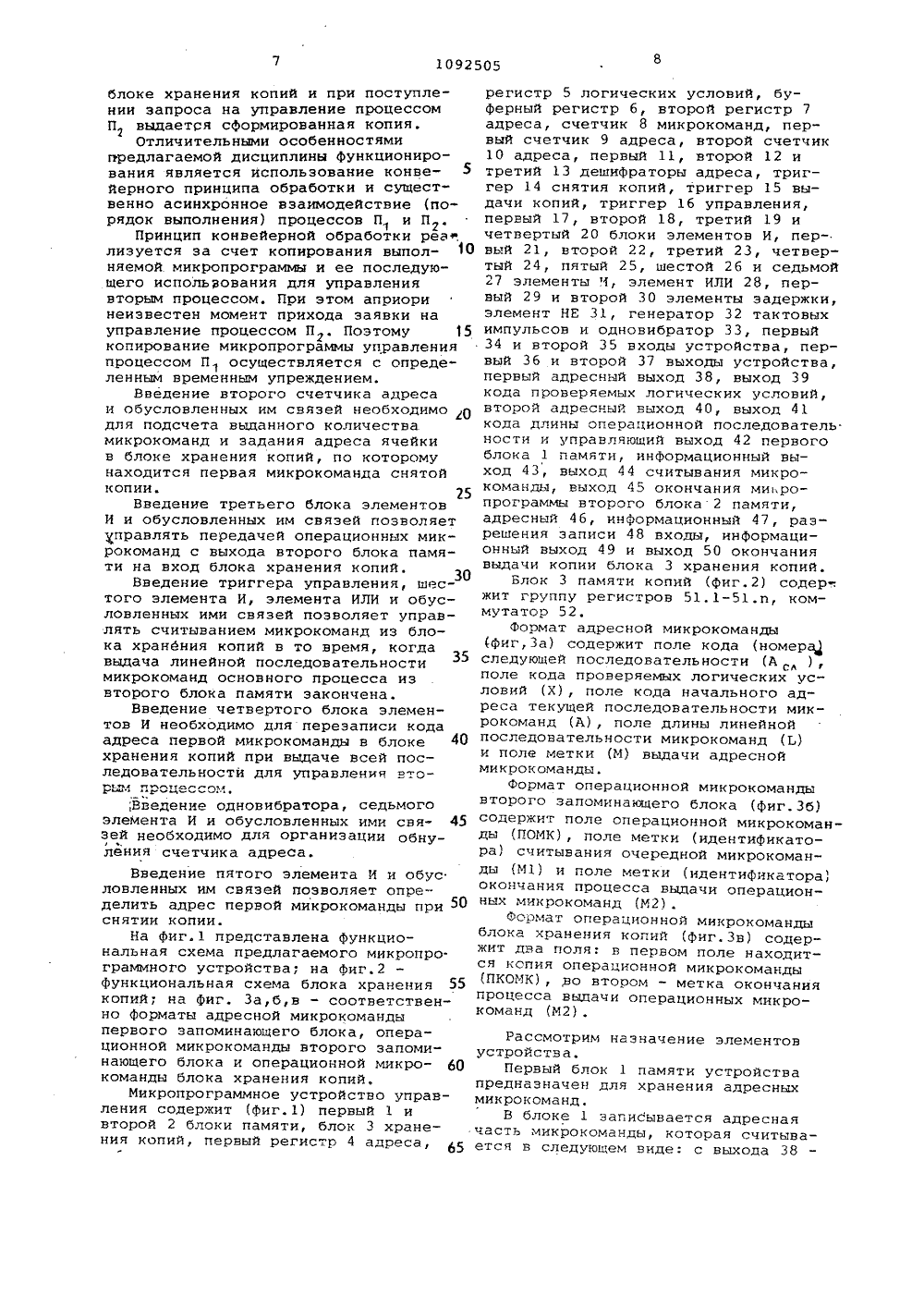

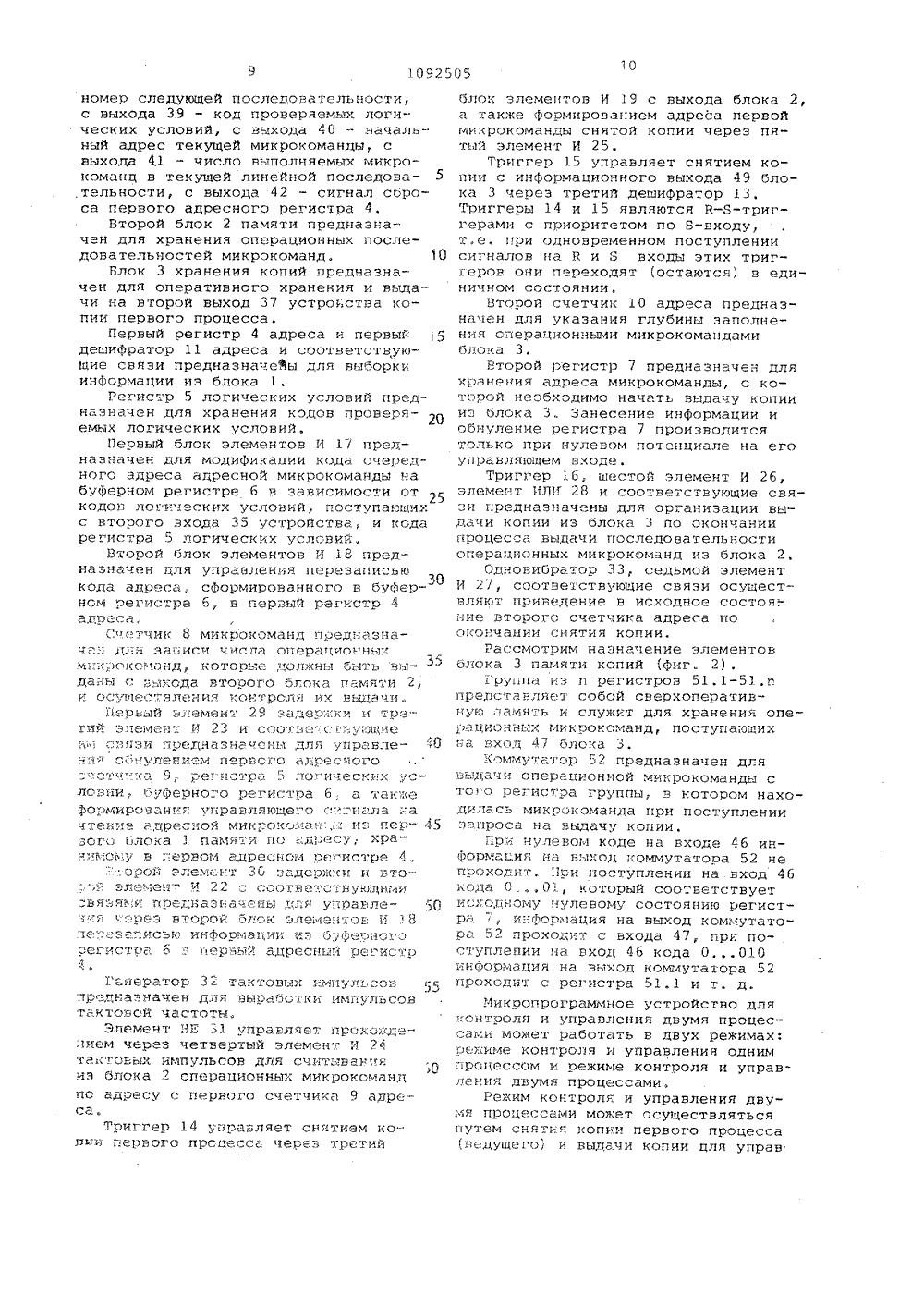

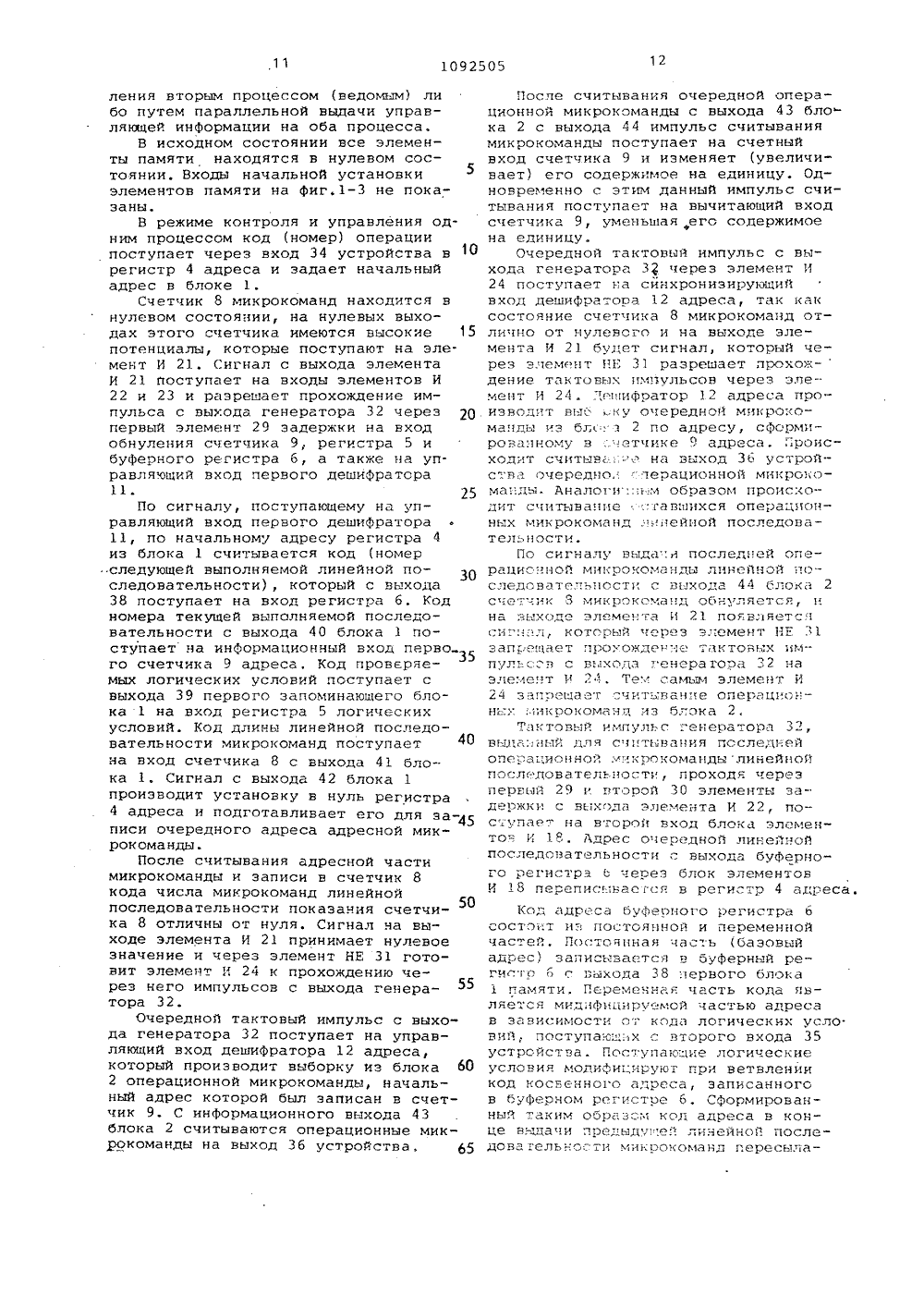

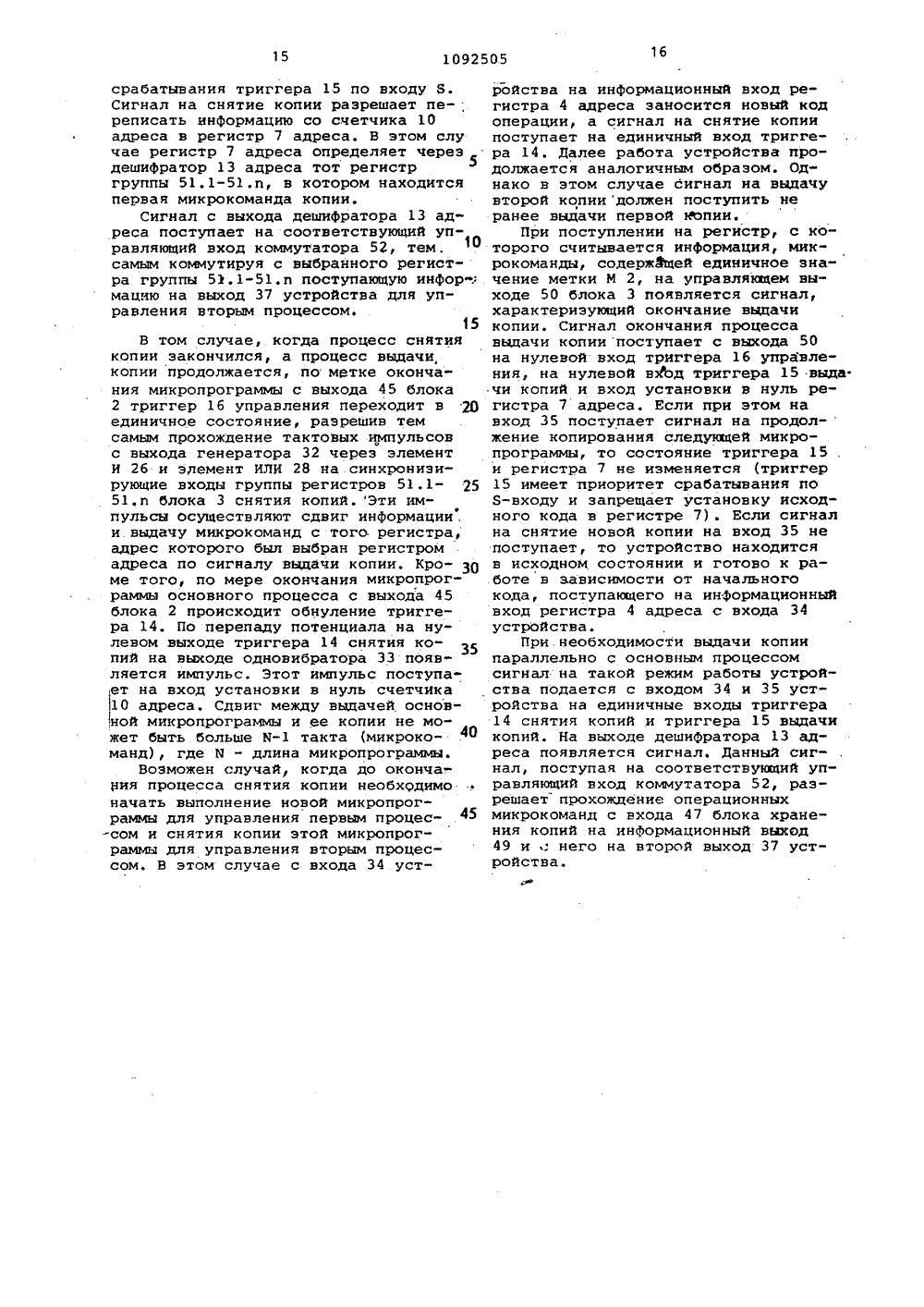

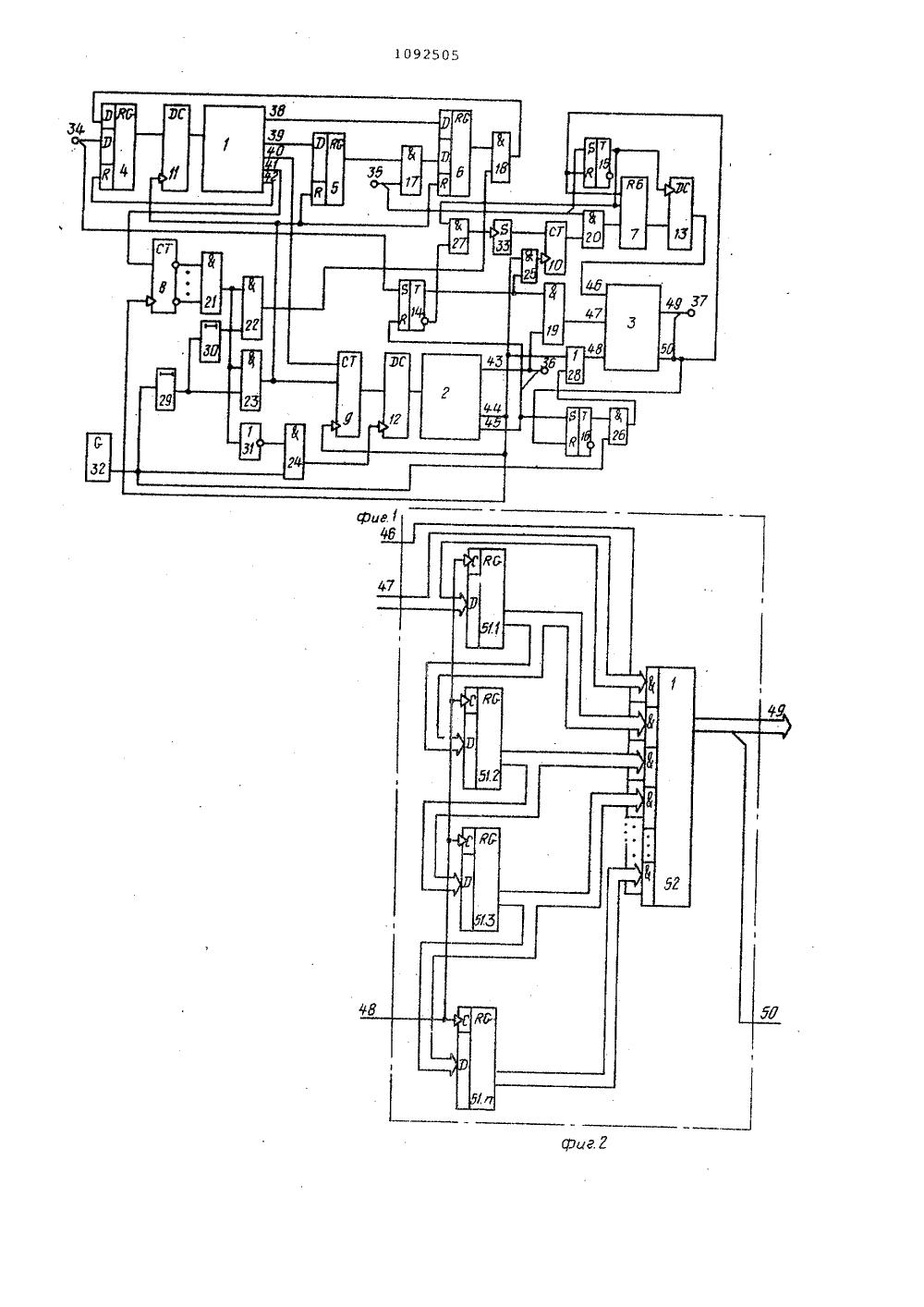

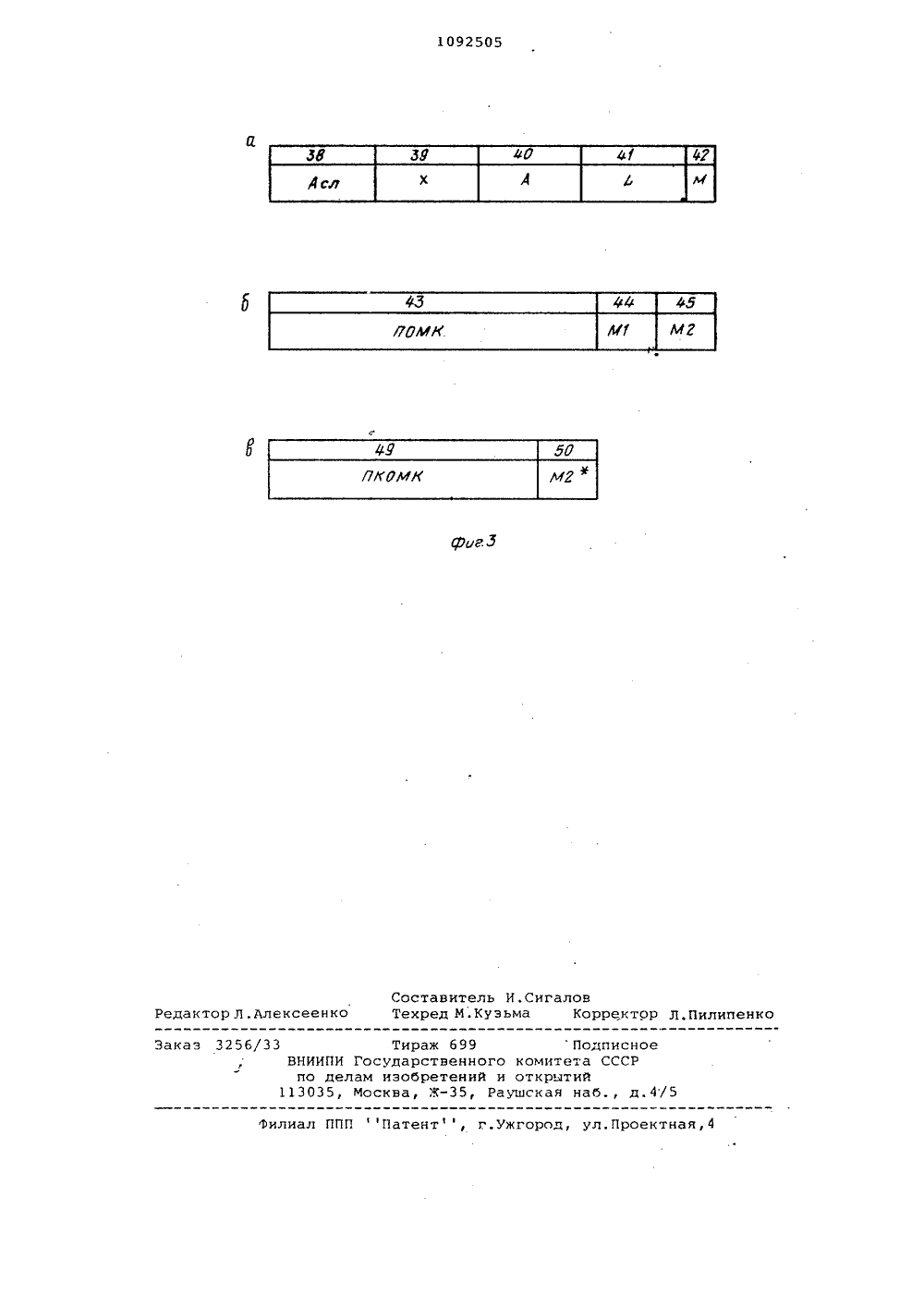

СОЮЗ СОВЕТСКИХюавааепвж119) (111 б Р 9/22; 6 1 00 ЕНИЯ ЕЛЬ АВТОРСКОМУ С Мельниковенко,рбаш льство СССР 1972. стно СССР 1978,ство СССР 1980. ство СССР 1979 (про 4, А 83038 тип)ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ САНИЕ ИЗОБ(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее первый и второй блоки памяти, блок памяти копий,два регистра адреса, регистр логических условий, буферный регистр, счетчик микрокоманд, первый счетчик адреса, первый, второй и третий дешифраторы адреса, первый и второй блокиэлементов И, триггер снятия копий,триггер выдачи копий, генератор тактовых импульсов, пять элементов И,дна элемента задержки и элемент НЕ,причем информационный вход устройствасоединен с первым информационным входом перного регистра адреса, выходпервого регистра адреса соединен свходом первого дешифратора адреса,выход которого соединен с входом первого блока памяти, первый адресныйвыход первого блока памяти соециненс перным информационным входом буферного регистра, выход кода проверяемых логических условий первого блока памяти соединен с информационнымвходом регистра логических условий,выход которого соединен с .первым входом первого блока элементов И, выходпервого блока элементов И соединенс вторым информационным входом буферного регистра, выход Которого соединен с первым входом второго блока элементов И, выход которого соединен с вторым информационным входом первого регистра адреса, второй адресный выход первого блока памяти соединен с информационным входом первого счетчика адреса, выход которого соединен с входом второго дешифратора адреса, выход дешифратора адреса соединен с входом второго блока памяти, информационный выход которого соединен с первым информационным выходом устройства, вход кодов логических условий устройства соединен с вторым входом первого блока элементов И выход кода длины операционнойО последовательности первого блока па мяти соединен с информациочным входом счетчика микрокоманд, нулевые вы ходы которого соединены с входами первого элемента И, выход первого элемента И соединен с первыми входами второго и третьего элементов И и входом элемента НЕ, выход генератора тактовых импульсов соединен с первым входом четвертого элемента И и входом первого элемента задержки, выход которого соединен с вторым входом третьего элемента И и входом второго элемента задержки, выход которого соединен с вторым входом второго элемента И, выход второго элемента И соединен с вторым входом второго бло ка элементов И, выход элемента НЕ со единен с вторым входом чЕтвертого элемента И, выход которого соединен с синхронизирующим нходом второго дешифратора адреса, выход считывания микрокоманды второго блока памяти соединен с счетным входом первого счетчика адреса, выход третьего элемента И соединен с входами установкив нуль первого счетчика адреса, регистра логических условий, буферного регистра и синхронизирующим входом первого дешифратора адреса, управляющий вход первого блока памяти1092505 Составитель И.Сигаловедактор Л,Алексеенко Техред М,Кузьма Корректор п.пилипен Зака о д. 4/ илиал ППП Патент, г.ужгород, ул.Проектная,4 56/33 ВНИИПИ Госу по делам и 113035, Моск, Р 92 Ог,соединен с установкой в нуль первого регистра адреса, выход второго регистра адреса соединен с входом третьего дешифратора адреса, выход которого соединен с адресным входом блока памяти копий, о т л и ч а ющ е е с я тем, что, с целью повышения производительности, в устройст.во введены второй счетчик адреса, ., триггер, третий и четвертый блоки элементов И, элемент ИЛИ, шестой и седьмой элементы И и одновибратор, причем информационный вход устройства соединен с единичным входом триггера снятия копий, единичный выход которого соединен с первым входом пятого элемента И и управляющим входом третьего блокаеэлементов И, выход которого соединен с информационным входом блока памяти копий, выход окончания выдачи копий блока памяти копий соединен с. вторым выходом устройства и нулевым входом триггера управления, единичный выход которого соединен с первым входом шестого элемента И, выход генератора тактовых импульсов соединен с вторым входом шестого элемента И, выход которого соединен с первым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, выхоД элемента ИЛИ соединен с вхо-. дом разрешения записи блока памяти копий, нход кодов логических условий устройства соединен с единичным нхо 1Изобретение относится к автомати ке и вычислительной технике и может быть использовано в качестве устройства микропрограммного управления при построении вычислительных машин и систем, а также управляющих устройств н антоматиэированных системах управления технологическими процессами.Известны микропрограммные устройства управления, содержащие два блока памяти, регистры логических условий, счетчики, дешифраторы, регистры логические элементы И, НЕ, элементы задержки и генератор тактовых импуль.сов 1 - 3 . 15Недостатками укаэанных устройств являются ограниченные функциональные возможности и низкая производительность, которые обусловлены невозможностью управления двумя параллельно протекающими аналогичными процессами, один иэ которых по отношению к другому может быть сдвинут но времени. дом триггера выдачи копий и первым входом четвертого блока элементов И, выход которого соединен с информационным входом второго регистра адреса, нулевой выход триггера снятия копий соединен с перным входом седьмого элемента И, выход которого через одновибратор соединен с установочным входом второго счетчика адреса, выход второго счетчика адреса соединен с вторым входом четвертого блока элементов И, выход считывания микрокоманды второго блока памяти соединен с вторым входом элемента ИЛИ, нычитающим входом счетчика микрокоманд и с вторым входом пятого элемента И, выход которого соединен с счетным входом второго счетчика адреса, едикичкый выход триггера выдачи копий соединен с входом записи второго ре= .-истра адреса, син:ропиэирующим входом третьего дешифратора адреса и вторым входом седьмого элемента И выход скончания микропоограммы второго блока памяти соединен с первым выходом устройства, с едикичкьг входом триггера управления и нулевым входом триггера снятия копий выход)окончания выдачи копий блока памяти кОпий соедие с нулевым н:Одом триг - гера выдачи копий и устаовочкы входом второго регистра адреса, информационный выход блока хранения копи соединен с вторым выходом ус-ройстна. 2Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является микропрограмное устройство, содержацее первый и нторой блоки памяти, блок хранения копий, дна регистра адреса, регистр логических условий, буферный регистр, счетчик микрокомакд, первый счетчик адреса, первый, Второй и третий дешифратооы адреса, первый и второй блоки элементов И, триггер снятия копии триггер ньщачи копии, генератор тактовых импуль-. сон, пять элементов И, элемент НЕ, причем первый вход устройства соединен с первым информационным нходом первого регистра адреса, выход первого регистра адреса соедикек с входом первого дешифратора адреса, выход которого соединен с входом первого блока памяти, первый адресный вход первого блока памяти соединен с ервым информационным входом буферного регистра, выход кода проверяемых логических условий первого бло 1092505разнесено во времени. Например, управлять процессом передачи заранее сформированного массива кодов для нескольких абонентов при условии, что готовность нторого и,последующих абонентов к приему информации будет достигнута до момента окончания ее передачи первому абоненту. В такой ситуации известное устройство может реализовать указанные процессы толь-. ко н существенно последовательном режиме. Таким образом, это устройство имеет низкую производительность, об-, условленную большими потерями времени на ожидание окончания одного процесса и невозможностью управления параллельным выполнением двумя идентичными процессами, сдвинутыми но времени. Это существенно снижает функциональные возможности устройства и ограничивает область его применения,Бель изобретения - повышение производительности устройства.Поставленная цель достигается тем что н устройство, содержащее первый :и второй блоки памяти, блок паяти копий, два регистра адреса, регистр логических условий, буферный регистр, счетчик микрокоманд, первый счетчик адреса, первый, второй и третий дешифраторы адреса, первый и второй блоки элементов И, триггер снятия копий триггер выдачи копий, генератор тактовых импульсон,два элемента задержки и пять элементов И, элемент НЕ, причем информационный вход устройства соединен с первым информацйонным входом первого регистра адреса, выход первого регистра адреса соединен с входом первого дешифратора адреса, выход которого соединен с вхо-. дом первого блока памяти, первый ад 35 40 условий, буферного регистра и синхро 50 нонки н нуль первого регистра адреса,выход второго регистра адреса соеди нен с входом третьего дешифратора адреса, выход которого соединен с первым управляющим входом блока хранения копий 4).Недостатком этого устройства является низкая производительность, которая обусловлена возможностью управления только одним процессом, На практике возможны случаи, когда необходимо организовать контроль и управление двумя (или несколькими) идентичными процессами, начало которых 65 ка памяти соединен с информационнымвходом регистра логических условий,выход которого соединен с первымивходами первого блока элементов И,выход первого блока элементов И соединен с вторым информационным вхо-.,дом буферного регистра, выход которого соединен с первыми входами второго блока элементов И, выход которого соединен с вторым информационным входом первого регистра адреса,второй адресный выход первого блокапамяти соединен с информационнымвходом первого счетчика адреса, выход которого соединен с входом второго дешифратора адреса, выход дешифратора адреса соединен с входомвторого блока памяти, информационный выход которого соединен с первым выходом устройства, второй входустройства соединен с вторыми входами первого блока элементов И, выход кода длины операционной последовательности первого блока памятисоединен с информационным входомсчетчика микокоманд, нулевые выходы которого соединены с нходами первого элемента И, выход первого элемента И соединен с первыми входамивторого и третьего элементов И ивходом элемента НЕ, выход генераторатактовых импульсов соединен с первымнходом четвертого элемента И и входом первого элемента задержки, выход которого соединен с вторым входом третьего элемента И и входомвторого элемента задержки, выходкоторого соединен с вторым входомвторого элемента И; выход второгоэлемента И соединен с вторыми входами нторогс блока. элементов И, выход элемента НЕ соединен с вторымвходом четвертого элемента И, выход,которого соединен с синхронизирующим входом второго дешифратора адреса, первый управляющий выход второго блока памяти соединен со счетным входом первого счетчика адреса,выход третьего элемента И соединенс входами установки в нуль первогосчетчика адреса, регистра логических низирующим входом первого дешифратора адреса, управляющий выход первого блока памяти соединен с входом уста 5 10 15 20 25 30 ресный выход первого блока памяти соединен с первым информационным входомбуферного регистра, выход кода проверяемых логических условий первого блока памяти соединен с информационнымвходом регистра логических условий,выход которого соединен с первым входом первого блока элементов И, выходпервого блока элементов И соединенс вторым информационным входом буферного регистра, выход которого соединен с первым входом второго блокаэлементов И, выход которого соединенс вторым информационным входом первого регистра адреса, нторой адресный выход первого блока памяти соединен с информационным входом первогосчетчика адреса, выход которого соединен с входом второго дешифратораадреса, выход дешифратора адреса соединен с входом второго блока памяти,информационный выход которого соединен с первым информационным выходомустройства, вход кодов логических условий устройства соединен с вторымвходом первого блока элементов И, выход кода длины операционной последова 1092505тельности первого блока памяти соецинен с информационным входом счетчикамикрокоманд, нулевые выходы которогосоединены с входами первого элементаИ, выход первого элемента И соединенс первыми входами второго й третьегоэлементов И и входом элемента НЕ, выход генератора тактовых импульсовсоединен с первым входом четвертогоэлемента И и входом первого элементазадержки, выход которого соединен с 10вторым входом третьего элемента Ии входом второго элемента задержки,выход которого соединен с вторымвходом второго элемента И, выход второго элемента И соединен с вторым 5входом второго блока элементов И ныХод элемента НЕ соединен с вторымвходом четвертого элемента И, выходкоторого соединен с синхронизирующим входом второго дешифратора адре- щоса, выход считывания микрокомандывторого блока памяти соединен сосчетным входом первого счетчика адреса, выход третьего элемента И соединен с входами установки в нуль первого счетчика адреса, регистра логических условий, буферного регистраи синхронизирующим нходом первогодешифратора адреса, управляющийвход первого блока памяти соединенс нходом установки н нуль первогорегистра адреса, выход второго регистра адреса соединен с входом третьего дешифратора адреса, выход которого соединен с адресным входом блокапамяти копий, введены второй счетчик адреса, триггер, третий и четвертый блоки элементов И, элементИЛИ, шестой и седьмой элементы И,одновибратор, причем информационныйвход устройства соединен с единичным вхОдом триггера снятия копии,единичный выход которого соединенс первым входом пятого элемента Ии управляющим входом третьего блокаэлементов И, выход которого соединен с информационным входом блокапамяти копий, выход окончания выдачи копии блока памяти копий соединен с вторым выходом устройстваи нулевым входом триггера управления 50единичный выход которого соединен спервым входом шестого элемента И,выход генератора тактовых импульсонсоединен с вторым входом шестогоэлемента И, выход которого соединенс первым входом элемента ИЛИ, выходэлемента ИЛИ соединен с входом разрешения записи блока памяти копий,вход кодов логических условий устройстна соединен с единичным входомтриггера выдачи копий и первым нхо Одом четвертого блока элементов И, выход которого соединен с информационным нходом второго регистра адреса,нулевой выход триггера снятия копийсоединен с первым входом седьмого 65 элемента И, выход которого через однонибратор соединен с установочным нходом второго счетчика адреса,выход второго счетчика адреса соединен с вторым входом четвертого блокаэлементов И, выход считывания микрокоманды второго блока памяти соединен с вторым входом элемента ИЛИ,нычитающим входом счетчика микрокоманд и с вторым входом пятого элемента И, выход которого соединен сосчетным входом второго счетчика адреса, единичный выход триггера выдачикопий соединен с входом записи второго регистра адреса, синхронизирующимвходом третьего дешифратора адреса ивторым входом седьмого элемента И,выход окончания микропрограммы второго блока памяти соединен с первымвыходом устройства, с единичным входом триггера управления и нулевымвходом триггера снятия копий, выходокончания выдачи копий блока памятикопий соединен с нулевым входом триг.гера выдачи копий и установочнымвходом второго регистра адреса, информационный выход блока хранения копий соецинен с вторым выходом устройства,Сущность изобретения состоит нповышении производительности устройства путем Оперативного копированиялинейных последовательностей микрокоманд первого процесса и использования их копий для управления вторымпроцессом.Такая задача возникает н случае,когда процессы управления зачастую .описываются нерентабельными микропрограммами, что не позволяет одновременно использовать одну и ту же микропрограмму более, чем одному процессу.В случаях, когда реализуемые микропрограммы являются рентабельными,для обеспечения требуемой надежностиуправления технологическими процессами требуется предоставление каждомупроцессу индивидуальной копии микропрограммы,Общий принцип действия (дисциплинафункционирования) предлагаемого устройства состоит в следующем,При выполнении микропрограмм управления процессом П осуществляетсяих копирование (перезапись)в специальном оперативном блоке памяти сцелью последующего использования дляуправления идентичным процессом ППри этом емкость блока хранения копий может определяться самой длинноймикропрограммой, реализуемой привыполнении процесса (последовательности процессов) П1Управление процессами П и П организуется следующим образом.При выдаче микропрограммы дляуправления процессом П осуществля 1ется ее копирование в специальномблоке хранения копий и при поступлении запроса на управление процессом П выдается сформированная копия,Отличительными особенностями предлагаемой дисциплины функционирования является использование конве йерного принципа обработки и существенно асинхронное взаимодействие (порядок выполнения) процессов П и П 2.Принцип конвейерной обработки реа. лизуется за счет копирования выпол няемой микропрограммы и ее последующего использования для управления вторым процессом. При этом априори неизвестен момент прихода заявки на управление процессом П 2. Поэтому 15 копирование микропрограммы управления процессом П осуществляется с опреде 1ленным временным упреждением.Введение второго счетчика адреса и обусловленных им связей необходимо д для подсчета выданного количества микрокоманд и задания адреса ячейки в блоке хранения копий, по которому находится первая микрокоманда снятой копии. 25Введение третьего блока элементов И и обусловленных им связей позволяет (правлять передачей операционных микрокоманд с выхода второго блока памяти на вход блока хранения копий.Введение триггера управления, шестого элемента И, элемента ИЛИ и обусловленных ими связей позволяет управлять считыванием микрокоманд из блока хранения копий в то время, когда выдача линейной последовательности микрокоманд основного процесса из второго блока памяти закончена.Введение четвертого блока элементов И необходимо для перезаписи кода адреса первой микрокоманды в блоке 40 хранения копий при выдаче всей последовательности для управления. этот ф.так зчлтталлЛъл2 ДД- " -,Введение одновибратора, седьмого элемента И и обусловленных ими свя зей необходимо для организации обнуления счетчика адреса.Введение пятого элемента И и обус ловленных им связей позволяет определить адрес первой микрокоманды при 5 О снятии копии.На Фиг.1 представлена функциональная схема предлагаемого микропрограммного устройства; на фиг.2 функциональная схема блока хранения 55 копий; на Фиг. За,б,в - соответственно Форматы адресной микрокоманды первого запоминающего блока, операционной микрокоманды второго запоми" нающего блока и операционной микро команды блока хранения копий.Микропрограммное устройство управления содержит (фиг.1) перный 1 и второй 2 блоки памяти, блок 3 хранения копий, первый Регистр 4 адреса, 65 регистр 5 логических условий, буферный регистр 6, второй регистр 7адреса, счетчик 8 микрокоманд, перный счетчик 9 адреса, второй счетчик10 адреса, первый 11, второй 12 итретий 13 дешифраторы адреса, триггер 14 снятия копий, триггер 15 выдачи копий, триггер 16 управления,первый 17, второй 18, третий 19 ичетвертый 20 блоки элементов И, первый 21, второй 22, третий 23, четвертый 24, пятый 25, шестой 26 и седьмой27 элементы И, элемент ИЛИ 28, первый 29 и второй 30 элементы задержки,элемент НЕ 31, генератор 32 тактовыхимпульсов и одновибратор 33, первый34 и второй 35 входы устройства, первый 36 и второй 37 выходы устройства,перный адресный выход 38, выход 39кода проверяемых логических условий,второй адресный выход 40, выход 41кода длины операционной последователь.ности и управляющий выход 42 первогоблока 1 памяти, информационный выход 43, выход 44 считывания микрокоманды, выход 45 окончания ми,ропрограммы второго блока 2 памяти,адресный 46, информационный 47, разрешения записи 48 входы, информационный выход 49 и выход 50 окончаниявыдачи копии блока 3 хранения копий.Блок 3 памяти копий (фиг.2) содер-.жит группу регистров 51.1-51.п, коммутатор 52,Формат адресной микрокоманды(фиг,За) содержит поле кода (номераследующей последовательности (А),поле кода пронеряемых логических условий (Х), поле кода начального адреса текущей последовательности микрокоманд (А), поле длины линейнойпоследовательности микрокоманд (Ь)и поле метки (М) выдачи адресноймикрокоманды.Формат операционной микрокомандывторого запоминающего блока (фиг.Зб)содержит поле операционной микрокоманды (ПОМК), поле метки (идентификатора, считывания очередной микрокоманды (М 1) и поле метки (идентификатора,окончания процесса выдачи операционных микрокоманд (М 2).Формат операционной микрокомандыблока хранения копий (фиг.Зв) содержит дна поля: в первом поле находится кспия операционной микрокоманды(ПКОМК), но втором - метка окончанияпроцесса выдачи операционных микрокоманд (М 2).Рассмотрим назначение элементов устройства.Первый блок 1 памяти устройства предназначен для хранения адресных микрокоманд,В блоке 1 записывается адресная часть микрокоманды, которая считывается в следующем виде: с выхода 38номер следующей последовательности с выхода 3,9 - код проверяемых логических условий, с выхода 40 - начальный адрес текущей микрокоманды, с .Выхода 41 - число выполняемых микро- команд в текущей линейной последова ,тельности, с выхода 42 - сигнал сброса первого адресного регистра 4.Второй блок 2 памяти предназначен для хранения операционных последовательностей микрокоманд, 0Блок 3 хранения копий предназначен для оперативного хранения и Вьдачи на второй выход 37 устройства копии первого процесса.Первый регистр 4 адреса и первый дешифратор 11 адреса и соответствук- щие связи преднаэначе(т)ы для Выборки информации из блока .1,Регистр 5 логических условий предназначен для хранения кодов проверяемых логических условий.Первый блок элементов И 17 пред - назначен для модификации кода очередногс адреса адресной микрокоманды на буферном регистре б в зависимости ат кодов логических условий, поступающих с второго Входа 35 устройства и кода регистра 5 логических условий.13 торой блок элементов И 18 предназначен для управления перезаписью кода адреса сформированного в буферном регистре б, в первый регистр 4 адресагЕТЧИК Б МИКОКОМанД П СЕДа аДЛИ ЗаИСН ЧЛСЛа ОПЕРаЦОгНЫХ м.ИРРксманДг НОтОРьье Олжны быть эь.ф Даны с выхода вторОГО бгока тамЯти И ОС;,ЧЕС:ВЕНЯ КОНТСЛЯ ИХ ВЫДачиЕ Р ЬЬЙ Э".ЕМгз г 1 т 2 9 3 г 1 ДЕРл".К И И ТР Е - тий элемент И 23 и соотвс ств,1 вквле-четч ка вг РегистРа 5 логлческих холовй, буферного регистра 6 а таке фОгМИРОВаНИЯ УПРаВЛЯЮЩСГО С".Гнаа; - а чтене гдресной микрокглан:,г,: из пер зого блока 1 гамяти по адресу хранис;у В г:ервом адресном регистре 4.. Я :эрез Второй блок элю 1 ентов И 1 Я -е;: записью информации иэ буферного Регистра б: тервьЙ адресный ре ис р"тредназначен дЯ Выработки импухьсовтактовой частоты,Элемент 11 Б 31 уравляет рохожцзнием через четвертый элемент И 24тактовых импульсов для считываняиэ блока 2 операционных микрокомандпс адресу с первого счетчикгп 9 адреса,Триггер 14 управляет снятием коттиг пе(СВОГО ПРсцесса чеРез ТРетий блок элементов И 19 с выхода блока 2,а также формированием адреса первоймикрокоманды снятой копии через пятьтй элемент И 25.Триггер 1.5 управляет снятием копии с информационного выхода 49 блока 3 через третий дешифратор 13,Триггеры 14 и 15 являются Б-Я-триггерами с приоритетом по Я-входу,т,е. при одновременном поступлениисигналов на В и Я входы этих триггероя они переходят (остаются) в единичном состоянии.Бторой счетчик 10 адреса предназначен для указания глубины заполнения Операционнымл микрокомандамиблока 3.Бторой регистр 7 предназначен дляхранения адреса микрокоманды, с которой необходимо начать выдачу копиииэ блока 3 Занесетие информации иобнуление регистра 7 производитсятолько при нулевом потенциале иа егоуправляющем входе,Триггер 16 шестой элемент И 26,элемент ИЛИ 28 и соответствующие связи предназначены для организации выдачи копии из блока 3 по окончаниипроцесса выдачи последовательностиоперационных микрокоманд из блока 2,Одновибратор 33 седьмой элементИ 27, соответствующие связи осущестВляют приведение в исходное состоя-.ние второго счетчика адреса поокончании снятия копии.Рассмотрим назначение элементовблока 3 памяти копий (фиг., 2).1 руппгз лз и реистров 511-51.ппредставляет собой сверхоперативную ,в .амтгть и служит для хранения Операционных микрокоманд, постуаюшихьа Вход 4 Олока .Хотлмутатор 52 предназначен ДлЯвачи Операционной микрОкОманды сРЕГЛСТРа РУПЫ В КОТОРОМ НаХОдилась микрокоманда при поступлениизапроса на выдачу копии.При нулевом коде на входе 46 информация на выход коммутатора 52 непроходит,. При поступлении на вход 46КОДа 0 01 г КОТОРЫЙ СООТВЕТСТВУЕТисходному нулевому сотоянию реГистра 7, информация на выход коммутаторг 1 5 прохо ,.".-. с входа 47 г прн поступлении на Вход 46 кода 0010информация на выход коммутатора 52проходит с регистра 51.1 и т, д.Микропрограммное устройство длянтроля и управления двумя процес;ами может работать в двух режимах: режиме контроля и управления одним процессом и режиме контроля и управ- .ения двуля процессамиРежим контроля и управления двумя процессами может осуществляться путем снятия копии первого процесса (Ведущего) и выдачи копии для управления вторым процессом (ведомым) ли бо путем параллельной выдачи управляющей информации на оба процесса,В исходном состоянии все элементы памяти находятся в нулевом состоянии. Входы начальной установки элементов памяти на фиг.1-3 не показаны.В режиме контроля и управления одним процессом код (номер) операции поступает через вход 34 устройства в 10 регистр 4 адреса и задает начальный адрес в блоке 1.Счетчик 8 микрокоманд находится в нулевом состоянии, на нулевых выходах этого счетчика имеются высокие 15 потенциалы, которые поступают на элемент И 21, Сигнал с выхода элемента И 21 поступает на входы элементов И 22 и 23 и разрешает прохождение импульса с выхода генератора 32 через 2 первый элемент 29 задержки на вход обнуления счетчика 9, регистра 5 и буФерного регистра б, а также а управляющий вход первого дешифратсра 1125По сигналу, поступающему на управляющий вход первого дешифратара 11, по начальному адресу регистра 4 из блока 1 считывается код (номер следующей выполняемой линейной последовательности) который с выхода 38 поступает на вход регистра б. Код номера текущей выполняемой последовательности с выхода 40 блока 1 поступает на информационный вход перво го счетчика 9 адреса. Код проверяемых логических условий поступает с выхода 39 первого запоминающего блока 1 на вход регистра 5 логических условий. Кад длины линейной последовательности микрокаманд поступает 4 О на вход счетчика 8 с выхода 41 блока 1, Сигнал с выхода 42 блока 1 производит установку в нуль регистра4 адреса и подготавливает его для записи очередного адреса адресной микрокаманды.После считывания адресной части микрокоманды и записи в счетчик 8 кода числа микракоманд линейной последовательности показания счетчика 8 отличны ат нуля. Сигнал на выходе элемента И 21 принимает нулевое значение и через элемент НЕ 31 готовит элемент И 24 к прохождению через него импульсов с выхода генератора 32.Очередной тактовый импульс с выхода генератора 32 поступает на управляющий вход дешифратора 12 адреса, который производит выборку из блока 60 2 операционной микракоманды, начальный адрес которой был записан в счетчик 9. С информационного выхода 43 блока 2 считываются операционные микрокоманды на выход 36 устройства. После считывания очередной Операционной микракаманды с выхода 43 блока 2 с выхода 44 импульс считываниямикрокоманды поступает на счетныйвход счетчика 9 и изменяет (увеличивает) его содержимое на единицу. Одновременно с этим данный импульс считывания поступает ка вычитающий входсчетчика 9, уменьшая ега содержимоена единицу,Очередной тактовый импульс с выхода генератора 3 через элемент и24 поступает ка сйкхракизирующийвход дешифратара 12 адреса, так каксостояние счетчика 8 микракамакд отличка от улеваго и на выходе элемента И 21 будет сигнал, который через элемент НЕ 31 разрешает прохож-дение тактовых импульсов через элемент И 24",емифратар 12 адреса производит вы; ку очередной микракомады из блг. з 2 па адресу, сформированному в :.-.етчкке 9 адреса, Праисход,.т считыв:,в:е на выход 36 устройства Очереда,:. "перациакной микрокомакды. Аналоги.ым образам происходит счктываке Гавшихся аперациокых мккрокомад .ейнойтельасти.ПО сигналу выдали последей операциакай микракамакды линейкой последовательасти с выхода 44 блаха 2счетчик 8 микракамад обнуляется кка выходе элемента и 21 паявляетсксгкал, который через эемект НЕ 31запрещает пра.:аждеке тактовых импульс; в с выхода гекерагара 32 каэлемент И 24. Те Оамьм элемент И24 запрещает :чктывакйе аперацкаккых 1 икракамац яз блока 2.Тактовый импульс генератора 32,выла:.ый для Оттывакя последнейаперациаО м .крокомадылинейкойпоследовательасти, проходя черезпервый 29 и второй 30 элементы задержки с выхода элемента И 22, пас упае. ка второй вход блока элемента и 18. Адрес очередной ликейкайпоследовательности с выхода буферного регистра 6 через блок элементови 18 перепис;.ваегся в реги"тр 4 адресаКад адреса буферага регистра 6 состоит из постоянной и переменкой частей. Пос.таяная час.ь (базавьй адрес) записывается в буферный регистр 6 с выхода 38 первого блока 1 амяти. Перемекая часть када является мидкфйцирумой частью адреса в зависимости от кода логических усло. вий поступаю .1 х . второго входа 35 устрсйства. Поступающие логические условия модифицируют при ветвлении код каскенага адреса, записанного в буферном регистре 6, Сформированный -.аким образам код адреса в конце выдачи предыдл,ей линейкой последовагельО: ти мккаакомакд пересыла -Состояние счетчика 8 микрокоманд становится отличным от нулевого, и с выхода элемента И 21 сигнал эапре щает обнуление счетчика 9 адреса и перезапись информации из регистра б в регистр 4. Далее работа устройства происходит аналогично.В режиме контроля и управления двумя процессами управление двумя процессами заключается в снятии ко" пии первого процесса (ведущего) и выдачи ее второму (ведомому) процессу. При этом второй процесс может либо совпадать с первым (осуществляется параллельная выдача двух одинаковых последовательностей микрокоманд), либо не совпадать (осуществляется уп" равление процессами со сдвигом во времени). 60Для управления первым процессом операционные микрокомандывыдаются с информационного выхода 43 блока 2 и поступают на первый выход Зб устройства. 15 65 ется из буферного регистра б в регистр 4 адреса.Импульс считывания последней операционной микрокоманды линейной последовательности не успевает обнулить регистр 5 логических условий и буфер 5 ный регистр б (обнуление не должно быть проведено до тех пор, пока не произойдет модификация адреса в конце линейной последовательности), а также осуществить перезапись информа ции из буферного регистра б в регистр 4 адреса. Это объясняется тем, что время задержки первого элемента 29 задержки выбрано меньшим, чем время считывания операционной микрокоманды 5 из блока 2, а время задержки второго элемента 30 задержки выбрано большим времени считывания адресной микрокоманды из блока 1.Очередной тактовый импульс после 20 считывания последней операционной микрокоманды предыдущей линейной последовательности с выхода генератора 32 через первый элемент 29 задержки поступает на второй вход элемента И 23, Сигнал на первом входе элемента И И 23, соединенном с выходом элемента И 21 (после выдачи последней микрокоманды линейной последовательности состояние счетчика 8 микрокоманд будет нулевым и на выходе элемента И 21 будет высокий потенциал), разрешает прохождение тактового импульса для онуления регистра 5 логических условий, буферного регистра б и первого счетчика 9 адреса. Одновременно с этим данный импульс, постугая на синхронизирующий вход дешифратора 11 адреса, производит считывание очередной адресной микрокоманды из блока 1 по адресу, сформированному на регис тре 4 адреса,Сигнал на снятие копии первого процесса приходит с поступлением кода операции с входа 34 устройства на единичный вход триггера 14, Единичный выход триггера 14 разрешает снятие копии (последовательностей операционных микрокоманд) с информационного выхода 43 через блок элементов И 19 на информационный вход 47 блока снятия копий 3 (фиг.2).Идентификатор (метка) выдачи очередной операционной микрокоманды с выхода 44 блока 2, поступая через элемент ИЛИ 28 на синхронизирующие входы регистров 51.1-51,п, разреша.-, ет запись первой операционной микро- команды последовательности с входа 47 блока в регистр 51.1 группы регистров. Длительность импульса метки выбирается так, чтобы она не превышала времени срабатывания триггеров регистров 51.1-51.п, Кроме того, метка выдачи операционной микрокоманды с выхода 44 блока 2 через элемент И 25 поступает на счетный вход счетчика 10 адреса и увеличивает его состояние на единицу. Счетчик 10 адреса отслеживает глубину заполнения блока 3, т. е. определяет адрес первой микрокоманды выданной последовательности.При выдаче очередной микрокоманды с выхода 43 блока 2 идентификатор выдачи с выхода 44 через элемент ИЛИ 28 поступает на вход 48 блока 3 хранения копий. С входа 48 этот сигнал поступает на синхронизирующие входы группы регистров 51,1-51.п и осуществляет перезапись предыдущей микрокоманды из регистра51,1 в регистр 51,2, Поступившая микрокомандазаписывается в первый регйстр 51,1, Группа регистров 51.1-51.п можетбыть выполнена, например, на основе0-триггеров. Аналогичным образомблок 3 хранения копий заполнявсяоперационными микрокомандами по мереих выдачи с выхода 43 блока 2,Счетчик 10 адреса по мере поступления микрокоманд в блок 3 по идентификатору их выдачи считает их количество, определяя тем самым адрестого регистра группы 51.1-51.п, вкотором находится первая операционнаямикрокоманда снятой копии (счетчик10 адреса в этом случае выполняет роль указателя стека).При необходимости выдать снятую копию первого процесса для управления вторым процессом с входа 35 устройства поступает сигнал на выдачу копии на ециничный вход триггера 15 выдачи копий и на вход блока элементов И 20. Переключение триггера 15 по данному сигналу происходит после занесения информации в регистр 7, Это обеспечивается введением задержкисрабатывания триггера 15 по входу 8. Сигнал на снятие копии разрешает переписать информацию со счетчика 10 адреса в регистр 7 адреса. В этом слу чае регистр 7 адреса определяет через дешифратор 13 адреса тот регистр группы 51.1-51.п, в котором находится первая микрокоманда копии,Сигнал с выхода дешифратора 13 адреса поступает на соответствующий управляющий вход коммутатора 52, тем. самым коммутируя с выбранного регистра группы 52.1-51.п поступающую инфор-; мацию на выход 37 устройства для управления вторым процессом.15В том случае, когда процесс снятия копии закончился, а процесс выдачи, копии продолжается, по метке окончания микропрограммы с выхода 45 блока 2 триггер 16 управления переходит в Я) единичное состояние, разрешив тем самым прохождение тактовых импульсов с выхода генератора 32 через элемент И 26 и эЛемент ИЛИ 28 на синхронизирующие входы группы регистров 51.1- 25 51,п блока 3 снятия копий. Эти импульсы осуществляют сдвиг информации. и выдачу микрокоманд с того регистра, адрес которого был выбран регистром адреса по сигналу выдачи копии. Кро- ЗО ме того, по мере окончания микропрограммы основного процесса с выхода 45 блока 2 происходит обнуление триггера 14. По перепаду потенциала на нулевом выходе триггера 14 снятия копий на выходе одновибратора 33 появляется импульс. Этот импульс поступа,ет на вход установки в нуль счетчика10 адреса. Сдвиг между выдачей основ,ной микропрограммы и ее копии не может быть больше Итакта (микроко- .4 О манд), где Н - длина микропрограммы,Возможен случай, когда до окончания процесса снятия копии необходимо начать выполнение новой микропрограммы для управленияпервым процес -сом и снятия копии этой микропрограммы для управления вторым процессом. В этом случае с входа 34 устройства на информационный вход регистра 4 адреса заносится новый код операции, а сигнал на снятие копии поступает на единичный вход триггера 14. Далее работа устройства продолжается аналогичным образом. Однако в этом случае сигнал на выдачу второй копии должен поступить не ранее выдачи первой юзпии.При поступлении на регистр, с которого считывается информация, микрокоманды, содержйщей единичное значение метки М 2, на управляющем выходе 50 блока 3 появляется сигнал, характеризующий окончание выдачи копии. Сигнал окончания процесса выдачи копки поступает с выхода 50 на нулевой вход триггера 16 управления, на нулевой в 8 эд триггера 15 выда. чи копий и вход установки в нуль регистра 7 адреса. Если при этом на вход 35 поступает сигнал на продол-жение копирования следующей микропрограммы, то состояние триггера 15 . и регистра 7 не изменяется (триггер 15 имеет приоритет срабатывания по Я-входу и запрещает установку исходного кода в регистре 7). Если сигнал на снятие новой копии на вход 35 не поступает, то устройство находится в исходном состоянии и готово к работе в зависимости от начального кода, поступающего на информационный вход регистра 4 адреса с входа 34 устройства.При.необходимости выдачи копии параллельно с основным процессом сигнал на такой режим работы устройства подается с входом 34 и 35 устройства на единичные входы триггера 14 снятия копий и триггера 15 выдачи копий. На выходе дешифратора 13 адреса появляется сигнал. Данный сигнал, поступая на соответствующий управляющий вход коммутатора 52, разрешает прохождение операционных микрокоманд с входа 47 блока хранения копий на инФормационный выход 49 инего на второй выход 37 устройства.

СмотретьЗаявка

3549948, 08.02.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, КАЛЬНИЦКИЙ ВИКТОР ЛЕОНИДОВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 15.05.1984

Код ссылки

<a href="https://patents.su/11-1092505-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Умножитель частоты следования импульсов

Следующий патент: Устройство буферизации команд процессора

Случайный патент: Экстремальный регулятор для объектов с транспортным запаздыванием