Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1264172

Авторы: Безруков, Костинский, Рымарчук

Текст

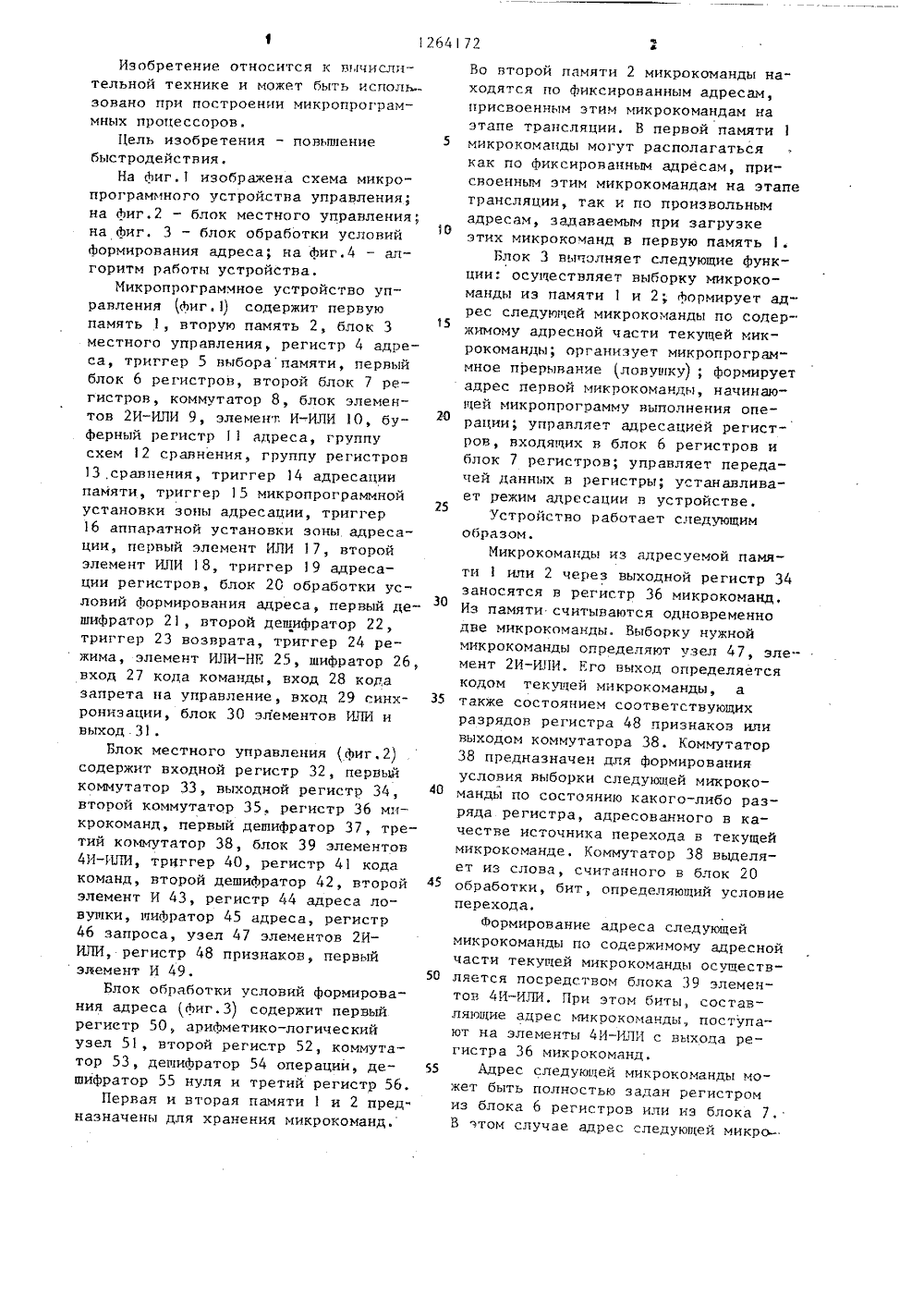

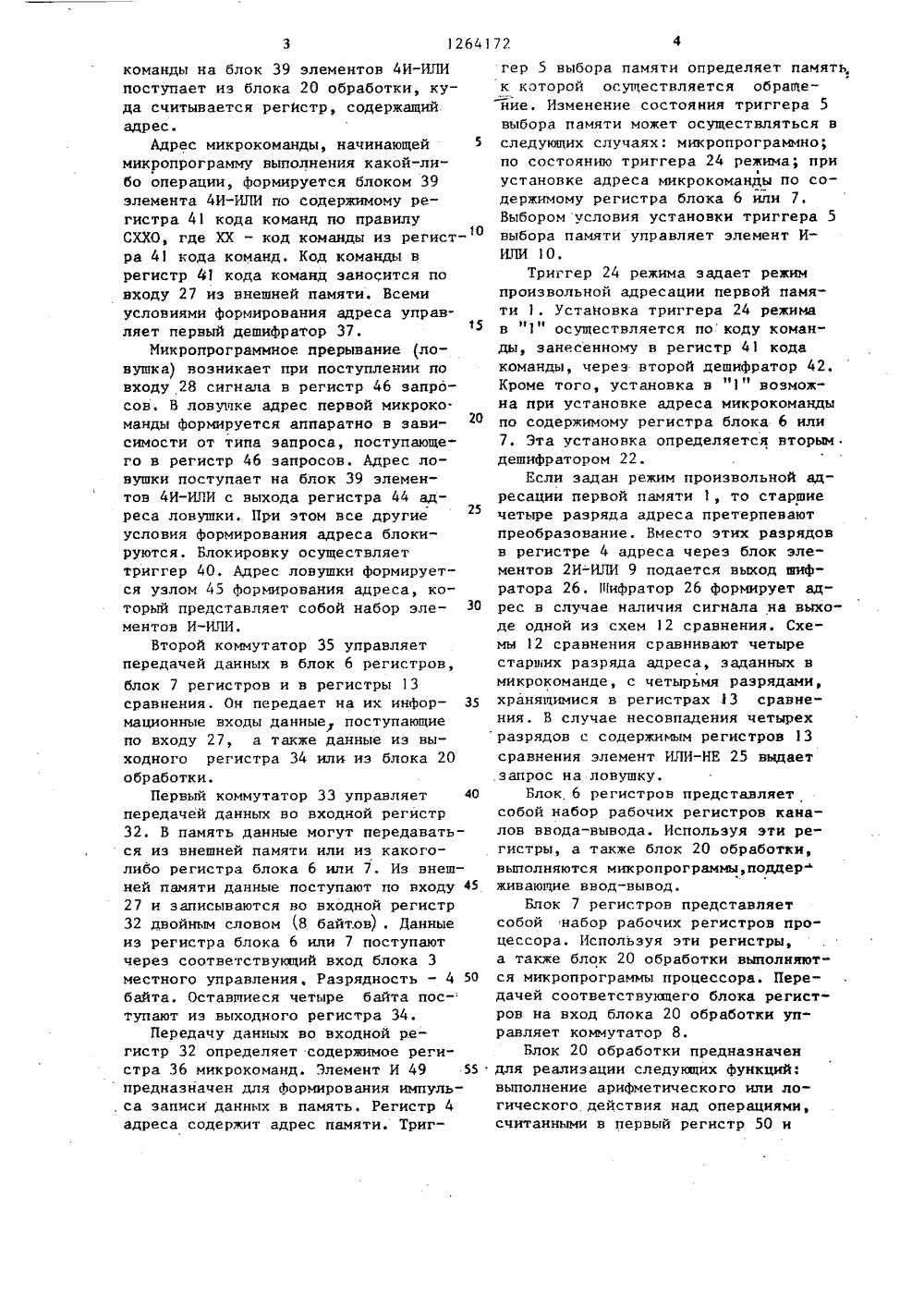

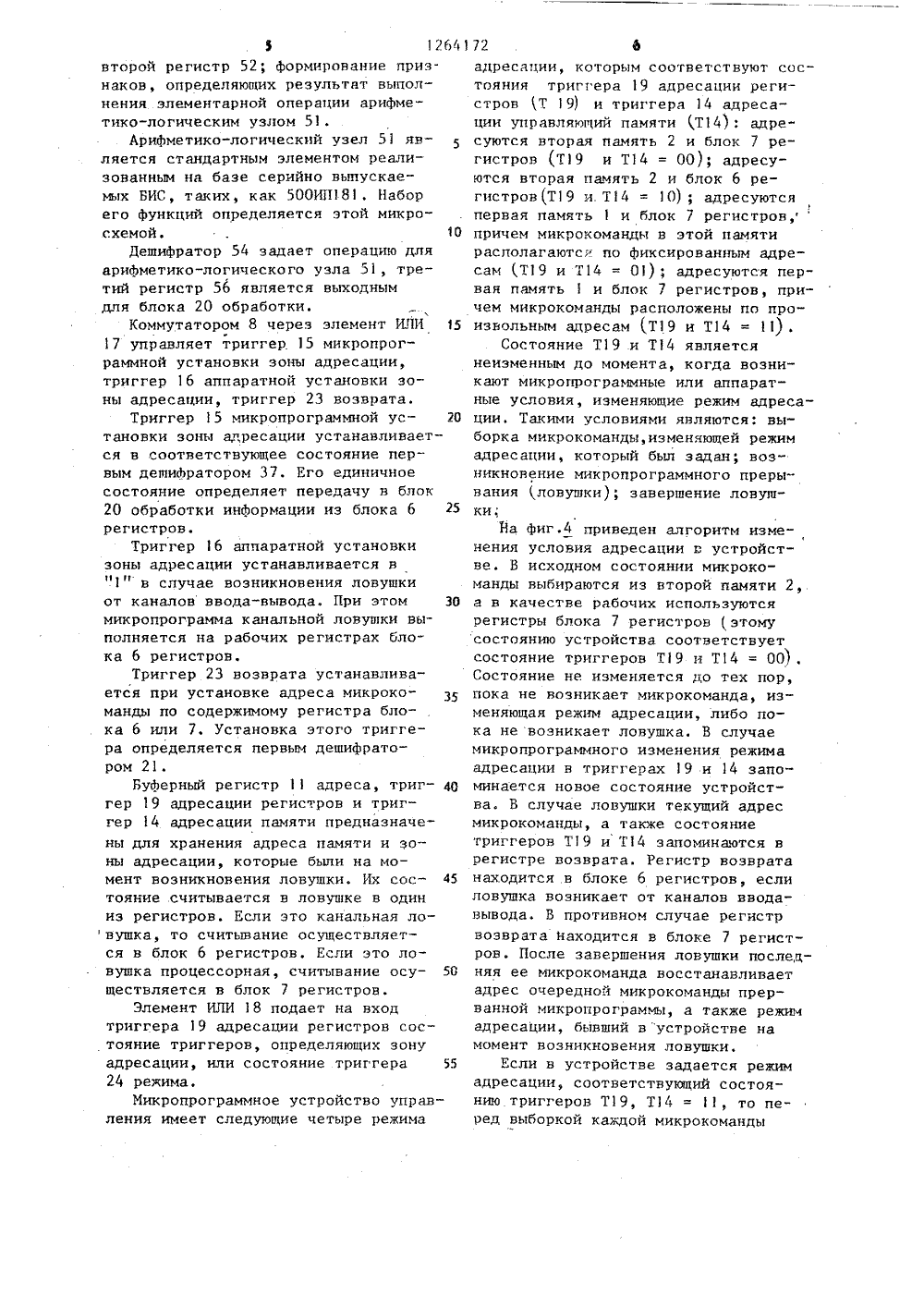

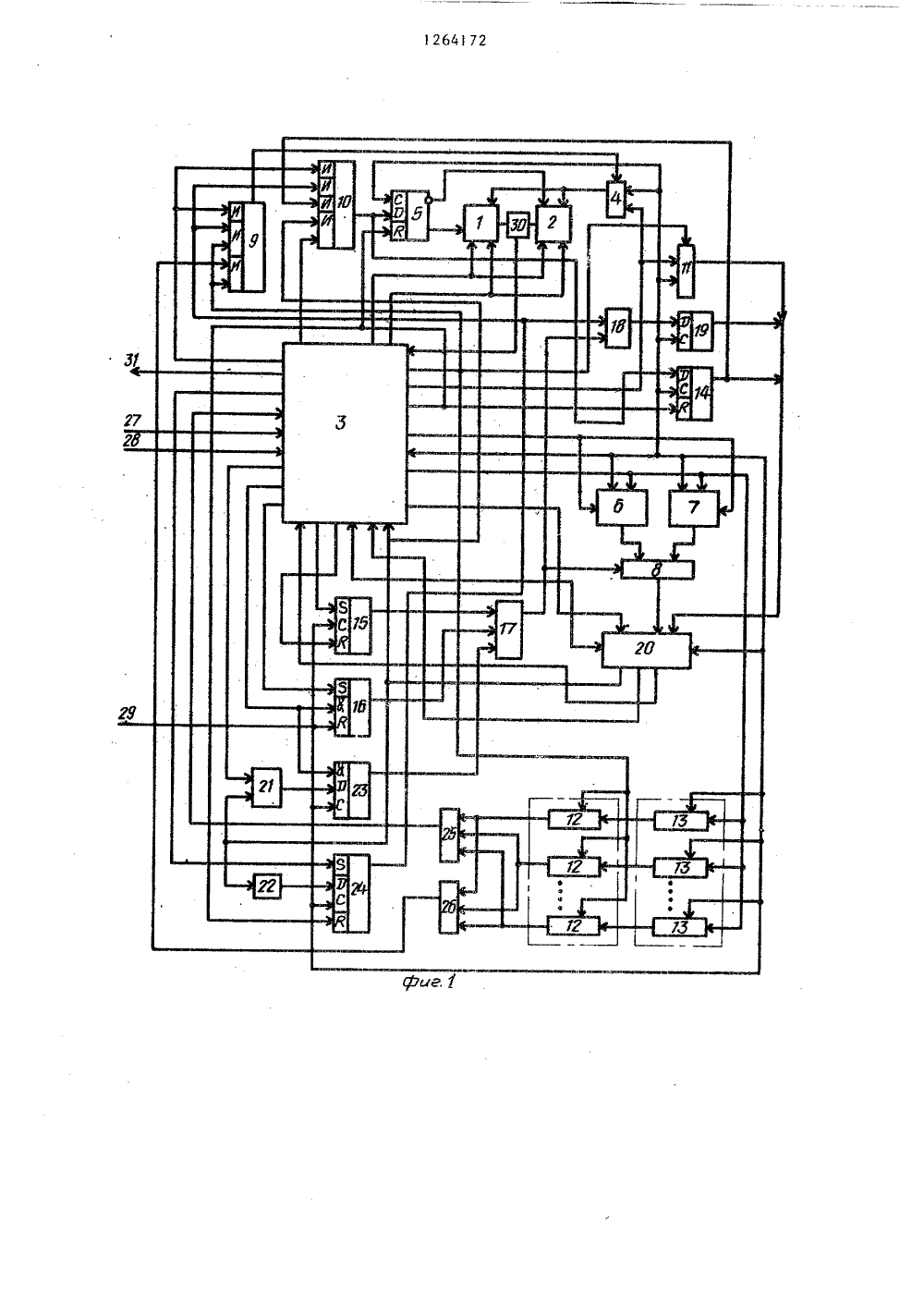

) (11 4 С 06 Г 9/22 Я АНИЕ ИЗОБРЕТ О ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССР У 760099, кл. С 06 Р 9/22, 1976.Патент США У 3643221, кл. С 06 Р 9/22, 1970.Авторское свидетельство СССР Ф 763898, кл. С 06 Г 9/22, 1976. (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ(57) Изобретение относится к вычис-лительной технике. Цель изобретения - повышение быстродействия. Микропрограммное устройство управления содержит первую и вторую память,блок местного управления, регистрадреса, буферный регистр адреса,шифратор, первый и второй дешифраторы, два блока регистров, блок условий формирования адресов, коммутатор, триггер выбора памяти, блокэлементов 2 И-ИЛИ, элемент И-ИЛИ, схе.мы сравнения, регистры сравнения,триггер адресации памяти, триггермикропрограммной установки зоны адресации, триггер аппаратной установки зоны адресации, первый ивторой элементы ИЛИ, триггер адресации регистров, триггер возврата,триггер режима, элемент ИЛИ-НЕ иблок элементов ИЛИ. 1 зп.ф-лы,4 ил.. Кас арда ректор А.Зимокосон/5 ушская наб. роизводственно-полиграФическое предприятие, г.ужгород, ул, Проектна 3/49 Тираж б 7 НИИПИ Государственн по делам изобрете 3035, Москва, Ж, Подписго комитета СССРий и открытийИзобретение относится к вычислительной технике и может быть исполь.зовано при построении микропрограммных процессоров.Цель изобретения - повышениебыстродействия,На Аиг. изображена схема микропрограммного устройства упранления;на Аиг.2 - блок местного управления;1 Она Аиг. 3 - блок обработки условииформирования адреса; на Аиг.4 - алгоритм работы устройства.Микропрограммное устройство управления (Аиг1) содержит первуюпамять 1, вторую память 2, блок 315местного управления, регистр 4 адреса, триггер 5 выборапамяти, первыйблок 6 регистров, второй блок 7 регистров, коммутатор 8, блок элементов 2 И-ИЛИ 9, элемент И-ИЛИ 10, бу 20ферный регистр 11 адреса, группусхем 12 сравнения, группу регистрон13,сравнения, триггер 14 адресациипамяти, триггер 15 микропрограммной25установки зоны адресации, триггер16 аппаратной установки зоны адресации, первый элемент ИЛИ 17, второйэлемент ИЛИ 18, триггер 19 адресации регистров, блок 20 обработки условий Аормирования адреса, первый де 30шифратор 21, второй дешифратор 22,триггер 23 возврата, триггер 24 режима, элемент ИЛИ-НЕ 25, шифратор 26,вход 27 кода команды, вход 28 кодазапрета на управление, вход 29 синхронизации, блок 30 элементов ИЛИ ивыход 31.Блок местного управления (Аиг.2)содержит входной регистр 32, первыйкоммутатор 33, выходной регистр 34, 4 Овторой коммутатор 35, регистр 36 микрокоманд, первый дешифратор 37, третий коммутатор 38, блок 39 элементов4 И-ИЛИ, триггер 40, регистр 41 кодакоманд, второй дешиАратор 42, второй 45элемент И 43, регистр 44 адреса ловушки, шиАратор 45 адреса, регистр46 запроса, узел 47 элементов 2 ИИЛИ, регистр 48 признаков, первыйэлемент И 49. 5 ОБлок обработки условий формирования адреса (Аиг.3) содержит первыйрегистр 50, ариАметико-логическийузел 51, второй регистр 52, коммутатор 53, дешиАратор 54 операции, дешифратор 55 нуля и третий регистр 56.Первая и вторая памятии 2 пред.назначены для хранения микрокоманд. Во второй памяти 2 микрокоманды находятся по Фиксированным адресам, присвоенным этим микрокомандам на этапе трансляции. В первой памяти 1 микрокоманды могут располагаться как по фиксированным адресам, присвоенным этим микрокомандам на этапе трансляции, так и по произвольным адресам, задаваемым при загрузке этих микрокоманд в первую память 1.Блок 3 выполняет следующие функции: осуществляет выборку микрокоманды иэ памяти 1 и 2; формирует адрес следующей микрокоманды по содержимому адресной части текущей микрокоманды; организует микропрограммное прерывание (ловушку); формирует адрес первой микрокоманды, начинающей микропрограмму ныполнения операции; управляет адресацией регистров, входящих в блок 6 регистров и блок 7 регистров; управляет передачей данных н регистры; устанавливает режим адресации и устройстве,Устройстно работает следующим образом.Микрокоманды из адресуемой памяти 1 или 2 через выходной регистр 34 заносятся н регистр 36 микрокоманд, Из памяти считываются одновременно дне микрокоманды. Выборку нужной микрокоманды определяют узел 47, элемент 2 И-ИЛИ, Его выход определяется кодом текущей микрокоманды, а также состоянием соответствующих разрядов регистра 48 признаков или выходом коммутатора 38. Коммутатор 38 предназначен для формирования условия выборки следующей микрокоманды по состоянию какого-либо разряда регистра, адресованного в качестве источника перехода в текущей микрокоманде. Коммутатор 38 выделяет из слова, считанного в блок 20 обработки, бит, определяющий условие перехода.Формирование адреса следующей микрокоманды по содержимому адресной части текущей микрокоманды осуществляется посредством блока 39 элементов 4 И-ИЛИ, При этом биты, составляющие адрес микрокоманды поступают на элементы 4 И-ИЛИ с выхода регистра 36 микрокоманд.Адрес следующей микрокоманды может быть полностью задан регистром из блока 6 регистров или из блока В этом случае адрес следующей микро-.25 команды на блок 39 элементов 4 И-ИЛИ поступает из блока 20 обработки, куда считывается регистр, содержащий. адрес.Адрес микрокоманды, начинающей микропрограмму выполнения какой-либо операции, формируется блоком 39 элемента 4 И-ИЛИ по содержимому регистра 41 кода команд по правилу СХХО, где ХХ - код команды иэ регист 10 ра 41 кода команд. Код команды в регистр 41 кода команд заносится по входу 27 из внешней памяти, Всеми условиями формирования адреса управляет первый дешифратор 37.Микропрограммное прерывание (ловушка) возникает при поступлении по входу 28 сигнала в регистр 46 запросов. В ловушке адрес первой микрокоманды формируется аппаратно в зависимости от типа запроса, поступающего в регистр 46 запросов. Адрес ловушки поступает на блок 39 элементов 4 И-ИЛИ с выхода регистра 44 адреса ловушки. При этом все другие условия формирования адреса блокируются. Блокировку осуществляет триггер 40, Адрес ловушки формируется узлом 45 формирования адреса, который представляет собой набор эле- ЗО ментов И-ИЛИ.Второй коммутатор 35 управляет передачей данных в блок 6 регистров, блок 7 регистров и в регистры 13 сравнения, Он передает на их инфор мационные входы данные, поступающие по входу 27, а также данные из выходного регистра 34 или из блока 20 обработки.Первый коммутатор 33 управляет 40 передачей данных во входной регистр 32В память данные могут передаваться иэ внешней памяти или из какого- либо регистра блока 6 или 7. Из внешней памяти данные поступают по входу 45 27 и записываются во входной регистр 32 двойным словом (8. байтов) . Данные из регистра блока 6 или 7 поступают через соответствующий вход блока 3 местного управления, Разрядность - 4 50 байта. Оставшиеся четыре байта пос- тупают иэ выходного регистра 34.Передачу данных во входной регистр 32 определяет содержимое регистра 36 микрокоманд. Элемент И 49 55 предназначен для формирования импульса записи данных в память, Регистр 4 адреса содержит адрес памяти. Триггер 5 выбора памяти определяет память, к которой осуществляется обращение. Изменение состояния триггера 5 выбора памяти может осуществляться в следующих случаях: микропрограммно; по состоянию триггера 24 режима; при6 установке адреса микрокоманды по содержимому регистра блока 6 или 7. Выбором условия установки триггера 5 выбора памяти управляет элемент ИИЛИ 1 О.Триггер 24 режима задает режим произвольной адресации первой памяти 1. Установка триггера 24 режима в "1" осуществляется по коду команды, занесенному в регистр 41 кода команды, через второй дешифратор 42. Кроме того, установка в "1" возможна при установке адреса микрокоманды по содержимому регистра блока 6 или 7. Эта установка определяется вторым дешифратором 22.Если задан режим произвольной адресации первой памяти 1, то старшие четыре разряда адреса претерпевают преобразование. Вместо этих разрядов в регистре 4 адреса через блок эле" ментов 2 И-ИЛИ 9 подается выход шифратора 26. Шифратор 26 формирует адрес в случае наличия сигнала на выходе одной из схем 12 сравнения. Схемы 12 сравнения сравнивают четыре старших разряда адреса, заданных в микрокоманде, с четырьмя разрядами, хранящимися в регистрах 3 сравнения, В случае несовпадения четырех разрядов с содержимым регистров 13 сравнения элемент ИЛИ-НЕ 25 выдает запрос на ловушку.Блок 6 регистров представляет собой набор рабочих регистров каналов ввода-вывода. Используя эти регистры, а также блок 20 обработки, выполняются микропрограммы,поддер живающие ввод-вывод.Блок 7 регистров представляет собой набор рабочих регистров процессора. Используя эти регистры, а также блок 20 обработки выполняются микропрограммы процессора. Передачей соответствукщего блока регистров на вход блока 20 обработки управляет коммутатор 8.Блок 20 обработки предназначен для реализации следующих функций: выполнение арифметического или логического действия над операциями, считанными в первый регистр 50 и3 12641 второй регистр 52; формирование признаков, определяющих результат выполнения элементарной операции арифметико-логическим узлом 51.Арифметико-логический узел 51 является стандартным элементом реализованным на базе серийно выпускаемых БИС, таких, как 500 ИП 181. Набор его функций определяется этой микросхемой. ОДешифратор 54 задает операцию для арифметико-логического узла 51, третий регистр 56 является выходным для блока 20 обработки.Коммутатором 8 через элемент ИЛИ 5 17 управляет триггер. 15 микропрограммной установки зоны адресации, триггер 16 аппаратной установки зоны адресации, триггер 23 возврата.Триггер 15 микропрограммной ус тановки зоны адресации устанавливается в соответствующее состояние первым дешифратором 37. Его единичное состояние определяет передачу в блок 20 обработки информации из блока 6 25 регистров.Триггер 6 аппаратной установки эоны адресации устанавливается в "1" в случае возникновения ловушки от каналов ввода-вывода. При этом 30 микропрограмма канальной ловушки выполняется на рабочих регистрах блока 6 регистров.Триггер 23 возврата устанавливается при установке адреса микрокоманды по содержимому регистра блока 6 или 7, Установка этого триггера определяется первым дешифратором 21.Буферный регистр 11 адреса, триг гер 19 адресации регистров и триггер 14 адресации памяти предназначены для хранения адреса памяти и Эоны адресации, которые были на момент возникновения ловушки. Их сос тояние считывается в ловушке в один из регистров. Если это канальная ловушка, то считывание осуществляется в блок 6 регистров, Если это ловушка процессорная, считывание осу ществляется в блок 7 регистров.Элемент ИЛИ 18 подает на вход триггера 19 адресации регистров состояние триггеров, определяющих зону адресации, или состояние триггера 55 24 режима,Микропрограммное устройство управления имеет следующие четыре режима адресации, которым соответствуют состояния триггера 19 адресации регистров (Т 19) и триггера 14 адресации управляющий памяти (Т 14): адресуются вторая память 2 и блок 7 регистров (Т 9 и Т 14 = 00); адресуются вторая память 2 и блок 6 регистров(Т 19 и Т 14 = 10); адресуются первая память 1 и блок 7 регистров,причем микрокоманды в этой памяти располагаютс". по фиксированным адресам (Т 19 и Т 14 = О); адресуются первая память 1 и блокрегистров, причем микрокоманды расположены по произвольным адресам (Т 19 и Т 14 = 11) .Состояние Т 19 и Т 14 являетсянеизменным до момента, когда возникают микропрограммные или аппаратные условия, изменяющие режим ацресации. Такими условиями являются: выборка микрокоманды,изменяющей режимадресации, который был задан; возникновение микропрограммного прерывания (ловушки); завершение ловушки;Йа фиг.4 приведен алгоритм изменения условия адресации в устройстве. В исходном состоянии микрокоманды выбираются из второй памяти 2,а в качестве рабочих используютсярегистры блока 7 регистров (этомусостоянию устройства соответствуетсостояние триггеров Т 19 и Т 14 = ОО),Состояние не изменяется до тех пор,пока не возникает микрокоманда, изменяющая режим адресации, либо пока не возникает ловушка. В случаемикропрограммного изменения режимаадресации в триггерах 19 и 14 запоминается новое состояние устройства. В случае ловушки текущий адресмикрокоманды, а также состояниетриггеров Т 19 и Т 4 запоминаются врегистре возврата. Регистр возвратанаходится в блоке 6 регистров, еслиловушка возникает от каналов вводавывода, В противном случае регистрвозврата находится в блоке 7 регистров. После завершения ловушки последняя ее микрокоманда восстанавливаетадрес очередной микрокоманды прерванной микропрограммы, а также режимадресации, бывший в "устройстве намомент возникновения ловушки,Если в устройстве задается режкчадресации, соответствующий состоянию триггеров Т 19, Т 14 = 11, то перед выборкой каждой микрокомандыпроверяется наличие первой памяти 1,Если содержимое одного из регистров13 сравнения не совпадает с че,.тырьмя старшими разрядами адреса мик,рокоманды, возникает ловушка. Эта 5ловушка запоминает адрес этой микрокоманды, а также состояние триггеров Т 19, Т 4 = 11, и устанавливаетустройство в состояние Т 19, Т 4 = 00.В ловушке в свободный регистр 13 10сравнения загружается адрес этоймикрокоманды. В первую память 1 загружается группа микрокоманд, старшие четыре разряда адреса которыхсовладаютс содержимым регистра 13 15сравнения, Иикрокоманды загружаютсяиз оперативной памяти. Последнеймикрокомандой ловушки восстанавливается адрес прерванной микрокоманды,а также режим, соответствующий Т 19, 20Т 14 = 11. Адрес очередной микрокоманды вновь сравнивается с содержимым регистров 13 сравнения, но теперь шифратор 26 выдает номер регистра, в котором произошло сравнение. 25Этот номер заносится в регистр 4адреса и является адресом очередноймикрокоманды,Все режимы адресации устройствамикропрограммного управления завер- ЗОшаются переходом в состояние, соответствующее Т 19,Т 14 = 00. Формула изобретения351. Микропрограммное устройство управления, содержащее первую и вторую память, регистр адреса, буферный регистр адреса, шифратор, первый и второй дешифраторы, два блока регистров, блок элементов ИЛИ, блок обработки условий формирования адреса и блок местного управления, содержащий входной регистр, выходной регистр, два элемента И, регистр 45 признаков, три коммутатора, регистр кода команд, регистр микрокоманд, первый и второй управляющие дешифраторы, шифратор адреса, узел элементов 2 И-ИЛИ и узел элементов 4 И-ИЛИ, причем адресные входы первой и второй памяти соединены с выходом регистра адреса, вход синхронизации устройства соединен с синхровходами блока обработки условий формирования;55 . адреса, первого и второго блоков регистров регистра адреса, буферного регистра адреса, регистра признаков входного и выходного регистров, регистра кода команд и .регистра микрокоманд, стробирующим входом второго управляющего дешифратора и с первыми входами первого и второго элементов И, вход кода команды устройства соединен с первыми йнформационными входами первого и второго коммутаторов и информационным входом регистра кода команд, входы записи и информационные входы первой и второй памяти соединены соответственно с выходом первого элемента И и выходом входного регистра, информационный вход которого соединен .с выходом первого коммутатора, второй информационный вход которого соединен с первым информационным входом третьего коммутатора и с первым информационным входом блока обработки условий формирования адреса, управляющий вход третьего коммутатора соединен с управляющим входом первого коммутатора, с выходом поля местного управления регистра микрокоманд и входом первого управляющего дешифратора, первый, второй и третий выходы которого соединены соответствено .с первыми входами первой, второй и третьей групп узла элементов 4 И-ИЛИ, первый выход которого соединен со старшими разрядами информационного входа буферного регистра адреса, младшие разряды Информационного входа которого соединены с младшими разрядами информационного входа регистра адреса, с вторым выходом узла элементов 4 И-ИЛИ, с выходом узла элементов 2 И-ИЛИ и с первым информационным входом регистра микрокоманд, выход поля адреса которого соединен с вторым входом первой группы узла элементов 4 И-ИЛИ, второй вход второй группы которого соединен с выходом регистра кода команд и с информационным входом второго управляющего дешифратора, второй вход третьей группы узла элементов 4 И-ИЛИ соединен с вторым информационным выходом блока обработки условий формирования адреса, с информационным входом первого дешифратора и с входом второго дешифратора, ,четвертый и пятый выходы первого уд равляющего дешифратора соединены соответственно с первым входом первой и второй групп узла элементов 2 И-ИЛИ50 вторые входы первой и второй групп которого соединены соответственно с выходами третьего коммутатора и Ре-,- гистра признаков, информационный вход которого соединен с выходом 5 признаков результата блока обработки условий формирования адреса, выход результата которого соединен с вторым информационным входом второ10 го коммутатора, третий информационный вход которого соединен с третьим информационным входом первого коммутатора, с вторым информационным входом регистра микрокоманд и с15 выходом выходного регистра, выход поля управления обработкой условий формирования адресарегистра микро- команд соединен с входом кода операции блока обработки условий Формирования адреса, первый информационный вход которого соединен с выходом коммутатора, первый и второй информационные входы которого соединены соответственно с выходами первого и25 второго блоков регистров, информационный вход и вход номера регистра которых соединены с соответствующими разрядами выхода второго коммутатора, управляющий вход которого соединен с шестым выходом первого управляющего дешифратора, седьмой выход которого соединен с вторым входом первого элемента И, восьмой выход первого управляющего дешифратора соединен с входами записи пер вого и второго блоков регистров, выходы первой и второй памяти через блок элементов ИЛИ соединены с информационными входами выходного Регистра, о т л и ч а ю щ е е с я 40 тем, что, с целью повышения быстро - действия, в него введены триггер выбора памяти, блок элементов 2 ИИЛИ, элемент И-ИЛИ, группа схем сравнения, группа регистров сравнения, 45 триггер адресации памяти, триггер микропрограммной установки зоны адресации, триггер аппаратной установки зоны адресации, первый и второй элементы ИЛИ, триггер адресации регистров, триггер возврата, триггер режима и элемент ИЛИ-НЕ; в блок местного управления введены регистр запроса, регистр адреса ловушки и триггер, причем выход буферного ре гистра адреса и выходы триггера адреса регистров и триггера адреса памяти поразрядно соединены с вторым информационным входом блока обработки условий Формирования адреса, выход триггера адреса памяти соединен с первым входом элемента И-ИЛИ., второй и третий входы которого соединены соответственно с вторым информационным выходом блока обработки условий Формирования адреса и девятым выходом первого управляющего дешифратора, десятый выход которого соединен с первым входом блокаэлементов 2 И -ИЛИ и четвертым входом элемента И-ИЛИ, пятый вход которого соединен с вторым входом блока элементов 2 И-ИЛИ, первым входом второго элемента ИЛИ и выходом триггера режима, вход установки в"1" и инФормационный вход которого соединены соответственно с выходами второго управляющего дешифратора и второго дешифратора, третий, и четвертый входы блока элементов 2 И-ИЛИ соединены с первыми входами схем срав-, нения группы и с первым выходом узла элементов 4 И-ИЛИ, третьи входы первой и третьей групп которого соединены с инверсным выходом триггера и входами установки в "О" триггера адреса памяти, триггера выбора памяти и триггера Режима, синхровход которого соединен с синхровходами триггера выбора памяти, триггера адресации регистров, триггера адресации памяти, регистров сравнения группы, триггера возврата, регистра запроса, регистра адреса ловушки триггера микропрограммной установки зоны адресации, выходом синхронизации устройства и первым входом установки в "О триггера аппаратной установки зоны адресации., второй вход установки в "О" которого соединен с первым информационным входом триггера возврата и одиннадцатым выходом первого управляюшего дешифратора, двенадцатый выход которого соединен со стробирующим входом первого дешифратора, выход которого соединен с вторым информационным входом триггера возврата, выход которого соединен с первым входом первого элемента ИЛИ второй и третий входы которого соединены соответственно с выходами триггера аппаратной установки зоны адресации и триггера микропрограммной установки зоны адресации, вход установки в"1" и вход установки вО которого соединены с оо тв е тств ен 264172но с тринадцатым и" четырнадцатымвыходами первого управляющего дешифратора, вход установки в "1" тригге -.ра аппаратной установки зоны адресации соединен с выходом второгоэлемента И, второй вход которогосоединен с прямым выходом триггераи первым входом четвертой группыузла элементов 4 И-ИЛИ, второй входчетвертой группы которого соединенс выходом регистра адреса ловушки,информационный вход которого соединен с первым выходом шифратора адреса, второй и третий выходы которогосоединены соответственно с информационным входом триггера и третьимвходом второго элемента И, вход шиф 1 О 15 ратора адреса соединен с выходом регистра запросов, первый разряд информационного входа которого соеди 20 нен с выходом элемента ИЛИ-НЕ, остальные разряды информационного вхо да регистра запроса соединены с входами кода запроса на управление25 устройства, входы элемента ИЛИ-НЕ соединены с одномоментными входами шифратора и с выходами схем сравнения группы, вторые входы которых соединены с выходами одноименных регистров сравнения группы, информационные входы. которых соединены с выходами второго коммутатора, выход шифратора соединен с пятым входом блока элементов 2 И-ИЛИ, выход которого соединен со старшими разрядами информационного входа регистра адреса, выход элемента И-ИЛИ соединен с информационными входами триггера адресации памяти и триггера выбора памяти, прямой и инверсный вы О ходы которого соединены соответст- . венно с входами выборки первой и второй памяти, выход первого элемента ИЛИ соединен с управляющим входом коммутатора и вторым входом вто рого элемента И 1 И 1, выход которогосоединен с информационным входомтриггера адресации регистров. 2. Устройство по и.1, о т л ич а ю щ е е с я тем, что блок обработки условий формирования адреса содержит три регистра, дешифратор операций, арифметика-логический узел, дешифратор нулей и коммутатор, причем первый информационный вход блока подключен к первому информационному входу коммутатора, второй информационный вход которого соединен с информационным входом первого регистра и подключен к второму информационному входу блока, синхровход блока подключен к синхро- входам первого, второго и третьего регистров, выход первого регистра соединен с первым информационным входом арифметика-логического узла и подключен к первому информационному выходу блока, вход кода операции блока подключен к входу дешифратора операции, первый и второй выходы которого соединены соответственно с управляющим входом коммутатора и входом кода операции арифметико-логического узла, выход результата которого соединен с информационным входом третьего регистра и вхоцом дешифратора нулей, выход которого объединен с выходом признака результата арифметико-логического узла и подключен к выходу признака результата блока, выход третьего регистра подключен к выходу результата блока, выход коммутатора соединен с информационным вкодом второго регистра, выход которого соединен с вторым информационным входом арифметико-логического узла и подключен к второму информационному выходу блока.

СмотретьЗаявка

3723911, 11.04.1984

ПРЕДПРИЯТИЕ ПЯ М-5339

КОСТИНСКИЙ АРКАДИЙ ЯКОВЛЕВИЧ, БЕЗРУКОВ ВЛАДИМИР АЛЕКСАНДРОВИЧ, РЫМАРЧУК АЛЕКСАНДР ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.10.1986

Код ссылки

<a href="https://patents.su/10-1264172-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Программное устройство управления

Следующий патент: Устройство для распределения заданий процессорам

Случайный патент: Устройство для прядения искусственной оболочки