Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

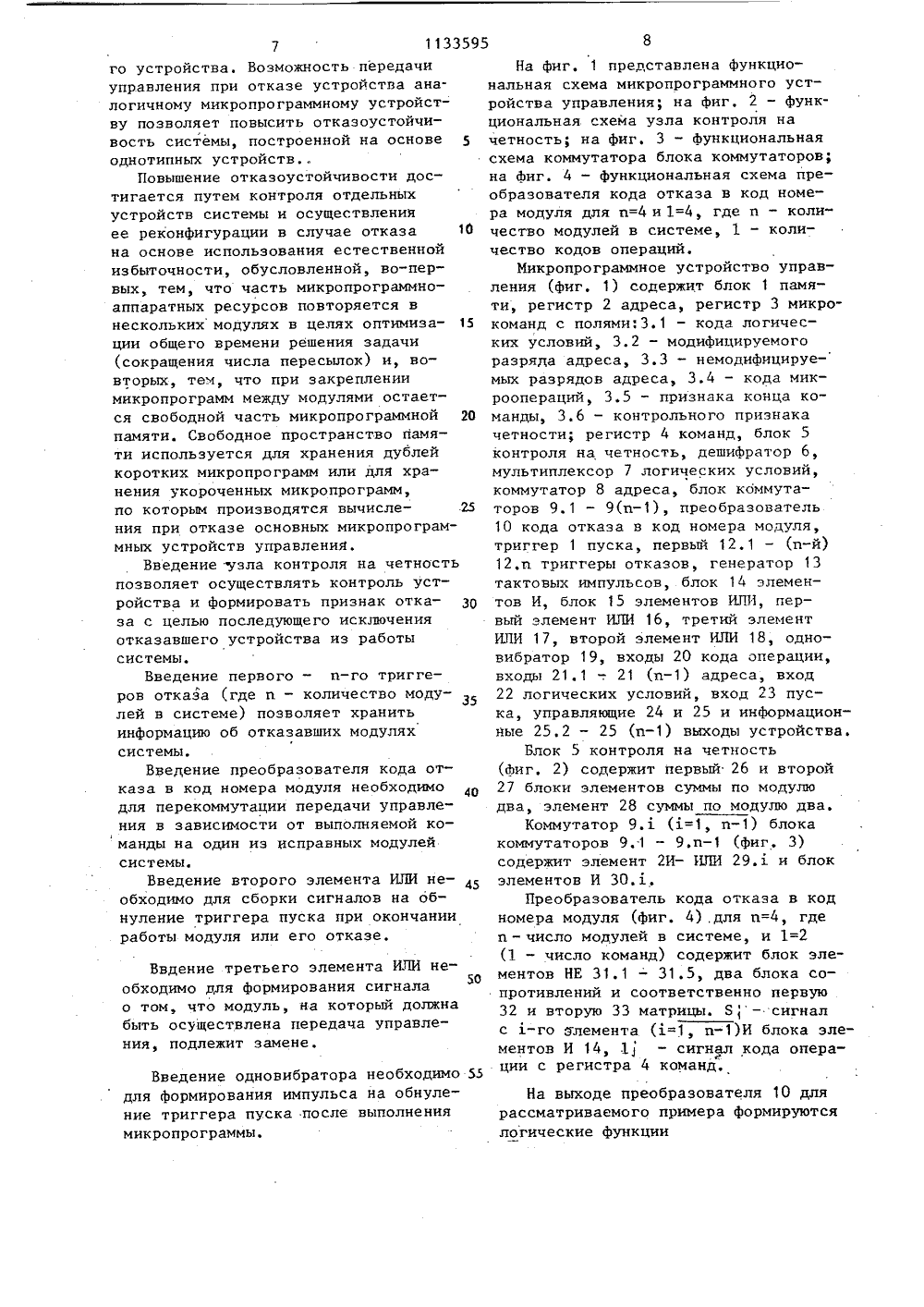

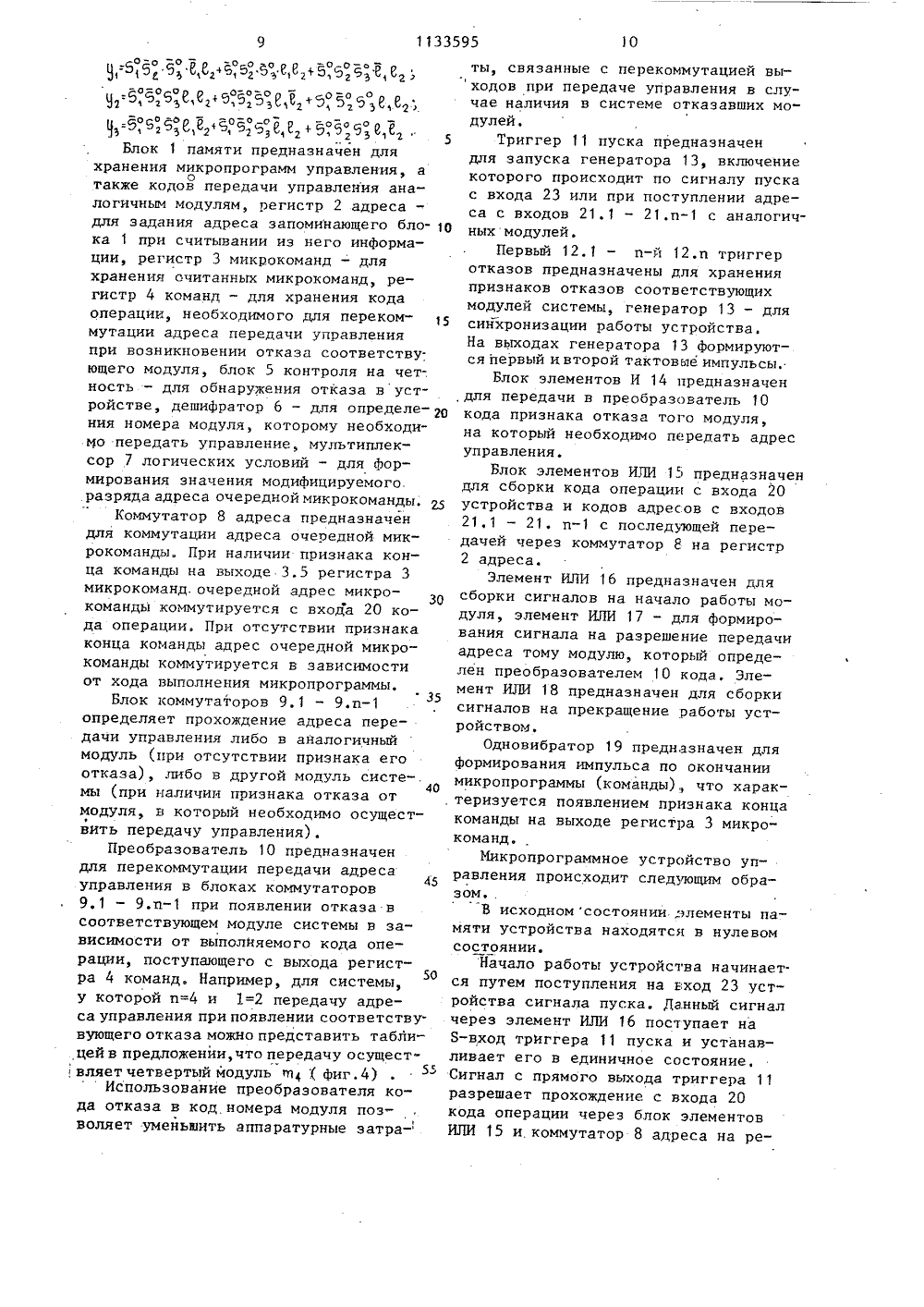

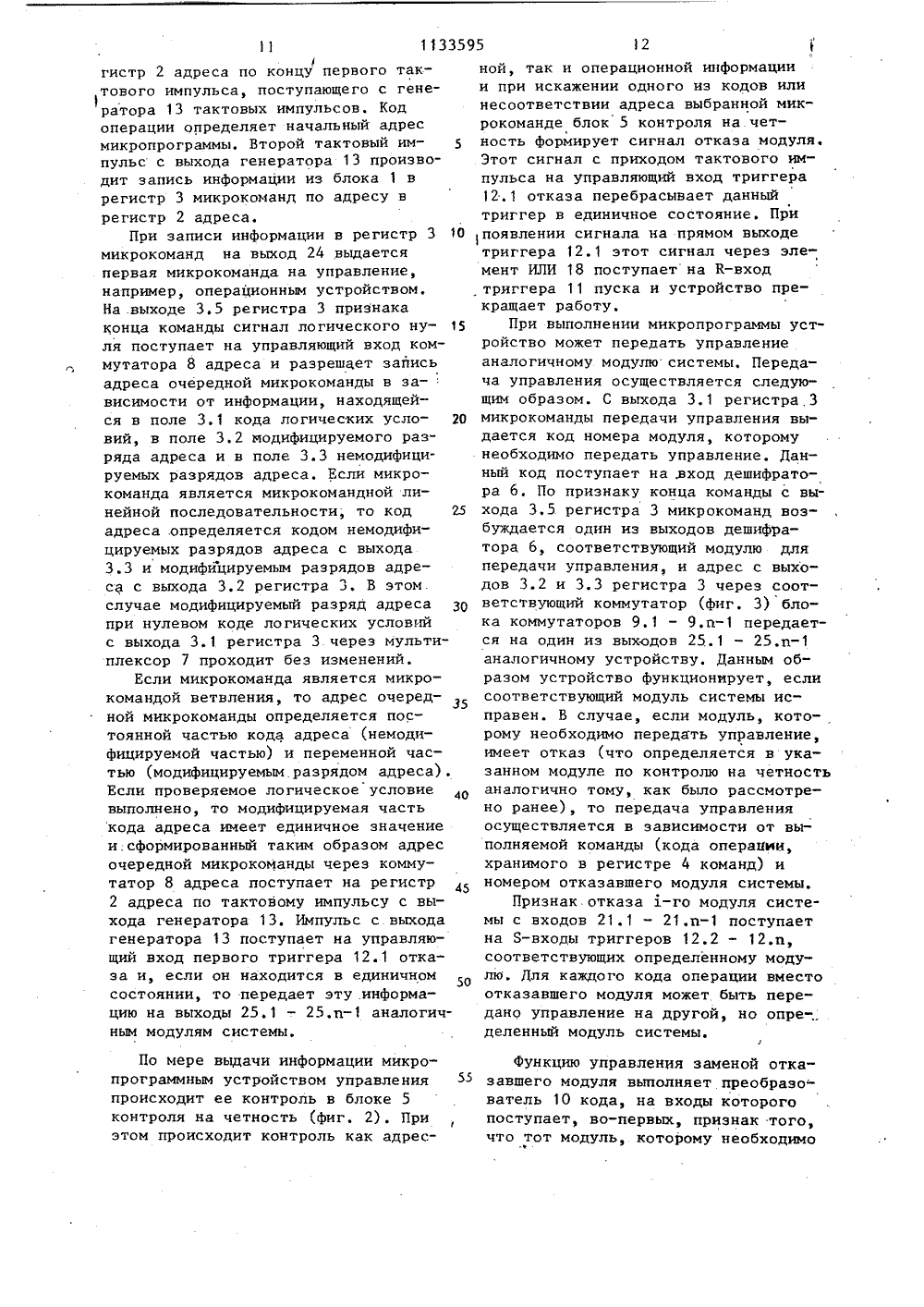

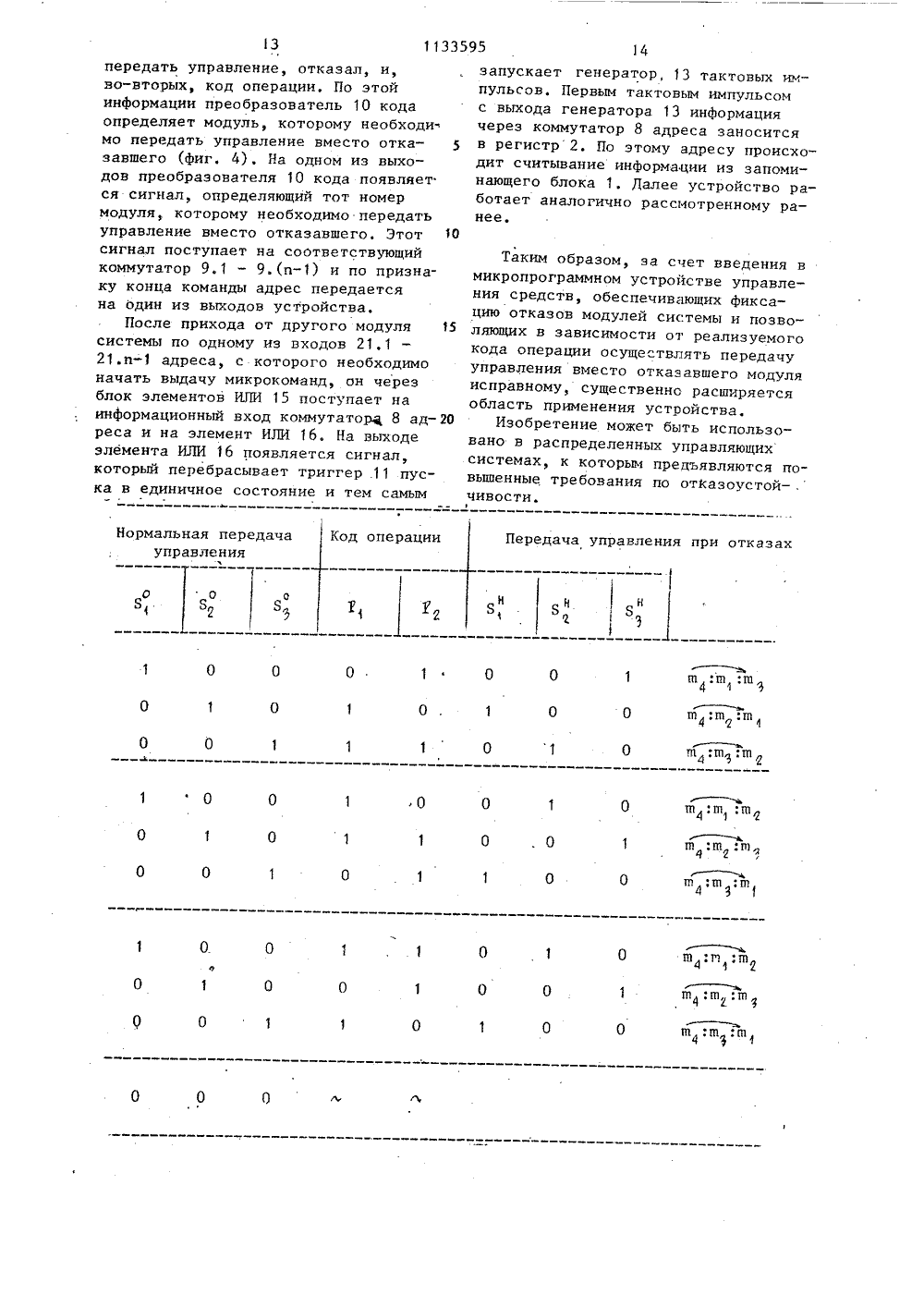

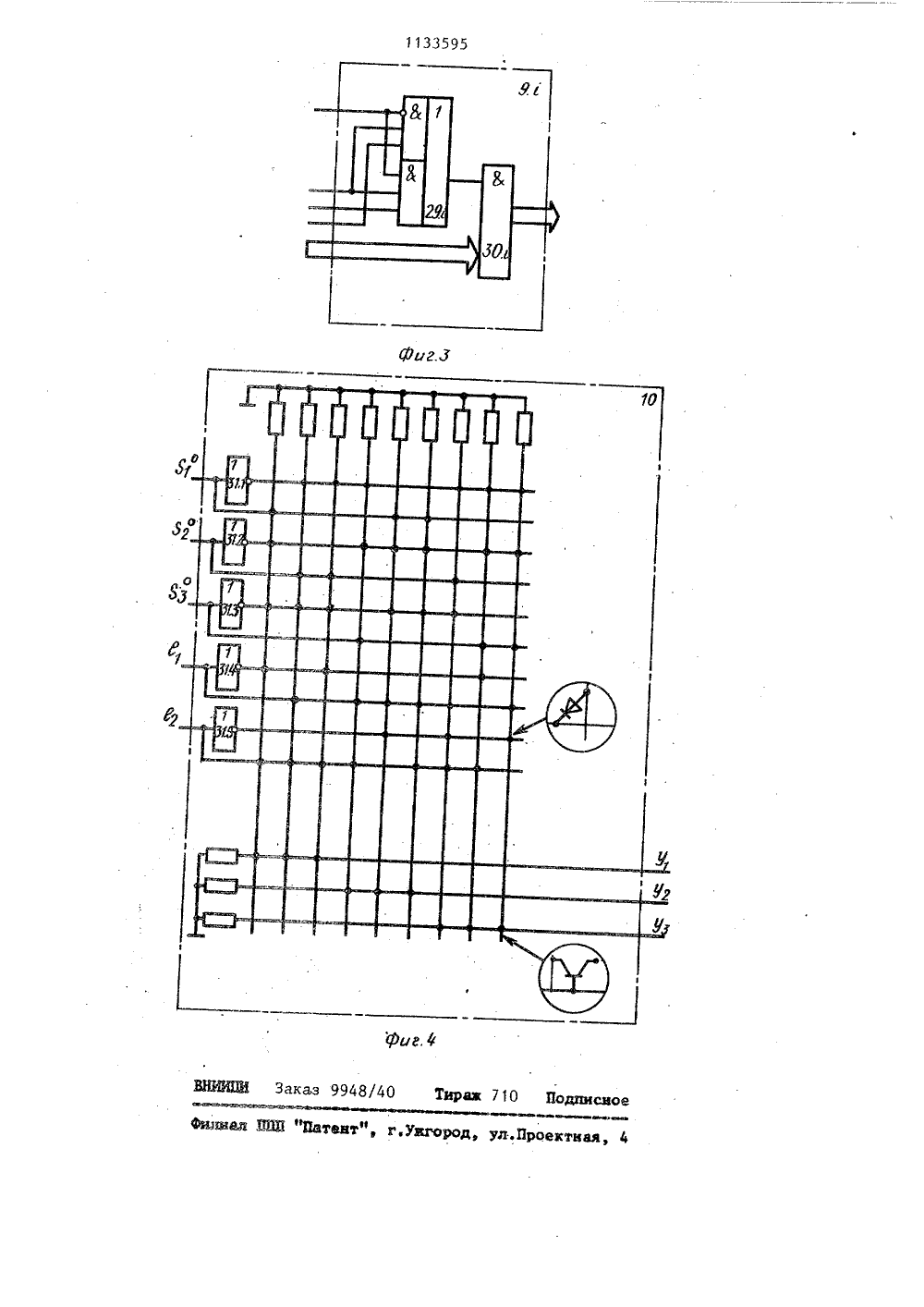

(19) (И) 4(51) С 06 Р 9/22 С 06 Р 11/00 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРпо делАм изОБРетений и ОтнРытий МЗОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) 1, Авторское свидетельство СССР217006, кл. С 06 Р 9/22, 1967.2. Авторское свидетельство СССР474806, кл. С 06 Р 9/22, 1975.3, Авторское свидетельство СССР596947, кл. С 06 Р 9/22, 1978. (54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти,регистр адреса, регистр команд, .регистр микрокоманд, дешифратор, мультиплексор логических условий, коммутатор адреса, триггер пуска., генератор тактовых импульсов, блок коммутаторов, блок элементов И, блок элементов ИЛИ,.первый элемент ИЛИ, причем выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с входом блока памяти, выход блока памяти соединен с информационным входом регистра микрокоманд, выход кода логических условий регистра микрокоманд соединен с управляющим входом мультиплексора логических условий и входом дешифратора, выход модифицируемого разряда адреса регистра микрокоманд соединен с первым информационным входом мультиплексора логических условий, выходы немодифицируемых разрядов адреса регистра микрокоманд соединены с первым информационным входом коммута тора адреса и группой информационных входов блока коммутаторов, выход микроопераций регистра микрокомандявляется управляющим выходом устройства, выходы дешифратора соединены с первой группой управляющих входов блока коммутаторов, выходы которых являются информаЦиОнными выходами устройства, выход мультиплексоралогических условий соединен с входом модифицируемого разряда адресапервого информационного входа коммутатора адреса и входами немсдпфицируемых разрядов адреса адресныхвходов блока коммутаторов, прямойвыход триггера пуска соединен свходом генератора тактовых импульсов, первый выход которого соединенс входом синхронизации регистра адреса и регистра команд, вход логических условий устройства соединенс вторым информационным входом муль.типлексора логических условий, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд, вход кода операции устройства соединен синформационным входом регистра команд и входом блока элементов ИЛИ,входы адреса устройства соединеныс группой входов блока элементовИЛИ, выход которого соединен с вторыминформационным входом коммутатора адреса, прямой. выход триггера пускасоединен с прямым управляющим входомкоммутатора адреса, выход конца команды регистра микрокоманд соединенс.инверсным управляющим входом коммутатора адреса, о т л и ч а ю щ е -е с я тем, что, с целью расширения области применения, в устройствовведены преобразователь кода отказа1133595 О 15 20 в код номера модуля, группа тригге,ров отказов, второй и третий элементыИЛИ и одновибратор, причем выход кодалогических условий, выходы немодифицируемых разрядов адреса и выход микроопераций регистра микрокоманд соединены с пувым входом блока контроля на четность, выход контрольногопризнака четности регистра микрокоманд соединен с вторым входом блокаконтроля на четность, выход которогосоединен с Э-входом первого триггераотказа группы, прямой выход которогосоединен с выходом отказа устройстваи первым входом второго элемента ИЛИ,выход которого соединен с К-входомтриггера пуска, выход регистра адреса соединен с третьим входом блокаконтроля на четность, выход контрольного признака четности регистра адреса соединен с четвертым входомблока контроля на четность, входпуска устройства соединен с входомпервого элемента ИЛИ, выход блокаэлементов ИЛИ соединен с группойвходов первого элемента ИЛИ, входы Изобретение относится к автоматикеи вычислительной технике и можетбыть использовано при построении реконфигурируемых управляющих и вычислительных систем с использованиеммножества однотипных микропрограммныхустройств управления,Известно микропрограммное устройство, содержащее запоминающий блок,регистры, дешифраторы, блок распределения элементарных операций, элементы И 11,Недостатком устройства являютсябольшие аппаратурные затраты и отсутствие возможности передачи управления аналогичному устройству, что,в свою очередь, ограничивает функциональные возможности устройства,Известно устройство микропрограммного управления, содержащее счетчиккоманд регистр, дешифратор, матрицу микроопераций; арифметическоеустройство, регистр микроопераций 2.Недостатками устройства являются отсутствие возможности передачи отказа устройства соединены с Б-входами соответствующих триггеров отказа группы, начиная со второго, прямые выходы которых соединены с первой группой входов блска элементов И, выходы блока элементов Исоединены с первой группой преобразователя кода отказа в код номера модуля, выходы регистра командсоединены с второй группой входовпреобразователя кода отказа в кодномера модуля, выходы которого соединены с второй группой управляющихвходов блока коммутаторов и входами третьего элемента ИЛИ, выходы дешифратора соединены с второй группой входов блока элементов ИЛИ, выход третьего элемента ИЛИ соединенс третьей группой управляющих вхо,дов блока коммутаторов, выход признака конца команды регистра микрокоманд соединен с четвертой группойуправляющих входов блока коммутаторов,управляющим входомдешифратора и входом одновибратора, выход которого соединен с вторым входом второго элемента ИЛИ. управления с одного микропрограммного устройства на другое, отсутствиевозможности наращивания объема иколичества микропрограмм, а также сложность в создании унифицированныхблоков микропрограммных устройств исистем управления. Наиболее близким по технической сущности и достигаемому положительному эффекту к изобретению является микропрограммное устройство управления, которое содержит запоминающий блок, регистр адреса, регистр команд, регистр микрокоманд, мультйплексор логических условий, коммутатор адреса, триггер пуска, генератор тактовых импульсов, блок коммутаторов, блок элементов И, блок элементов ИЛИ, первый элемент ИЛИ, причем выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с входом запоминающего блока, выход кода логических условий запоминающего блокасоединен с управляющим входом мультиплексора логических условий и входом дешифратора, выход модифицируемого разряда адреса запоминающего блока соединенс первым информационным5 входом мультиплексора логических условий, выход немодифицируемых разрядов адреса запоминающего блока сое- динен с входами немодифицируемых разрядов адреса первого информацион ного входа коммутатора адреса ивхо 4 ами немодифицируемых разрядов адреса адресных входов блока коммутаторов, выходы микроопераций запоминающего блока являются первыми 15 выходами устройства, выходы дешифратора соединены с первыми управляющими входами блока коммутаторов, выходы которых являются адресными выходами вторых выходов устройства, щ выход мультиплексора логических условий соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса .и входами немодифицируемых разрядов 25 адреса адресных входов блока коммутаторов, прямой выход триггера пуска соединен с входом генератора тактовых импульсов, первый выход которого соединен с синхронизирующим вхо дом регистра адреса и синхронизирующим входом регистра команд, вход логических условий устройства соеди нен с вторым информационным входом мультиплексора логических условий,35 второй выход генератора тактовых импульсов соединен с синхронизирующим входом регистра микрокоманд, вход кода операции устройства соединен с информационным входом регистра40 команд и первым входом блока элементов ИЛИ, первый - (и)-й входы адреса устройства соединены с вторым - и-м входами блока элементов ИЛИ, выход которого соединен с вторым информационным входом коммутатора адреса, прямой выход триггера пуска соединен с прямым управляющим входом коммутатора адреса, выход признака конца команды регистра микрокоманд50 соединен с инверсным управляющим входом коммутатора адреса 3 .Недостатком известного устройства является узкая область применения, что обусловлено отсутствием средств, 55 позволяющих осуществить реконфигурацию системы, построенной из однотипных микропрограммных устройств управления, при отказе одного из этих уст-.,ройств, а это приводит к отказу всейсистемы.В модулях распределенных управляющих систем имеется естественная избыточность, обусловленная тем, чточасть микропрограммно-аппаратурныхресурсов повторяется в несколькихмодулях в целях оптимизации общеговремени решения задачи (сокращениячисла пересылок), Следовательно,эта избыточность является важным резервом повышения отказоустойчивостисистемы. Однако этот резерв не реализуется, что снижает надежностьраспределенной управляющей системыв целом и ограничивает область применения устройства классом систем,к которым не предъявляются высокиетребования по отказоустойчивости,Другим дополнительным резервомповышения отказоустойчивости распределенных управляющих систем является тот факт, что при закреплениимикропрограмм между модулями, какправило, остается свободной часть микропрограммной памяти. Свободные линейки могут быть использованы для хранения дублей коротких микропрограммили для хранения укороченных микропрограмм, по которым производятсявычисления при отказе основных, что,в свою очередь, может повысить надежность системы в целом. Однако этавозможность в устройстве также нереализована.Указанные обстоятельства существенно ограничивают область примененияизвестного устройства,Целью изобретения является расширение области применения за счет введения технических средств, позволяющих осуществлять реконфигураци 1программного и аппаратного обеспечения распределенной системы, построенной на унифицированных микропрограммных модулях при возникновении вних отказов.Поставленная цель достигается тем, что в микропрограммное устройст во управления, содержащее блок памяти, регистр адреса, регистр команд,регистр микрокоманд, дешифратор, мультиплексор логических условий, коммутатор адреса, триггер пуска, генератор тактовых импульсов, блок коммутаторов, блок элементов И, блок элементов ИЛИ, первый элемент10 ИЛИ, причем выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с входом блока памяти, выход блока памяти соединен с информацион ным входом регистра микрокоманд, выход кода логических условий регистра микрокоманд соединен с управляющим входом мультиплексора логических условий и входом дешифратора, выход модифицируемого разряда адреса регистра. микрокоманд соединен с первым информационным входом мультиплексора логических условий, выходы немодифицируемых разрядов адреса регист ра микрокоманд соединены с первым информационным входом коммутатора адреса и группой информационных входов блока коммутаторов, выход микроопераций регистра микрокоманд является 20 управляющим выходом устройства, выходы дешифратора соединены с первой группой управляющих входов блока коммутаторов, выходы которых являются информационными выходами устройства, 25 выход мультиплексора логических условий соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса и входами немодифицируемых разрядов 30 адреса. адресных входов блока коммутаторов, прямой выход триггера пуска соединен с входом генератора тактовых импульсов, первый выход которо. го. соединен с входом синхронизации д 5 регистра адреса и регистра команд, вход логических условий устройства соединен с вторым информационным входом мультиплексора логических условий, второй выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд, вход кода операции устройства соединен с информационным входом регистра команд и входом блока элементов 45 ИЛИ, входы адреса устройства соединены с группой входов блока элементов ИЛИ, выход которого соединен с вторым информационным входом коммутатора адреса, прямой выход триггера 50 пуска соединен с прямым управляющим входом коммутатора адреса, выход конца команды регистра микрокомандСсоединен с инверсным управляющим входом коммутатора адреса, дополни тельно введены преобразователь кода отказа в код номера модуля, блок контроля на четность, группа триггеров отказов, второй и третий элементы ИЛИ и одновибратор, причем выходкода логических условий, выходы немодифицируемых разрядов адреса ивыход микроопераций регистра микрокоманд соединены с первым входом блока контроля на четность, выход контрольного признака четности регистрамикрокоманд соединен с вторым входомблока контроля на четность, выход которого соединен с 0-входом первоготриггера отказа группы, прямой выходкоторого соединен с выходом отказаустройства и первым входом второгоэлемента ИЛИ, выход которого соединенс К-входом триггера пуска, выход регистра адреса. соединен с третьимвходом блока контроля на четность,выход контрольного признака четностирегистра адреса соединен с четвертым входом блока контроля на четность,вход пуска устройства соединен свходом первого элемента ИЛИ, выходблока элементов ИЛИ соединен с группой входов первого элемента ИЛИ,входы отказа устройства соединеныс Б-входами Соответствующих триггеров отказа группы, начиная с второго, прямые выходы которых соединеныс первой группой входов блока элементов И выходы блока элементов Исоединены с первой группой входовпреобразователя кода отказа в код номера модуля, выходы регистра командсоединены с второй группой входовпреобразователя кода отказа в код номера модуля, выходы которого соединены с второй группой управляющихвходов блока коммутаторов и входамитретьего элемента ИЛИ выходы дешифратора соединены с второй группойблока элементов ИЛИ, выход третьегоэлемента ИЛИ соединен с третьей группой управляющих входов блока коммутаторов, выход признака конца команды регистра микрокоманд соединенс четвертой группой управляющихвходов блока коммутаторов, управляющим входом дешифратора и входомодновибратора, выход которого соединен с вторым входом второго элемента ИЛИ. Сущность изобретения заключается в расширении области применения путем введения средств, обеспечивающих передачу управления устройству, в котором хранится полная или усеченная копия микропрограммы отказавшего устройства. Возможность передачиуправления при отказе устройства аналогичному микропрограммному устройству позволяет повысить отказоустойчивость системы, построенной на основеоднотипных устройств.,Повышение отказоустойчивости достигается путем контроля отдельныхустройств системы и осуществленияее реконфигурации в случае отказа 10на основе использования естественнойизбыточности, обусловленной, во-первых, тем, что часть микропрограммноаппаратных ресурсов повторяется внескольких модулях в целях оптимизации общего времени решения задачи(сокращения числа пересылок) и, вовторых, тем, что при закреплениимикропрограмм между модулями остается свободной часть микропрограммной 20памяти, Свободное пространство памяти используется для хранения дублейкоротких микропрограмм или для хранения укороченных микропрограмм,по которым производятся вычисле- .25ния при отказе основных микропрограммных устройств управления.Введение узла контроля на четностьпозволяет осуществлять контроль устройства и формировать признак отка- З 0за с целью последующего исключенияотказавшего устройства из работысистемы,Введение первого - и-го триггеров отказа (где п - количество моду 35лей в системе) позволяет хранитьинформацию об отказавших модуляхсистемы.Введение преобразователя кода отказа в код номера модуля необходимо 40для перекоммутации передачи управления в зависимости от выполняемой команды на один из исправных модулейсистемы.Введение второго элемента ИЛИ необходимо для сборки сигналов на обнуление триггера пуска при окончанииработы модуля или его отказе.Ввдение третьего элемента ИЛИ не 50 обходимо для формирования сигнала о том, что модуль, на который должна быть осуществлена передача управления, подлежит замене,Введение одновибратара необходимо 55 для Формирования импульса на обнуление триггера пуска после выполнения микропрограммы. На Фиг. 1 представлена функциональная схема микропрограммного устройства управления; на Фиг, 2 - функциональная схема узла контроля начетность; на фиг, 3 - функциональнаясхема коммутатора блока коммутаторов;на Фиг. 4 - функциональная схема преобразователя кода отказа в код номера модуля для п=4 и 1=4, где и - количество модулей в системе, 1 - количество кодов операций.Микропрограммное устройство управления (фиг. 1) содержит блок 1 памяти, регистр 2 адреса, регистр 3 микрокоманд с полями:3.1 - кода логических условий, 3.2 - модифицируемогоразряда адреса, 3.3 - немодифицируемых разрядов адреса, 3.4 - кода микроопераций, 3.5 - признака конца команды, 3.6 - контрольного признакачетности; регистр 4 команд, блок 5контроля на четность, дешифратор 6,мультиплексор 7 логических условий,коммутатор 8 адреса, блок коммутаторов 91 - 9(п), преобразователь10 кода отказа в код номера модуля,триггер 1 пуска, первый 12,1 - (и-й)12.п триггеры отказов, генератор 13тактовых импульсов, блок 14 элементов И, блок 15 элементов ИЛИ, первый элемент ИЛИ 16, третий элементИЛИ 17, второй элемент ИЛИ 18, одновибратор 19, входы 20 кода операции,входы 211 в . 21 (и) адреса, вход22 логических условий, вход 23 пуска, управляющие 24 и 25 и информационные 25.2 - 25 (п) выходы устройства.Блок 5 контроля на четность(Фиг. 2) содержит первый 26 и второй27 блоки элементов суммы по модулюдва, элемент 28 суммы по модулю два.Коммутатор 9.д (=1, и) блокакоммутаторов 91 - 9,п(фиг. 3)содержит элемент 2 И- ИЛИ 29.х и блокэлементов И 30.1.Преобразователь кода отказа в кодномера модуля (Фиг. 4),для п=4, гдеп - число модулей в системе, и 1=2(1 - число команд) содержит блок элементов НЕ 31.1 - 31.5, два блока сопротивлений и соответственно первую32 и вторую 33 матрицы. 8 - сигналс -го элемента Я=1, п)И блока элементов И 14, .1 - сигнал кода операции с регистра 4 команд,На выходе преобразователя 10 длярассматриваемого примера формируютсялогические функцииБлок 1 памяти предназначен дляхранения микропрограмм управления, аотакже кодов передачи управления аналогичным модулям, регистр 2 адреса - для задания адреса запоминающего блока 1 при считывании из него информации, регистр 3 микрокоманд - для хранения очитанных микрокоманд, регистр 4 команд - для хранения кода операции, необходимого для перекоммутации адреса передачи управления при возникновении отказа соответствующего модуля, блок 5 контроля на чет-. ность - для обнаружения отказа в устройстве, дешифратор б - для определе- о ния номера модуля, которому необходимо передать управление, мультиплексор 7 логических условий - для формирования значения модифицируемого . разряда адреса очередной микрокоманды.Коммутатор 8 адреса предназначен для коммутации адреса очередной микрокоманды. При наличии признака конца команды на выходе 3.5 регистра 3микрокоманд. очередной адрес микро- команды коммутируется с входа 20 кода операции. При отсутствии признака конца команды адрес очередной микро- команды коммутируется в зависимости от хода выполнения микропрограммы.Блок коммутаторов 9.1 - 9.п35 определяет прохождение адреса передачи управления либо в аналогичный модуль (при отсутствии признака его отказа), либо в другой модуль систе-,40 мы (при наличии признака отказа от модуля, в который необходимо осуществить передачу управления).Преобразователь 10 предназначен для перекоммутации передачи адреса45 управления в блоках коммутаторов 9,1 - 9.ппри появлении отказа в соответствующем модуле системы в зависимости от выполняемого кода операции, поступающего с выхода регист 50 ра 4 команд, Например, для системы, у которой п=4 и 1=2 передачу адреса управления при появлении соответствувующего отказа можно представить таблицей в предложении,что передачу осущест вляет четвертый модуль ю 4 ( Фиг.4)Использование преобразователя кода отказа в код номера модуля позволяет умейьшить аппаратурные затраты, связанные с перекоммутацией выходов при передаче управления в случае наличия в системе отказавших модулей.Триггер 11 пуска предназначен для запуска генератора 13, включение которого происходит по сигналу пуска с входа 23 или при поступлении адреса с входов 21,1 - 21,пс аналогичных модулей.Первый 12.1 - п-й 12,п триггер отказов предназначены для хранения признаков отказов соответствующих модулей системы, генератор 13 - для синхронизации работы устройства.На выходах генератора 13 Формируются первый и второй тактовые импульсы.Блок элементов И 14 предназначен для передачи в преобразователь 10 кода признака отказа того модуля, на который необходимо передать адрес управления.Блок элементов ИЛИ 15 предназначен для сборки кода операции с входа 20 устройства и кодов адресов с входов 21,1 - 21. ис последующей передачей через коммутатор 8 на регистр 2 адреса.Элемент ИЛИ 16 предназначен для сборки сигналов на начало работы модуля, элемент ИЛИ 17 - для формирования сигнала на разрешение передачиадреса тому модулю, который определен преобразователем 10 кода, Элемент ИЛИ 18 предназначен для сборки сигналов на прекращение работы устройством.Одновибратор 19 предназначен дляформирования импульса по окончаниимикропрограммы (команды) что характеризуется появлением признака концакоманды на выходе регистра 3 микрокоманд,Микропрограммное устройство управления происходит следующим образом.В исходном состоянии элементы памяти устройства находятся в нулевом состоянии.Начало работы устройства начинает. ся путем поступления на вход 23 устройства сигнала пуска. Данный сигнал через элемент ИЛИ 16 поступает на Б-вход триггера 11 пуска и устанавливает его в единичное состояниеСигнал с прямого выхода триггера 11разрешает прохождение с входа 20кода операции через блок элементовИЛИ 15 и коммутатор 8 адреса на ре1133595 2 55 гистр 2 адреса по концу первого тактового импульса поступающего с генеЭратора 13 тактовых импульсов. Кодоперации определяет начальный адресмикропрограммы. Второй тактовый импульс с выхода генератора 13 производит запись информации из блока 1 врегистр 3 микрокоманд по адресу врегистр 2 адреса.При записи информации в регистр 3 10микрокоманд на выход 24 выдаетсяпервая микрокоманда на управление,например, операционным устройством.На .выходе 3.5 регистра 3 признакаконца команды сигнал логического нуля поступает на управляющий вход коммутатора 8 адреса и разрешает записьадреса очередной микрокоманды в за-:висимости от информации, находящейся в поле 3.1 кода логических условий, в поле 3.2 яодифицируемого разряда адреса и в поле 3.3 немодифицируемых разрядов адреса. Если микрокоманда является микрокомандной линейной последовательности, то код 25адреса определяется кодом немодифицируемых разрядов адреса с выхода3.3 и модифицируемым разрядов адреса с выхода 3.2 регистра 3. В этом.случае модифицируемый разряд адресапри нулевом коде логических условийс выхода 3.1 регистра 3 через мультиплексор 7 проходит без изменений.Если микрокоманда является микрокомандой ветвления, то адрес очередной микрокоманды определяется постоянной частью кода адреса (немодифицируемой частью) и переменной частью (модифицируемым.разрядом адреса) .Если проверяемое логическое условие 40выполнено, то модифицируемая частькода адреса имеет единичное значениеи.сформированный таким образом адресочередной микрокоманды через коммутатор 8 адреса поступает на регистр 42 адреса по тактовому импульсу с выхода генератора 13. Импульс с выходагенератора 13 поступает на управляющий вход первого триггера 12.1 отказа и, если он находится в единичномсостоянии, то передает эту .информацию на выходы 25,1 - 25.паналогичным модулям системы,По мере выдачи информации микропрограммным устройством управления происходит ее контроль в блоке 5 контроля на четность (фиг. 2), При этом происходит контроль как адресной, так и операционной информациии при искажении одного из кодов илинесоответствии адреса выбранной микрокоманде блок 5 контроля на четность формирует сигнал отказа модуля.Этот сигнал с приходом тактового импульса на управляющий вход триггера12.1 отказа перебрасывает данныйтриггер в единичное состояние. Припоявлении сигнала на прямом выходе триггера 12.1 этот сигнал через элемент ИЛИ 18 поступаетна К-вход триггера 11 пуска и устройство прекращает работу,При выполнении микропрограммы устройство может передать управление аналогичному модулю системы, Передача управления осуществляется следующим образом. С выхода 3.1 регистра,3 микрокоманды передачи управления выдается код номера модуля, которому необходимо передать управление. Данный код поступает на вход дешифратора 6, По признаку конца команды с выхода 3.5 регистра 3 микрокоманд возбуждается один из выходов дешифратора 6, соответствующий модулю дляпередачи управления, и адрес с выходов 3,2 и 3,3 регистра 3 через соответствующий коммутатор (фиг. 3) блока коммутаторов 9.1 - 9.ппередается на один из выходов 251 - 25,паналогичному устройству, Данным образом устройство функционирует, если соответствующий модуль системы исправенВ случае, если модуль, которому необходимо передать управление, имеет отказ (что определяется в указанном модуле по контролю на четность аналогично тому, как было рассмотрено ранее), то передача управления осуществляется в зависимости от выполняемой команды (кода операции, хранимого в регистре 4 команд) и номером отказавшего модуля системы.Признак отказа -го модуля системы с входов 21.1 - 21.ппоступает на Б-входы триггеров 12.2 - 12.п, соответствующих определенному модулю. Для каждого кода операции вместо отказавшего модуля может быть передано управление на другой, но опре-,. деленный модуль системы. Функцию управления заменой отказавшего модуля выполняет преобразо- ватель 10 кода, на входы которого поступает, во-первых, признак того, что тот модуль, которому необходимо1133595 34 13 НР Б Н Э о 2 4 0 1 0 0 0 0 0 0 0 0 0 0 0 10 0 0 0 4 3 1 0 0 0 0 0 0 О О. 0 0 4 1 1 0 0 0 0 0 0 0 0 О передать управление, отказал, и, во-вторых, код операции. По этой информации преобразователь 10 кода определяет модуль, которому необходи. мо передать управление вместо отка завшего (фиг. 4). На одном из выходов преобразователя 10 кода появляет ся сигнал, определяющий тот номер модуля, которому необходимо передать управление вместо отказавшего, Этот 1 О сигнал поступает на соответствующий коммутатор 9. 1 - 9.(п) и по признаку конца команды адрес передается на один из выходов устройства.После прихода от другого модуля 15 системы по одному из входов 21.1 21.падреса, с которого необходимо начать выдачу микрокоманд, он через блок элементов ИЛИ 15 поступает на информационный вход коммутатор 8 ад реса и на элемент ИЛИ 16, На выходе элемента ИЛИ 16 появляется сигнал, который перебрасывает триггер .11 пуска в единичное состояние и тем самым Нормальная передача Код операции управления запускает генератор, 13 тактовых кмпульсов. Первым тактовым импульсомс выхода генератора 13 информациячерез коммутатор 8 адреса заноситсяв регистр 2. По этому адресу происходит считывание информации из запоминающего блока 1. Далее устройство работает аналогично рассмотренному ранее. Таким образом, за счет введения в микропрограммном устройстве управления средств, обеспечивающих фиксацию отказов модулей системы и позволяющих в зависимости ог реализуемого кода операции осуществлять передачу управления вместо отказавшего модуля исправному, существенно расширяется область применения устройства.Изобретение может быть использовано в распределенных управляющих системах, к которым предъявляются повышенные требования по отКазоустой-, чивости,1 Передача управления при отказах

СмотретьЗаявка

3587867, 04.05.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА. КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/07, G06F 9/22

Метки: микропрограммное

Опубликовано: 07.01.1985

Код ссылки

<a href="https://patents.su/10-1133595-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Мультимикропрограммная управляющая система

Следующий патент: Устройство для определения характеристик связности ориентированного графа

Случайный патент: Секция двухскатного покрытия сборно-разборного здания