Вычислительное устройство для решения дифференциальных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

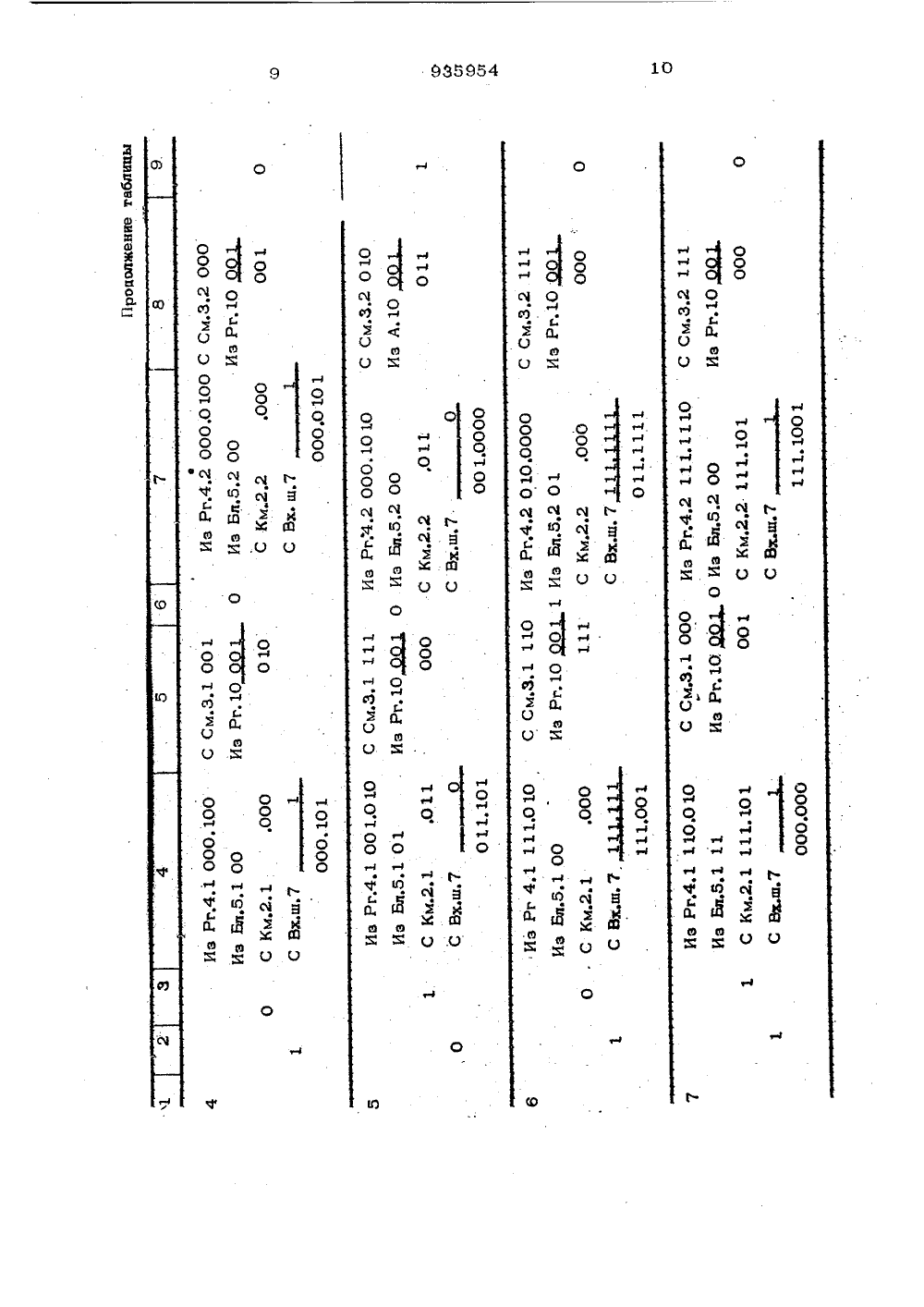

ао делан изобретеннй н аткрыткй(72) Авторы изобретения РКиевский ордена Ленина политехнический институтиМ, 50-летия.Великой Октябрьской социалистической револйщщ(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИффЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ Изобретение относится к вычислительной технике и может быть применено цля решения систем дифференциальных уравнений.Известно устройство, решающее дифференциальные уравнения, представляющие собой интегрирующее устройство и преп- назначенное цля решения дифференциаль-ных уравнений, зацанных в форме Шеннона 1.Недостатком этого решения является невозможность использования достаточно точных "самоначинаюшихся" метоцов численного интегрирования, что обуславливает низкое быстродействие, особенно на15 начальном участке.Наиболее близким техническим решением к изобретению является устройство, содержащее регистры приращений, первый регистр остатка, выходы которого подведены ко входам первого сумматора, соециненного со входами блока выделения цифры, второй сумматор, связанный со входами второго блока выделения цифры,в котором шаг интегрирования выполняется за время двух сложений и одногоумн ожени я.Однако это устройство не обладаетнедостаточным быстродействием,Целью предлагаемого изобретения. является повышение быстродействия.Поставленная цель достигается тем,что в устройство, содержащее регистрыприращений, цва сумматора, два блокавыделения цифры и первый регистр остатка; выхоц которого подключен ко входуостатка первого сумматора, выхоц операнда которого подключен ко входу остаткапервого сумматора, выход операнда которого подключен к информационному вхоцупервого блока выцеления цифры, выходоперанда второго сумматора подключен кинформационному входу второго блока выделения цифры, введены второй регистростатка; реша 1 ощий блок и два коммутатора, причем выхоцы регистров приращенийподктиочены к информационным входам коммутаторов, управляющие входы которых038084 6ввния при достаточно бобьшом количестве ц шагов М практически не зависит от разрядности функций и стремится к Тсо ==(01). (Для примера из таблицы это5 время равно четырем тактам сложения),В а- известном устройстве процесс интегрирования на данном шаге не может быть сово мешен с процессом интегрирования на послепуюших шагах, а кажаый шаг интегри- , 0 рования выполняется эа время авух сложений и одного умножения, т.е. время интегрирования в известном устройстве возрастает с увеличением раэряаности и превосхоаит среанее время выполнения шага .15 в предлагаемом, устройстве. Если учесть, 1 . что в известном устройстве (реализующем ае формулу интегрирования первого поряака)аля получения той же точности, что и впредлагаемом (гце реализована формула20 второго порядка) требуется значительноуменьшить величину шага интегрирования,(а при этом во столько же раз увеличивается время вычисления) то вполне очео видно, что цель изобретения с помощью25преалагаемого технического решения цоссти гается.1 51, соаержашего коа х -92, а к сумматору 3,2 - регистр 1, содержащий ко1. Ф( . При этом с выхоца блока 5.2на выхоцную шину 8 поступает значениецифры результата Чи 1, имеющей весР " . Каждый цикл занимается сигнлом в тактирующей. шине 9, по которомукоды, сформированные на выхоае сумматров 3, заносятся в реп(стры 4, коцы,сформированные на выхоае сумматора 11заносятся в регистр 12, в блок 6 поцготавливается к приему очереаной цифры.Работа устройства на примере интегр(рования аифференциального урсвня 1 = 1цля адоичной системы счисления с цифрами 1, О, 1, при Уи =11010111, =01иллюстрируется прилагаемой таблицей, гполучен результатУ=1 ЮОООО,Преалагаемое устройство позволяетформировать на выходе разряаы значенияискомой функции в и+1 -ой точке с выаержкой на 0+1 циклов относительно ввца в устройство соответствующих разряаов функции в точке, Это позволяет припосле аовательном соецинении устройствприступить к выполнению очередного шагаинтегрирования не после окончания прецы 30цущего шага, а непосредственно после получения первых раэряаов результатов этого шага, Таким образом, процессы интегрирования на И-ом, И+1 -ом(,-И+2 -омшагах при использовании прецлагаемыхустройств могут быть совмещены во вре-.З 5мени, и время выполнения М шагов составляет: гае И - разряцность преастввления функ 40ций 3 Ь- время суммирования, а среанеевремя выполнения оцно(ч шага интегрироПрецлагаемое устройство позволяет не только уменьшать время вычисления (эа счет совмещения во времени операций, о носящихся как к оцному, так и разным шагам интегрирования), но и сохранить обьем вычислений по сравнению с устройствами, реалиеукзцими явные методы интегрирования, В преалагаемом устройстве на каждом шаге интегрирования вычисляется только оано значение правой части, тогда как в известном устройстве при реализации метоаа Рунге-Кутта того же поряцка нв квжцом шаге интегрирования правую часть необхопимо вычислять ава раза.Т 5 9359Получаем результат=1001010 1ф ормула изобретения 1, Вычислительное устройство для решения дифференциальных уравнений, содержащее регистры приращений, два сумматора, два блока выделения цифры и первый реестр остатка, выход которого подключен к входу остатка первого сумматора, о . выход операнда которого подключен к информационному входу первого блока выделения цифры, выход операнда второго сумматора подключен к информационному входу второго блока выделения цифры, о тл и ч а ю щ е е с я тем, что, с цельюповышения быстродействия, в него введены решающий блок, два коммутатора и второй регистр остатка; вйход которого соединен с входом остатка второго сумматора, 0 причем выходы регистров приращений подключены к информационным входам коммутаторов управляющие входы которых соединены с выходом решающего блока, к информационному входу которого подключен выход первого блока выделения цифры, выход первого и ввход второго коммутаторов подключены к входам приращений первого и второго сумматоров соответственно, входы операндов сумматоров подключены к 30 входу цифры операндов устройства, выходыпервого и второго блоков выделения цифрыподключены к соответствующим входампервого и второго сумматоров соответственно, выходы остатка сумматоров подключены к входам соответствующих регистров, к таКтирующему входу устройстваподключены управляющие входы блоков выделения цифры, регистров остатка и решающего блока, а выход второго блока выделения цифры подключен к выходу результата устройства.2. Устройство по п. 1, о т л и ч а -ю щ е е с я тем, что блок выделенияцифры содержит регистр констант, сумматор и регистр цифры, причем выход регистра цифры соединен с выходом блока,управляющий вход - . с управляющим входомблока, . а информационный "вход - с выходом сумматора, первый вход которого соединен с выходом регистра констант, а второй вход подключен к информационномувходу блокаИсточники информации,принятяе во внимание при экспертизе1, Автооское свидетельство СССРМ 637833, кл. б 06 Х 1/02, 1975.2. Авторское "видетельство СССРМ 568060, кл, б 06 Х 1/02, 1974935954 Составитель С. Гро ехред К.Мыцьо оваКаррек П р И. Мус ецакт 4213/52 Тираж 73 ВНИИ ПИ Государственногоно делам изобретений и 13035, Москва, Ж, Ра Пошасомитета СССРткрьЬийушская набеу це 4/ Зак ал

СмотретьЗаявка

2844234, 27.11.1979

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ЖАБИН ВАЛЕРИЙ ИВАНОВИЧ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, КОЗАК ВЛАДИМИР СИДОРОВИЧ, ПОКАРЖЕВСКИЙ АЛЕКСАНДР СЕРГЕЕВИЧ, СКОЧКО АЛЕКСАНДР ПЕТРОВИЧ, ТАРАСЕНКО ВЛАДИМИР ПЕТРОВИЧ, ШВЕЦ ЕВГЕНИЙ МИХАЙЛОВИЧ, ЩЕРБИНА АЛЕКСАНДР АНДРЕЕВИЧ

МПК / Метки

МПК: G06F 7/64

Метки: вычислительное, дифференциальных, решения, уравнений

Опубликовано: 15.06.1982

Код ссылки

<a href="https://patents.su/9-935954-vychislitelnoe-ustrojjstvo-dlya-resheniya-differencialnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительное устройство для решения дифференциальных уравнений</a>

Предыдущий патент: Генератор случайных последовательностей чисел

Следующий патент: Цифро-частотный интегратор

Случайный патент: Жолоб для выпуска чугуна из плавильных печей