Цифровой синтезатор сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

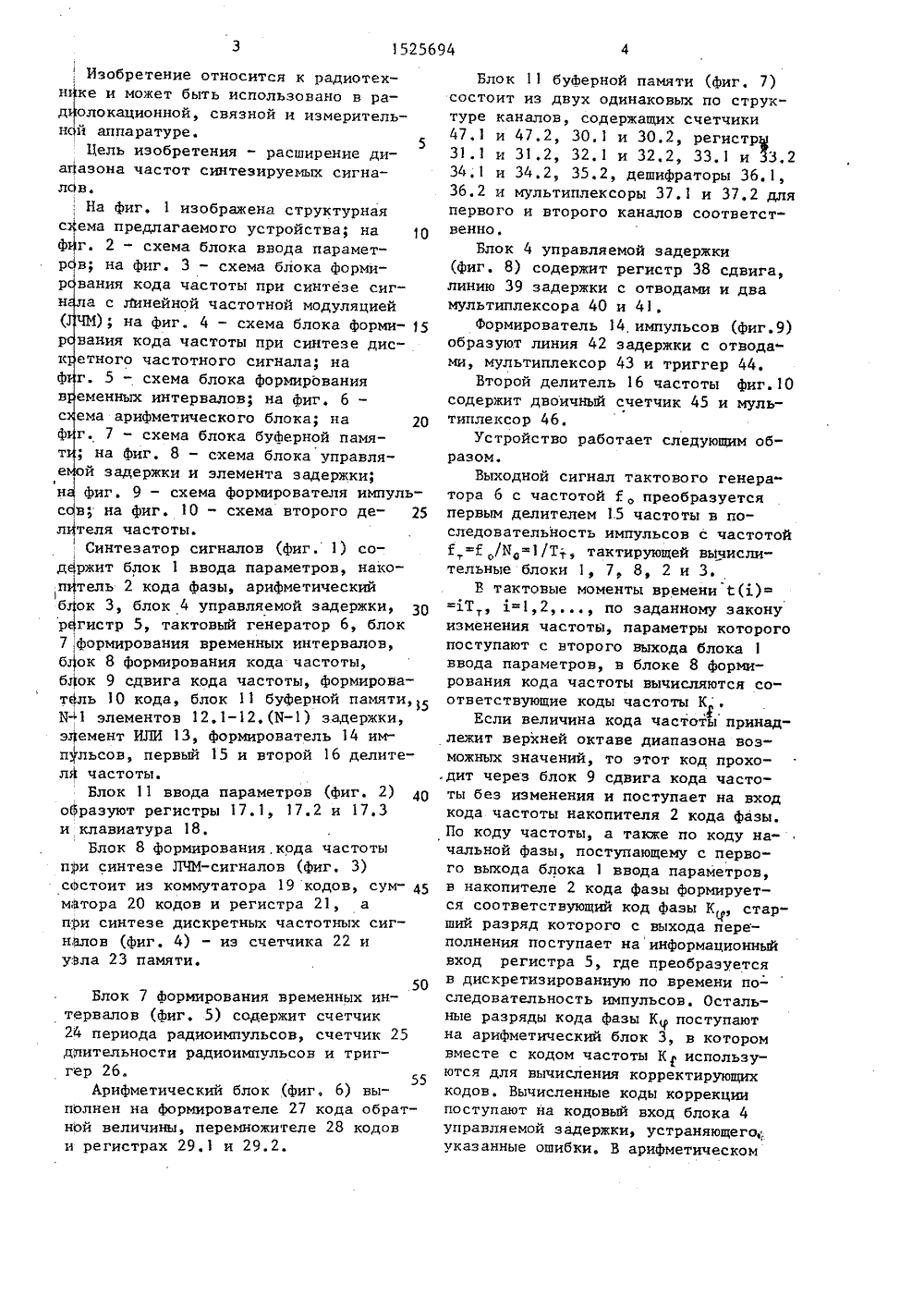

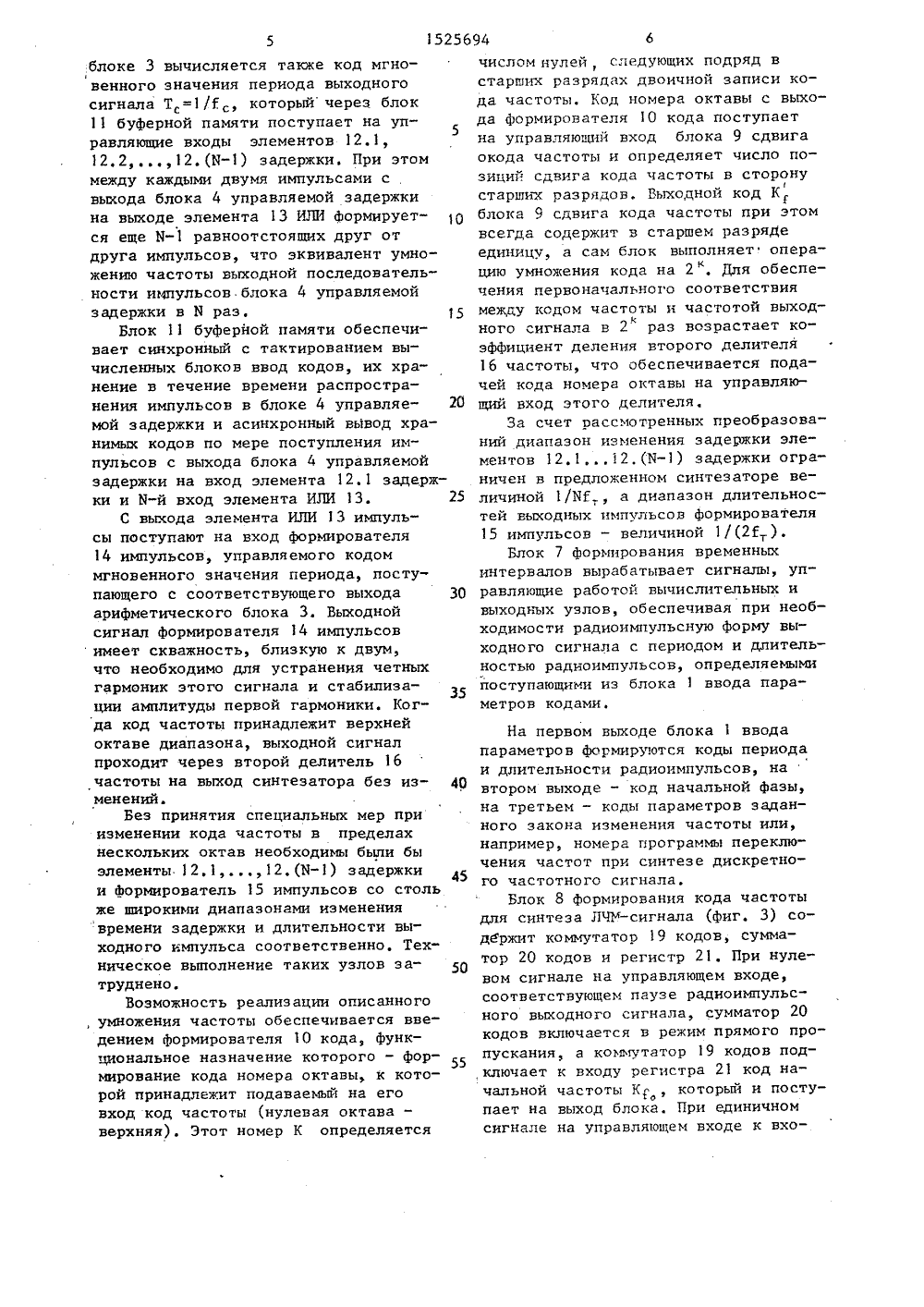

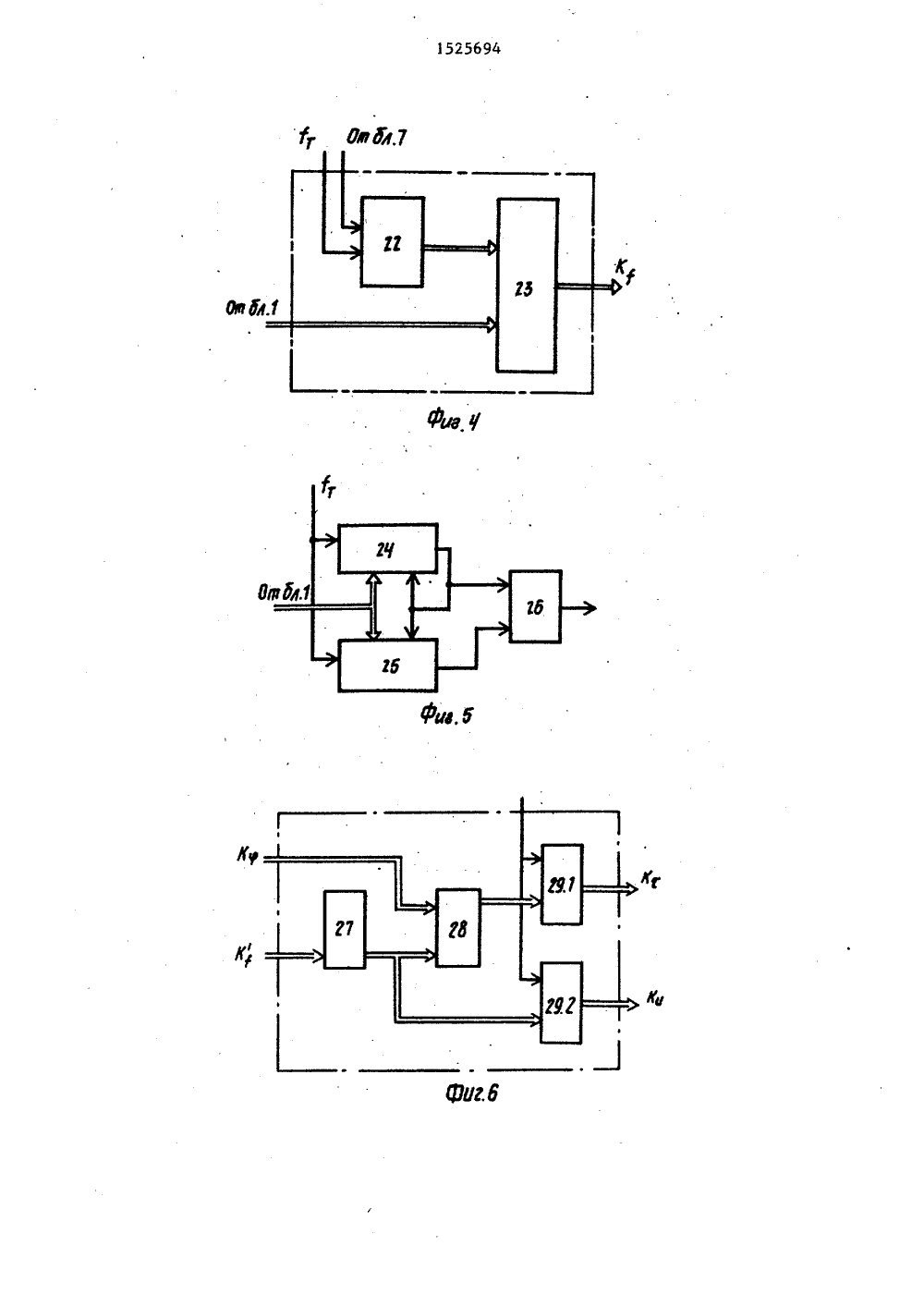

Блок 7 формирования временных интервалов (фиг. 5) содержит счетчик 24 периода радиоимпульсов, счетчик 2 длительности радиоимпульсов и триггер 26.Арифметичесполнен на форной величины,55 кий блок (фиг, 6) вымирователе 27 кода обратперемножителе 28 кодов ,1 и 29.2.регистрах Изобретение относится к радиотехнике и может быть использовано в радиолокационной, связной и измерительной аппаратуре.5Цель изобретения - расширение диапазона частот синтезируемых сигналОв.На фиг. 1 изображена структурная сема предлагаемого устройства; на 10 фиг. 2 - схема блока ввода параметр в; на фиг. 3 - схема блока формир вания кода частоты при синтезе сигн а с Линейной частотной модуляцией ( ЧМ); на фиг. 4 - схема блока форми р вания кода частоты при синтезе диск етного частотного сигнала; на ф г. 5 - схема блока формирования в еменных интервалов; на фиг. 6 - с ема арифметического блока; на 20 ф г. 7 - схема блока буферной памят ; на Фиг, 8 - схема блока управляе ой задержки и элемента задержки; 1 н фиг. 9 - схема формирователя импульс в; на фиг. 10 - схема второго де л теля частоты.Синтезатор сигналов (фиг. 1) сод 4 ржит блок 1 ввода параметров, накопитель 2 кода фазы, арифметическийбЛок 3, блок 4 управляемой задержки, регистр 5, тактовый генератор 6, блок 7 ,формирования временных интервалов, блок 8 формирования кода частоты, блок 9 сдвига кода частоты, формироватЬль 10 кода, блок 11 буферной памяти,15 Бэлементов 12,1-12.(Ы) задержки, элемент ИЛИ 13, формирователь 14 импульсов, первый 15 и второй 16 делителй частоты.Блок 11 ввода параметров (фиг. 2) 40 образуют регистры 17.1, 17.2 и 17.3 и клавиатура 18,Блок 8 формирования, кода частоты при синтезе ЛЧМ-сигналов (фиг. 3) состоит из коммутатора 19 кодов, сум матора 20 кодов и регистра 21, а при синтезе дискретных частотных сигналов (фиг. 4) - из счетчика 22 и узла 23 памяти. Блок 11 буферной памяти (фиг. 7)состоит из двух одинаковых по структуре каналов, содержащих счетчики47.1 и 47.2, 30,1 и 30,2, регистры31,1 и 31,2, 32.1 и 32.2, 33.1 и 33,234.1 и 34,2, 35,2, дешифрагоры 36.1,36.2 и мультиплексоры 37,1 и 37,2 дляпервого и второго каналов соответственно,Блок 4 управляемой задержки(фиг. 8) содержит регистр 38 сдвига,линию 39 задержки с отводами и двамультиплексора 40 и 41,Формирователь 14,импульсов (фиг.9)образуют линия 42 задержки с отводами, мультиплексор 43 и триггер 44.Второй делитель 16 частоты фиг.10содержит двоичный счетчик 45 и мультиплексор 46,Устройство работает следующим образом.Выходной сигнал тактового генератора б с частотой К, преобразуетсяпервым делителем 15 частоты в последовательность импульсов с частотойЕ, Г /Ир 1/Т, тактирующей вычислительные блоки 1, 7, 8, 2 и 3.В тактовые моменты времени 1Т , "-1,2 по заданному законуизменения частоты, параметры которогопоступают с второго выхода блока 1ввода параметров, в блоке 8 формирования кода частоты вычисляются соответствующие коды частоты К.Если величина кода частоты принадлежит верхней октаве диапазона возможных значений, то этот код прохо,дит через блок 9 сдвига кода частоты без изменения и поступает на входкода частоты накопителя 2 кода фазы.По коду частоты, а также по коду начальной фазы, поступающему с первого выхода блока 1 ввода параметров,в накопителе 2 кода фазы формируется соответствующий код фазы К стар"ший разряд которого с выхода йереполнения поступает на информационныйвход регистра 5, где преобразуетсяв дискретизированную по времени последовательность импульсов. Остальные разряды кода Фазы К поступаютна арифметический блок 3, в которомвместе с кодом частоты К используются для вычисления корректирующихкодов. Вычисленные коды коррекциипоступают на кодовый вход блока 4управляемой задержки, устраняющегоуказанные ошибки. В арифметическомблоке 3 вычисляется также код мгновенного значения периода выходногосигнала Т =1/Г , которыйчерез блок11 буферной памяти поступает на уп 5равляющие входы элементов 121,12,212,(Ю) задержки. При этоммежду каждыми двумя импульсами свыхода блоха 4 управляемой задержкина выходе элемента 13 ИЛИ формируется еще Иравноотстоящих друг отдруга импульсов, что эквивалент умножению частоты выходной последовательности импульсов блока 4 управляемойзадержки в Ю раз, 15Блок 11 буферной памяти обеспечивает синхронный с тактированием вычисленных блоков ввод кодов, их хранение в течение времени распространения импульсов в блоке 4 управляемой задержки и асинхронный вывод хранимых кодов по мере поступления импульсов с выхода блока 4 управляемойзадержки на вход элемента 12.1 задержки и Н-й вход элемента ИЛИ 13. 25С выхода элемента ИЛИ 13 импульсы поступают на вход формирователя14 импульсов, управляемого кодоммгновенного значения периода, поступающего с соответствующего выхода 30арифметического блока 3, Выходнойсигнал формирователя 14 импульсовимеет скважность, близкую к двум,что необходимо для устранения четныхгармоник этого сигнала и стабилизации амплитуды первой гармоники. Когда код частоты принадлежит верхнейоктаве диапазона, выходной сигналпроходит через второй делитель 16частоты на выход синтезатора без изменений.Без принятия специальных мер приизменении кода частоты в пределахнескольких октав необходимы были быэлементы 12,112,(Б) задержки 45и формирователь 15 импульсов со стольже широкими диапазонами изменениявремени задержки и длительности выходного импульса соответственно, Техническое выполнение таких узлов затруднено,Возможность реализации описанного, умножения частоты обеспечивается введением формирователя 10 кода, функциональное назначение которого - фор 55мирование кода номера октавы, к которой принадлежит подаваемый на еговход код частоты (нулевая октава -верхняя). Этот номер К определяется числом нулей следующих подряд встарших разрядах двоичной записи кода частоты. Код номера октавы с выхода формирователя 1 О кода поступаетна управляющий вход блока 9 сдвигаокода частоты и определяет число позиций сдвига кода частоты в сторонустарших разрядов. Выхоцной код Кблока 9 сдвига кода частоты при этомвсегда содержит в старшем разрядеединицу, а сам блок выполняет операцию умножения кода на 2 , Для обеспечения первоначального соответствиямежду кодом частоты и частотой выходного сигнала в 2 раз возрастает коэффициент деления второго делителя16 частоты, что обеспечивается подачей кода номера октавы на управляющий вход этого делителя,За счет рассмотренных преобразований диапазон изменения задержки элементов 12,112.(Б) задержки ограничен в предложенном синтезаторе величиной 1/ИГ , а диапазон длительностей выходных импульсов формирователя15 импульсов - величиной 1/(21 ),Блок 7 формирования временныхинтервалов вырабатывает сигналы управляющие работой вычислительных ивыходных узлов, обеспечивая при необходимости радиоимпульсную форму выходного сигнала с периодом и длительностью радиоимпульсов, определяемымипоступающими из блока 1 ввода параметров кодами,На первом выходе блока 1 ввода параметров формируются коды периода и длительности радионмпульсов, на втором выходе - код начальной фазы, на третьем - коды параметров заданного закона изменения частоты или, например, номера программы переключения частот при синтезе дискретного частотного сигнала.Блок 8 формирования кода частоты для синтеза ЛЧ 1 ф-сигнала (фиг, 3) содержит коммутатор 19 кодов, сумматор 20 кодов и регистр 21. При нулевом сигнале на управляющем входе, соответствующем паузе радиоимпульсного выходного сигнала, сумматор 20 кодов включается в режим прямого пропускания, а коммутатор 19 кодов подключает к входу регистра 21 код начальной частоты К 1 , который и поступает на выход блока. При единичном сигнале на управляющем входе к вхо 1525694ду сумматора 20 кодов, переключенного в режим суммирования, коммутаторо 1 ч 19 подключается код скорости частотной модуляции К. При этом суммагор 20 кодов и регистр 21 образуют накопитель кода, выполняющий цифровое ин егрирование кода скорости и форми ующий линейно изменяющийся код ча тоты.,Для синтеза дискретного частотно о сигнала блок 8 Формирования кода ча тоты (фиг, 4) содержит счетчик 22 и зелпамяти 23,.Нулевым сигнал управления счетчик 22 устан вливается в начальное состояне, При единичном управляющем сигнал разрешается работа счетчика 22, кс 1 торый осуществляет последовательнь" перебор адреса узла 23 памяти. Н выходе узла 23 памяти формируется к д частоты, значение которого измен ется в соответствии с заданной проаммой. Выбор необходимой программы о уществляется кодом номера програм,.поступающим с блока 1 ввода парам тров.Блок 7 формирования верменных интервалов (фиг. 5) представляет собой счетчик 24 периода радиоимпульсфв и счетчик 25 длительности радиоифпульсов, выходы переполнения которых подключены к входам триггера 26. Кды периода радиоимпульсов и длитель нфсти радиоимпульсов подаются на вхо- дМ предустановки соответствующих сметчиков. Предустановка осуществляе 1 ся импульсом переполнения счетчика 24 периода радиоимпульсов.Накопитель 2 кода фазы выполнен и функционирует аналогично блоку 8 формрования кода частоты для синтеза ЛМ-сигнала (фиг, 3). При нулевом снгнале управления на выходе накопителя 2 кода Фазы устанавливается код начальной Фазы К, а при одиночномо сигнале управления формируется код Фазы в соответствии с кодом частоты, поступающим на вход.Код коррекции К, устраняющий ошибки дискретизации, вычисляется в арифметическом блоке 3. Этот код определяется как КлК Для формирования дополнительныхИмпульсов необходимо знать их периоледованиягде Е - частота сигнала на выходе 5 элемента ИЛИ 13,Вычислив код интерполяции К 1/Кмы можем определить значение необходимого периода следования ТтТ- КС д Иф 10 где Т- период следования тактовыхимпульсов.Код интерполяции К подается на 15управляющие входы элементов 12,1 12,(Н) задержки, которые и обеспечивают формирование дополнительных импульсов в соответствующие моменты времени. Кроме тогО, код интерполяции К управляет формирователем 14 импульсов, который вырабатывает импульсы с длительностью йффТ /2. Вычисление кода интерполяции Ктакже происходит в арифметическом блоке 3 (Фиг. 6).Код частоты К поступает на вход формирователя 27 кода обратной величины, С его выхода код интерполяции К поступает на вход регистра 29,2 и на первый вход перемножителя 28 кодов. На второй вход перемножителя 28 кодов поступает код фазы К, а на выходе формируется код коррекции К К/К , который поступает на вход регистра 29,1. Выходы регистров 29,1 35 и 29.2 являются выходами арифметического блока 3.Коды на выходе арифметического блока 3 появляются с задержкой на такт относительно момента появления импульса переполнения на выходе накопителя 2 кода Фазы. Для задержки этого импульса используется регистр 5.Блок 11 буферной памяти содержит(фиг. 7) два идентичных канала, один из которых осуществляет задержку кода интерполяции К, а другой кода номера октавы формируемого сигнала. Рассмотрим работу одного из каналов. Импульс переполнения осуществляет запись соот ветствующего ему кода в Один из регистров 31.134.1, номер которого определяется состоянием счетчика 47.1 и дешифратора 361. Кроме того, этот импульс увеличивает состояние счетчи ка на единицу, т.е. осуществляет подготовку схемы к записи следующего значения кода. При появлении импульса на выходе блока 4 управляемой за 525694 10держки происходит перезапись значениякода с одного из регистров 31,1341 в выходной регистр 351 черезмультиплексор 37,1 Выбор соответствующего регистра определяется состоянием счетчика 30.1, которое такжеизменяется с приходом каждого импчльса. Для правильной работы блока, 11необходимо при включении питанияустановить счетчики 47.1 и 30.1 в нулевое состояние.Блок управляемой задержки можетбыть выполнен по схеме фиг. 8, Частьрегулируемой задержки реализуется спомощью мультиплексора 40 и регистра38 сдвига, тактирование которого осуществляется с частотой 1, остальнаячасть - с помощью линии 39 задержки сотводами и мультиплексора. 41. Входной импульс подается на вход разрешения мультиплексора 40, а код коррекции К на управляющие входы мультиплексоров 40 и 41Возможна реализация всего диапазона регулируемой 25задержки только на основе многоотводной линии задержки. В этом случае регистр 38 сдвига и мультиплексор 40отсутствуют, а входной импульс подается на вход линии 39 задержки с отводами.Элементы задержки 12.112.Ю,работает аналогично блоку 4 управляемой задержки, но поскольку входныеимпульсы асинхронны с опорной частотой Е, то реализовать их можно толь 1 ко на основе многоотводной линииз аде ржки.Возможная реализация формирователя 14 импульсов показана на фиг. 9. 40Импульсы входной последовательностипоступают на вход линии 42 задержкис отводами и на вход установки высокого уровня триггера 44, Через времяопределяемое кодем интерполяции К(номером отвода, подключаемогомультиплексором 43), импульс черезмультиплексор 43 поступает на входсброса триггера 4. Таким образом, выходной поток импульсов имеет вид меандра,Второй делитель 16 частоты содержит двоичный счетчик 45 и мультиплексор 46. Входной сигнал подается натактовый вход двоичного счетчика 45.Мультиплексор 46 пропускает на выходлибо входной сигнал, либо сигнал свыхода одного из разрядов двоичногосчетчика 45 в соответствии с кодом номера октавы синтеэируемого сигнала. управляющий сигнал подается на разрешающий вход мультиплексора 46 и обеспечивает отсутствие сигнала на выходе в паузах между радиоимпульсами.Формула изобретенияЦифровой синтезатор сигналов, содержащий накопитель кода фазы, арифметический блок, блок управляемой зацеркки, регистр, причем информационный вьход накопителя кода фазы подключен к первому информационному входу арифметического блока, выход кода коррекции которого подключен к управляющему входу блока управляемой задержки, информационный вход которого подключен к выходу регистра, тактовый вход синтезатора подключен к тактовому входу блока управляемой задержки, о т л и ч а ю щ и й с я тем, что, с целью расширения диапазона частот синтезируемых сигналов, в него введены блок формирования временных интервалов, блок формирования кода частоты, блок сдвига кода частоты, Формирователь кода номера октавы, блок буферной памяти, (Б) элементов задержки, элемент ИЛИ, формирователь импульсов, два делителя частоты, причем тактовый вход синтезатора подключен к входу первого делителя частоты, выход которого подключен к тактовым входам блока формирования временных интервалов, блока формирования кода частоты, накопителя кода фазы, арифметического блока и регистра вход кода периода и длительности синтезатора подключен к входу блока формирования временного ин" тервала, выход которого подключен к первому управляющему входу второго делителя частоты, управляющему входу накопителя кода фазы и управляющему входу блока формирования кода частоты, информационный вход которого подключен к входу задания параметров синтезатора, вход кода начальной фазы которого подключен к входу кода начальной фазы накопителя кода фазы, выход блока формирования кода частоты подключен к информационному входу блока сдвига кода частоты и входу формирователя кода номера октавы, выход которого подключен к первому информационному входу блока буферной памяти з управляющему входу блокасднига кода частоты, выход которогоподключен к входу кода частоты накопителя кода Фазы и к второму информационному входу ариФметического блока,ввод переполнения накопителя кодаФаы подключен к инФормационному входу регистра, выход кода интерполяцииарМФметического блока подключен к второчу инФормационному входу буфернойпамяти, выход кода интерполяции котороГо подключен к управляющим входам(3-1) элементов задержки и управляющему входу Формирователя импульсов,выод которого подключен к информационному входу второго делителя частоты, второй управляющий вход каторогсподключен к выходу кода номера о,".двы блока буферной памяти, первый ивторой тактовые входы которого подключены к выходам регистра и блокауправляемой задержки, выход которогочерез последовательно соединенные(Ю"1) элементов задержки подключен к(Б) и непосредственно к Б-му входамэлемента ИЛИ, выход которого подключен к входу Формирователя импульсов,выход второго делителя частоты подключен к выходу синтезатора.1525694 ОтЙО оставитель С.Куроехред М.Дидык Корре Редактор Л.Пчолииска аксимиши Заказ 7227/44 Тираж 668 ПодписноеНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС113035, Москва, Ж, Раушская наб., д. 4/5 роизводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 1 О

СмотретьЗаявка

4405665, 17.03.1988

ВСЕСОЮЗНЫЙ ЗАОЧНЫЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ

КОЧЕМАСОВ ВИКТОР НЕОФИДОВИЧ, НЕЧАЕВ ИГОРЬ ВЛАДИМИРОВИЧ, РАКОВ ИГОРЬ АРЬЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: сигналов, синтезатор, цифровой

Опубликовано: 30.11.1989

Код ссылки

<a href="https://patents.su/9-1525694-cifrovojj-sintezator-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой синтезатор сигналов</a>

Предыдущий патент: Генератор ортогональных кодов

Следующий патент: Таймер

Случайный патент: Способ определения потребности бычков в обменной энергии