Устройство для вычисления функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1348829

Автор: Пьянков

Текст

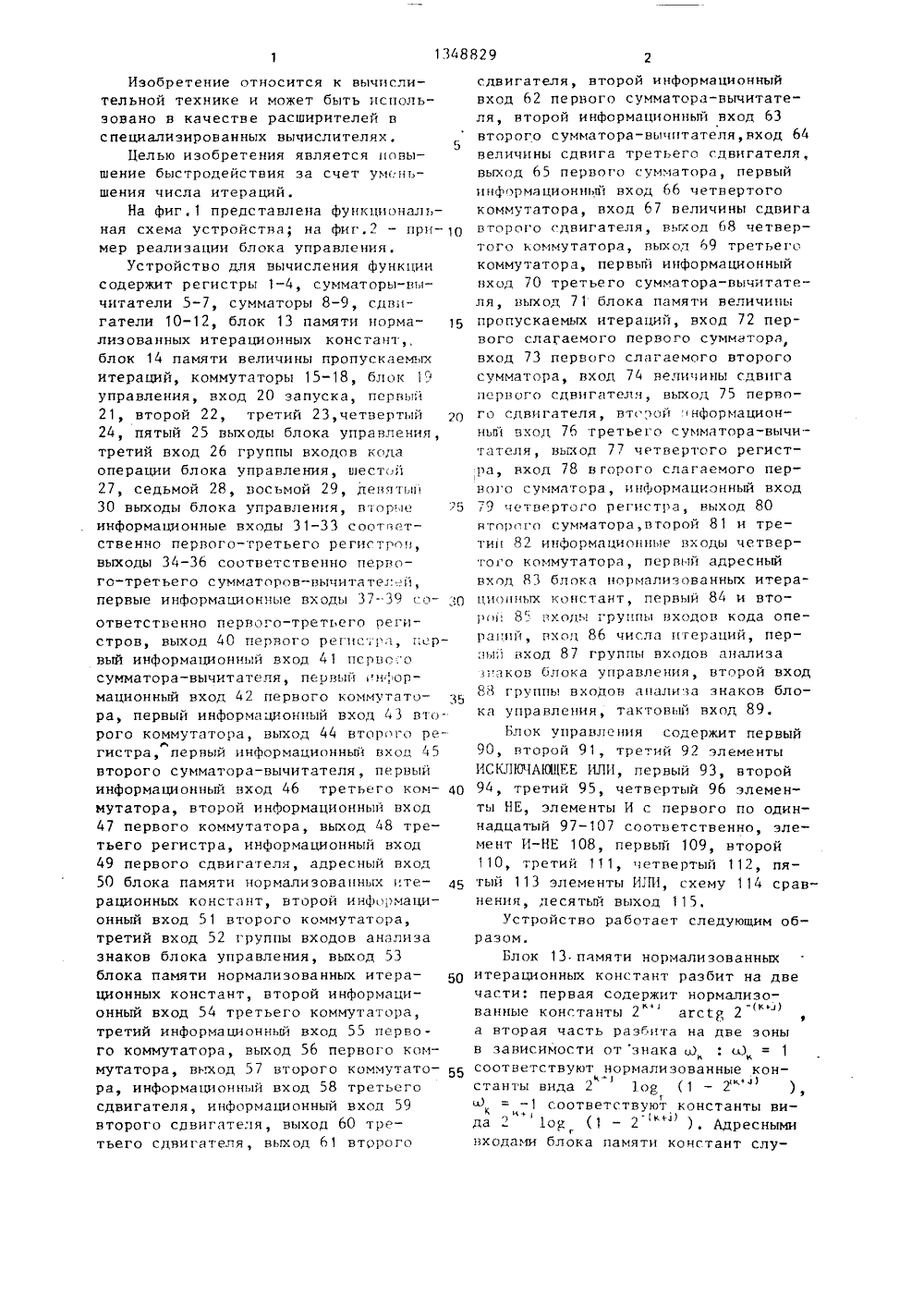

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК С 06 Р 7/54 САНИЕ ИЗОБРЕТЕН йМ Л 1,детельство СССР 6 Г 7/38, 1982, олов В,Б, Специ ссоры: итераци руктуры, М,: Ра 34-236, рис.5.1 ЛЯ ВЫЧИСЛЕНИЯ ФУН ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ А ВТОРСКОМУ СВИДЕТЕЛЬСТ(56) Авторское свУ 114 1399, кл, СБайков В.Л., Слизированные процные алгоритмы и си связь, 1985, с5. 19.(54) УСТРОЙСТВО Д 57) Изобретение относится к вычи ительной технике и может быть ис ЯО 1348829 А 1 пользовано в специализированных вычислителях в устройствах, работающих в реальном масштабе времени,Целью изобретения является повышениебыстродействия за счет уменьшениячисла операций, Устройство содержитрегистры 1-4, сумматоры-вычитатели5-9, сдвигатели 10-12, блок 13 памяти нормализованных итерационныхконстант, блок 14 памяти величиныпропускаемых итераций, коммутаторы15-18, блок 19 управления. В устройстве используется разновидность итерационного алгоритма Волдера (методсимметричных итераций) для вычисления ряда элементарных функций, 2 илИзобретение относится к вычислительной технике и может быть использовано в качестве расширителей вспециализированных вычислителях,5Целью изобретения является повышение быстродействия за счет уменьшения числа итераций.На фиг.1 представлена функциональ - ная схема устройства; на фиг,2 - прн мер реализации блока управления,Устройство для вычисления функции содержит регистры 1-4, сумматоры-вычитатели 5-7, сумматоры 8-9, сдвпгатели 10-12, блок 13 памяти норма лизованных итерационных констант блок 14 памяти величины пропускаемых итераций, коммутаторы 15-18, блок 9 управления, вход 20 запуска, первый 21, второй 22, третий 23,четвертый 20 24, пятый 25 выходы блока управления, третий вход 26 группы входов кода операции блока управления, шестой 27, седьмой 28, восьмой 29, девятып 30 выходы блока управления, вторы 25 информационные входы 31-33 соответственно первого-третьего регистроп, выходы 34-36 соответственно первого-третьего сумматоров-вычитател-.:й, первые информационные входы 37-.39 соответственно первого-третьего регистров, выход 40 первого регпс,р, первый информационный вход 4 1 перво о сумматора-вычитателя, первыйи,ормационный вход 42 первого коммутатора, первый информационный вход 43 второго коммутатора, выход 44 второго релгистра, первый информационный вход 45 второго сумматора-вычитателя, первый информационный вход 46 третьего ком мутатора, второй информационный вход 47 первого коммутатора, выход 48 третьего регистра, информационный вход 49 первого сдвигателя, адресный вход 50 блока памяти нормализованных ите рационных констант, второй информационный вход 51 второго коммутатора, третий вход 52 группы входов анализа знаков блока управления, выход 53 блока памяти нормализованных итера ционных констант, второй информационный вход 54 третьего коммутатора, третий информационный вход 55 первого коммутатора, выход 56 первого коммутатора, выход 57 второго коммутато ра, информационный вход 58 третьего сдвигателя, информационный вход 59 второго сдвигателя, выход 60 третьего сдвигателя, выход 61 второго сдвигателя, второй информационный вход 62 первого сумматора-вычитателя, второй информационный вход 63 второго сумматора-вычитателя,вход 64 величины сдвига третьего сдвигателя, выход 65 первого сумматора, первый информационный вход 66 четвертого коммутатора, вход 67 величины сдвига второго сдвигателя, выход 68 четвертого коммутатора, выход 69 третьего коммутатора, первый информационный вход 70 третьего сумматора-вычитателя, выход 71 блока памяти величинь; пропускаемых итераций, вход 72 первого слаГаемого первого сумматора, вход 73 первого слагаемого второго сумматора, вход 74 величины сдвига первого сдвигателн, выход 75 первого сдвигателя, второй:информационный вход 76 третьего сумматора-вычитателя, выход 77 четвертого регистра, вход 78 в горого слагаемого первого сумматора, информационный вход 79 четвертого регистра, выход 80 второго сумматора, второй 81 и третин 82 информационнье входы четвертого коммутатора, первый адресный вход 83 блока нормализованных итерационных констант, первый 84 и второй 8" входы группы входов кода операций, вход 86 числа итераций, первый вход 87 группы входов анализа ; аков блока управления, второй вход 88 группь 1 входов анализа знаков блока управления, тактовый вход 89,Блок управления содержит первый 90, второй 91, третий 92 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 93, второй 94, третий 95, четвертый 96 элементы НЕ, элементы И с первого по одиннадцатый 97-107 соответственно, элемент И-НЕ 108, первый 109, второй 110, третий 111, четвертый 112, пятый 113 элементы ИЛИ, схему 114 сравнения, десятый выход 115.Устройство работает следующим образом.Блок 13 памяти нормализованных итерационных констант разбит на две части: первая содержит нормализованные константы 2" агсг 8 2 а вторая часть разбита на две зоны в зависимости от знака а) : оЭ = 1нн соответствуют нормализованные конистанты вида 2 1 од ( - 2 " )гц = - 1 соответствуют константы вида 2 1 оя (1 - 2). Адресными входами блока памяти констант служит код 01+) ( п,где п - разрядность устройства, зддп д и еще одинразряд для выбора необходимой частиблока памяти.Блок 14 памяти величины пропускаемых итераций служит для хранениявеличин, означающих количество пропускаемых в процессе вычисленийитераций. Адресными входами блокаявляются старшие девять разрядов,включая знаковый, сводимого к нулюаргумента функции, который хранитсяв регистре 3.Устройство функционирует в пятирежимах,В первом режиме производится операция деления ) = А/В. Деление осуществляется в соответствии со следующими рекуррентными соотношениями: 10 15 20 4-1, если г , 0 2 =В - 1,6) =А, г =Оэ ь А/В, 30 При этом на входах 84, 85, 26 установлен код 010, а на входе 86 число равно и - 1. По сигналу начальной установки на входе 20 регистр 4 уста навливается в 0. В нулевом состоянии регистр 4 находится до начала следующего такта, для чего сигнал на ". чальной установки должен перекрывать синхроимпульс на выходе 21, по котоврому происходит прием исходных данныхалгоритма г = В - 1 в регистр 3о16, = А в регистр 1.В д-м такте работы в регистрах 1 и 3 находятся величины ги 6( 6 1),45 а в регистре 4 - величина Е. Таким образом, третий сдвигатель 12 пропускает операнды 6, сдвинутыми на 1 + 3 разрядов вправо (в сторону младших разрядов), второй сдвигатель 11 - г сдвинутыми на Е разрядовквправо, а первый сдвигатель 10 - г сдвинутыми на 3 разрядов влево (в сторону старших разрядов), При этом блок 14 памяти в соответствии с э55 старшими разрядами г выдает значекние 3. Тогда на входы 41, 70 сумматоров-вычитателей 5, 7 поступают опе-1, если 2) О,г =х,6,=0, 2=0,6, = 1 о 8(х) .Этому режиму соответствует код 001 на входах 84, 85 и 26. Аналогично, как и в предыдущем режиме, по сигналу установки на входе 20 регистр 4 обнуляется, а в регистрах 1 и 3 по приходу синхроимпульса записываются исходные данные: В в регистр 1 и г в регистр 3 с входов 37 и 39 соответственно. Вычисление 2 по перКвому рекуррентному соотношению в (2) осуществляется точно так же, как и ранды Я и 22 к соответственно, а на входы 62, 76 - соответственно-(к +)2 г и О 2 . Сумматоры-вычитатели 5, 7 производят действия согласно алгоритму (1). Результаты Ок и г . записываются по синхроимпульсу в регистры 1, 3 соответственно. На входуправления сдвигом третьего сдвигателя 12 поступает величина 1+) с выхода 65 первого сумматора 8,который производит суммирование величины 1 из регистра 4 с величиной из блока 14 памяти, На вход управления сдвигом сдвигателя 11 через четвертый коммутатор 18 поступает величина 1 с с выхода 77 регистра 4. На вход 74 величины сдвига первого сдвигателя 10 всегда подается величина 3 с выхода 71 блока 14 памяти, Величина 1 в регистре 4 после каждой итерации увеличивается на величину 1.После того как значение 1 в регистре 4 станет равным или большим числа и - 1, установленного на входе 86, схема 114 сравнения выработает сигнал запрета дальнейшей работы устройства. По этому сигналу произойдет блокировка синхроимпульсов, подаваемых на вход 89 блока управления. В регистре 1 будет находиться результат операции деления 8= А/В.Во втором режиме производится вычисление функции 1 оргх в соответствии со следующими рекуррентными со отношениями:30 45 К+зк,= 2 а - 2 1 о( + в операции деления. Вычисление О вК соответствии с вторым рекуррентным соотношением (2) осуществляется следующим образом. На вход сдвигателя 12 через коммутатор 15 поступает константа 2"1 о 8 (1 + 2 " ), считанная погадресу ц из блока 13 памяти нормализованных итерационных констант, На вход управления сдвигом третьего сдвигателя 12 поступает величина с выхода первого сумматора 8, и третий сдвигатель 12 производит сдвиг на разрядов вправо, т.е, на информационный вход сумматора-вычитателя 5 подается 1 оя (1 + 2 " ), на управляющем входе в соответствии с кодом операции устанавливается "1" и сумматор-вычитатель 5 производит операцию вычитания 8 -1 оя ( 1+2 " ) . Ре 1 -20 эультат вычитания в начале следующего такта записывается в регистрВ д-м такте в регистре 1 находится величина 6 , в регистре 3 - г а в регистре 4 - Е(Е. с 1). На выходе 26 65 сумматора 8 получена величина с + 3, которая подается на вход управления сдвигом третьего сдвигателя 12 и на вход 83 блока 13 памяти нормализованных итерационных констант. На другой вход блока 13 памяти в соответствии с кодом операции из блока 19 управления подается "0", а на третий вход - значение со вырабатываемое в блоке 19 управления в зависимости от кода операции и знакового разряда регистра 3. В соответствии с тим адресом из блока 13 памяти считывается нормализованная константа 2 " 1 о 8 (1 + 2 ), кото 40 рая подается через первый коммутатор 15 на вход сдвигателя 12 и сдвинута в нем на 1 +разрядов вправо. Результат сдвига подается на вход 62 сумматора-вычитателя 5, на вход 41 которого подается величина О . СК выхода 34 сумматора-вычитателя 5 величина О -1 ор (1 + 2 ) запишется по входу 31 в регистр 1. При достижении регистром 4 состояния п - 1 схема 114 сравнения выработает сигнал запрета и останавливает вычислительный процесс, При этом в регистре 1 находится результат 6= 1 оя х.Вычисление функции г " осуществляется в соответствии со следующими рекурренчными соотношениями: О . = 0 +д у 2 ; (3)з 1 яп сдк = з 1 яп гг = х , 0 = 1, г = О, 6: г",В этом режиме на входах 84, 85 и 26 кода операции устанавливается код 110.В нулевом такте по сигналу установки по входу 20 происходит обнуление регистра 4 и по синхроимпульсу на входе 21 запись исходных данных в регистры 1 - 3: О, в регистр 1 и 2, г в регистр 3, В соответствииОс кодом операции на первом коммутаторе 15 выбирается вход 42, на втором коммутаторе 16 - вход 43, на третьем коммутаторе 17 - вход 54 и на четвертом коммутаторе 18 - вход 66, В первом такте я, из регистра 3 поступает на вход 49 сдвигателя 10На вход 50 блока 14 памяти величины пропускаемых итераций поступают старшие з разрядов г и на выходе 71 устанавливается соответствующее значение 3, поступающее на вход 74 управления сдвигом сдвигателя первого 10 и на вход 72 первого сумматора 8. На входе управления сдвигом третьего и второго сдвигателей 12 и 11 поступает также величина 3, но уже с выхода 65 первого сумматора 8, На вход 76 сумматора-вычитателя 7 поступает величина 2 г , а на вход 70 черезотретий коммутатор 17 с выхода 53 блока 13 памяти поступает нормали-. зованная константа 2" 1 од (1 + 2 ).г На управляющем входе сумматора-вычитателя 7 в соответствии с кодом операции устанавливается "1", и сумматор-вычитатель 7 производит вычитание согласно (3). На управляющие входы сумматоров-вычитателей 5 и 7 иэ блока управления подается знак о) ("0" при Э = 1 и " 1" при сд = - 1); На входы 41 и 45 сумматоров-вычитателей 5 и 7 иэ регистров 1 и 2 соответственно считывается значение 6, а на входы 62 и 63 этих же сумматоров-вычитателей с выходов сдвигателей 12 и 11 - величина 6, 2 ". Сумматоры-вычитатели производят сложение или вычитание в зависимости отзнака и) . Результат, равный 8,записывается в начале следующего1348829 45 г, = 2 г - о)о)к 50 з 1.цп О-)= з).яп к 55 О = агсГц у/х,такта в регистры 1 и 2, В регистр записывается с выхода первого сумматора 8 величина ), а в регистр 3 с выхода 36 регистра 3 - величина г5Аналог ично в г-м такте работы регистр 4 находится в состоянии 1, в регистрахи 2 - текущее значение 6 , а в регистре 3 - текущее значение я, Третий и второи сдвигатели 12 и 11 производят сдвиг 6 на 1 с +кразрядов вправо, д первый сдвигдтелт 10 - ндрдэрпцо, влево. Значение 1 с1 получается суммированием в первом сумматоре 8 значения 1 с и считанного из блока 14 памяти значенияИз блока )3 памяти нормализованных итерационных кснстант на вход 70 сумматора-вычитдтеля 7 считывается цорк.; мдлизсцднндя константа 21.оя (1 +.к ) г +). При этом ца первый вход бпока 13 из б - ,д 19 управления пода е т с ч 0 , д . д в то и ой вход - з ц д к )лчд вход . 3 - д ц д ч е ни е 1; + ) с выхода 65 сулл;дторд 8, 25Таким образом, сумматор-вычитдтельсовместно с первым сдвигателем 10 производит вычисления согласно пер - вому рекуррентцому соотношению в (3), а сумматоры-вычитатели 5 и 6 совмест но со сдвигдтеляля 12 и 11 - вычисления согласцо второму соотношения в (3). Результаты вычислений г ик )к, в начале . + 1)-го такта записываются в регистр 3 и в регистрыи 2.35 11 осле того как итерационный индекс 1 с, хранящийся в регистре 4, достигает значения п - 1, установленного на входе 86 схемы 114 сравнения, схема вырабатывает сигнал запрета и вычисления заканчиваются.Функция агсСд у/х вычисляется в устройстве в соответствии со следующими рекуррентными соотношениями:- (2 к+.)о),= а) +и) г 2(4)8, = О+ и)к агсгд 2 г=у, о-) =х,6=О, г=О,Этому режиму соответствует код 111 на входах 84, 85, 26 кодл операции, Аналогично, как и в предыдущих режимах, по сигналу на входе 20 региструстанавливается в "0", а в регистрах 1-3 по синхроимпульсу записываются исходные данные: в регистр 1 6 ,в регистр 2 - ь)и в регистр 3 к В первом такте к, из регистра 3 через гдвигатель 10 поступает на вход 76 сумматора-вычитателя 7 и одновременно через вход 51 коммутатора 15, с твпгатель 11 - цд вход 63 сумматора-вычитателя 6, Переменная из регистра 2 поступает на вход 45 сумматора-вычитателя 6 и одновременно через вход 46 коммутатора 17 - нд вход 70 сумматора-вычптателя 7. Переленцдя О из регистра 1 поступает цд вход 41 сумматора-вычптдтеля 5, на вход 62 которого через вход 47 коммутатора 15 и сдвигдтеля 12 из блока 13 пдмяти подается константа дгссд 2. Блок управления днализи - рует знаковый разряд регистра 3, поступивший ца его вход 52, и выдает сигналы управления знаком алгебраического сложения нд управляющие входы суммдторов-вычитателей 5-7, согласно алгоритму (4). При этом сдвигдтель 12 производит сдвиг нормализованной константы 2 агсг.р 2наразрядов вправо, т.е. производит денормдлизацию константы. На вход 67управления сдвигом сдвигателя 11 через вход 81 коммутатора 18 подаетсяс выхода сумматора 9 значение 21 с +равное в первом такте ), Величина21 + 3 получается в сумматоре 9 спомощью суммирования значения 1, хранящегося в регистре 4 и значенияиз блока 14 памяти, при этом для получения величины 21 выходы регистра 4подключаются к входу 78 сумматора 9со смещением влево на один разряд,В начале следующего такта результаты суммирования И ) и г записываются в регистры 1-3 соответственно,по синхроимпульсу с выхода 21,а в регистр 4 - значение 3 с выхода 65 сумматора 8, Аналогично, в ).-м такте работы регистр 4 находится в состоянии О = 1 с .1 с). Таким образом, сдвигатель 12 пропускает нормализованную константу 2 дгсс 1; 2 "со сдвигом на 1 с + 1 разрядов вправо, поскольку на выходе 65 суммато - , 1348829 10)к оагсг 8 2 К 16 =20 - ч)к+ к К я 1 гп с,) = я 1,п д г =0 ц) = 1 0 =Ч ь о ф о г, - к я 1 пО.п - к сояР 40 О= 0 В начале выполнения операции на входах 84, 85 и 26 устанавливается код 100, а на входе 26 код, соответствующий максимально возможному числу итераций, По сигналу начальной установки на входе 20 и синхроимпульсу на выходе 21 в регистры 1-3 записываются исходные данные; г в реогистр 1, и) в регистр 2 и 6, в регистр 3, регистр 4 обнуляется. На управляющих входах коммутаторов 15-18 в соответствии с кодом операции установлены коды, подключающие выход 40 регистра 1 через коммутатор 16 к входу 59 сдвигателя 11, выход 44 регистра 2 через коммутатор 15 к входу 50 55 ра 8 установлено значение 1 +Сдвигатель 11 пропускает значение г из регистра 3, сдвинутым вправо на 21 с + 3 разрядов, так как на выходе5 сумматора 9 устанавливается это значение, а сдвигатель 10 - значение г из регистра 3, сдвинутым на 3 разрядов влево, Сумматор-вычитатель 7 выполняет действие (сложение или вычитание) согласно первому рекуррентному соотношению в (4), сумматор-вычитатель 6 - согласно второму, а сумматор-вычитатель 5 - согласно третьему. Полученные результаты в нача ле следующего такта записываются в регистры 3-1 соответственноВ регистр 4 записывается значение 1 +После того как состояние регистра 4 равно или больше кода, заданного по входу 86, сигнал на выходе схемы 114 сравнения заблокирует дальнейшие вычисления, При этом в регистре 1 окажется результат операции, т.е.агссд у/х. 25Вычисление функций 1 я 1 пйи 1 сову осуществляется в соответствии со слс 58 сдвигателя 10, выход 53 блока 13 памяти через коммутатор 17 к входу 70 сумматора-вычитателя 7 и выход 65 сумматора 8 к входу 67 сдвигателя 11. В следующем первом такте г из регистра 1 поступает на вход 4 1 сумматора-вычитателя 5 и через вход 43 коммутатора 16 и сдвигатель 11 на вход 63 сумматора-вычитателя 6,ц) из регистра 2 - на вход 45 сумматоравычитателя 6 и через вход 47 коммутатора 16 и сдвигатель 12 на вход 62 сумматора-вычитателя 5, 6 из регистра 3 через сдвигатель 10 - на вход 76 сумматора-вычи 1 ателя 7. На выходе 65 сумматора 8 устанавливается значение, равное 3 (количеству пропускаеюх в этом такте н,левых итераций), по адресу 1 на вход 83 из блока 13 памяти считыв; ется константа 2 агсс 8 2 , которая через вход 54 коммутатора 17 поступает на вход 70 сумматора-пычитателя /,Так).м оораэом, сдвигатели 12 и 11 сдвигают информацию на ) разрядов вправо, а сдвигатель 10 - на 1 разрядов влево. Старший (знаковый) разряд операнда 0 по входу 52 поступает в блок 19 управления, вырабатывающий знак алгебраического суммирования для сумматоров-вычитателей 5-7, которые производят действия согласно рекуррентным соотношениям (5) и результаты г , и 1, и О по синхросигналу с выхода 21 записываются в регистры 1-3 соответственно.В 1-м такте работы устройства регистр 4 находится в состоянии 1(11) и сдвигатели 12 и 11 пропускают операнды, сдвинутыми вправо на 1 с + 3 разрядов, а блок 13 памяти констант выдает по адресу 1 + 3 константу 2 " агсс 8 2 ") . Сумматоры-вычитатели 5-7 производят действие согласно алгоритму (5), результаты г , сд и, записываются в к+зк+ к+1регистры 1-3 соответственно, а в регистр 4 записывается значение 1 + После того как состояние регистра 4достигает или превышает значение кода по входу 86 схемы 114 вырабатывается сигнал сравнения и запрещает дальнейшую работу устройства, При этом в регистрах 1 и 2 оказываются записанными результаты г= 1 ядпМ и ц 3 = 1 соя. Учет коэффициента деформации вектора 1 в полученных соотношениях может быть проведен с по.мощью выполнения операции деленияи получения функции СдМ,Блок управления работает следующимобразом,Схема, собранная на элементах 90,591, 93, 94, 103, 104 и 110, предназначена для инверсии знакового разряда регистра 3 в операциях деления ивычисления функции 1 оях. В началевыполнения операции при записИ в регистры 1-3 исходных данных инвертируется знаковый разряд операнда, записываемого в регистр 3. При этом старший (знаковый) разряд записываемогов регистр 3 операнда подается на вход87 блока 19 управления и с него напервый вход элемента ИСКЛЮЧАКЦЕЕ ИЛИ90, на второй вход которого с входа84 кода операции в операциях деленияи логарифмирования подается ноль, ав остальных операциях - единица. Навыходе элемента НЕ 93 образуется инвертированное значение знакового разряда входного числа, которое при действии на входе 20 сигнала установкипроходит через элементы 103 и 110 навход 115 знакового разряда регистра3. Аналогично производится учет знака величины сд на элементах 91, 94, Зп104 и 110. В этом случае инвертируется знаковый разряд числа, получаемого на входе 88 сумматора-вычитателя 7 в процессе выполнения этих операций. В остальных операциях инверсии35знакового разряда не будет, так какна вторых входах элементов 90 и 91будет единица, находящаяся на входе 84Элементы ИСКЛЮЧАКЕ 1 ЕЕ ИЛИ 92 и НЕ95 служат для формирования знака величины д , с помощью знакового разряда регистра 3, поступающего на вход52, а знак ,) поступает через выход23 на второй управляющий вход блока13 памяти и на первый вход сумматора-вычитателя 6,Схема 114 сравнения и элементИЛИ 109 служат для остановки работыустройства, после того как индекс итераций 1, хранящийся в регистре 4 ипоступающий из него на вход 78, достигает или превышает код, соответствует максимальному значению индекса итераций и заданный по входу 86,Остальные элементы блока 19 управления (97-102, 105-108 и 111-113)служат для выработки сигналов управления коммутаторами 15-18 (вход 26 и выходы 27-30) сигналов управления сложением-вычитанием сумматоров-вычитателей 5, 7 (выходы 24, 25) и сигнала управления для блока 13 памяти в зависимости от кода операции,установленного на входах 84, 85 и 26.Формула и з обретенияУстройство для вычисления функции, содержащее три регистра, три сумматора-вычитателя, два сдвигателя, четыре коммутатора, блок памяти нормализованных итерационных констант, блок памяти величины пропускаемых итера)ций,причем выходы первого и второго регистров соединены с входами первых операндов соответственно первого и второго сумматоров-вычитателей, выходы второго и третьего сумматороввычитателей соединены с первыми информационными входами соответственно второго и третьего регистров, выход первого регистра и выход блока памяти нормализованных итерационных констант соединены соответственно с первым и вторым информационными входами первого коммутатора, выходы старших разрядов третьего регистра соединены с адресными входами блока памяти величины проПускаемых итераций, выход первого регистра соединен с первым информационным входом второго коммутатора, выход блока памяти величины пропускаемых итераций соединен с входом величины сдвига первого сдвигателя, выход второго регистра соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом блока памяти нормализованных итерационных констант, третий информационный вход третьего коммутатора соединен с выходом второго сдвигателя, информационный вход которого соединен с выходом второго коммутатора, входы первого и второго операндов третьего сумматора-вычитателя соединены с выходами соответственно третьего коммутатора и первого сдвигателя, о т л и ч а - ю щ е е с я тем, что, с целью повышения быстродействия за счет уменьшения числа итераций, в него дополнительно введены два сумматора, четвертый регистр и блок управления, причем выход первого сумматора-вычитателя соединен с первым информационным входом первого регистра, первый, второй и третий входы начальной установки данных устройства соединены с вторыми информационными входами соответственно первого, второго и третьего регистров, выход третьего регистра соединен с вторым информационным входом второго коммутатора и с информационным входомпервого сдвигателя, выход первого коммутатора соединен с информационным входом третьего сдвигателя, выходы третьего и второго сдвигателей соединены с входами второго операнда соответственно первого и второго сумматоров-вычитателей, вьгход блока памяти величины пропускаемых итераций соединен с входами первых слагаемыхпервого и второго сумматоров, входвторого слагаемого первого сумматора 10 соединен с выходом четвертого регистра, информационный вход которогосоединен с выходом первого сумматора,выход четвертого регистра соединен со 25сдвигом на один разряд в сторонустарших разрядов с входом второгослагаемого второго сумматора, выходпервого сумматора соединен с входомвеличины сдвига третьего сдвигателя 30и первым информационным входом четвертого коммутатора, второй и третийинфорМационные входы которого с.оединены соответственно с выходом второго сумматора и выходом четвертого. регистра, старший разряд из группытретьего входа начальной установкиданных устройства и выходы старшихразрядов третьего регистра и третьегосумматора-вычитателя соединены с 40группой входов анализа знаков итерационных переменных блока управления,вход запуска и тактовый вход устройства соединены с одноименными входамиблока управления, группа входов кода 4операции устройства соединена с одноименной группой входов блока управления, вход числа итераций устройствасоединен с одноименным входом блокауправления, выход первого сумматора 0соединен с первым разрядом адресного входа блока памяти нормализованных итерационных констант и входомпризнака окончания итерации блока управления, первый выход блока управления соединен с синхронизирующимивходами первого, второго и третьегорегистров, второй выход блока управления соединен с вторым разрядом ад. ресного входа блока памяти нормализованных итерационных констант,третий выход блока управления соединен с третьим разрядом адресного входа блока памяти итерационных констант и управляющим входом второго сумматора-вычитателя, четвертый и пятый выходы блока управления соединены с управляющими входами соответственнопервого и третьего сумматоров-вычитателей, третий вход группы входов кода операции блока управления и шестой выход блока управления соединены с управляющими входами первого коммутатора, управляющий вход второго коммутатора соединен с седьмым выходом блока управления, восьмой и девятый выходы блока управления соединены с управляющими входами третьего и четвертого коммутаторов, десятый выход блока. управления соединен с входом старшего разряда третьего регистра, вход начальной установки блока управления соединен с входами сброса первого, второго, третьего регистров и четвертого регистров, причем блок управления содержит три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре элемента НЕ, одиннадцать элементов И, элемент И-НЕ, пять элементов ИЛИ и схему сравнения, входы первого и второго операндов схемы сравнения соединены соответственно с входами признака окончания итерации и числа итераций блока управления, выход схемы сравнения соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с тактовым входом блока управления, выход первого элемента ИЛИ соединен с первым выходом блока управления, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с первого по третий, элементов И с первого по четвертый и элемента И-НЕ соединены с первым входом группы входов кода операции блока управления, второй вход которой соединен с вторыми инверсными входами первого и второго элементов . И, вторым входом элемента И-НЕ и с первыми входами пятого и шестого элементов И, третий вход группы входов кода операции соецинен с вторыми входами третьего и четвертого элементов И, вторые входы элементов ИСКЛЮЧАКЩЕЕ ИЛИ с первого по третий соединены соответственно с первым, третьим и вторым входами группы входов анализа знаков итерационных переменных15 6 1348829 Г 1 Х блока управления, выходы первого и второго элементов ИСКЛЮЧАКЦЕЕ ИЛИ соединены через соответственно первый и второй элементы НЕ с первыми входами соответственно седьмого и восьмо 5 го элементов И, второй вход седьмого элемента И и второй инверсный вход восьмого элемента И соединены с входом запуска блока управления, выходы седьмого и восьмого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с десятым выходом блока управления, выход"третье го элемента ИСКЛЮЧАКПЕЕ ИЛИ соединен с входом третьего элемента НЕ и с первыми входами девятого и десятого элементов И, выход третьего элемента НЕ соединен с третьим выходом блока управления, с первым входом одиннадцатого и вторым входом пятого элементов И, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, вторым входом девятого элемента И и шестым выходом блока управления, выход девятого элемента И соединен с первым входом четвертогоэлемента ИЛИ, второй и третий входыкоторого соединены с выходами соответственно пятого и второго элементов И, выход четвертого элемента ИЛИсоединен с четвертым выходом блокауправления, выход элемента И-НЕ соединен с вторым входом одиннадцатогоэлемента И, выход которого соединенс первым входом пятого элемента ИЛИ,второй и третий входы которого соединены с выходами соответственно десятого и шестого элементов И, выход пятого элемента ИЛИ соединен с пятымвыходом блока управления, выход третьего элемента И соединен с вторымвходом третьего элемента ИЛИ,с вторым входом десятого элемента И и свосьмым выходом блока управления, выход третьего элемента ИЛИ соединенс вторым выходом блока управления,выход четвертого элемента И соединенс вторым входом шестого элемента Ии с девятым выходом блока управленияи через четвертый элемент НЕ - с седьмым выходом блока управления.

СмотретьЗаявка

4090462, 28.04.1986

ПРЕДПРИЯТИЕ ПЯ В-2969

ПЬЯНКОВ ЕВГЕНИЙ КОНСТАНТИНОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычисления, функции

Опубликовано: 30.10.1987

Код ссылки

<a href="https://patents.su/9-1348829-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции</a>

Предыдущий патент: Устройство для воспроизведения функций

Следующий патент: Устройство для вычисления синуса и косинуса угла табличным методом

Случайный патент: Подъемник