Устройство для определения фазы спектральных составляющих

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

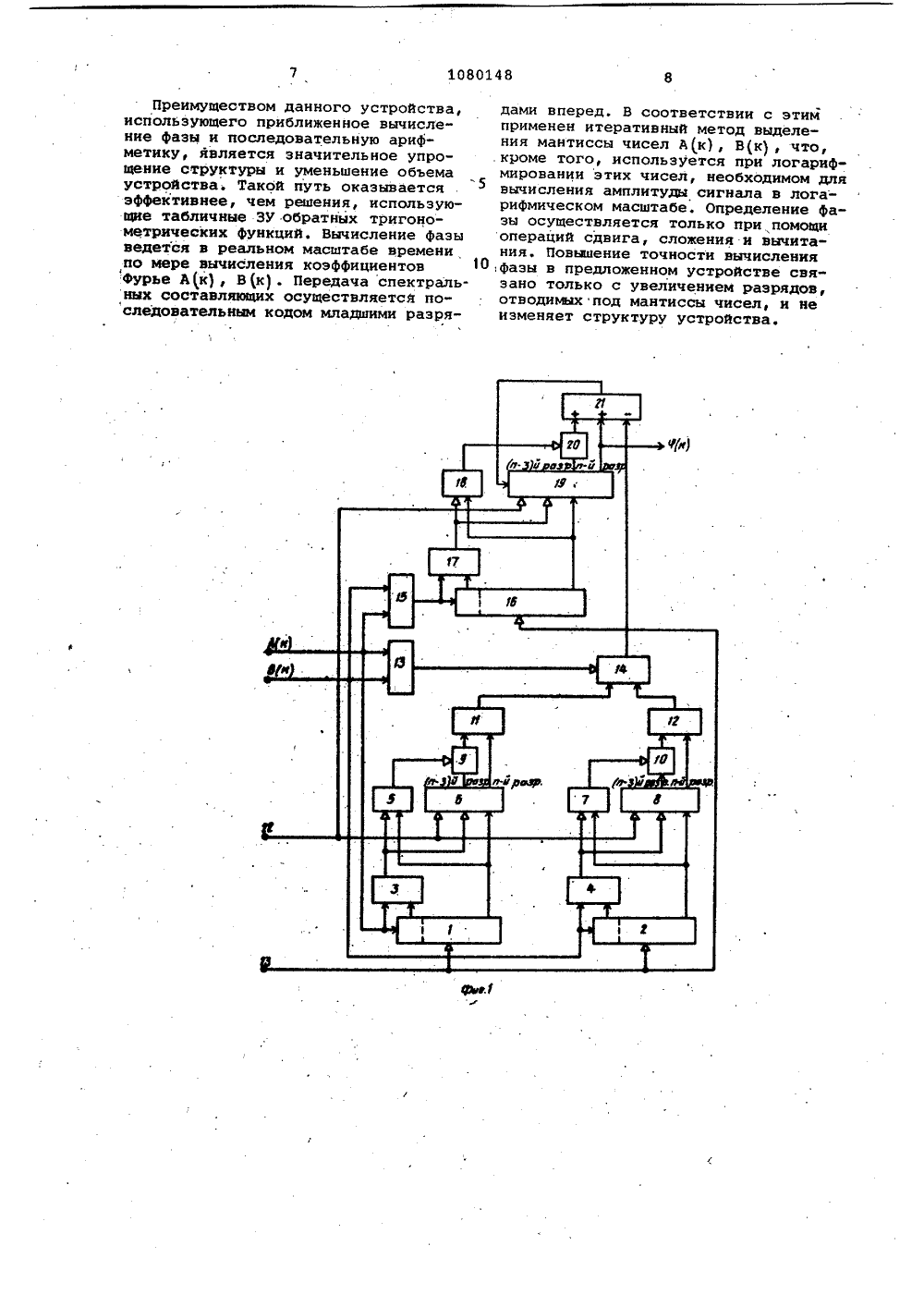

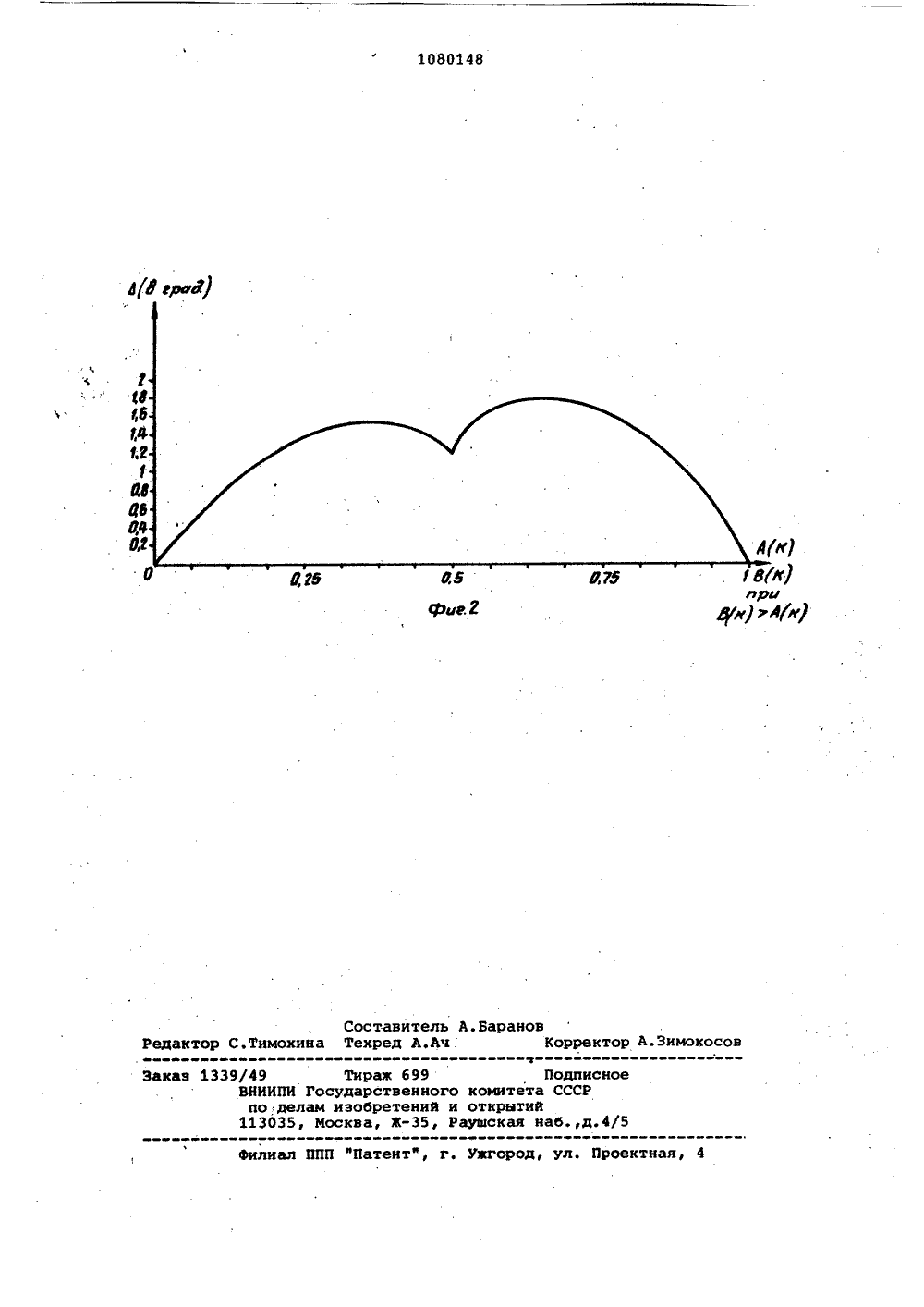

% ч1 И,46 Ф К АВТОРСНОМУ СВ ТЕЛЬСТВУ СУДАРСТВЕННЫЙ НОМИТЕТ ССС ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ.,(71) Львовский ордена Ленина поли:.технический институт им. Ленинского(56) 1, Авторское свидетельство СССР1 Ф 78823 ф кл. СОб. 15/36 ю 1978 ф2. Иуссар Д., Гангюли У. Экспрессанализ, кинетики система .- прибордпя анализа передаточной функции вреальном масштабе времени.ТИИЭР,т.65, 1977, Ф 5, с. 184 (прототип).(54)(57) УСТРОЙСТВО. ДЛЯ ОПРЕДЕЛЕНИЯФАЗЫ СПЕКТРАЛЬНЫХ СОСТАВЛЯЮЩИХ,сойЬржащее первый и второй регистры, блок сравнения и первый мультиплексор, управляющий вход которогосоединен с выходом блока сравнения,.первый и второй входы которого являются соответственно первым ивторым информационными входами уст.ройства, о т л и ч а ю щ е е с ятем, что, с целью упрощения устрой.ства, оно содержит третий регистр, .три. сдвиговых регистра, три элемейтаНЕРАВНОЗНАЧНОСТЬ, три триггера, четйре одноразрядных сумматора, второй,;третий и четвертый мультиплексоры,причем первый вход блока сравнения,объединен с первым входом первого.элемента НЕРАВНОЗНАЧНОСТЬ и инфор-:мационным входом первого. регистра,выход стараего разряда которого;подключен ко второму входу первогоэлемента НЕРАВНОЗНАЧНОСТЬ, выходкоторого соединен с.тактовым входомпервого сдвигового регистра и тактовым входом первого триггера, выходкоторого подключен к управляющему:входу второго мультиплексора, выходкоторого соединен с первым входомпервого одноразрядного сумматора,Ъ выход которого соединен с первым входом первого мультиплексора, второй вход которого соединен с выходом второго одноразрядного сумматора, первый вход которого подключен к выходу третьего мультиплексора, уп.равляющий вход которого подключен к выходу второго триггера, тактовый вход которого объединен с тактовым входом второго сдвигового регистра и подключен к выходу второго элемента НЕРАВНОЗНАЧНОСТЬ, первый вход которого подключен к выходу. старщего разряда второго регистра, информационный вход которого объединен со вторым входом второго элемента НЕРАВНОЗНАЧНОСТЬ и вторым входомблока сравнения;информационный выход .первого регистра подключен к установочному входу первого триггера и информационному входу первого сдви. С гового регистра, выходы ( П -3)-го и й -го разрядов которого соединены соответственно со входом второго мультиплексора и вторым входом первого одноразрядного сумматора, ин.формационный выход второго регистра соединен с установочным входом второго триггера и информационным входом второго сдвигового регистра, выходы (,и -3)-го и п -го разрядов которого соединены соответственно со вхо дом третьего мультиплексора и вторым входом второго одноразрядного сумматора, выход первого мультиплексора подключен к первому входу третьего одноразрядного сумматора, второй вход которого соединен с вЫходом чет,вертого мультиплексора, управляющий вход которого подключен к выходу третьего триггера, тактовый вход которого объединен с тактовым входом третьего сдвигового регистра и подключен к выходу третьего элемента НЕРАВНОЗНАЧНОСТЬ, первый вход которого соединен с выходом старыего1080148 разряда третьего регистра, информационный вход которого объединен совторым входом третьего элемента НЕРАВНОЗНАЧНОСТЬ и подключен к выходучетвертого одноразрядного сумматора,первый и второй входы которого объединены соответственно с первым ивторым входами блока сравнения, информационный выход третьего регистра подключен к установочному входутретьего триггера и информационному,входу третьего сдвигового регистра,выходы ( ь -3) -го и п -го. разрядовкоторого подключены соответственноко входу четвертого мультиплексораИзобретение относится к вычислительной технике, в частности к специализированным вычислительным устройствам, и рредназначено для вычисления фазы спектральных состав ляющих в спектроанализаторах в реальном масштабе времени.Известно устройство для определения фазы спектральных составляющих исследуемого сигнала, содержащее 10 операционные регистры, сумматор, блок сравнения, мультиплексор, двухканальный блок логарифмирования, блок вычитания 11 .Однако такое устройство характеризуется сложностью схеваа, наличием дорогостоящих узлов, таких как логарифматор, предполагающий наличие ПЗУ.Наиболее близким по технической сущности к изобретению является уст.ройство,содержащее операционные регистры, мультиплексор, блок сравнения кроме того, в него входят дели.тель, ПЗУ, ряд ключей. При этом уп равляющий вход мулвтиплексора соединен с выходом блока сравнения, первыФ и второй входы которого являются соответственно первым и вторым информационными входами устройства 2 .Недостатком этой схема являешься наличие сложных и дорогостоящих узлов, таких как делитель и 9-разрядное ПЗУ.Целью изобретения является упрощение устройства для определения фазы спектральных составлякаих.Указанная цель достигается тем, что устройство для определения фазы спектральных составляющих, содержащее первый и второй регистры, 40 блок сравнения и первый мультиплексор, управляющий вход которого соединен с выходом блока сравнения, пер. 4 Ь третьему входу третьего одноразрядного сумматора, выход которого подключен ко входу последовательной записи информации третьего сдвиговогб регистра, выход п -го разряда которого является информационным выходом устройства, тактовые входы первого, второго и третьего регистров объединены и являются тактовым входом устройства, а входы управления сдвигом первого, второго и третьего сдвиговых регистров объединены и являются входом задания количества сдвигов устройства. вый и второй входы которого являютсясоответственно первым и вторым информационными входами устройства, содер.жит третий регистр, три сдвиговыхрегистра, три элемента НЕРАВНОЗНАЧНОСТЬ, три триггера, четыре одноразрядных сумматора, второй, третий ичетвертый мультиплексоры, причемпервый вход блока сравнения объединен с первым входом .первого элемента НЕРАВНОЗНАЧНОСТЬ и информационнымвходом первого регистра, выход старщего разряда которого подключен ковторому входу первого элемента НЕРАВНОЗНАЧНОСТЬ, выход которого соединен с тактовым входом первого сдвигового регистра и тактовым входомпервого триггера, выход которогоподключен к управляющему входу второго мультиплексора, выход которого соединен с первымвходом первого одноразрядного сумматора, выходкоторого соединен с первым входомпервого мультиплексора, второй входкоторого соединен с выходом второго одноразрядного суьиатора, первыйвход которого подключен .к выходутретьего мультиплексора, управляющийвход которого подключен к выходувторого триггера, тактовый входкоторого объединен с тактовым входомвторого сдвигового регистра и подключен к выходу второго элементаНЕРАВНОЗНАЧНОСТЬ, первый вход которого подключен к выходу старшегоразряда второго регистра, информационный вход которого объединен совторым входом второго элемента НЕРАЭНОЗНАЧНОСТЬ и вторым входом блокасравнения, информационный выход первого регистра подключен к установочному входу первого триггера и информационному входу первого сдвнгового регистра, выходы и -3 -го и Ь-го,1080148вый регистр 19, мультиплексор 20, одноразрядный сумматор 21, вход задания количества сдвигов 22, такто. вый вход 23.На фиг. 1 пькаэана функциональная схема предлагаемого устройства, на фиг. 2 - график погрешности опреде ления фазы.Устройство содержит регистры 1, 2, элементы НЕРАВНОЗНАЧНОСТЬ 3, 4, триггер 5, сдвиговый регистр б, триггер 7, сдвиговый регистр 8, мультиплек-, 60 соры.9, 10, одноразрядные сумматоры 11, 12, блок сравнения 13, мультиплексор 14, одноразрядный суима тор 15, регистр 16, элемент НЕРАВНОЗНАЧИМОСТЬ 17, триггер 18, сдвиго , д Устройство работает следующимобразом.Вычисленные коэффициенты преобразования фурье Ак), В(к) в последовательном двоичном коде вводятсямладшими разрядами вперед в регистры 1, 2. Элементом НЕРАВНОЗНАЧНОСТЬ3 анализируются два соседних разряда двоичного числа А(к. При каждомнесовпадении разрядов на выходе элемента 3 появляется сигнал, разрешающий занесение в регистр 6 содержимо 1го регистра 1, не включая старшийразряд, а также занесение следующего за старшим разряда в триггер 5.Последнее занесение имеет место,когда на входе элемента 3 находитсяпервый знаковый и следующий эа нимзначащий разряды числа. Таким образомосуществляется нормализация числаА(к) . Число В к) нормализуется аналогичным образом - /од управлениемэлемента НЕРАВНОЗНАЧНОСТЬ 4 происходит занесение мантиссы без старшейзначащей единицы в регистр 8 и следующего за старшим разряда - в триггер 7. Когда процесс ввода чиселокончен, в регистрах б, 8 содержатся значащие части (мантиссы) чиселА(к), В(к) без старших разрядов, ав триггерах 5, 7 - содержимое стар-.ших регистров 6, 8 соответственно.Одновременно с процессом нормализации чисел А(к), В(к) происходитнормализация их суюы. Последовательный код суммы А(к)+В(к) с выходаодноразрядного сумматора 15 вводитсямпадшими разрядами вперед в регистр16. Затем производится нормализациясуммы описанным способом одновременно с нормализацией чисел А(к),В(к).Элемент НЕРАВНОЗНАЧНОСТЬ 17 управляет занесением мантиссы суван беэстаршей значащей единицы к следующего за старшим разряда мантиссы врегистр 19 и триггер 18 соответст-.венно,1После окончания ввода чисел поддействием сигнала на входе 22 происходит сдвиг регистров б, 8, 19,во время которого осуществляетсякоррекция двоичных кодов, содержа"щихся в этих регистрах. Коррекциякода регистра 6 осуществляется путем поразрядного суммирования, начиная с младших разрядов, на одноразрядном суьиаторе 11 двоичногокода регистра с црявем кодом поправки, если содержимое триггера 5 нуль, и с обратным, если - единица.Прямой или обратный код поправккпередается в сумиЬтбр 11 через муль1080148 В соответствии с изложенным фазаопределяется по следующим соотноше- .15 киям М,.М,)-Н-(М,Ч+М,.Ф-(М,-11, Месли 1 мМ, ,51 М,Мс(,5(М, МД+- 1-(М,+а.4 ЯМ,-(1 8(М,-4) ",еслиМ Ме 4 4,51н 5 М,ф Мг 2,и,нмн 1.1 Я 1 мнмн +(м, фО(.м н 1) Вмеаннн,енм,в,1 Т1,5 МОФ Мс 2,где МО и М - мантиссы соответственно большего и меньшегоиз чисел А(к) и В(к), 30представленных в кодес плавающей запятой; Ид, В(к) 2 ф МВ, где Пд,. МЗ - соответственно поряд,ки и мантиссы чисел, 35 А(к)=2 Оа П.З и Мл, А(к) = 27 26 25 24 23 22 21 20 19 18 17 8(М)м 1 0 О 1 1 0 1 0 1 0 01 0 1 0 1 0в виде с плавающей запятой:011011 100110100В( . 010110 1010101011После нормализации в регистре б находится код 00110100, в регист,ре 8 - 01010101, в регистре 19- 00111111 - мантисса нормализованной 50 суммы без старшей значащей единицы.Содержимое триггеров 5, 7, 18 в данном ннслучае равно нулю. После коррекции двоичный код регистра б равен00110100550000011000111010 16 15 14 13 12 11 10 9 8 7 б 5 4 3 1 0 0 0 0 О 0 0 О О О О О О О О 101000000000000 в. регистре 8 01010101 00001010 01011111 типлексор 9, которым управляет триг. гер 5. Поправка равна двоичному коду регистра б, сдвинутому на 3 разряда в сторону младших разрядов.Одновременно аналогичным образом осуществляется коррекция двоичного кода регистра 8 на сумматоре 12, мультиплексоре 10, триггере 7 и коррекция двоичного кода регистра 19 на сумматоре 21, мультиплексоре 20 и триггере 18. Блок сравнения 13 сравнивает по абсолютной величине числа А(к) и В(к), определяет боль-. шее и управляет мультиплексором 14 -. на его выходе появляется откорректированный двоичный код мантиссы ббольшего числа. На сумматоре 21 про.исходит одновременно коррекция мантиссы суммы и вычитание откорректкованной мантиссы большего числа поазрядно. Полученный на выходе сумматора 21 результат задвигается в регистр 19 по последовательному вхо- ду на место старых разрядов. После й сдвигов процесс коррекции окончен, в регистре 19 находится двоичный код, пропорциональный фазе Цк) в пределах 0 - 45 е. Рассмотрим пример вычисления фазы (используем 8 разрядов мантиссы, не считая старшего значащего; разря-, да).Пусть из процессора быстрого преобразования Фурье поступают числа А(к), В(к) (вверху указаны номера тактов). Под управлением блока сравненкя 13 на выход мультиплексора 14 пропускается код 00111010, так как число А (к больше числа В (к)На сумматоре 21 выполняется одновременно коррекция мантиссы суммы и вычитание откорректированной мантиссы большего числа (вместо вычитания выполня-. ется суммирование с обратным кодом)00111111 ..0000011111000101юнт00001011 Полученный код пропорционален- - т.е, ( = 1,9345 фИстинное значение фазы в данном примере равноЦмСи с = ои с 1 0,0322=1,538(к) еА(в)т.е. погрешность составляет 0,40Как видно кэ фиг.2, погрешность зйачений фазы, вычисленной с помощью предлагаемого устройства, не превышает 1,80 .1080148 7Преимуществом данного устройства, использующего приближенное вычисление фазы и последовательную арифметику, является значительное упрощение структуры и уменьшение обьема устройства. Такой путь оказывается эффективнее, чем решения, использующие табличные ЗУ обратнйх тригонометрических функций. Вычисление фазы ведется в реальном масштабе времени по мере вычисления коэффициентов 1 фурье А(к), Вк) . Передача спектральных составляющих осуществляется последовательным кодом младшими разрядами вперед. В соответствии с этимприменен итеративный метод выделения мантиссы чисел Ак, В(к), что,кроме того, используется при логарифмировании этих чисел, необходимом длявычисления амплитуды сигнала в логарифмическом масштабе. Определение фазы осуществляется только при,помощиопераций сдвига, сложения и вычитания, Повышение точности вычисленияфазы в предложенном устройстве связано только с увеличением разрядов,отводимых под мантиссы чисел, и неизменяет структуру устройства.Заказ 1339/49 Тираж 699 ВНИИПИ Государственного комитет по делам изобретений и открнти 113035, Москва, Ж, Раушская

СмотретьЗаявка

3511008, 12.11.1982

ЛЬВОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

ГОРЯЧЕВА ЕЛЕНА ДМИТРИЕВНА, РОЗЕНБЛАТ МИША ШЛЕМОВИЧ

МПК / Метки

МПК: G06F 17/14, G06F 9/46

Метки: составляющих, спектральных, фазы

Опубликовано: 15.03.1984

Код ссылки

<a href="https://patents.su/6-1080148-ustrojjstvo-dlya-opredeleniya-fazy-spektralnykh-sostavlyayushhikh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения фазы спектральных составляющих</a>

Предыдущий патент: Устройство для обхода сеточной области

Следующий патент: Устройство для формирования адресов процессора быстрого преобразования фурье

Случайный патент: Координаточувствительное фотоэлектрическоеустройство