Устройство для умножения десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

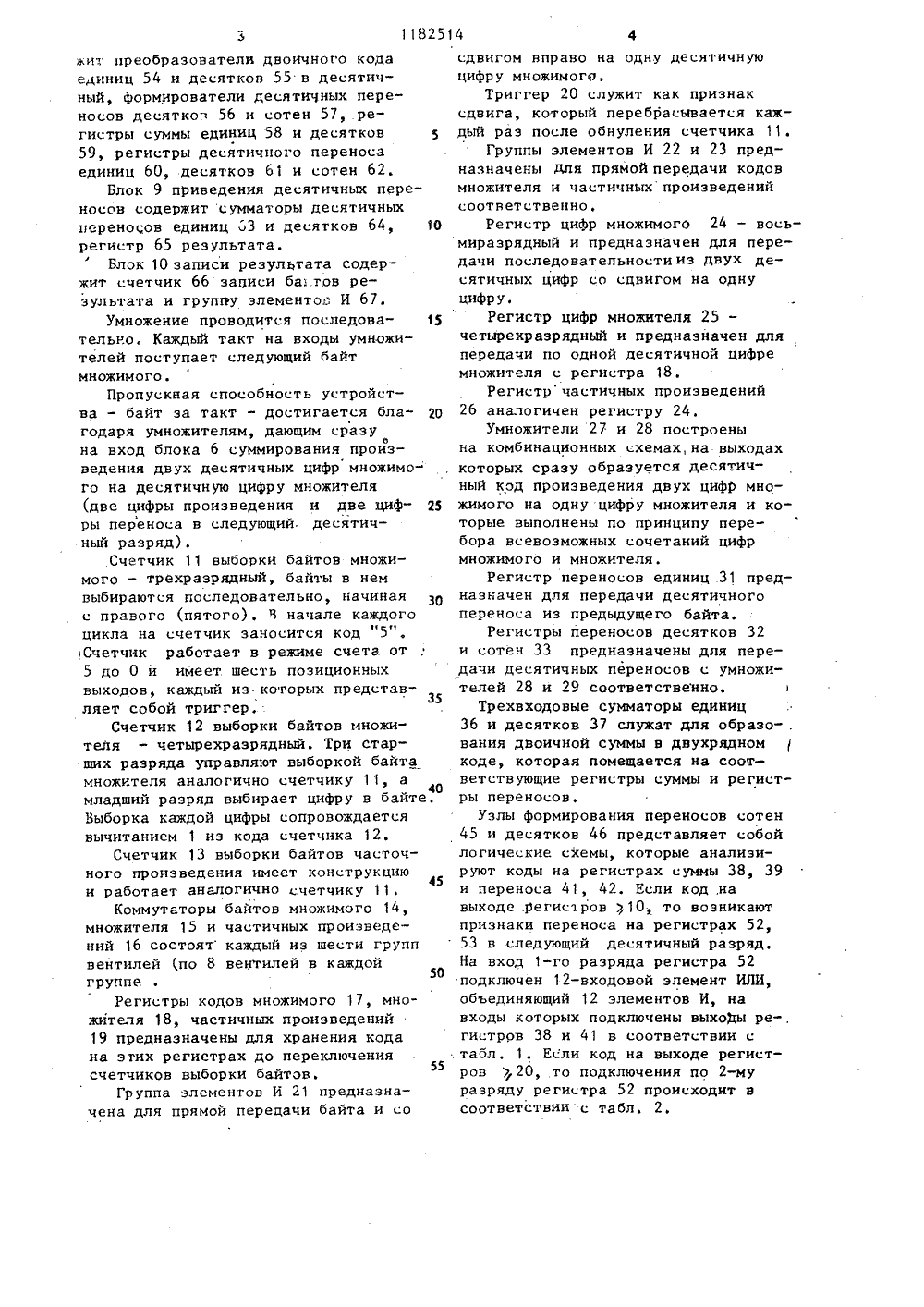

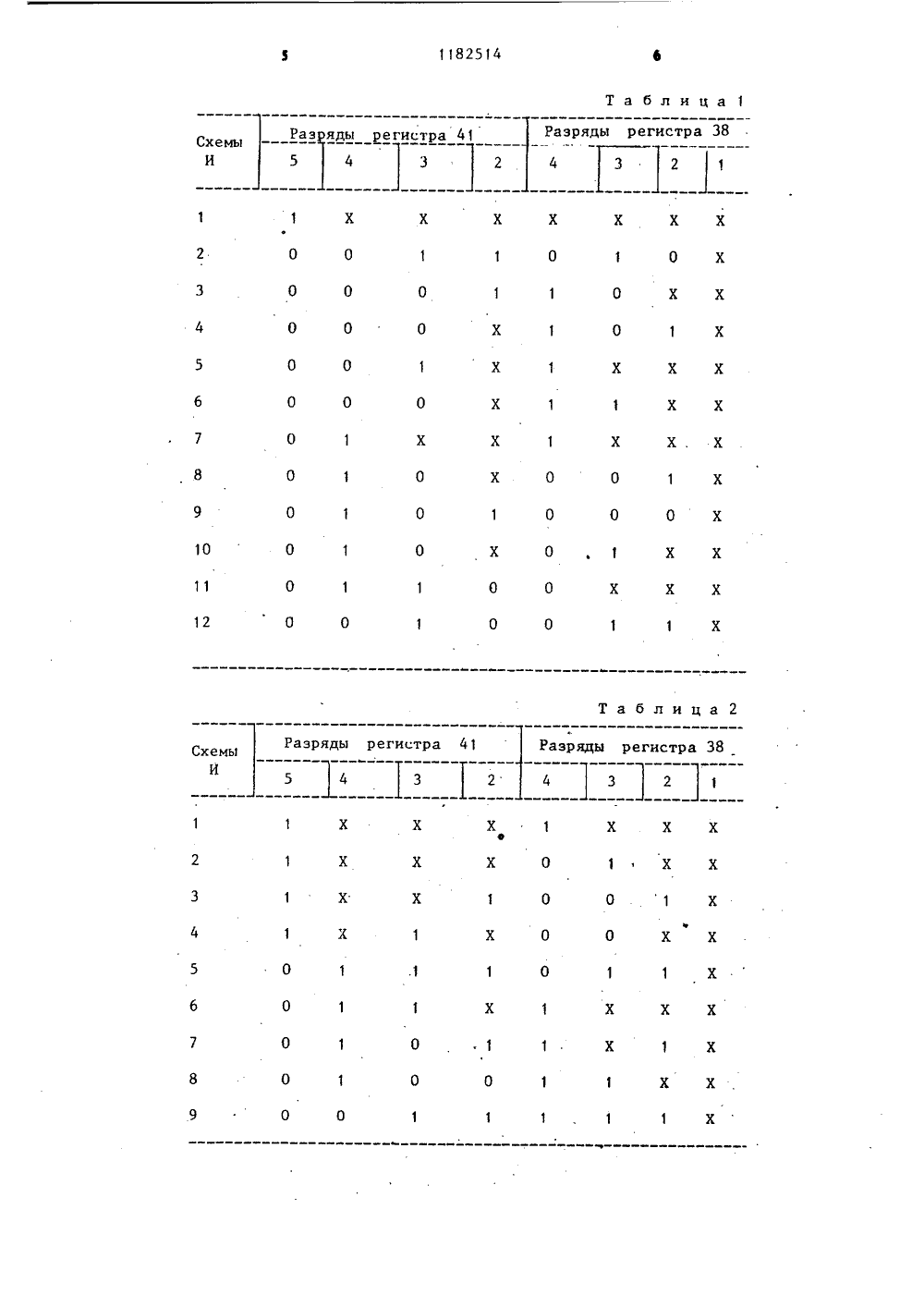

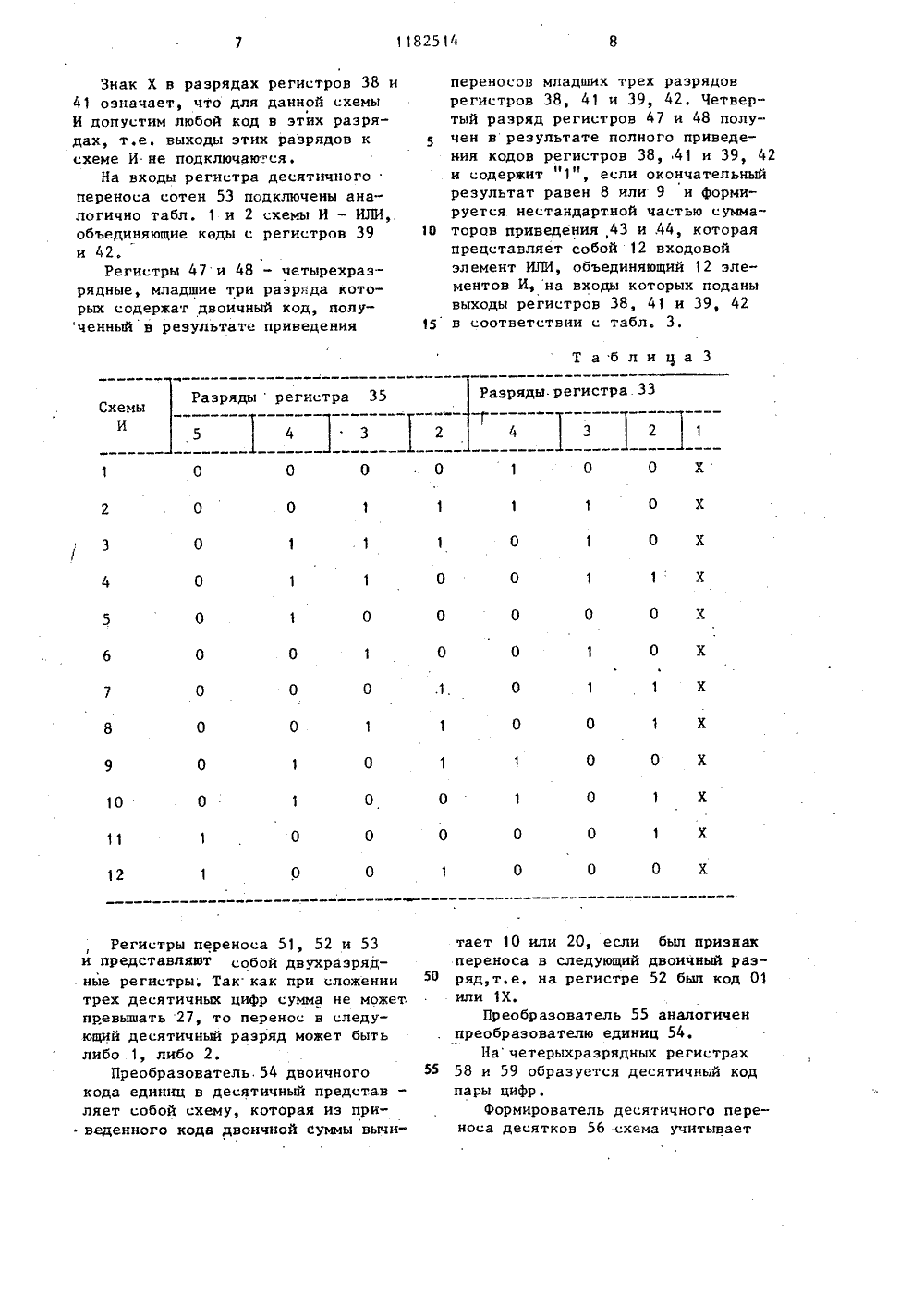

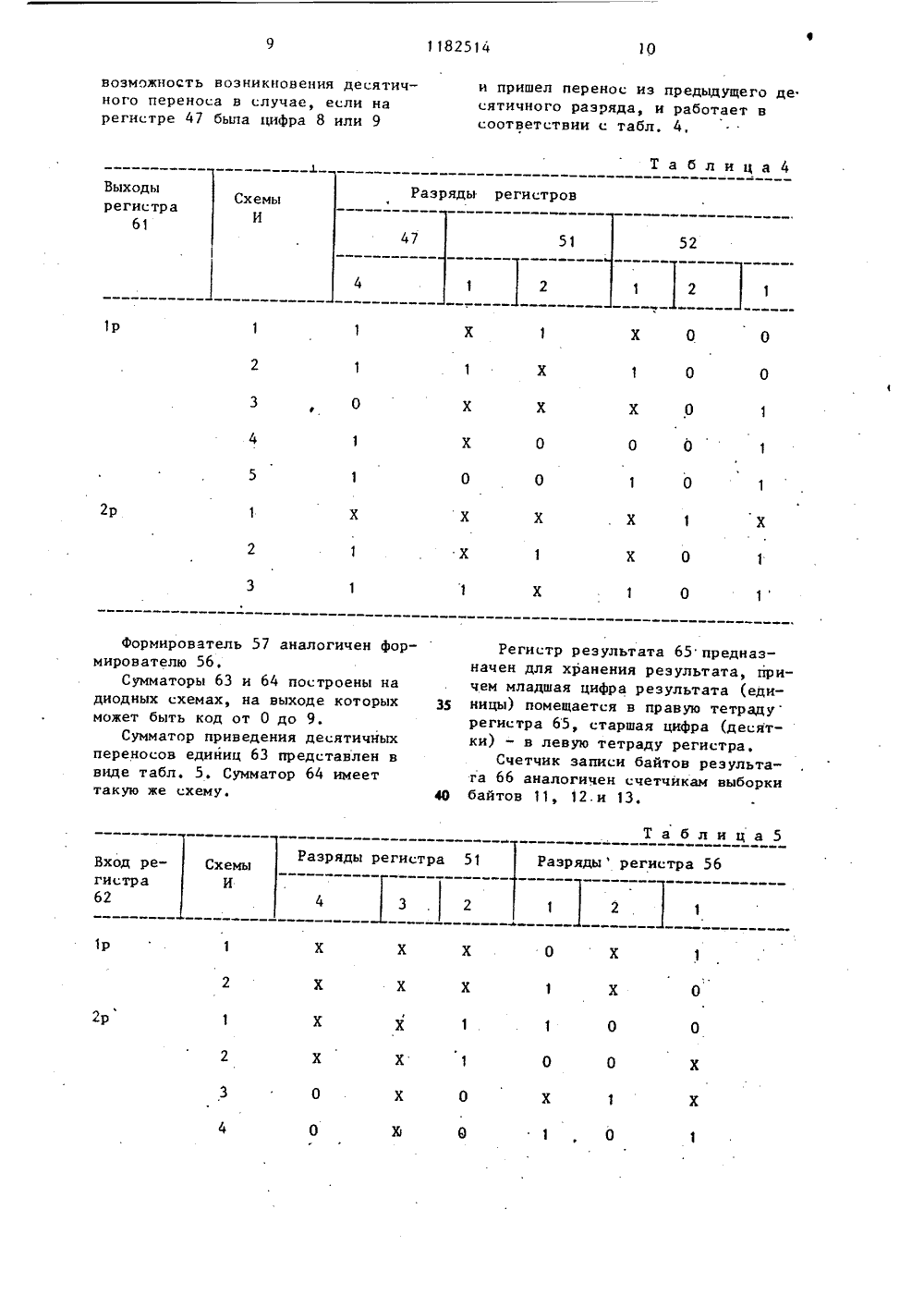

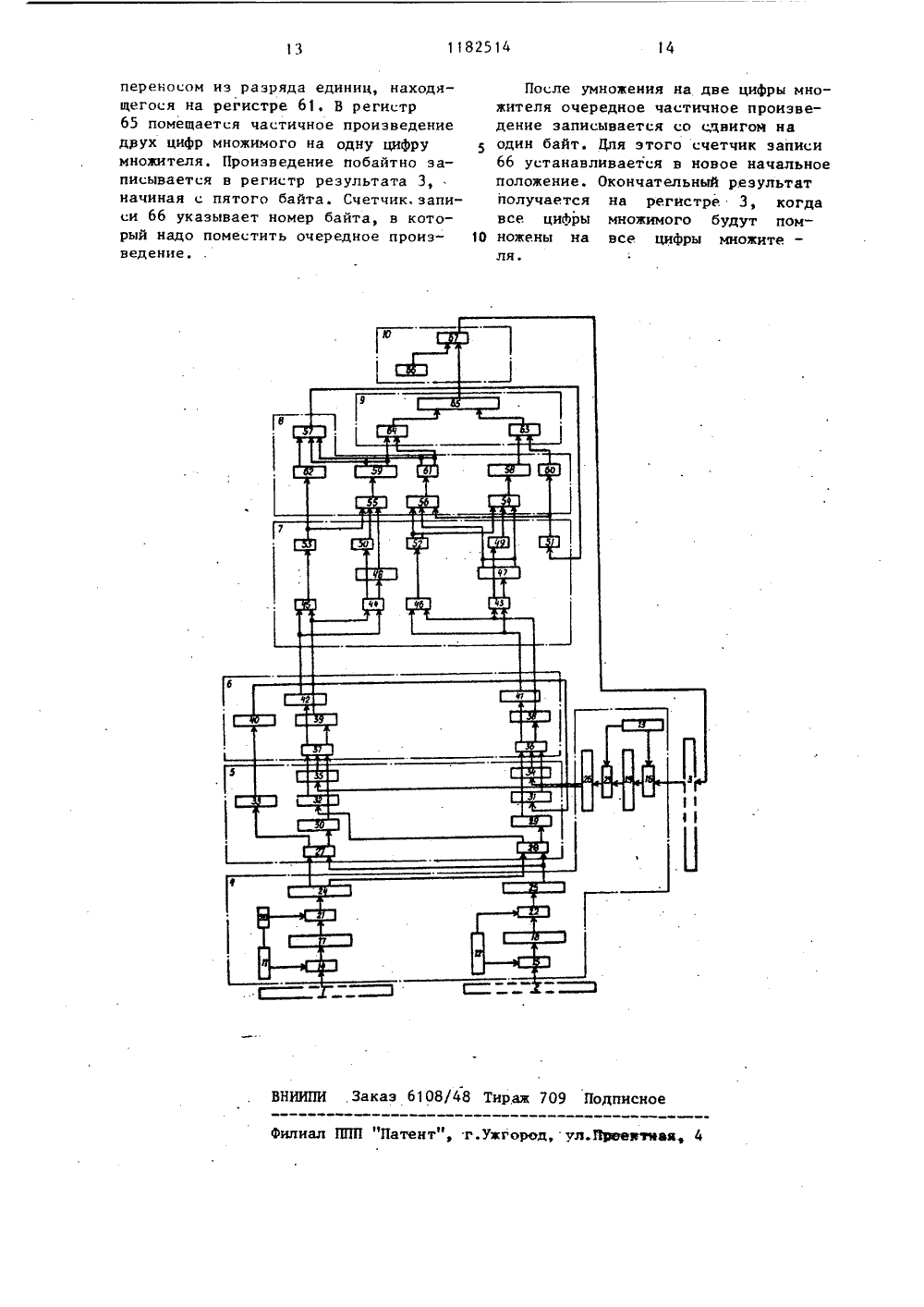

(5 Ц 4 С ИСАНИЕИЗОБРЕТЕНИЯ 1 У СВ ЕТЕЛЬСТВУ ТОР ааай ГОСУДМфствЕННЫЙ НОМИТЕт СССРПО АЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГП 4 Й(54) (57) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее регистры,множимого, множителя и результатамножительный блок, блок суммирования, блок преобразования двоичногокода результата в десятичный н блокприведения десятичных переносов,о т л и ч а ю щ е,е с я тем, что,с целью повышения быстродействия,в него введены блок формированияпереносов, блок записи результатови блок выборки байтов, причем блоквыборки байтов содержит счетчикивыборки байтов множимого, множителя и частичного произведения, коммутаторы байтов множимого,.множителя и частичных произведений, регистры кодов множимого., множителя и частичных произведений, триггер, тригруппы элементов И и регистры цифрмножимого, множителя и частичныхпроизведений, множительиый блок со.держит умножители десяткор и единиц,рвгистры единиц и десятков, регистры,переносов единиц, десятков и сотени регистры единиц и десятков частич,ного произведения, блок суммированиясодержит трехвходовые сумматорыединиц и десятков, регистры суммыединиц, десятков и сотен и регистры 8018251 переносов единиц и десятков, блок формирования переносов содержит двухвходовые сумматоры приведения. пере,носов единиц и десятков, узлы формирования перЕносов сотен и десятков, регистры суммы единиц и десятков, регистры переносов единиц и десятков,4 регистры десятичного переноса единиц, десятков и сотен, блок преобразования двоичного кода результата в десятичный содержит преобразователи двоичного кода единиц и десятков в десятичный, формирователи десятичных переносов десятков и сотен, регистры суммы единиц и десятков, регистры десятич-ного переноса единиц, десятков и сотен, блок приведения десятичных переносов содержит сумматоры приведения десятичных переносов единиц и десятков и регистр результата, а блок записи результата содержит счетчик записи байтов результата и группуэлементов И, выходы которых соединены с входом регистра результата, выходы регистров множимого, множителя и реэультата соединены соответственно с информационными входами коммутаторов множимого, множителя и частичных г.роизведений блока 1 . ЭФЬ выборки байтов, управляющие входы которых соединены соответственно с информационными. выходами счетчиков выборки байтов множимого,множителя; и частичных произведений блока выбор- юВ 1 ки байтов, выходы сброса которых, кроме выхода сброса счетчика выборки байтов множимого, соединены соответственно с первыми входами элементов И, первой и второй групп блока выборки байтов, выход сброса счетчика выборки байтов множимого блока. выбор 1182514кч байтов соединен с входом установки триггера блока .выборки байтов, выход которого соединен с первымивходамц. злементов И. третьей группы блока выборки байтов, вторые входы элементов И первой, второй и третьей групп блока выборки байтов соединены соответственно с выходами регистров кодов множителя частичных произведе)ний и множимого блока выборки байтов, а выходы - с входами регистров цифр множителя, частичных произведений и множимого блока выборки байтов, выходы старшей и младшей цифр регистра цифр множимого блока выборки байтов соединены соответственно с первыми входами умножителей единиц и десятков множительного блока, вторые входы которых соединены с выходом регистра цифр множителя блока выборки байтов, выходы старшей и младпй.й цифр регистра цифр частичного произведения которого соединены соответственно с входами регистров десятков и единиц частичного произведения множительного блока, первый выход умножителя десятков которого соединен с входом регистра переносов сотен множительного блока, выход которого соединен с входом регистра суммы сотен блока суммирования, выход которого соединен с входом регистра переносов единиц множительного блока, второй выход умножителя десятков которого соединен с входом регистра десятков множительного блока, вход регистра переносов десятков которого соединен с первым выходом умножителя единиц множительного блока, второй выход которого соединен с входом регистра единиц множительного блока, выходы регистров единиц, переносов единиц и единиц частичного произведения которого соединены соответственно с входами трехвходового сумматора единиц блока суммирования, входы трехвходового сумматора десятков которого соединены соответственно с выходами регистров десятков; переносов десятков и десятков частичного произведения множительного блока,- выходысуммы трехвходовых сумматоров единиц и десятков блока суммирования соединены соответственно с входами регистровсуммы единиц и десятков блока суммирования, входы регистров переносов единиц и десятков которого соединены соответственно с выходами переноса трехвходовыхсумматоров единиц и десятков блокасуммирования, выходы регистров суммы десятков и единиц которого соединены соответственно с-первыми входами узла формирования переносов сотени двухвходового сумматора приведенияпереносов десятков и узла формирования переносов десятков и двухвходового сумматора приведения переносовединиц блока Формирования переносов,вторые входы которых соединены соответственно с выходами регистровпереносов десятков и единиц блокасуммирования, выходы узлов формировафния переносов сотен и десятков блокаформирования переносов соединенысоответственно с входами регистровдесятичного переноса сотен и десятковблока Формирования переносов,выход регистра переноса сотен которого соединен с первым входом преоб-разователя двоичного кода десятковв десятичный и входом регистра десятичного переноса сотен блока преобразования двоичного кода результатав десятичный, второй и третий входыпреобразователя двоичного кодадесятков в десятичный которогб соединены соответственно с выходамирегистров переносов и суммы десятковблока формирования переносов, входыкоторых соединены соответственнос выходами переноса и суммы двухвходового сумматора приведения переносовдесятков блока формирования переносов,выход узла формирования переносовдесятков которого соединен с входомрегистра десятичного переноса блокаФормирования переносов, выход коТорого соединен с первыми входами преобразователя двоичного кода единицв десятичный и Формирователя десятичного переноса десятков блока преобразования двоичного кода результатав десятичный, вторые входы которыхсоединены с выходом регистра суммыединиц блока формирования переносов , вход которого соединен свыходом .суммы двухвходового сумматора приведения переносов единицблока формирования переносов, выходпереноса которого соединен с входомрегистра переносов единиц блокаформирования переносов, выход кото"рого соединен с третьим входом преобразователя двоичного кода единицв десятичный блока преобразования1182514 25 двоичного кода результата в десятичный, третий вход формирователя десятичного переноса десятков и вход регистра десятичного переноса единиц которого соединены с выходом регистра десятичного переноса единиц блока формирования переносов, вход которого соединен с выходом формирователя десятичного переноса сотен блока преобразования двоичного кода результата в десятичный, первый вход которого соединен с выходом регистра десятичного переноса сотен блока преобразования двоичного кода резуль;тата в десятичный, а второй и третий входы - с входами сумматора приведения десятичных переносов десятков блока приведения десятичных переносов и выходами регистров суммы и десятичйого переноса десятков блока преобразования двоичного кода результата. в десятичный соответственно, . входы которых соединены соответстенно с выходами преобразователей двоич 1Изобретение относится к вычислительной технике.Целью изобретения является повышение быстродействия. На чертеже представлена блок-схема устройства для умножения десятичных чисел.Устройство содержит регистры множимого 1, множителя 2, результата 3, блок 4 выборки байтов, множительный блок 5, блок 6 суммирования, блок 7 формирования переносов, блок 8 преобразования двоичного кода результата в десятичный, блок 9 приведения десятичных переносов, блок 10 записи результата.Блок 4 выборкибайтов содержит счетчики выборки байтов множимого 11, множителя 12 и частичного йроизведения 13, коммутаторы байтов множимого 14, множителя 15 и частичного произведения 16, регистры кодов множимого 1.7, множителя 18 и частичных произведений 19, триггер 20, трн группы элементов И 21 23, регистры цифр множимого 24,5 1 О 15 20 ного кода десятков и переносовв десятичный блока преобразованиядвоичного кода результата в.десятичный,выход преобразователя двоичного кода единиц в десятичный которогосоединен с входом регистра суммыединиц блока преобразования двоичного кода результата в десятичный,выходы регистров суммы и десятичногопереноса единиц которого соединеныс входами сумматора приведения десятичного переноса единиц блокаприведения десятичных переносов, выходы сумматоров приведения десятичных переносов единиц и десятковкоторого соединены соответственнос входами младшей и старшей тетрадрегистра результата блока приведения десятичных переносоз, выходкоторого соединен с первыми входамиэлементов И группы блока записирезультата, вторые входыкоторых соединены с выходом счетчика записи байтов результата блока записи результата. 2множителя 25 и частичных произведений 26.Множительный блок 5 содержит умножители десятков 27 и единиц 28, регистры единиц 29 и десятков 30, регистры переносов единиц 31, десятков 32 и сотен 33, регистры единиц 34 и десятков 35 частичного произведения.Блок 6 суммирования содержит 0трехвходовые сумматоры единиц 36 и десятков 37, регистры суммы единиц 38, десятков 39 и сотен 40, регистры переносов единиц 41 и десятков 42.Блок 7 формирования переносов содержит двухвходовые сумматоры приведения переносов единиц 43 и десятков 44, узлы формирования пере-, носов сотен 45 и десятков 46, регистры суммы единиц 47 и десятков 48, регистры переносов единиц 49 и десятков 50, регистры десятичного переноса единиц 51, десятков 52 и сотен53.Блок 8 преобразования двоичногокода результатав десятичный содер 1182514жит преобразователи двоичного кодаединиц 54 и десятков 55 в десятичный, формирователи десятиЧных переносов десятков 56 и сотен 57, регистры суммы единиц 58 и десятков59, регистры десятичного переносаединиц 60, десятков 61 и сотен 62.Блок 9 приведения десятичных переносов содержит сумматоры десятичныхпереносов единиц о 3 и десятков 64,регистр 65 результата.Блок 10 записи результата содержит счетчик 66 записи батов результата и группу элементов И 67.Умножение проводится последовательно. Каждый такт на входы умножителей поступает следующий байтмножимого,Пропускная способность устройства - байт за такт - достигается бла"годаря умножителям, дающим сразуна вход блока 6 суммирования произведения двух десятичных цифр множимого на десятичную цифру множителя(две цифры произведения и две цифры переноса в следующий. десятичный разряд),Счетчик 11 выборки байтов множимого - трехразрядный, байты в немвыбираются последовательно, начинаяс правого (пятого). Ч начале каждогоцикла на счетчик заносится код "5".Счетчик работает в режиме счета от5 до 0 и имеет шесть позиционныхвыходов, каждый из которых представляет собой триггер,Счетчик 12 выборки байтов множителя - четырехразрядный. Три старших разряда управляют выборкой байтамножителя аналогично счетчику 11, амладший разряд выбирает цифру в байтеВыборка каждой цифры сопровождаетсявычитанием 1 иэ кода счетчика 12.Счетчик 13 выборки байтов часточного произведения имеет конструкциюи работает аналогично счетчику 11.Коммутаторы байтов множимого 14,множителя 15 и частичных произведений 16 состоят каждый иэ шести группвентилей (по 8 вентилей в каждойгруппеРегистры кодов множимого 17, множителя 18, частичных произведений19 предназначены для хранения кодана этих регистрах до переключениясчетчиков выборки байтов.Группа элементов И 21 предназначена для прямой передачи байта и со сдвигом вправо на одну десятичнуюцифру множимого,Триггер 20 служит как признаксдвига, который перебрасывается каждый раэ после обнуления счетчика 11.Группы элементов И 22 и 23 предназначены для прямой передачи кодовмножителя и частичных произведенийсоответственно,10 Регистр цифр множимого 24 - восьмиразрядный и предназначен для передачи последовательности из двух десятичных цифр со сдвигом на однуцифру,Регистр цифр множителя 25 -четырехразрядный и предназначен дляпередачи по одной десятичной цифремножителя с регистра 18.Регистр частичных произведений20 26 аналогичен регистру 24.Умножители 27 и 28 построенына комбинационных схемах,на выходах. которых сразу образуется десятичный код произведения двух цифр мно 25 жимого на одну цифру множителя и которые выполнены по принципу перебора всевозможных сочетаний цифрмножимого и множителя.Регистр переносов единиц .31 предназначен для передачи десятичногопереноса из предыдущего байта.Регистры переносов десятков 32и сотен 33 предназначены для передачи десятичных переносов с умножи 35телей 28 и 29 соответственно.Трехвходовые сумматоры единиц36 и десятков 37 служат для образо- .вания двоичной суммы в двухрядном (коде, которая помещается на соот 40ветствующие регистры суммы и регистры переносов,Узлы формирования переносов сотен45 и десятков 46 представляет собойлогические схемы, которые аналиэи 45руют коды на регистрах суммы 38, 39и переноса 41, 42. Если код,навыходе .регис 1 ров ) 10, то возникаютпризнаки переноса на регистрах 52,53 в следующий десятичный разряд.50На вход 1-го разряда регистра 52подключен 12-входовой элемент ИЛИ,объединяющий 12 элементов И, навходы которых подключены выходы ре-,гистров 38 и 41 в соответствии с.табл, 1. Если код на выходе регист 55ров ) 20, то подключения по 2-муразряду регистра 52 происходит всоответствии с табл, 2,118254 Раз Схемы И Х Х О О Х 4 О О Х О Х Х Х 8 9 О О Х О Х О 1 О Х О аблиц зряд егистра хемь ИТа блица Разряды регистра 38 Х 1 Х О1182514 Таблича 3 Разряды. регистра. 33 Разрядырегистра 35 Схемы 5 43 2 4 3 2 1 1 О 0 Х 0 0 0 0 1 1 0 Х 0 00 Х 0 0 3 0 0 0 0 0 0 0 0 0 0 0 0 0 8 0 0 0 0 0 0 0 О 10 0 0 0 0 0 0 12 Знак Х в разрядах регистров 38 и 41 означает, что для данной схемы И допустим любой код в этих разрядах, т.е, выходы этих разрядов к схеме И не подключаются.На входы регистра десятичного переноса сотен 53 подключены аналогично табл. 1 и 2 схемы И - ИЛИ,. объединяющие коды с регистров 39 и 42.Регистры 47 и 48 - четырехразрядные, младшие три разряда которых содержат двоичный код, полученный в результате приведения Регистры переноса 51, 52 и 53и представляют собой двухраэряд. ные регистры. Так как при сложении трех десятичных цифр сумма не может, превышать 27, то перенос в следующий десятичный разряд может быть либо 1, либо 2.Преобразователь.54 двоичного кода единиц в десятичный представ - ляет собой схему, которая из при веденного кода двоичной суммы вычипереносов младших трех разрядоврегистров 38, 41 и 39, 42Четвертый разряд регистров 47 и 48 получен в результате полного приведения кодов регистров 38, 41 и 39, 42и содержит "1", если окончательныйрезультат равен 8 или 9 и формируется нестандартной частью сумма О торов приведения 43 и,44, котораяпредставляет собой 12 входовойэлемент ИЛИ, объединяющий 12 элементов И,на входы которых поданывыходы регистров 38, 41 и 39, 42 15 в соответствии с табл. 3,1 Х 0 Х 0 Х Ъ 1 Х 1 Х 0 Х 1 Х 1 . Х 0 Х тает 10 или 20, если был признакпереноса в следующий двоичный раз" 0 ряд,т,е, на регистре 52 бып код 01или 1 Х.Преобразователь 55 аналогиченпреобразователю единиц 54.Начетерыхразрядных регистрах 55 58 н 59 образуется десятичный кодпары цифр.формирователь десятичного переноса десятков 56 схема учитывает1182514 и пришел перенос из предыдущего десятичного разряда, и работает всоответствии с табл. 4. Т а б л и ц а 4 Выходырегистра61 Разряды регистров Схемы И47 51 52 Х О О 1 О О Х 3, О Х О Х О О 2 р Х Х Х Регистр результата 65 предназначен для хранения результата, причем младшая цифра результата (еди ницы) помещается в правую тетрадурегистра 65, старшая цифра (десятки) - в левую тетраду регистра.Счетчик записи байтов результага 66 аналогичен счетчикам выборки 40 байтов 11, 12.и 13. Т а б л и ц а 5 Разряды регистра 51 Вход регистра 62 Схемы О 1 р Х Х Х О 2 р Х Х О О Х О возможность возникновения десятичного переноса в случае, если нарегистре 47 была цифра 8 или 9 Формирователь 57 аналогичен формирователю 56.Сумматоры 63 и 64 построены на диодных схемах, на выходе которых может быть код от О до 9.Сумматор приведения десятичных переносов единиц 63 представлен в виде табл. 5. Сумматор 64 имеет такую же схему. Х О О О 1 О Х 1 Х О 1 О Разряды регистра 56 1 О О О Х 1 1, ОВход регистра62 0 Зр 0 0 Х Х 0 0 Х Х 1 4 р 1 Х 0 О. О 3 0 К . 0 Х Устройство работает следующим образом,Начиная с младшего (пятого) байтамножимое и множитель с регистров1 и 2 выбирают на соответствующиерегистры 17 и 18 и затем байт множимого помещается на восьмираэрядныйрегистр 24. Каждый такт выбираетсяодин байт множимого,35Цифра (тетрада) множителя помещается на регистр 17 и хранится там,пока все байты множимого не будут.помножены на эту цифру. Затем выбирается следующая цифра из этого байта 4 Ои процедура повторяется. После умножения на две цифры множителя счетчиквыборки 12 переключается на новыйбайт.Старшая цифра (тетрада) множимого 4524 поступает на вход умножителя десятков 27, а младшая - на вход умножителя единиц 28. Цифра (тетрада)множителя поступает на входы обоихумножителей. Полученное на выходеумножителей 27 и 28 произведениесуммируется с помощью трехвходовыхсумматоров 36 и 37 с соответствующим десятичным разрядом частичного произведения и с переносомиз предыдущего десятичного разряда.Полусумма и перенос с выходаблока суммирования поступают навход блока формирования десятичных переносов, где с помощью сумматоров 43 и 44 производится частичное приведение двоичных переносов.Одновременно производится анализ результата на выходе блока суммирования. Если результат больше или равен 10, возникает признак перено- са в следующий десятичный разряд и на регистрах 52 и 53 записывается код 01 (для 10) или .10 (для двадцати).Полученный на выходе блока.7 результат преобразуется в десятичный код в блоке 8, Если был признак десятичного переноса в десятки, то преобразователь единиц 54 производит вычитание кода 10 или 20 из приведенной суммы единиц, а преобразователь десятков 55 вычитает 10 или 20 иэ суммы десятков, если был признак переноса сотен на регистре 53.Преобразованная в десятичный код сумма складывается с десятичным переносом из предыдущего разряда в блоке 9.Сумматор 63 складывает код регистра суммы единиц 58 с десятичным переносом иэ предыдущего байта, находящегося на регистре 60.Сумматор .64 складывает код регистра суммы десятков 59 с десятичным"Патент", г.ужгород,ул.Преем аа, 4 переносом из разряда единиц, находящегося на регистре 61. В регистр65 помещается частичное произведениедвух цифр множимого на одну цифрумножителя. Произведение побайтно записывается в регистр результата 3,начиная с пятого байта. Счетчик, записи 66 указывает номер байта, в который надо поместить очередное произведение. После умножения на две цифры множителя очередное частичное произведение записывается со сдвигом наодин байт. Цля этого счетчик записи66 устанавливается в новое начальноеположение. Окончательный результатполучается на регистре 3, когдавсе цифры множимого будут пом О ножены на все цифры множите -ля.

СмотретьЗаявка

3730019, 27.04.1984

ПРЕДПРИЯТИЕ ПЯ А-3162

ТЯПКИН МАРК ВАЛЕРИАНОВИЧ, ГОЛОВИНА МАРГАРИТА АЛЕКСЕЕВНА, БАКАНОВА ВАЛЕНТИНА АЛЕКСЕЕВНА, ВОЛКОВА ИННА ВЛАДИМИРОВНА

МПК / Метки

МПК: G06F 7/52

Метки: десятичных, умножения, чисел

Опубликовано: 30.09.1985

Код ссылки

<a href="https://patents.su/9-1182514-ustrojjstvo-dlya-umnozheniya-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения десятичных чисел</a>

Предыдущий патент: Последовательное устройство для деления чисел в дополнительном коде

Следующий патент: Устройство для вычисления тригонометрических функций

Случайный патент: Устройство для раздельного удаления навоза из животноводческого помещения