Микропрограммное управляющее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

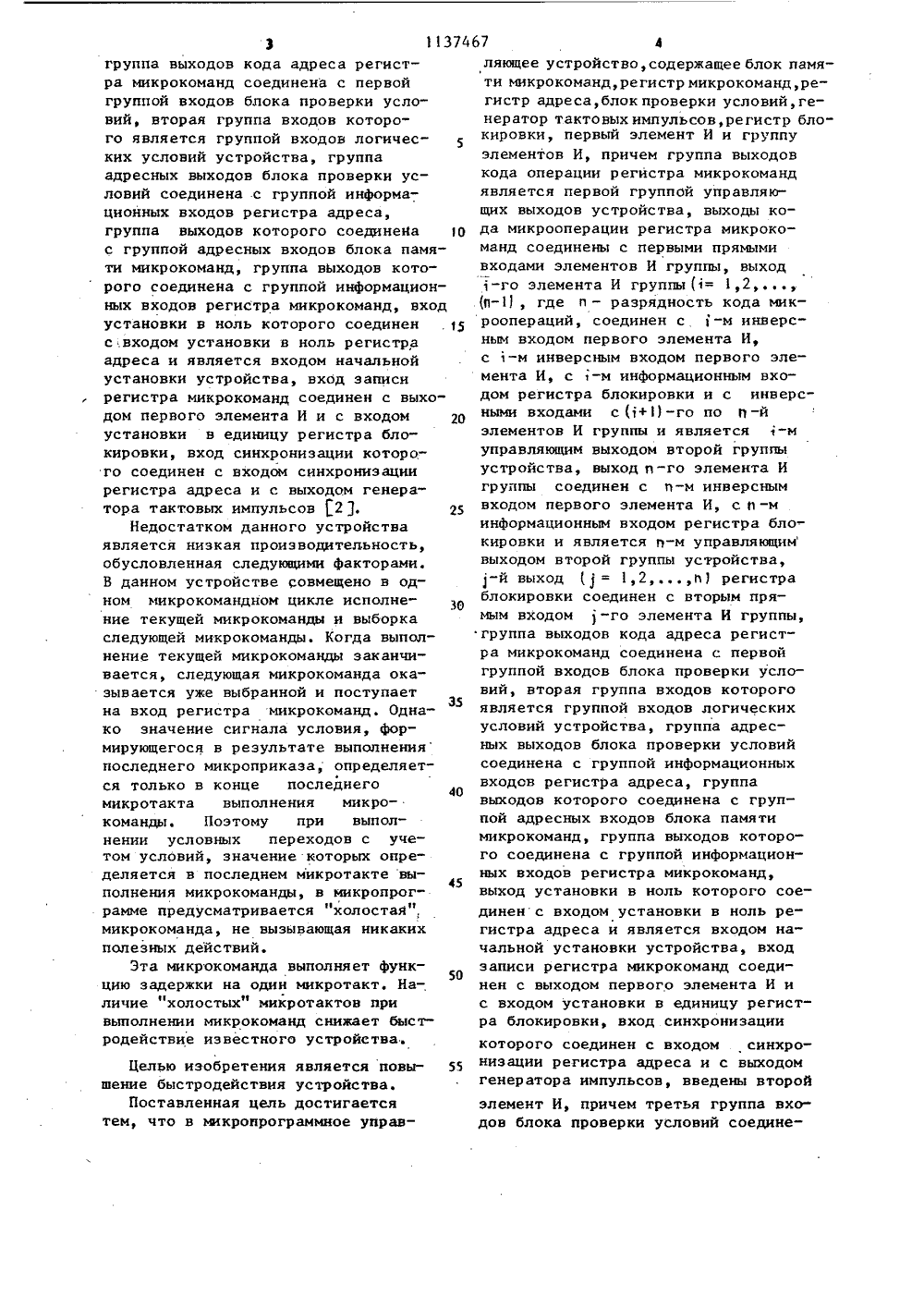

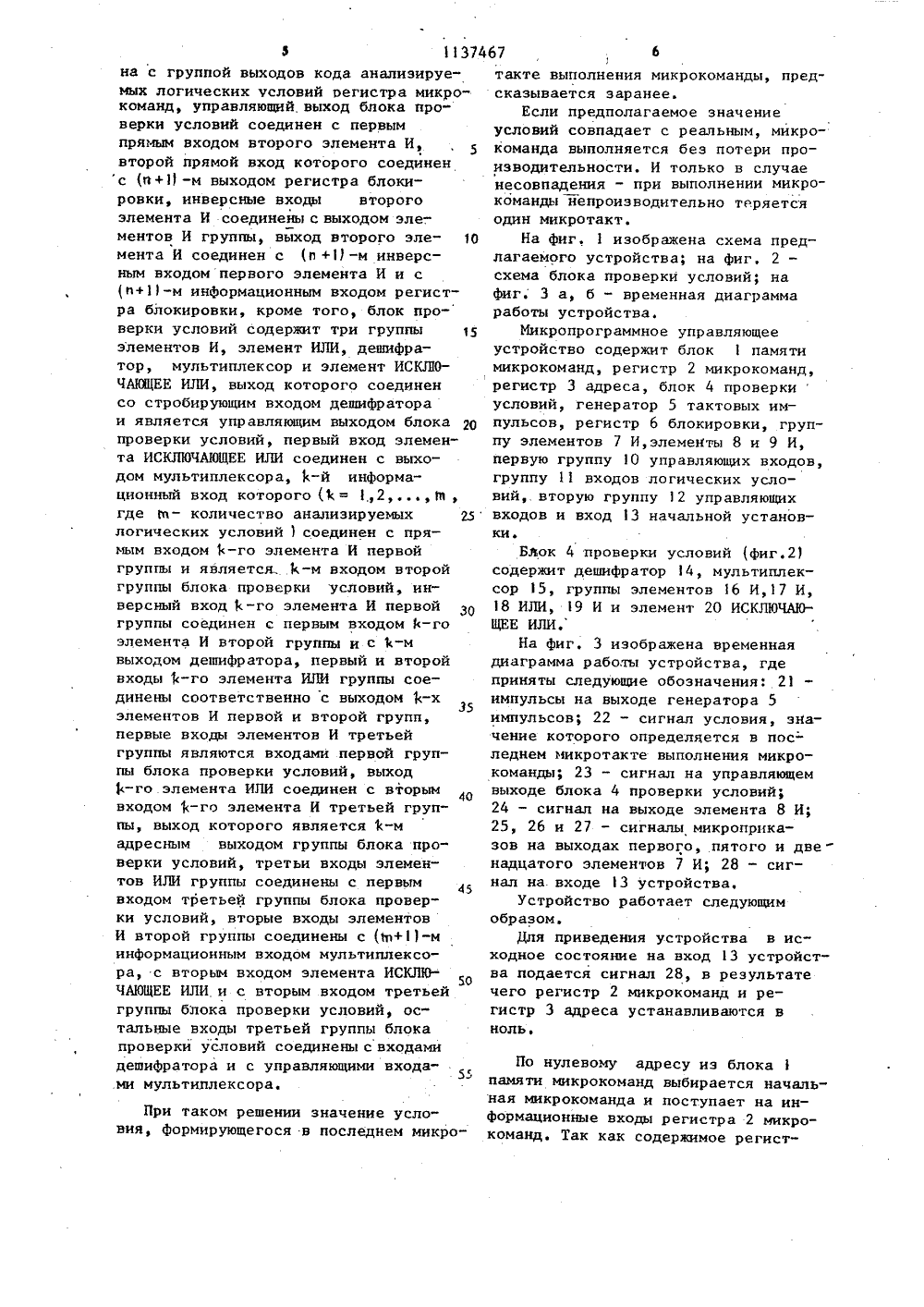

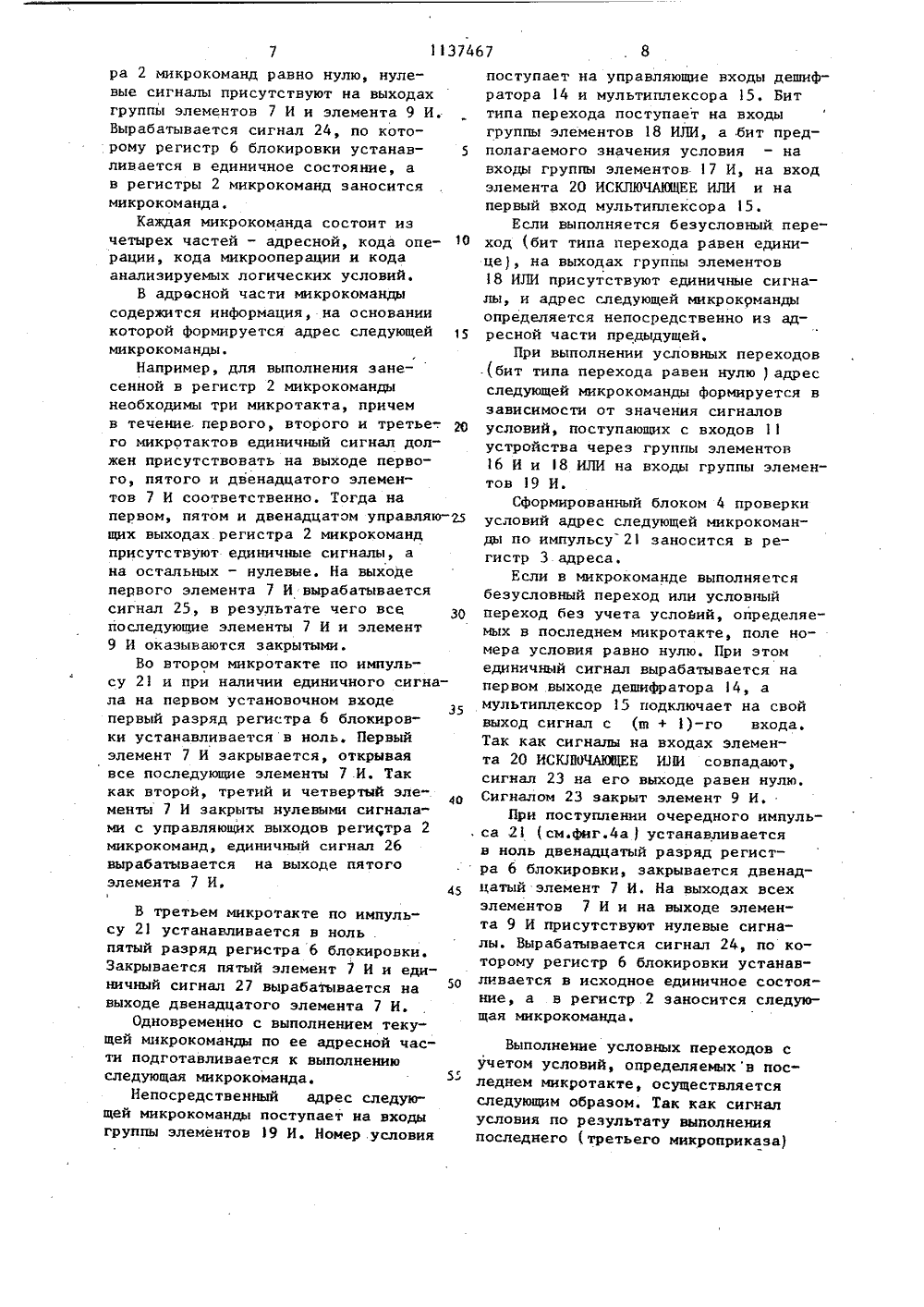

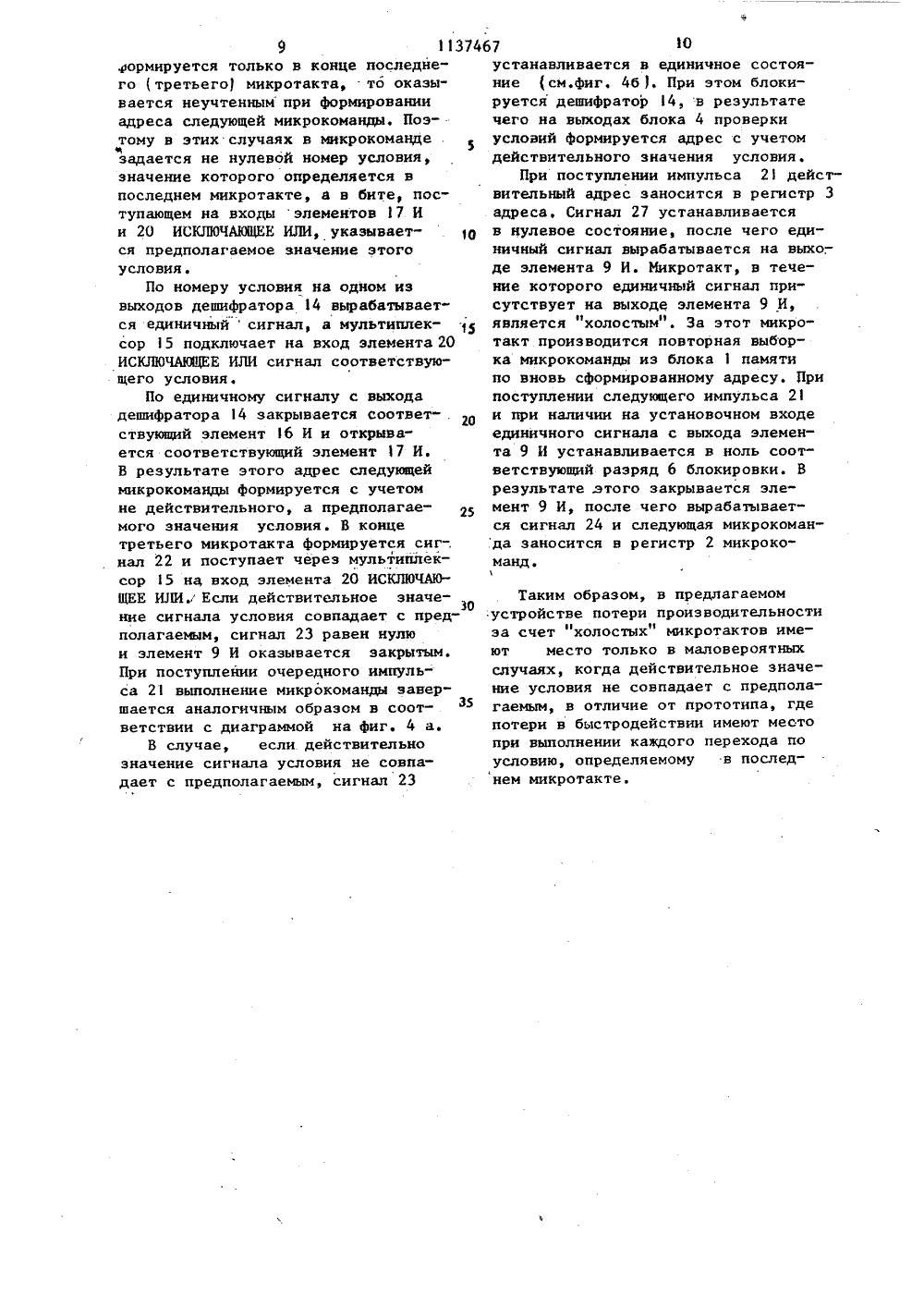

(5 С 06 Р 9/22 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ я аГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) 1. Авторское свидетельство СССРУ 970367, кл, С 06 Р 9/22, 1981.2, Авторское свидетельство СССР11 949657, кл. С 06 Е 9/22, 1980(54)(57) МИКРОПРОГРАММНОЕ УПРАВЛЯКЦЕЕ УСТРОЙСТВО, содержащее блокпамяти микрокоманд,регистр микрокоманд, регистр адреса, блок проверкиусловий, генератор тактовых импульсов, регистр блокировки, первый элемент И и группу элементов И, причем группа выходов кода операции регистра микрокоманд явля.ется первой группой управляющих выходов устройства, выходы кода микрооперации регистра микрокоманд соединены с первыми прямыми входами элементов И группы, выход 1-го элемента И группы . (1 = 1, 2 (вгде и - разрядность кода микроопераций, соединен с 1-м инверсным входом первого элемента И, с 1-м инверсным входом первого элемента И, с 1-м информационным входом регистра блокировки и синверсными входами с(1 +1)-го по и-й элементов И группы и является 1-м управляющим выходом второй группы устройства, выход и -го элемента И группы соединен с п -м инверсным входом первого элемента И, с о - м информационным входом регистра блокировки и является и - м управляющим выходом второй группы устройства, 1 - й выход =1,2,., а ) регистра блокировки соединен с вторым прямым входом -го элемента И группы, группа выходов кода адреса регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, группа адресных выходов блока проверки условий соединена с груп - пой информационных входов регистра адреса, группа выходов которого сое- ф динена с группой адресных входов блока памяти микрокоманд, группа выходов которого соединена с группой информационных входов регистра микро- команд, вход установки в ноль которого соединен с входом установки в ноль регистра адреса и являетс входом начальной установки устройства , вход записи регистра микрокоманд соединен с выходом первого элемента И и с входом установки в единицу регистра блоки ровки, вход синхронизации которого соединен с входом синхронизации ре гистра адреса и с выходом генерато ра импульсов, о т л и ч а ю щ е е с я тем, что, с целью повышенияего быстродействия, в него введенвторой элемент И, причем. третья грпа входов блока проверки условийсоединена с группой выходов кода алиэируемых логических условий регистра микрокоманд, управляющий выход блока проверки условий соединес первым прямым входом второго эле 11 мента И, второй прямой вход которого соединен с(пф 1) -м выходом регистра блокировки, инверсные входы . второго элемента И со:диненыс выходом элементов И гоупйы, выход второго элемента И соединен с (пм) -м инверсным входом г.;юого элемента И и с (ь 4"1) -м информационным входом регистра блокировки, кроме того, блок проверки условя содержит три группы элементов И, злемент ИЛИ, дешифратор, мультиплексор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен со стробирующим входом дешифратора и является управляющим выходом блока проверки условий, первый вход элемента ИСКЛЮЧА 10 ЩЕЕ ИЛИ соединен с выходом мультиплексора, М-й информационный вход которого с = 1,2е, где Ь " количес- во анализируемых логических условий ) соединен с прямым входом 1-го элемента И первой группы и является %-м входом второй группы .блока проверки условий, инверсный вход ,%-го элемента И первой группы сое 37467динен с первым входом %-го элемента И второй группы и с % -м выходом дешифратора, первый и второй ,входы М-го элемента ИЛИ группы соединены соответственно с выходом 3-х элементов И первой и второй групп, первые входы элементов И третьей группы являются вхсцами первой группы блока проверки условий, выход Ь-го элемента ИЛИ соединен с вторым входом %-го элемента И третьей группы, выход которого явля" ется %-м адресным выходом группы блока проверки условий, третьи входы элементов ИЛИ группы соединены с первым входом третьей группы блока проверки условий, вторые входы элементов И второй группы соединены с (п+1) -м информационным входом мультиплексора, с вторым входом элемента ИСКЛ)0 ЧАЮЩЕЕ ИЛИ и с вторым входом третьей, группы блока проверки условий, остальные входы третьей группы блока проверки условий соединены с входами дешифратора и с управляющими входамимультиплексора.1Изобретение относится к автоматике и вычислительной технике, в частности к микропропрограммным устройствам управления, и может бытьиспользовано в цифровых вычислительных системах, а также в терминальной аппаратуре.Известно микропрограммное управляющее устройство, содержащее блокпамяти микрокоманд, регистр микрокоманд, регистр адреса, блок проверки условий, генератор импульсов,регистр блокировки, элемент И игруппу элементов И 1,Недостатком данного устройства15является низкое быстродействие, обусловленное наличием "холостых микротактов".Наиболее близким по техническойсущности к предлагаемому является мик 20ропрбграммное управляющее устройство,содержащее блок памяти микрокоманд,регистр микрокоманд, регистр адреса,блок проверки условий, генератор тактовых импульсов, регистр блокировки,2первый элемент И и группу элементов И, группа выходов кода операции регистра микрокоманд является группой управляющих выходов устройства, выходы кода микроопераций регистра микрокоманд соединены с первыми прямыми входами элементов И группы, выход 1-го элемента И группы (1=1,2, , (П, где п - разрядность кода микроопераций, соединен с )-м инверсным входом первого элемента И, с 1-м информационным входом регистра блокировки и с инверсными входами с (1 +1)-го по е-й элементов И группы и является -м управляющим выходом второй группы устройства, выход и-го элемента И группы соединен с и -м инверсным входом первого элемента И, с и-м информационным входом регистра блокировки и является и -м управляющим выходом второй группы устройства, )-й выход= 1,2р) регистра блокировки соединен со вторым прямым входом )-го элемента И группы,ЗО Целью изобретения является повышение быстродействия устройства. Поставленная цель достигаетсятем, что в ьякронрограммное управгруппа выходов кода адреса регистра микрокоманд соединена с первойгруппой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, группаадресных выходов блока проверки условий соединена с группой информационных входов регистра адреса,группа выходов которого соединеиа 1 Ос группой адресных входов блока памяти микрокоманд, группа выходов которого соединена с группой информационных входов регистра микрокоманд, входустановки в ноль которого соединен . 15с,входом установки в ноль регистраадреса и является входом начальнойустановки устройства, вход записирегистра микрокоманд соединен с выходом первого элемента И и с входом 2 Оустановки в единицу регистра блокировки, вход синхронизации которо. -го соединен с входом синхронизациирегистра адреса и с выходом генератора тактовых импульсов 2), 25Недостатком данного устройстваявляется низкая производительность,обусловленная следующими факторами.В данном устройстве совмещено в одном микрокомандном цикле исполнение текущей микрокоманды и выборкаследующей микрокоманды. Когда выполнение текущей микрокоманды заканчивается, следующая микрокоманда оказывается уже выбранной и поступает35на вход регистра микрокоманд. Однако значение сигнала условия, формирующегося в результате выполненияпоследнего микроприказа, определяется только в конце последнегомикротакта выполнения микрокоманды. Поэтому при выполнении условных переходов с учетом условий, значение которых определяется в последнем микротакте выполнения микрокоманды, в микропрограмме предусматривается "холостая",микрокоманда, не вызывающая никакихполезных действий,Эта микрокоманда выполняет функцию задержки на один микротакт. Наличие "холостых" микротактов привыполнении микрокоманд снижает быстродействие известного устройства. ляющее устройство, содержащее блок памяти микрокоманд,регистр микрокоманд,регистр адреса, блок проверки условий, генератор тактовых импульсов, регистр блокировки, первый элемент И и группуэлементов И, причем группа выходовкода операции регистра микроксмандявляется первой группой управляющих выходов устройства, выходы кода микрооперации регистра микрокоманд соединены с первыми прямымивходами элементов И группы, выход1-го элемента И группы (1= 1,2(п), где п - разрядность кода микроопераций, соединен с 1 -м инверсным входом первого элемента И,с 1-м инверсным входом первого элемента И, с 1-м информационным входом регистра блокировки и с инверсными входами с (1+1) -го по О -йэлементов И группы и является -муправляющим выходом второй группыустройства, выход и -го элемента Игруппы соединен с и-м инверснымвходом первого элемента И, с и -минформационным входом регистра блокировки и является И-м управляющимвыходом второй группы устройства,1-й выход= 1,2 и) регистраблокировки соединен с вторым прямым входом 1 -го элемента И группы,группа выходов кода адреса регистра микрокоманд соединена с первойгруппой входов блока проверки условий, вторая группа входов которогоявляется группой входов логическихусловий устройства, группа адресных выходов блока проверки условийсоединена с группой информационныхвходов регистра адреса, группавыходов которого соединена с группой адресных входов блока памятимикрокоманд, группа выходов которого соединена с группой информационных входов регистра микрокоманд,выход установки в ноль которого соединенс входом установки в ноль регистра адреса и является входом начальной установки устройства, вход записи регистра микрокоманд соединен с выходом первого элемента И и с входом установки в единицу регистра блокировки, вход синхронизациикоторого соединен с входом синхронизации регистра адреса и с выходом генератора импульсов, введены второйэлемент И, причем третья группа входов блока проверки условий соедине 1374на с группой выходов кода анализируемых логических условий регистра микро- команд, управляющий выход блока нро" верки условий соединен с первым прямым входом второго элемента И, второй прямой вход которого соединен с (и+1 -м выходом регистра блокировки, инверсные входы второго элемента И соединены с выходом эле-. ментов И группы, выход второго эле" О мента И соединен с (п +1) -и инверсным входом первого элемента И и с (и+1)-м информационным входом регистра блокировки, кроме того, блок проверки условий содержит три группы 15 элементов И, элемент ИЛИ, дешифратор, мультиплексор и элемент ИСКЛОЧАЮЩЕЕ ИЛИ, выход которого соединен со стробирующим входом дешифратора и является управляющим выходом блока 20 проверки условий, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом мультиплексора, с-й информационный вход которого (% = 1.,2 М, где ьз- количество анализируемых 25 логических условийсоединен с прямым входом Ь-го элемента И первой группы и является 1-м входом второй группы блока проверки условий, инверсный вход к-го элемента И первой группы соединен с первым входом Ь-го элемента И второй группы и с %-м выходом дешифратора, первый и второй входы -го элемента ИЛИ группы соединены соответственно с выходом к-х35 элементов И первой и второй групп, первые входы элементов И третьей группы являются входами первой группы блока проверки условий, выход -го элемента ИЛИ соединен с вторым входом -го элемента И третьей группы, выход которого является %-м адресным выходом группы блока про" верки условий, третьи входы элементов ИЛИ группы соединены с первым входом третьей группы блока проверки условий, вторые входы элементов И второй группы соединены с (1 п+11-м информационным входом мультиплексора, с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с вторым входом третьей группы блока проверки условий, остальные входы третьей группы блока проверки условий соединены с входами дешифратора и с управляющими входа.ми мультиплексора.При таком решении значение условия, формирующегося в последнем микро По нулевому адресу из блока памяти микрокоманд выбирается начальная микрокоманда и поступает на информационные входы регистра 2 микро- команд. Так как содержимое регист45 ра 2 микрокоманд равно нулю, нулевые сигналы присутствуют на выходах группы элементов 7 И и элемента 9 И. Вырабатывается сигнал 24, по которому регистр 6 блокировки устанав ливается в единичное состояние, а в регистры 2 микрокоманд заносится микрокоманда,Каждая микрокоманда состоит из четырех частей - адресной, кода опе рации, кода микрооперации и кода анализируемых логических условий.В адрвсной части микрокоманды содержится информация, иа основании которой формируется адрес следующей 15 микрокоманды.Например, для выполнения занесенной в регистр 2 микрокоманды необходимы три микротакта, причем в течение первого, второго и третье-. го микротактов единичный сигнал должен присутствовать на выходе первого, пятого и двенадцатого элементов 7 И соответственно. Тогда на первом, пятом и двенадцатом управляющих выходах. регистра 2 микрокоманд присутствуют единичные сигналы, а на остальных - нулевые. На выходе первого элемента 7 И вырабатывается сигнал 25, в результате чего все последующие элементы 7 И и элемент 9 И оказываются закрытыми.Во втором микротакте по импульсу 21 и при наличии единичного сигнала на первом установочном входе35 первый разряд регистра 6 блокировки устанавливается в ноль. Первый элемент 7 И закрывается, открывая все последующие элементы 7.И. Так как второй, третий и четвертый элементы 7 И закрыты нулевыми сигналами с управляющих выходов регистра 2 микрокоманд, единичный сигнал 26 вырабатывается на выходе пятого элемента 7 И.В третьем микротакте по импульсу 21 устанавливается в ноль . пятый разряд регистра 6 блокировки. Закрывается пятый элемент 7 И и единичный сигнал 27 вырабатывается на выходе двенадцатого элемента 7 И.Одновременно с выполнением текущей микрокоманды по ее адресной части подготавливается к выполнению следующая микрокоманда.55Непосредственный адрес следующей микрокоманды поступает на входы группы элементов 19 И. Номер условия поступает на управляющие входы дешифратора 14 и мультиплексора 15. Биттипа перехода поступает на входыгруппы элементов 18 ИЛИ, а бит предполагаемого значения условия - навходы группы элементов 17 И, на входэлемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ и напервый вход мультиплексора 15.Если выполняется безусловный переход (бит типа перехода равен единице), на выходах группы элементов18 ИЛИ присутствуют единичные сигналы, и адрес следующей микрокрмандыопределяется непосредственно из адресной части предыдущей,При выполнении условных переходов.(бит типа перехода равен нулю ) адресследующей микрокоманды формируется взависимости от значения сигналовусловий, поступающих с входов 11устройства через группы элементов16 И и 18 ИЛИ на входы группы элементов 19 И.Сформированный блоком 4 проверкиусловий адрес следующей микрокоманды по импульсу 21 заносится в регистр 3 адреса.Если в микрокоманде выполняетсябезусловный переход или условныйпереход без учета услойий, определяемых в последнем микротакте, поле номера условия равно нулю, При этомединичный сигнал вырабатывается напервом выходе дешифратора 14, амультиплексор 15 подключает на свойвыход сигнал с (ш + 1)-го входа,Так как сигналы на входах элемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ совпадают,сигнал 23 на его выходе равен нулю.Сигналом 23 закрыт элемент 9 И.При поступлении очередного импульса 21 (см.фиг.4 а ) устанавливаетсяв ноль двенадцатый разряд регистра 6 блокировки, закрывается двенадцатый элемент 7 И. На выходах всехэлементов 7 И и на выходе элемента 9 И присутствуют нулевые сигналы. Вырабатывается сигнал 24, по которому регистр 6 блокировки устанавливается в исходное единичное состояние, а в регистр 2 заносится следующая микрокоманда,Выполнение условных переходов с учетом условий, определяемыхв последнем микротакте, осуществляется следующим образом. Так как сигнал условия по результату выполнения последнего 1 третьего микроприказа)9 1374 формируется только в конце последнего ( третьего 1 микротакта, . то оказывается неучтенным при формировании адреса следующей микрокоманды. Поэ тому в этих случаях в микрокоманде . задается не нулевой номер условия, значение которого определяется в последнем микротакте, а в бите, поступающем на входы элементов 7 И и 20 ИСКЛЮЧАЮЩЕЕ ИЛИ, указывает О ся предполагаемое значение этого условия.По номеру условия на одном из выходов дешнфратора 4 вырабатывается единичныйсигнал, а мультиплексор 15 подключает на вход элемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ сигнал соответствующего условия.По единичному сигналу с выхода дешифратора 14 закрывается соответ- . ствующий элемент 16 И и открывается соответствующий элемент 17 И. В результате этого адрес следующей микрокоманды формируется с учетом не действительного, а предполагаемого значения условия. В конце третьего микротакта формируется сиг-, нал 22 и поступает через мультиплексор 15 на вход элемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ. Если действительное значение сигнала условия совпадает с предполагаемым, сигнал 23 равен нулю и элемент 9 И оказывается закрытым. При поступлении очередного импульса 21 выполнение микрокоманды завершается аналогичным образом в соответствии с диаграммой на фиг. 4 а.В случае, если действительно значение сигнала условия не совпадает с предполагаемым, сигнал 23 67 Оустанавливается в единичное состояние (см.фиг. 4 б. При этом блокируется дешифратор 14, в результате чего на выходах блока 4 проверки условий формируется адрес с учетом действительного значения условия .При поступлении импульса 21 действительный адрес заносится в регистр 3 адреса. Сигнал 27 устанавливается в нулевое состояние, после чего единичный сигнал вырабатывается на выхо; де элемента 9 И. Микротакт, в течение которого единичный сигнал присутствует на выходе элемента 9 И, является "холостым". За этот микро- такт. производится повторная выборка микрокоманды из блока 1 памяти по вновь сформированному адресу. При поступлении следующего импульса 21 и при наличии на установочном входе единичного сигнала с выхода элемента 9 И устанавливается в ноль соответствующий разряд 6 блокировки. В результате этого закрывается элемент 9 И, после чего вырабатывается сигнал 24 и следующая микрокоманда заносится в регистр 2 микрокоманд. Таким образом, в предлагаемом устройстве потери производительности за счет "холостых" микротактов имеют место только в маловероятных случаях, когда действительное значение условия не совпадает с предполагаемым, в отличие от прототипа, где потери в быстродействии имеют место при выполнении каждого перехода по условию, определяемому в последнем микротакте..Долини едакто Заказ 10525/36 одпис Тираж 710 Государственного елам изобретений Москва, Ж"35, Р 1130 ал ППП "Патент", г.ужгород, ул.Проектная 2 д Ж 8 комитета СССРн открытийушская наб., д.4/5

СмотретьЗаявка

3551297, 08.02.1983

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО ЮЖНОГО ГОЛОВНОГО МОНТАЖНОГО УПРАВЛЕНИЯ СРЕДСТВ СВЯЗИ ЦЕНТРАЛЬНОГО НАУЧНО ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КАСКАД"

ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ, ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное, управляющее

Опубликовано: 30.01.1985

Код ссылки

<a href="https://patents.su/9-1137467-mikroprogrammnoe-upravlyayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное управляющее устройство</a>

Предыдущий патент: Генератор случайного потока чисел

Следующий патент: Устройство приоритета

Случайный патент: Автоклавная установка для вышелачивания боксита