Микро-эвм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

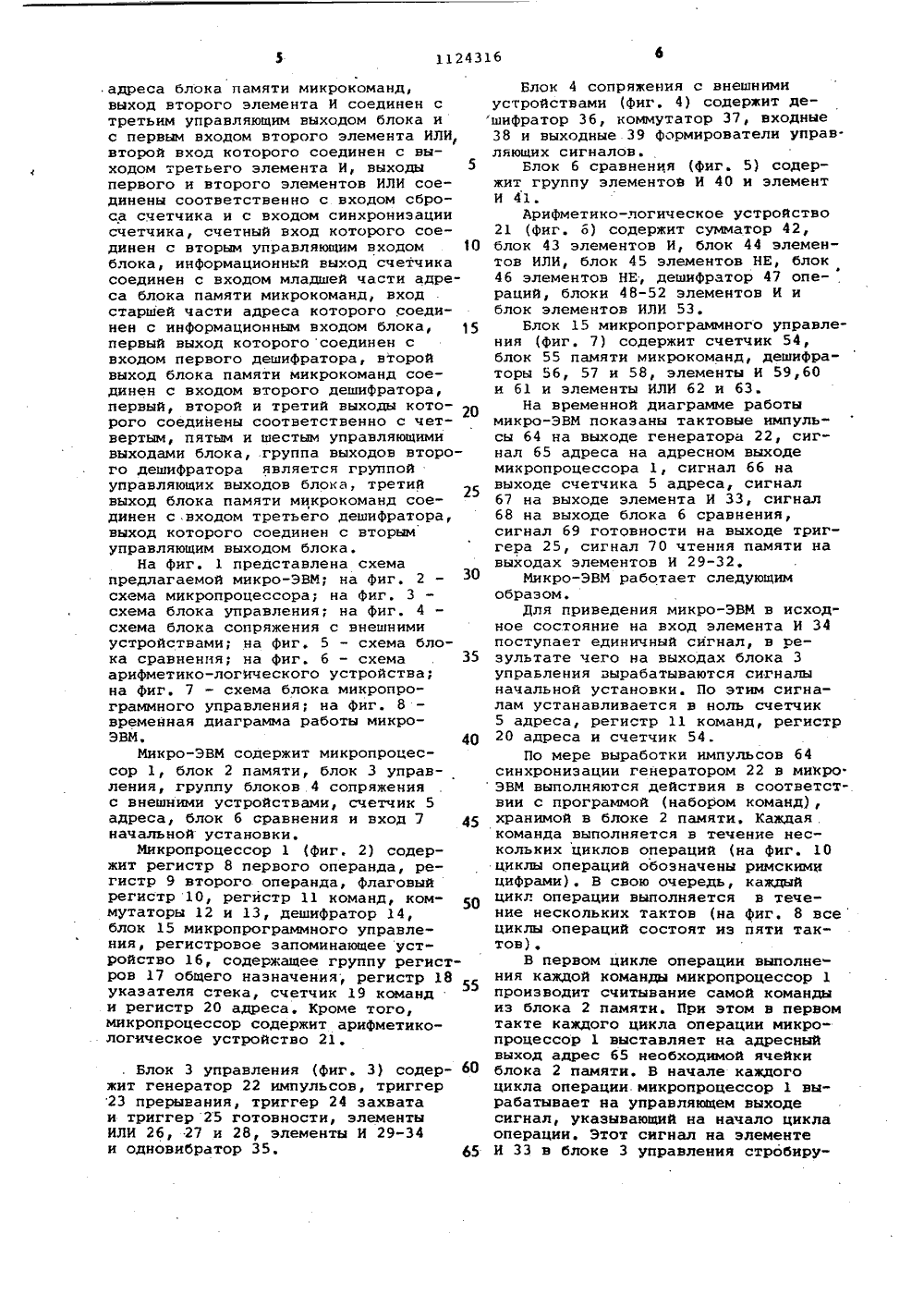

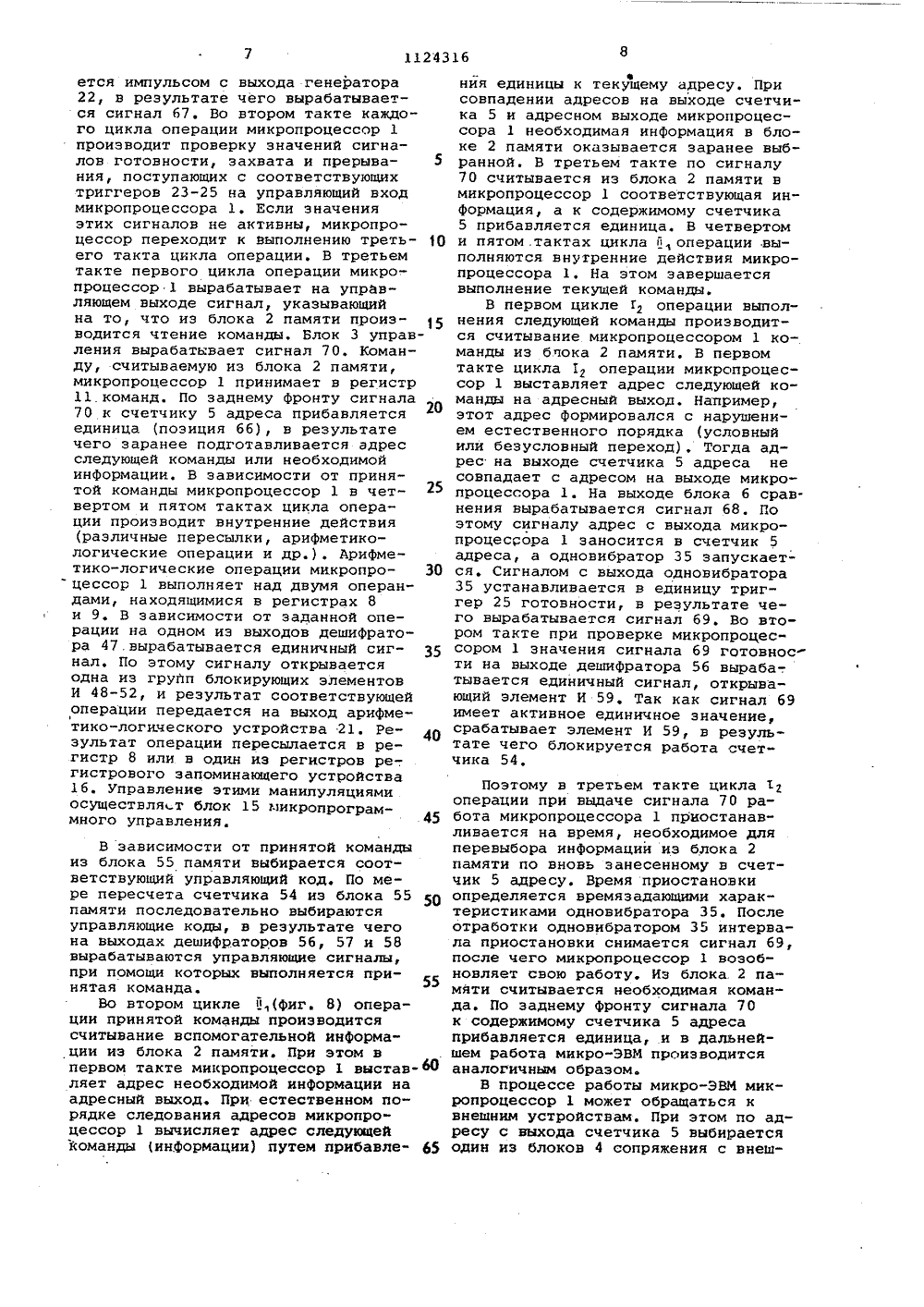

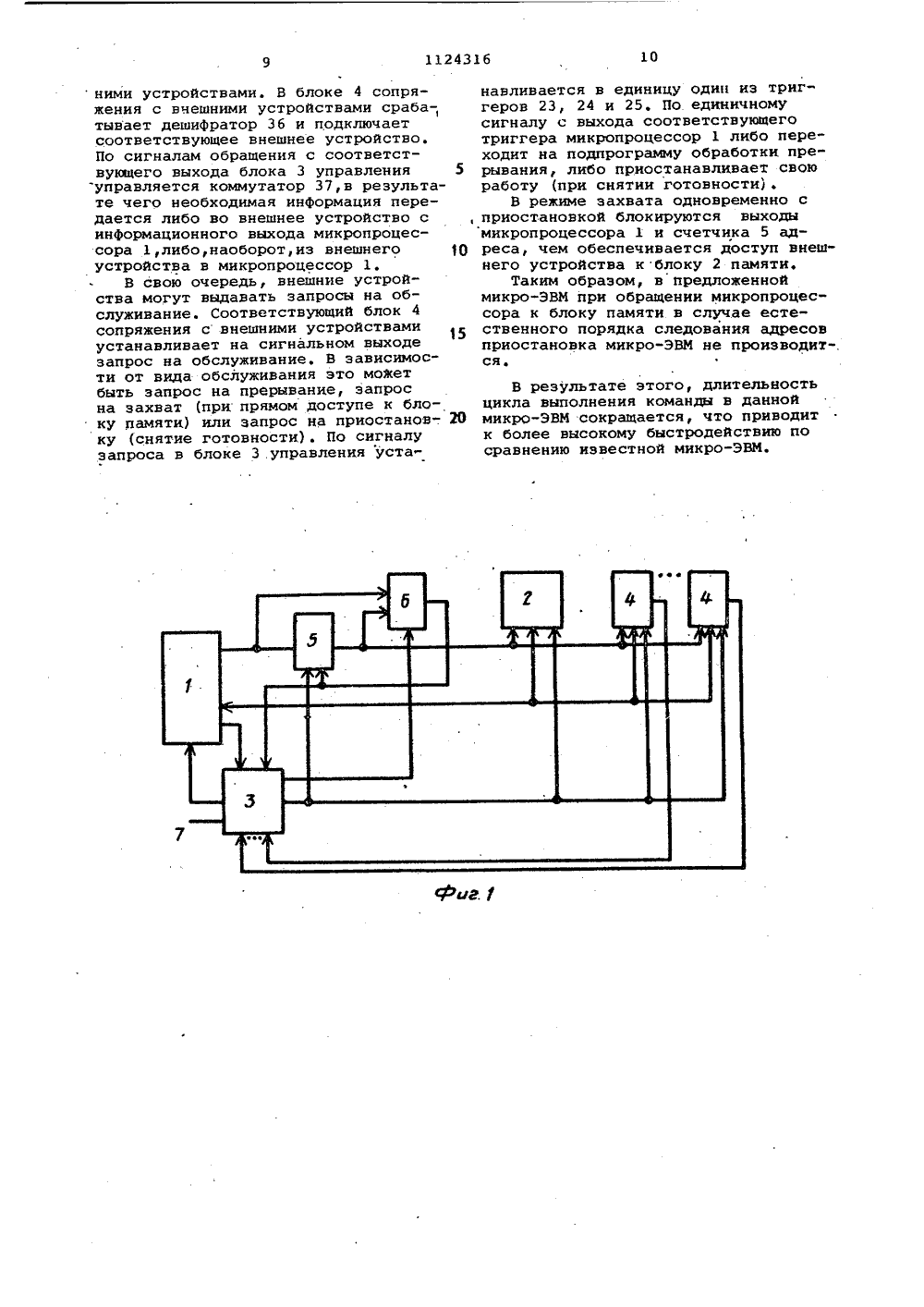

блоков сопряжения с внешними устройствами и с информационным выходом счетчика адреса, счетный вход которого соединен с выходом второго элемента И, вход сброса счетчика адреса соединен с .выходом первого элемента И, вход записи счетчика адреса соединен с входом одновибратора и с выходом блока сравнения, стробирующий вход которого соединен с выходом четвертого элемента И.2. Микро-ЭВМ по п,1, о т л и ч а ю щ а я с я тем, что микропроцессор содержит регистр первого операнда, регистр второго операнда, флаговый регистр, регистр команд, первый и второй коммутаторы, дешифратор, арифметико-логическое устройство, регистровое запоминающее устройство и блок .микропрограммного управления, первый управляющий выход которого соединен с входами записи регистра первого операнда и регистра второго операнда, выходы регистра первого операнда и регистра второго операнда соединены соответственно с первым и вторым информационными входами арифметико-логического устройства, вход кода операции которого соединен с вторым управляющим выходом блока микропрограммного управления и с входом записи флагового регистра, выход которого соединен с входом переноса арифметико-логического блока, выход переноса которого соединен с первым информационным входом перного коммутатора, второй информационный вход которого соединен с первым выходом второго коммутатора, второй выход которого соединен с информационным входом регистрового запоминающего устройства, первый информационный вход второго коммутатора соединен с первым. выходом первого коммутатора, с информационными входами регистра первого операнда, регистра второго операнда, флагового регистра и регистра команд и с входом дешифратора, второй информационный вход второго коммутатора соединен с первым информационным выходом регистрового запоминающего устройства, второй информационный выход которого является адресным выходом микропроцессора, вход записи регистра команд, управляющие входы первого и второго коммутаторов и первый . входчтения-записи регистровго запо.- минающего устройства подключены к третьему управляющему выходу блока микропрограммного управления, вход кода команды которого соединен с выходом регистра команд, группа выходов дешифратора соединена с группой управляющих входов регистрового запоминающего устройства, второй выход первого коммутатора является .информационным выходом микропроцессора, третий информационный вход первого коммутатора является информационным входом микропроцессора, первый,второй, третий., четвертый и пятый управляющие входы блока микропрограммного управления являются соответственно первым, вторым, третьим, четвертым и пятым управляющими входами микропроцессора, четвертый, пятый и шестой управляющие выходы блока микропрограммного управления являются соответственно первым, вторым и третьим управляющими выходами микропроцессора, группа управляющих выходов блока микропрограммного управления является группой управляющих выходов микропроцессора.3, Микро-ЭВМ по пп.1 и 2, о т л и ч а ю щ а я с я тем, что блок микропрограммного управления содержит счетчик, блок памяти микрокоманд,три дешифратора, два элемента ИЛИ и три элемента И, причем первый вход первого элемента ИЛИ соединен с первым управляющим входом блока и с первым управляющим выходом блока, второй вход первого элемента ИЛИ соединен с выходом первого дешифратора, второй выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с пятым и четвертым управляющими входами блока, третий выход дешифратора соединен с первым входом третьего элемента И, второй вход которого соединен с третьим управляющим входом блока, выход первого элемента И соединен, с входом младшего разряда адреса блока памяти микрокоманд, выход второго элемента И соединен с третьим управляющим выходом блока и с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выходы первого и второго элементов ИЛИ соединены соответственно с входом сброса счетчика и с входом синхронизации счетчика, счетный вход которого соединен со вторым управляющим входом блока, информационный выход счетчика соединен с входом младшей части адреса блока памяти микрокоманд, вход старшей части адреса которого соединен с информационным входом блока, первый выход которого соединен с входом первого дешифратора, второй выход блока памяти микро- команд соединен с входом второго дешифратора первый, второй и третий выходы которого соединечы соответственно с четвертым, пятым и шестым управляющими выходами блока, группа выходов второго дешифратора является группой, управляющих выходов блока, третий выход блока памяти микро- команд соединен с входом третьего дешифратора, выход которого соеди- нен со вторым управляющим выходом блока.Изобретение относится к вычислительной технике и может быть использовано в системах управления,Известна микро-ЭВМ, содержащаямикропроцессор, блок памяти, блокуправления, регистр состояния и блоки сопряжения с внешними устройствами 13Недостатком данной микро-ЭВМ является низкое быстродействие. Этообусловлено тем, что при считывании 10микропроцессором информации из блока памяти производится приостановкаработы микро-ЭВМ на время, требуемое для выборки информации из блока памяти15Наиболее близкой к предлагаемойпо технической сущности являетсямикро-ЭВМ, содержащая блок памяти,группу ь блоков сопряжения с внешними устройствами, микропроцессори блок управления, содержащий триэлемента ИЛИ, триггер захвата, триггер готовности; четыре элемента И,генератор импульсов, одновибратори группу и элементов И, -е (= 1,2,3) входы рервого, второго и третьего элементов ИЛИ соединены соответственно с запросным выходом -го блока сопряжения с внешними устройствами, выходы первого,второго и третьего элементов ИЛИ сое динены соответственно с запроснымвыходом -го блока сопряжения свнешними. устройствами, выходы первого, второго и третьего элементовИЛЙ соединены соответственно с входом установки в единицу триггерапрерывания, с информационным входомтриггера захвата и с информационнымвходом триггера готовности, входысброса которых соединены с выходомпервого элемента И и с первым управляющим входом микропроцессора, первый вход первого элемента И соединен с первыми входами второго, третьего и четвертого элементов Й и элементов И группы, с вторым управляющим входом микропроцессора, с вы- .ходом генератора импульсов и с входа- .ми синхронизации триггера захватаи триггера готовности, вход установки в ноль триггера прерывания соединен с вторым входом второго элементаИ и с первым управляющим выходом микропроцессора,выходы триггера прерыва"ния, триггера захвата и триггера готовности соединены соответственно 55с третьим,.четвертым и пятым управляющими входами микропроцессора,вторые входы третьего и четвертогоэлементов И соединены соответственно с вторым и третьим управляющими 0входами микропроцессора, второй вход1-го элемента И группы соединен соответственно с 4-м управляющим в)яходом группы микропроцессора, второйвход первого элемента И соединен свходом начальной установки микро-ЭВМ; 65( о +1)-й вход третьего элемента ИПГсоединен с выходом одновибратора,выход -го элемента И группы соединен соответственно с управляющимвходом -го блока сопряжения свнешними устройствами, выходы триггера захвата и третьего элемента Исоединены соответственно с входомчтения блока памяти и входом записиблока памяти, информационный входмикропроцессора соединен с информационными входами блока памяти и блоков сопряжения с внешними устройствами, информационный выход микропроцессора соединен с информационными входами блока памяти и блоковсопряжения 2,Недостатком известной микро-ЭВМявляется низкое быстродействие, Этообусловлено тем, что при считываниимикропроцессором информации из блока памяти производится приостановкаработы микро-ЭВМ на время, необходимое для выборки информации из памяти. Цель изобретения - повышениебыстродействия микро-.ЭВМ,Поставленная цель достигаетсятем, что в микро-ЭВМ, содержащуюблок памяти, группублоков сопряжения с внешними устройствами, микропроцессор и блок управления, содержащий три элемента ИЛИ, триггерпрерываний, триггер захвата, триггерготовности, четыре элемента И, генератор импульсов, одновибратор и группу ь элементов Й, -е ( = 1,2,3,и) входы первого, второго и третьего элементов ИЛИ соединены соответственно с запросным выходом -гоблока сопряжения с внешними устройствами, выходы первого, второго итретьего элементов ИЛИ соединенысоответственно с входом установки в:единицу триггера прерывания, с информационным входом триггера захвата и с информационным входом тригге.ра готовности, входы сброса которыхсоединены с выходом первого элемента И и с первым управляющим входоммикропроцессора, первый вход первого элемента И соединен с первымивходами второго, третьего и четвертого элементов И и элементов И группы, с вторым управлякяцим входоммикропроцессора, с выхода генератора импульсов и с входами синхронизации триггера захвата и триггера готовности, вход установки в нольтриггера прерывания соединен с вторым входом второго элемента И и спервым управляющим выходом микропроцессора, выходы триггера прерывания,триггера захвата и триггера готовности соединены соответственно стретьим, четвертым и пятым управляющими входами микропроцессора, вторые входи третьего и четвертого эле40 жит регистр первого операнда, регистр 50 операнда и регистра второго операнда,выходы регистра первого операнда ирегистра второго операнда соединенысоответственно с первым и вторым информационными входами арифметикологического устройства, вход кодаоперации которого соединен с вторымуправляющим выходом блока микропрограммного управления и с входом записи флагового регистра, выход. кото 5560 рого соединен с входом переноса арифметико-логического блока, выход пере.носа которого соединен с первым ин.формационным входом первого коммута.тора, второй информационный вход ко 65 ментов И соединены соответственно свторым и третьим управляющими выходами микропроцессора, второй вход1-го элемента И группы соединен соответственно с 1-м управляющим выходом группы микропроцессора, второйвход первого элемента И соединен свходом начальной установки микроЭВМ, ( и+1)-й вход третьего элемента ИЛИ соединен с выходом одновибратора, выход 1-го элемента И группы соединен соответственно с управляющим входом 1-.го блока сопряжения с внешними устройствами, выходытриггера захвата и третьего элемента И соединены соответственно с входом чтения блока памяти и с входомзаписи блока памяти, информационныйвход микропроцессора соединен с инФормационными входами блока памятии блоков сопряжения с внешними устройствами, информаЦионный выход микропроцессора соединен с информационными входами блока памяти и блоковсопряжения, введены блок сравненияи счетчик адреса, причем информационный вход счетчика адреса соединенс адресным выходом микропроцессораи с первым информационным входом .блока сравнения, второй информационный вход которого соединен с адресными входами блока памяти и блоковсопряжения с внешними устройствамии с информационным выходом счетчикаадреса, счетный вход которого соединен с выходом второго элемента И,вход сброса счетчика адреса соединен с выходом первого элемента И,вход записи счетчика адреса соединен с входом одновибратора и с выхо дом блока сравнения, стробирующийвход которого соединен с выходомчетвертого элемента И,1Кроме того, микропроцессор содервторого операнда, флаговый регистр,регистр команд, первый и второй коммутаторы, дешифратор, арифметикологическое устройство, регистровоезапоминающее устройство и блок микропрограммного управления, первыйуправляющий выход которого соединенс входами записи регистра первого 5 10 15 20 25 30 35 торого соединен с первым выходомвторого коммутатора, второй выходкоторого соединен с информационнымвходом регистрового запоминающегоустройства, первый информационныйвход второго коммутатора соединен спервым выходом первого коммутатора, с информационными входами регистра первого операнда, регистра второго операнда, флагового регистра и регистра команд и с входом дешифратора, второй информационный вход второго коммутатора соединен с первым информационным выходом регистровогозапоминающего устройства, второй информационный выход которого являетсяадресным выходом микропроцессора, вход записи регистра команд, управляющие входы первого и второго коммутаторов и первый вход чтения-записи регистрового запоминающего устройства подключены к третьему управляющему выходу блока микропрограммного управления, вход кода командыкоторого соединен с выходом регистра команд, группа выходов дешифратора соединена с группой управляющих входов регистрового запоминающего устройства, второй выход первого коммутатора является информационным.выходом микропроцессора, третий информационный вход первого коммутатора является информационным входом микропроцессора, первый, второй, третий, четвертый и пятый управляющие входы блока микропрограммного управления являются соответственнопервым, вторым, третьим, четвертыми пятым управляющими входами микропроцессора, четвертый, пятый и шестой управляющие выходы блока микропрограммного управления являются соответственно первым, вторым и третьим управляющими выходами микропроцессора, группа управляющих выходов блока микропрограммногоуправления является группой управляющих выходов микропроцессора.Кроме того, блок микропрограммного управления содержит счетчик, блок памяти микрокоманд, три дешифратора, два элемента ИЛИ и три элемента И, причем первый вход первого элемента ИЛИ соединен с первым управляющим входом блока и с первыМ управляющим выходом блока, второй вход первого элемента ИЛИ соединен с выходом первого дешифратора, второй выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с пятым и четвертым управляющими входами блока, третий выход дешифратора соединен с первым входом третьего элемента И, второй вход которого соединен с третьим управляющйм входом блока, выход первого элемента И, соединен с входом младшего разряда40 Блок 3 управления (Фиг. 3) содержит генератор 22 импульсов, триггер23 прерывания, триггер 24 захватаи триггер 25 готовности, элементыИЛИ 26, 27 и 28, элементы И 29-34и одновибратор 35. 65 адреса блока памяти мнкрокоманд,выход второго элемента И соединен стретьим управляющим выходом блока ис первым входом второго элемента ИЛИ,второй вход которого соединен с выходом третьего элемента И выходы 5первого и второго элементов ИЛИ соединены соответственно с входом сброса счетчика и с входом синхронизациисчетчика, счетный вход которого соединен с вторым управляющим входом 10блока, информационный выход счетчикасоединен с входом младшей части адреса блока памяти микрокоманд, входстаршей части адреса которого соединен с информационным входом блока, 15первый выход которого соединен свходом первого дешифратора, второйвыход блока памяти микрокоманд соединен с входом второго дешифратора,первый, второй и третий выходы которого соединены соответственно с четвертым, пятым и шестым управляющимивыходами блока, группа выходов второго дешифратора является группойуправляющих выходов блока, третийвыход блока памяти микрокоманд соединен с .входом третьего дешифратора,выход которого соединен с вторымуправляющим выходом блока,На фиг. 1 представлена схемапредлагаемой микро-ЭВМ; на фиг, 2схема микропроцессора; на Фиг. 3схема блока управления; на Фиг. 4схема блока сопряжения с внешнимиустройствами; на Фиг, 5 - схема блока сравнения; на фиг. 6 - схема . 35арифметико-логического устройства;на фиг. 7 - схема блока микропрограммного управления; на фиг. 8временная диаграмма работы микроЭВМ.Микро-ЭВМ содержит микропроцессор 1, блок 2 памяти, блок 3 управления, группу блоков 4 сопряженияс внешними устройствами, счетчик 5адреса, блок 6 сравнения и вход 7начальной установки.Микропроцессор 1 (фиг, 2) содержит регистр 8 первого операнда, регистр 9 второго операнда, флаговыйрегистр 10, регистр 11 команд, коммутаторы 12 и 13, дешифратор 14,блок 15 микропрограммного управления, регистровое запоминающее устройство 16, содержащее группу регистров 17 общего назначения, регистр 18указателя стека, счетчик 19 команди регистр 20 адреса. Кроме того,микропроцессор содержит арифметикологическое устройство 21,Блок 4 сопряжения с внешнимиустройствами (фиг. 4) содержит дешифратор 36, коммутатор 37, входные38 и выходные 39 формирователи управляющих сигналовБлок 6 сравнения (фиг. 5) содержит группу элементов И 40 и элементИ 41.Арифметико-логическое устройство21 (Фиг. 6) содержит сумматор 42,блок 43 элементов И, блок 44 элементов ИЛИ, блок 45 элементов НЕ, блок46 элементов НЕ, дешифратор 47 операций, блоки 48-52 элементов И иблок элементов ИЛИ 53.Блок 15 микропрограммного управления (фиг, 7) содержит счетчик 54,блок 55 памяти микрокоманд, дешифраторы 56, 57 и 58, элементы И 59,60и 61 и элементы ЙЛИ 62 и 63.На временной диаграмме работымикро-ЭВМ показаны тактовые импульсы 64 на выходе генератора 22, сигнал 65 адреса на адресном выходемикропроцессора 1, сигнал 66 навыходе счетчика 5 адреса, сигнал67 на выходе элемента И 33, сигнал68 на выходе блока 6 сравнения,сигнал 69 готовности на выходе триггера 25, сигнал 70 чтения памяти навыходах элементов И 29-32.Микро-ЭВМ работает следующимобразом,Для приведения микро-ЭВМ в исходное состояние на вход элемента И 34поступает единичный сигнал, в результате чего на выходах блока 3упраьления вырабатываются сигналыначальной установки. По этим сигналам устанавливается в ноль счетчик5 адреса, регистр 11 команд, регистр20 адреса и счетчик 54.По мере выработки импульсов 64синхронизации генератором 22 в микро.ЭВМ выполняются действия в соответствии с программой (набором команд),хранимой в блоке 2 памяти. Каждая .команда выполняется в течение нескольких циклов операций (на фиг. 10циклы операций обозначены римскимициФрами). В свою очередь, каждыйцикл операции выполняется в течение нескольких тактов (на фиг. 8 всециклы операций состоят из пяти тактов).В первом цикле операции выполнения каждой команды микропроцессор 1производит считывание самой командыиз блока 2 памяти. При этом в первомтакте каждого цикла операции микропроцессор 1 выставляет на адресныйвыход адрес 65 необходимой ячейкиблока 2 памяти, В начале каждогоцикла операции микропроцессор 1 вырабатывает на управляющем выходесигнал, указывающий на начало циклаоперации. Этот сигнал на элементеИ 33 в блоке 3 управления стробиру 1124316ется импульсом с выхода генератора22, в результате чего вырабатывается сигнал 67. Во втором такте каждого цикла операции микропроцессор 1производит проверку значений сигналов готовности, захвата и прерывания, поступающих с соответствующихтриггеров 23-25 на управляющий входмикропроцессора 1, Если значенияэтих сигналов не активны, микропроцессор переходит к выполнению третьего такта цикла операции. В третьемтакте первого цикла операции микропроцессор 1 вырабатывает на управляющем выходе сигнал, указывающийна то, что из блока 2 памяти производится чтение команды, Блок 3 управления вырабатывает сигнал 70. Команду, считываемую из блока 2 памяти,40 45 из блока 55 памяти выбирается соответствующий управляющий код. По мере пересчета счетчика 54 из блока 55 50памяти последовательно выбираютсяуправляющие коды, в результате чегона выходах дешифраторов 56, 57 и 58вырабатываются управляющие сигналы,при помощи которых выполняется принятая команда,Во втором цикле й(фиг. 8) операции принятой команды производитсясчитывание вспомогательной информации из блока 2 памяти. При этом впервом такте микропроцессор 1 выставмикропроцессор 1 принимает в регистр 11.команд. По заднему фронту сигнала70 к счетчику 5 адреса прибавляетсяединица (позиция 66), в результатечего заранее подготавливается адресследующей команды или необходимойинформации. В зависимости от принятой команды микропроцессор 1 в четвертом и пятом тактах цикла операции производит внутренние действия(различные пересылки, арифметикологические операции и др,). Арифметико-логические операции микропроцессор 1 выполняет над двумя операндами, находящимися в регистрах 8и 9. В зависимости от заданной операции на одном из выходов дешифратора 47.вырабатывается единичный сигнал. По этому сигналу открываетсяодна из групп блокирующих элементовИ 48-52, и результат соответствующейоперации передается на выход арифметико-логического устройства 21, Результат операции пересылается в регистр 8 или в один из регистров ре-.гистрового запоминающего устройства16, Управление этими манипуляциямиосуществлят блок 15 микропрограммного управления. В зависимости от принятой команды ляет адрес необходимой информации на адресный выход. При естественном по" рядке следования адресон микропро" цессор 1 вычисляет адрес следующей команды (информации) путем прибавле 20 25 30 35 нйя единицы к текущему адресу. Присовпадении адресов на выходе счетчика 5 и адресном выходе микропроцессора 1 необходимая информация в блоке 2 памяти оказывается заранее выбранной. В третьем такте по сигналу70 считывается из блока 2 памяти вмикропроцессор 1 соответствующая информация, а к содержимому счетчика5 прибавляется единица. В четвертоми пятом .тактах цикла йоперации выполняются внутренние действия микропроцессора 1. На этом завершаетсявыполнение текущей команды.В первом цикле 11 операции выполнения следующей команды производится считывание микропроцессором 1 команды из бчока 2 памяти. В первомтакте цикла 1 операции микропроцессор 1 выставляет адрес следующей команды на адресный выход. Например,этот адрес формировался с нарушением естественного порядка (условныйили безусловный переход), Тогда адрес на выходе счетчика 5 адреса несовпадает с адресом на выходе микропроцессора 1. На выходе блока 6 сравнения вырабатывается сигнал 68. Поэтому сигналу адрес с выхода микропроцессора 1 заносится в счетчик 5адреса, а одновибратор 35 запускается. Сигналом с выхода одновибратора35 устанавливается в единицу триггер 25 готовности, в результате чего вырабатывается сигнал 69. Во втором такте при проверке микропроцессором 1 значения сигнала 69 готовности на выходе дешифратора 56 выраба-.тывается единичный сигнал, открывающий элемент И 59. Так как сигнал 69имеет активное единичное значение,срабатывает элемент И 59, в результате чего блокируется работа счетчика 54,Поэтому в третьем такте цикла Т 2 операции при выдаче сигнала 70 работа микропроцессора 1 приостанав" ливается на время, необходимое для перевыбора информации иэ блока 2 памяти по вновь занесенному н счетчик 5 адресу. Время приостановки определяется времязадающими характеристиками одновибратора 35. После отработки одновибратором 35 интервала приостановки снимается сигнал 69, после чего микропроцессор 1 возобновляет свою работу. Из блока. 2 памяти считывается необходимая команда. По заднему фронту сигнала 70 к содержимому счетчика 5 адреса прибанляется единица, и в дальнейшем работа микро-ЭВМ производится аналогичным образом.В процессе работы микро-ЭВМ микропроцессор 1 может обращаться к внешним устройствам. При этом по адресу с выхода счетчика 5 выбирается один из блоков 4 сопряжения с внешними устройствами. В блоке 4 сопряжения с внешними устройствами сраба-, тывает дешифратор 36 и подключает соответствующее внешнее устройство. По сигналам обращения с соответствующего выхода блока 3 управления управляется коммутатор 37,в результате чего необходимая информация передается либо во внешнее устройство с информационного выхода микропроцессора 1,либо, наоборот,из внешнего устройства в микропроцессор 1.В свою очередь, внешние устройства могут выдавать запросы на обслуживание. Соответствующий блок 4 сопряжения с внешними устройствами устанавливает на сигнальном выходе запрос на обслуживание, В зависимости от вида обслуживания это может быть запрос на прерывание, запрос на захват (при прямом доступе к блоку памяти) или запрос на приостанов-. ку (снятие готовности). По сигналу запроса в блоке З.управления устанавливается в единицу один из триггеров 23, 24 и 25. По единичномусигналу с выхода соответствующеготриггера микропроцессор 1 либо переходит на подпрограмму обработки пре рывания, либо приостанавливает своюработу (при снятии готовности).В режиме захвата одновременно с,приостановкой блокируются выходымикропроцессора 1 и счетчика 5 ад реса, чем обеспечивается доступ внешнего устройства к блоку 2 памяти.Таким образом, в предложенноймикро-ЭВМ при обращении микропроцессора к блоку памяти в случае естественного порядка следования адресовприостановка микро-ЭВМ не производит-.ся. В результате этого, длительностьцикла выполнения команды в данной20 микро-ЭВМ сокращается, что приводитк более высокому быстродействию посравнению известной микро-ЭВМ.

СмотретьЗаявка

3480403, 13.08.1982

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО ЮЖНОГО ГОЛОВНОГО МОНТАЖНОГО УПРАВЛЕНИЯ СРЕДСТВ СВЯЗИ

ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ, ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микро-эвм

Опубликовано: 15.11.1984

Код ссылки

<a href="https://patents.su/9-1124316-mikro-ehvm.html" target="_blank" rel="follow" title="База патентов СССР">Микро-эвм</a>

Предыдущий патент: Устройство для формирования сигнала прерывания при отладке программ

Следующий патент: Устройство логической обработки

Случайный патент: Способ автоматической термической вырезки группы металлических деталей