Устройство для суммирования двоично-десятичных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 691851

Авторы: Владимиров, Габелко, Закидальский, Нифонтов, Пухов, Рябинин, Синьков

Текст

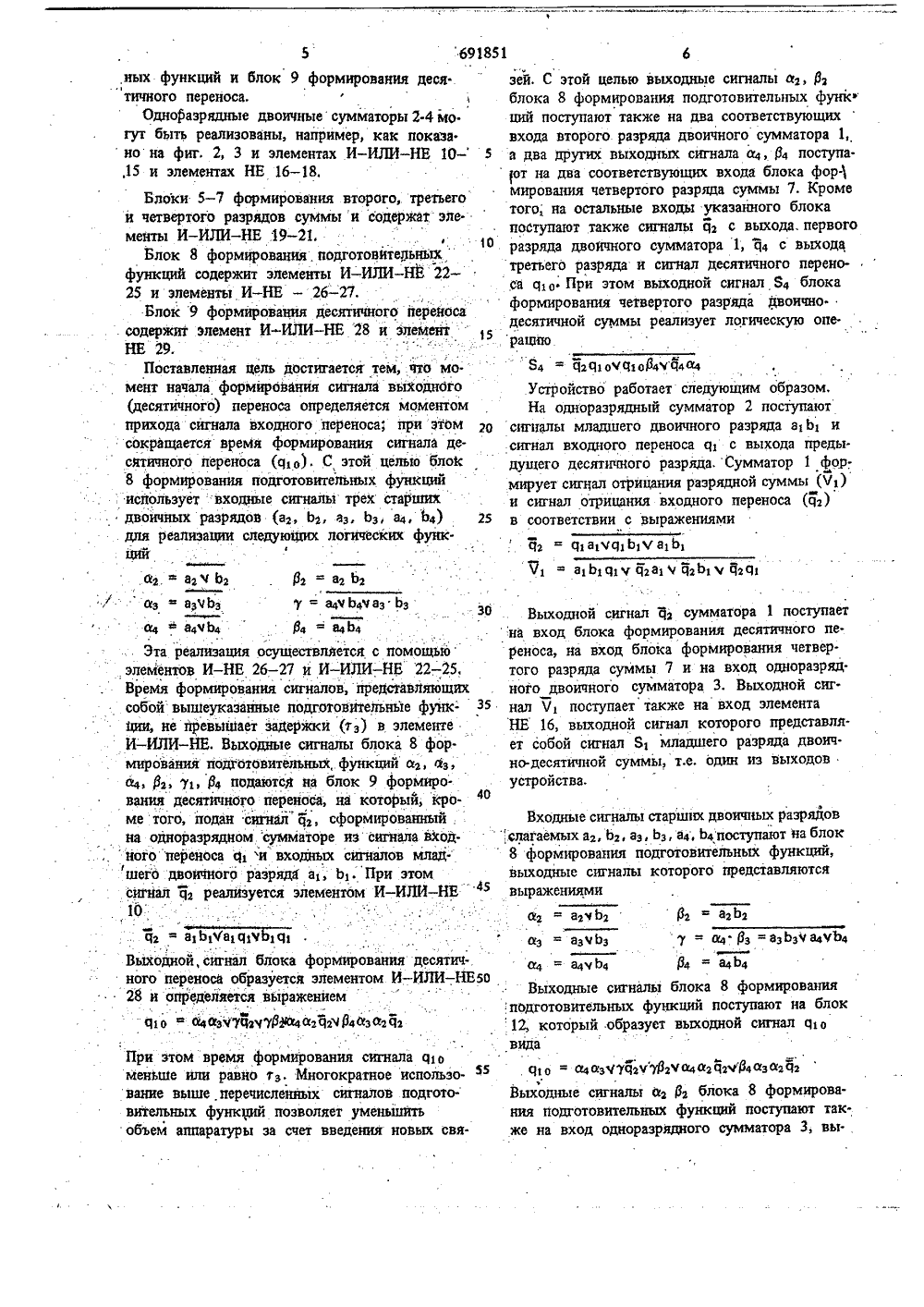

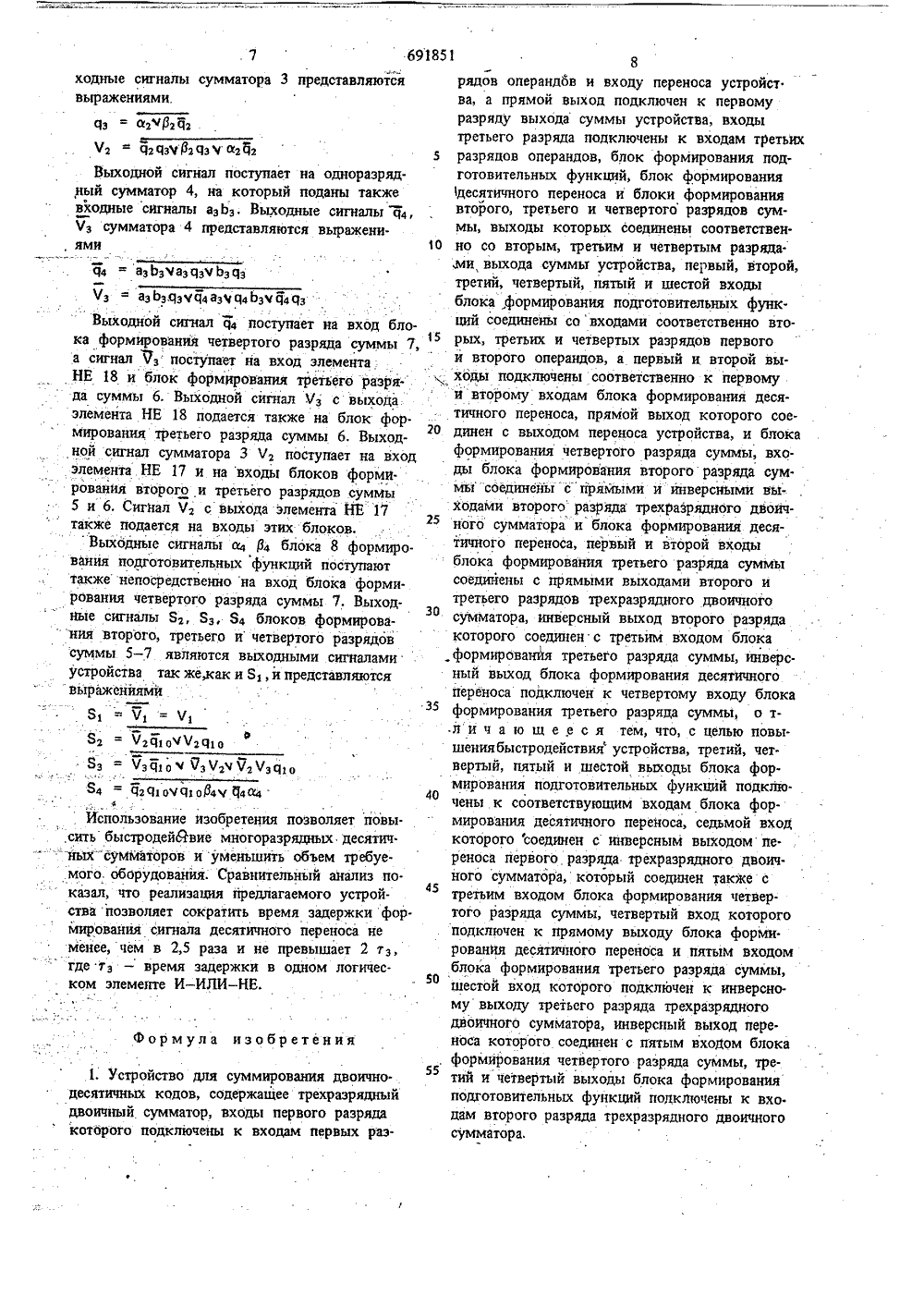

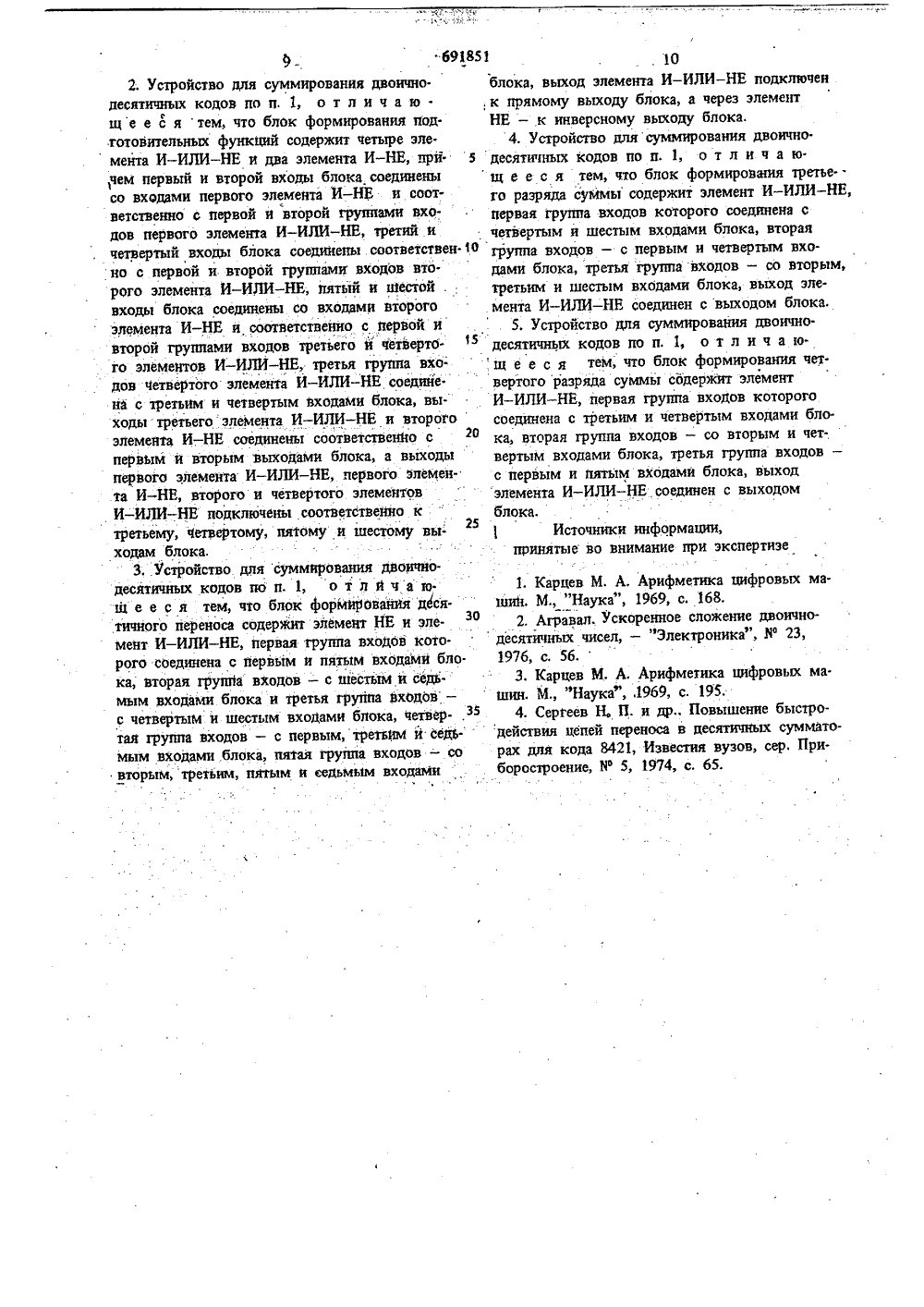

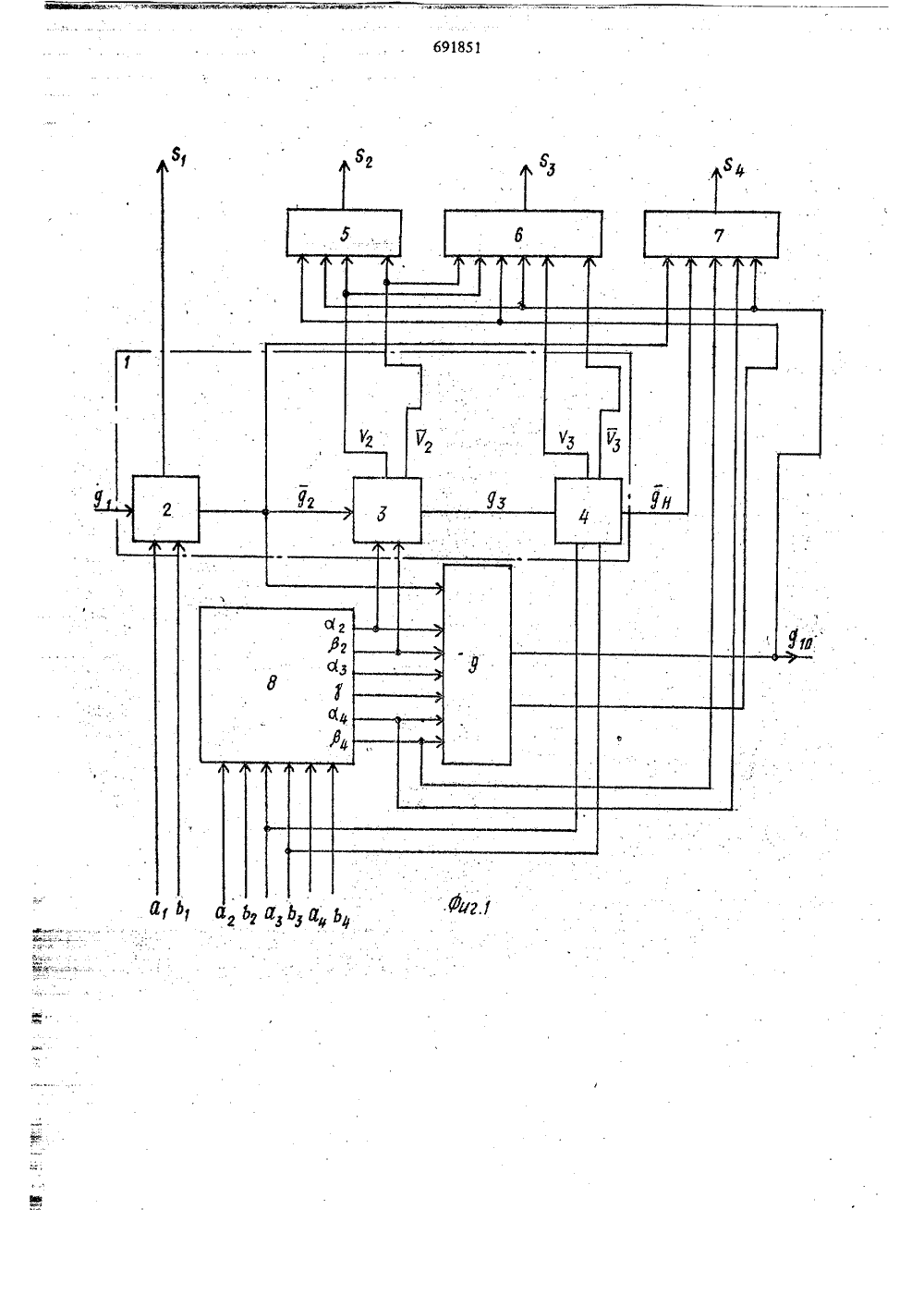

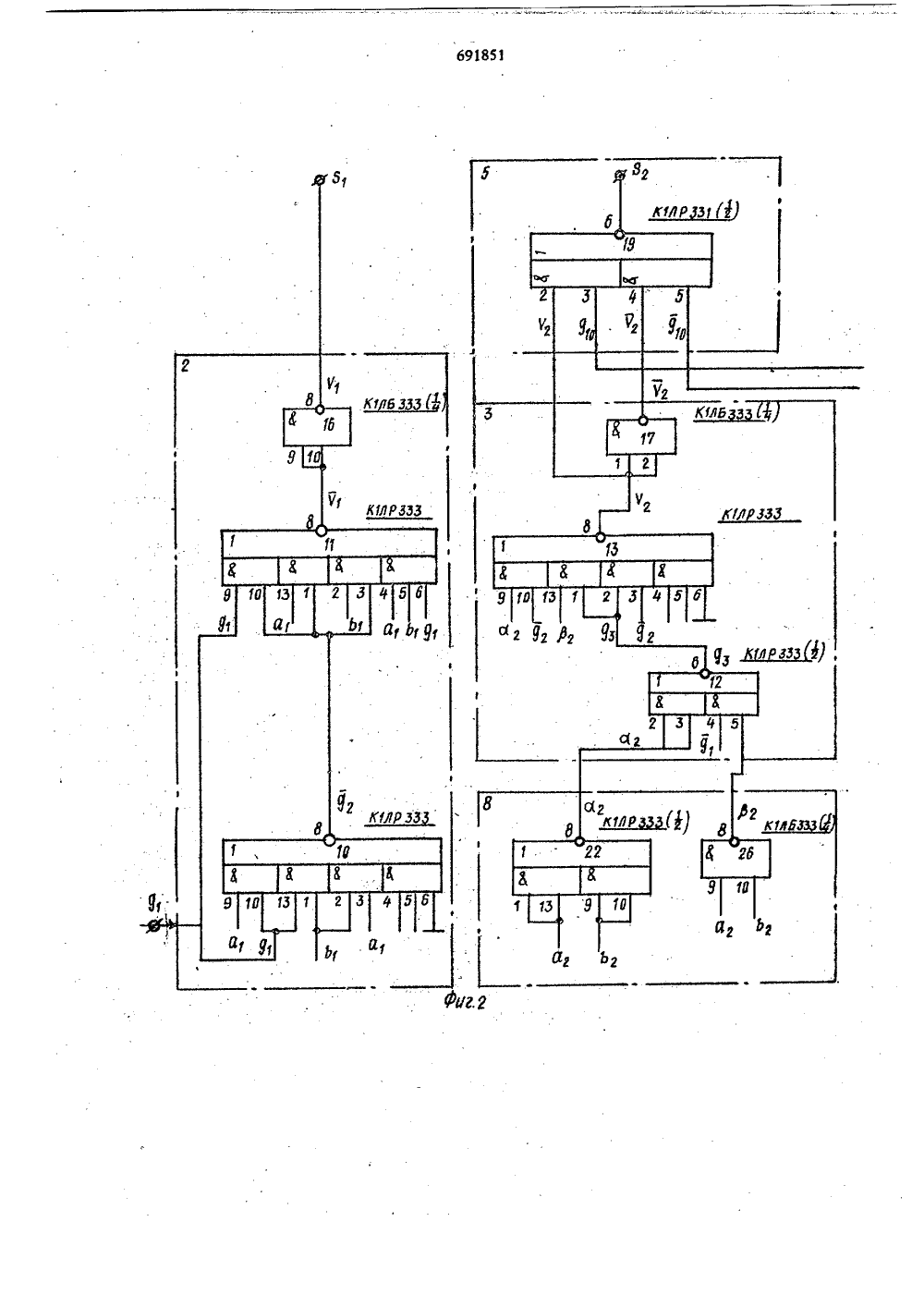

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СфветскикСоциакистичаскикеееспублик(53)М. Кл.О 06 Р 7/5 присоединением заявки РВ Гвсударственньб неинтет СССР ев делам нзвврвтвннй и втнрктнй3) Приоритет Опубликовайо 15,10,79 Бюллетень М 38 Дата опубликования описания 15,10,79 53 у УД К 681,325,5 (088,8) Г, Е. Пухов, М. В. Синьков, А. И. Закидальс Ю. М. Рябинин, В, К. Габелко и Н. Б, Нифо 72). Автори изобретен и миров(54) УСТРОЙСТВО ДЛЯ СУММИРОВАН ДВОИЧНО - ДЕСЯТИЧНЫХ КОДОВ азрядахатора, имир ования о Изобретение относится к области вычислительной техники, в частности к арифметическим устройствам с десятичной системой счисления,Изобретение может быть использовано вмногоразрядных десятичных сумматорах с ко.. дированием (1 - 2 - 4 - 8) и представляет собойо 1 цеоразрядный деоятичный сумматор.Известны устройства для суммированиядвоично-десятичных кодов, в которых имеются технические решения,"направленные на ускорение процесса считывания, Ускорение суммирования двоично десятичных кодов дости.гается, в частности, формированием сигналадесятичного переноса йз сигнала входного пере ,носа и пескорректированных сигналов двоич.ных сумм, который затем используется дляполучения скорректированной двоично десятич.ной суммы (1-3.Недостатком известных устройств являютсямалое быстродействие из-за запаздывания ситнала выходного переноса относительно сигналавходного переноса, что особенно снижает эф.фективность использования этого устройства 2в младших р многоразрццного десятичного суммсложность аппаратурпого решения фор сигнала выходного пе.- , реноса.Известно такжеустройство для суммирования двоично-десятичных кодов, содержащее трехразрядный двоичный сумматор, входы первого разряда которого подключены к входампервых разрядов операндов н входу переноса устройства, а примой выход подключен к пер.вому разряду выхода суммы устройства, входытретьего разряда подключены к входам третьих разрядов операндов, блок формирования подготовительпьас функций, блок формирования десятичного переноса и блоки формирования второго, третьего и четвертого разрядов суммы, выходыкоторых соединены соответственно со вторым, третьим и четвертым разрядами выхода суммы устройства, первый, второй, третий, четвертый, пятый и шестой входы блока формирования подготовительных функций соединеНы со входами соответственно вт рых, третьих и четвертых разрядов первого и второго операндов, а первый и второй вы.3 69185ходы подключены соответственно к первому и второму входам блока формирования десятичногопереноса, прямой выход которого соединен с вы.ходом переноса устройства, и блока формирования четвертого разряда суммы, входы бло;ка формирования второго разряда суммы соединены с прямыми и инверсными выходамивторого разряда трехразрядного двоичного,сумматора и блока формирования десятичногопереноса, первый и второй входы блока формирования третьего разряда суммы соединеныс прямыми выходами второго и третьего раз.рядов трехразрядного двоичного сумматора,инверсный выход второго разряда которогосоединен с третьиМ входом блока формирования третьего разряда суммы, инверсный выходблока формирования десятичного переноса подключен к четвертому входу блока формирования третьего разряда суммы 143,Недостатком известного устройства являетсянизкое быстродействие, обусловленное сравни.тельно медленным формированием сигнала де". . сятичного переноса. Этосвязайос тем,что входными сигналами блока формирования десятичного переноса помимо сравнительно быстрореализуемых подготовительных функций являются сигналы суммы второго и третьего разрядов двоичного сумматора, а также переносиз третьего разряда.Целью изобретения является повышениебыстродействия устройства.Для этого третий, четвертый, пятый и шестойвыходы блока формирования подготовительныхфункций подключены к соответствующим входам блока формирования десятичного переноса, седьмой вход которого соединен с инверсным выходом переноса первого разряда трехразрядного двоичного сумматора, который соединен также с третьим входом блока формирования четвертого разряда суммы, четвертыйвход которого подключен к прямому выходублока формирвания десятичного переноса ипятым входом блока формирования третьегоразряда суммы, шестой вход которого подключен к инверсному выходу третьего разряда" трехразрядного двоичного сумматора, инверсный выход переноса которого соединен с пятым входом блока формирования четвертогоразряда суммы, третий и четвертый выходыблока формирования подготовительных функ.,ций подключены к входам второго разрядатрехразрядного двоичного сумматора,"Поставленная цель достигается также тем,что блок формирования подготовительныхфункций содержит четыре элемента И - ИЛИ - НЕ55и два элемента И - НЕ, причем первый и вто.,рой входы блока соединены со входами первого элемента И - НЕ и соответственно с пер 1 4вой и второй группами входов первого эле.мента И - ИЛИ - НЕ, третий, четвертый входыблока соединены соответственно с первой ивторой группами входов второго элементаИ - ИЛИ - НЕ, пятый и шестой входы блокасоединены со входами второго элемента И - НЕи соответственно с первой и второй группамивходов третьего и четвертого элементовИ - ИЛИ - НЕ, третья группа входов четвертогоэлемента И - ИЛИ - НЕ соединена с третьими четвертым входами блока, выходы третьегоэлемента И - ИЛИ - НЕ и второго элементаИ - НЕ,соединены соответственно с первым ивторым выходами блока, выходы первого элемента И - ИЛИ - НЕ, первого элемента И - НЕ,второго и четвертого элементов И - ИЛИ - НЕподключены соответственно к третьему; чет.вертому, пятому и шестому выходам блока.Блок формирования десятичного переносасодержит элемент НЕ и элемент И - ИЛИ - НЕ,первая группа входов которого соединена спервым и пятым входами блока, вторая группа входов - с шестым и седьмым входамиблока, третья группа входов - с четвертыми шестым входами блока, четвертая группавходов - с первым, третьим и седьмым входами блока, пятая группа входов - со вторым, третьим, пятым и седьмым входами блока, выход элемента И - ИЛИ - НЕ подключенк прямому выходу блока, а через элементНЕ - к инверсному выходу блока. Блок формирования третьего разряда суммы содержйтэлемент И - ИЛИ - НЕ, первая группа входовкоторого соединена с четвертым и шестымвходами блока, вторая группа входов - с первым и четвертым входами блока, третья группа входов - со вторым, третьим и шестымвходами блока, выход элемента И - ИЛИ - НЕсоединен с выходом блока,Блок формирования четвертого разряда суммы содержит элемент И - ИЛИ - НЕ, перваягруппа входов которого соединена с третьими четвертым входами блока, вторая группавходов - со вторым и четвертым входамиблока, третья группа входов в : с первым ипятым входами блока, выход элементаИ - ИЛИ - НЕ соединен с выходом блока.На фиг. 1 представлено устройство длясуммирования двоично-десятичных кодов, блоксхема; фиг. 2 - 3 - то же, принципиальнаясхема. Устройство содержит трехразрядный двойчный сумматор 1 состоящий из трех последовательно соединенных одноразрядных двоич. ных сумматоров 2 - 4, блоки 5 - 7 формирования второго, третьего и четвертого разрядов суммы, блок 8 формирования подготовитель.691851 Выходной сигнал цг сумматора 1 поступает на вход блока формирования десятичного переноса, на вход блока формирования четвертого разряда суммы 7 и на вход одноразряд. ного двоичного сумматора 3. Выходной сигнал Ч поступает также на вход элемента НЕ 16, выходной сигнал которого представляет собой сигнал 8, младшего разряда двоично-десятичной суммы, т.е, один из выходов устройства,р крме того, подан сигнал цг, СфоРмиРованный Входные сигналы старших двоичных разрядовна одноразрядном сумматоре изсигнала Юсод-слагаемых аг, Ьг, аз, Ьз, а 4, Ь 4 ПостУпают на блокного переноса ц 1 и входных сигналов мщд. 8 формирования подготовительных функция,щего двоичного разряд а 1, Ь. При этом выходные сигналы которого представляютсяННЛ Ле ревлизуеея элеменем И - ИЛИ - НЕ 4 еырмкеннямн10Щ ЪЬ:ц.р ц щВйходной, сигнал блока формирования десятич- а 4 = а 4 чЬ 4 Р 4 - а 4 Ь 4ного переноса образуется элементом И - ИЛИ - НЕ 50Выходные сигналы блока 8 формирования28 и определяется выражениемОыходныо сигналь иРподготовительных функций поступают на блокц 1 оа 4 азч 7 цгч 7 Р 2 а 4 агсгчР 4 азагцг 12, который образует выходной сигнал ц 1 овидаПри этом время формирования сигнала ц 1 оменьше или равно тз, Многократное использо. 55ванне выше. перечисленных сигналов подгото- Выходньвигельных функвий позволяет уменьшить ния пообъем аппаратуры за счет введения новых свя же на в а 4 азч 7 цгч 7 Ргча 4 агцг рР 4 азагцг се сигналы аг Рг блока 8 формировадготовительных функций поступают так ход одноразрядного сумматора 3, вы,ных функций и блок 9 формирования деся.тичного переноса,Одноразрядные двоичные сумматоры 2.4 мо.гут быть реализованы, например, как показа.но на фиг, 2, 3 и элементах И - ИЛИ - НЕ 10- 5,15 и элементах НЕ 16 - 18,Блоки 5 - 7 формирования второго, третьего и четвертого разрядов суммы и содержат элементы И-ИЛИ - НЕ 19 - 21.Блок 8 формирования. подготовйтельньтхфункций содержит элементы И - ИЛИ-НВ 22- 25 и элементы И - НЕ - 26 - 27,Блок 9 формйрования десятичного переноса содержит элемент И-ИЛИ - НЕ 28 и элемент НЕ 29.Поставленная цель достигается тем, что мо. мент начала формировеания сигнала выходного (десятичного) переноса определяется моментом прихода сигнала входного переноса; при этом сокращается время формирования сигнала десятичного переноса (ц 1 о), С этой целью блок 8 формирования подготовительных функций использует входные сигналы трех старших двоичньпс разрядои (аг, Ь 2, аз. Ьз а 4, Ь 4) 25 для реализации следующих логических функцийЙг а 2 Ч Ь 2 . Р 2 а 2 Ьг30аз "азЧЬз 7 = е 4 чЬ 4 чазЬза 4 а 4 чЬ 4Р 4 = е 4 Ь 4. Эта реализация осуществляется с помощьв элементов И - НЕ 26 - 27 и И - ИЛИ - НЕ 22 - 25. Время формирования сигналов, представляющих собой вышеуказанные подгптовнтельные функ- З 5 ции, не превышает задержки (т,) в элементе И - ИЛИ - НЕ. Выходные сигналы блока 8 формирования подготовительных, функций аг аза 4 Рг 72 Р 4 подаются на блок 9 формирования десятичного пе еноса, на кото ый, о эей, С этой целью выходные сигналы аг, Р,блока 8 формирования подготовительных функций поступают также на два соответствующихвхода второго разряда двоичного сумматора 1,а два других выходных сигнала а 4, Р 4 поступают на два соответствующих входа блока фор мирования четвертого разряда суммы 7. Крометого, на остальные входы укаэанного блокапоступают также сигналы цг с выхода, первогоразряда двончного сумматора 1, ц 4 с выходатретьего разряда и сигнал десятичного переноса ц 1 о При этом выходной сигнал 84 блокаформирования четвертого разряда двоично.десятичной суъ 4 мы реализует логическую операцию84 - цг ц оЧцг оР 4 Ч ц 4 а 4Устройство работает следующим образом,На одноразрядный сумматор 2 поступаютсигналы младшего двоичного разряда а 1 Ь 1 исигнал входного переноса ц, с выхода преды.дущего десятичного разряда. Сумматор 1 формирует сигцал отрицания разрядной суммы (Ч,)и сигнал отрицания входного переноса (ц,)в соответствии с выражениямицг ц 1 аЧц, Ь,Ч а 1 Ь,7, а 1 Ьц 1 ч цга 1 ч цгЬ ч саксо69 4550 ходные сигналы сумматора 3 представляютсявыражениями.ЧЭ 92 Чф 2 Ч 2Ч 2 - СЬЧзЧ 02 ЧзЧ ф 2 ц 2Выходной сигнал поступает на одноразрядный сумматор 4, на который поданы такжевходные сИгналы аэЬ 2, Выходные сигналы 14,Ч 2 сумматора 4 представляются выражени, ямиЧэ = аэ Ьз Цэч ча азЧ Ча Ьзч ча ЦзВыходной сигнал с поступает на вход блока формирования четвертого разряда суммы 7,а сигнал 72 поступает на вход элементаНЕ 18 и блок формирования третьего разряда суммы 6. Выходной сигнал Ч 2 с выхода:элемента НЕ 18 подается также на блок формирования третьего разряда суммы 6. Выходной сигнал сумматора 3 Ч 2 поступает на входэлемента НЕ 17 и на входы блоков формирования второго и третьего разрядов суммы5 и 6. Сигнал Ч 2 с выхода элемента НЕ 17также подается на входы этих блоков.Выходные сигналы а Ра блока 8 формирования подготовительных функций поступаюттакже непосредственно на вход блока формирования четвертого разряда суммы 7. Выходные сигналы 82. Зз. 84 блоков формирования второго, третьего и четвертого разрядовсуммы 5 - 7 являются выходными сигналамиустройства так же,как и Яи представляютсявыражениями .8, - чз = ч,оз = ЧзоЗзочЧзоЗзояо = чзоЗзоч чзчзччззззоЗзо84 - ц 2 Ч 1 очЧ 1 о 54 ч чайаИспользование изобретения позволяет повы,сить быстродеййвие многоразрядных десятич.ныхсумматоров и уменьшить объем требуемого. оборудования. Сравнительный анализ по.казал, что реализация предлагаемого устройства позволяет сократить время задержки формирования сигнала десятичного переноса неменее, чем в 2,5 раза и не превышает 2 тзгде тэ - время задержки в одном логическом элеметтте И - ИЛИ - НЕ,формула изобретения 1. Устройство для суммирования двоично. десятичных кодов, содержащее трехразрядный двоичный сумматор, входы первого разряда которого подключены к входам первых раэ 185151015ходы подключены соответственно к первому 8рядов операндбв и входу переноса устройст ва, а прямой выход подключен к первому разряду выхода суммы устройства, входы третьего разряда подключены к входам третьих разрядов операндов, блок формирования подготовительных функций, блок формирования десятичного переноса и блоки формирования второго, третьего и четвертого разрядов суммы, выходы которых соединены соответствен. но со вторым, третьим и четвертым разряда. ,ми выхода суммы устройства, первый, второй,третий, четвертый, пятый и шестой входыблока, формирования подготовительных функций соединены со входами соответственно вторых, третьих и четвертых разрядов первогои второго операндов, а первый и второй выи второму входам блока формирования десятичного переноса, прямой выход которого сое.20 динен с выходом переноса устройства, и блокаформирования четвертого разряда суммы, входы блока формирования второго разряда сум.мы" соединены С" прямыми и инверсными выходами второго разряда трехразрядного двоичного сумматора и блока формирования десятичного переноса, первый и второй входыблока формирования третьего разряда суммысоединены с прямыми выходами второго итретьего разрядов трехразрядного двоичногосумматора, инверсный выход второго разрядакоторого соединен с третьим входом блокаформирования третьего разряда суммы, инверсный выход блока формирования десятичногойереноса подключен к четвертому входу блокаформирования третьего разряда суммы, о т.л и ч а ю щ е е с я тем, что, с целью повышениябыстродействия устройства, третий, четвертый, пятый и шестой выходы блока формирования подготовительных функций подключены к соответствующим входам блока формирования десятичного переноса, седьмой входкоторого соединен с инверсным выходом переноса первого разряда трехразрядного двоич.ного сумматора, который соединен также стретьим входом блока формирования четвертого разряда суммы, четвертый вход которогоподключен к прямому выходу блока форми.рования десятичного переноса и пятым входомблока формирования третьего разряда суммы,шестой вход которого подключен к инверсному выходу третьего разряда трехразрядного двоичного сумматора, инверсный выход пере.носа которого соединен с пятым вхопом блокаформирования четвертого разряда суммы, третий и четвертый выходы блока формированияподготовительных функций подключены к вхо.дам второго разряда трехразрядного двоичногосумматора.691851 2, Устройство для суммирования двоичнодесятичных кодов по п. 1, о т л и ч а ю .ще е с я тем, что блок формирования под. готовительных функций содержит четыре эле.мента И - ИЛИ - НЕ и два элемента И - НЕ, цри 5 ,чем первый и второй входы блока соединены со входами первого элемента И - НЕ и соответственно с первой и второй группами входов первого элемента И - ИЛИ-НЕ, третий и четвертый входы блока соедииены соответствен 0 но с первой и. второй группами входов второго элемента И - ИЛИ-НЕ, пятый и шестой . входы блока соединены со входами второго элемента И - НЕ и соответственно с первой и второй группами входов третьего й четвертого элементов И - ИЛИ - НЕ, третья группа вхо дов четвертого элемента И - ИЛИ - НЕ соедийе. на с третьим и четвертым входами блока, выходы третьего элемента И - ИЛИ - НЕ и второго элемента И - НЕ соединены соответственно с первым и вторым выходами блока, а выходы первого элемейта И - ИЛИ - НЕ, первого элеьента И-НЕ, второго и четвертого элементов И - ИЛИ - НЕ подключены соответственно к третьему, четвертому, пятому и шестому выходам блока.3. Устройство для суммирования двоичиодесятичных кодов по п. 1, о т л й ч а ю.щ е е с я тем, что блок форьйфовайия десятичного переноса содержит элемент НЕ и эле 30 мент И - ИЛИ - НЕ, первая группа входов которого соединена с йервым и пятым входами блока, вторая группа входов - с шестым и седьмым входами блока и третья группа входов - с четвертым и шестым входами блока, четвер.,з тая группа входов - с первым, третьйм й седЬ- мым входами блока, пятая группа входов - со вторым, третьим, пятым и еедьмым входами 1 Облока, выход элемента И - ИЛИ - НЕ подключенк прямому выходу блока, а через элементНЕ - к инверсному выходу блока.4, Устройство для суммирования двоично.десятичных кодов по п, 1, о т л и ч а ю.щ е е с я тем, что блок формироваия третье го разряда суМмы содержит элемент И - ИЛИ - НЕ,первая группа входов которого соединена счетвертым и шестым входами блока, втораягруппа входов - с первым и четвертым входами блока, третья грутша входов - со вторым,третьим и шестым входами блока, выход элемента И - ИЛИ - НЕ соединен с выходом блока.5, Устройство для суммирования двоичнодесятичных кодов по п. 1, о т л и ч а ющ е е с я тем, что блок формирования четвертого разряда суммы содержит элементИ-ИЛИ-НЕ, первая группа входов которогосоединена с третьим и четвертым входами блока, вторая группа входов - со вторым и четвертым входами блока, третья группа входов -с первым и пятым входами блока, выходэлемента И - ИЛИ - НЕ.соединен с выходомблока.Источники информации,принятые во внимание при экспертизе 1. Карцев М. А, Арифметика цифровых ма.шин, М "Наука", 1969, с, 168,2, Агравал, Ускоренное сложение двоичнодесятйчных чисел, - "Электроника", У 23,1976, с. 56.3. Карцев М А. Арифметика цифровых ма.шин. М фНаука", 1969, с. 195,4. Сергеев Н, П. и др., Повышение быстродействия цепей переноса в десятичных сумматорах для кода 8421, Известия вузов, сер. Приборостроение, У 5, 1974, с. 65,691851 а,оставитель ехред Л,Лд рез Корректор т Скворцова дак каков 39 писное Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 ираж 780И Государственного делам изобретений и Москва, Ж - 35, Рауш итета ССкрытийая наб., д,1ИЗ

СмотретьЗаявка

2406473, 27.09.1976

ПРЕДПРИЯТИЕ ПЯ В-2431

ПУХОВ ГЕОРГИЙ ЕВГЕНЬЕВИЧ, СИНЬКОВ МИХАИЛ ВИКТОРОВИЧ, ЗАКИДАЛЬСКИЙ АНАТОЛИЙ ИВАНОВИЧ, ВЛАДИМИРОВ ВАСИЛИЙ АЛЕКСАНДРОВИЧ, РЯБИНИН ЮРИЙ МИХАЙЛОВИЧ, ГАБЕЛКО ВЛАДИМИР КИРИЛЛОВИЧ, НИФОНТОВ НИКОЛАЙ БОРИСОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: двоично-десятичных, кодов, суммирования

Опубликовано: 15.10.1979

Код ссылки

<a href="https://patents.su/8-691851-ustrojjstvo-dlya-summirovaniya-dvoichno-desyatichnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования двоично-десятичных кодов</a>

Предыдущий патент: Накапливающий сумматор

Следующий патент: Частотно-импульсное множительноделительное устройство

Случайный патент: Разделительная горка карфофелеуборочного комбайна