Процессор для мультипроцессорной системы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1688252

Авторы: Белицкий, Городецкий, Дряпак, Зайончковский, Носова, Палагин

Текст

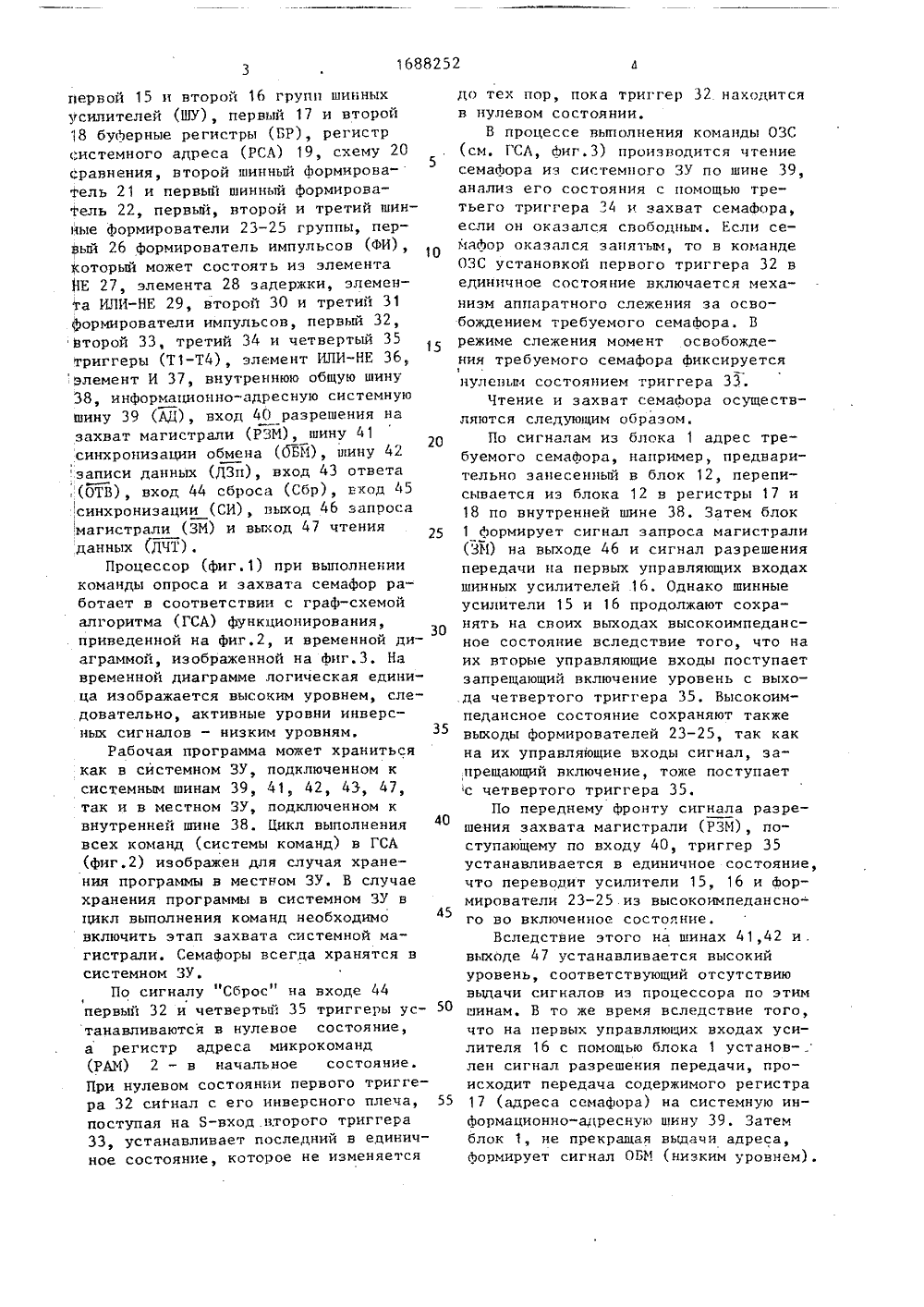

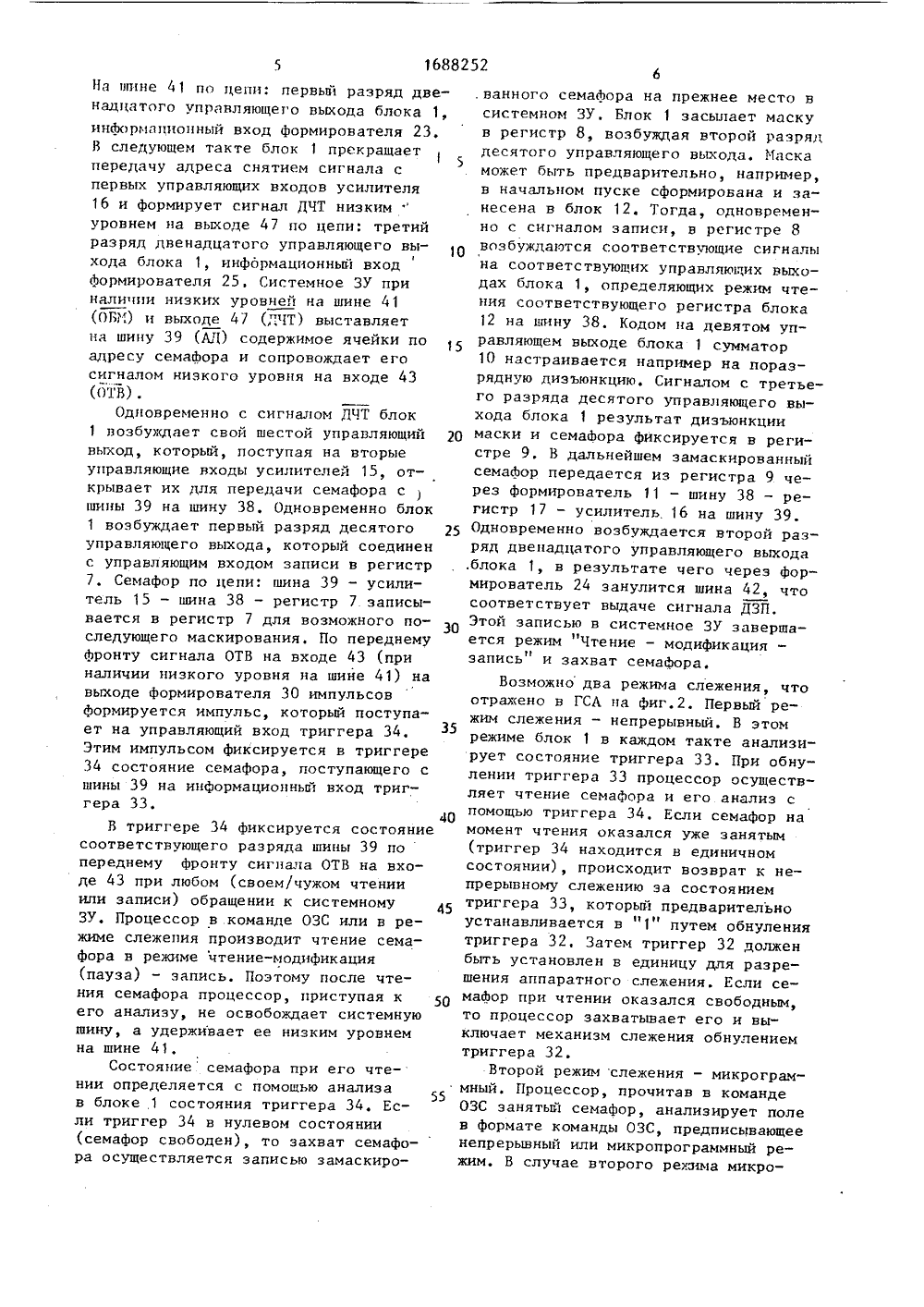

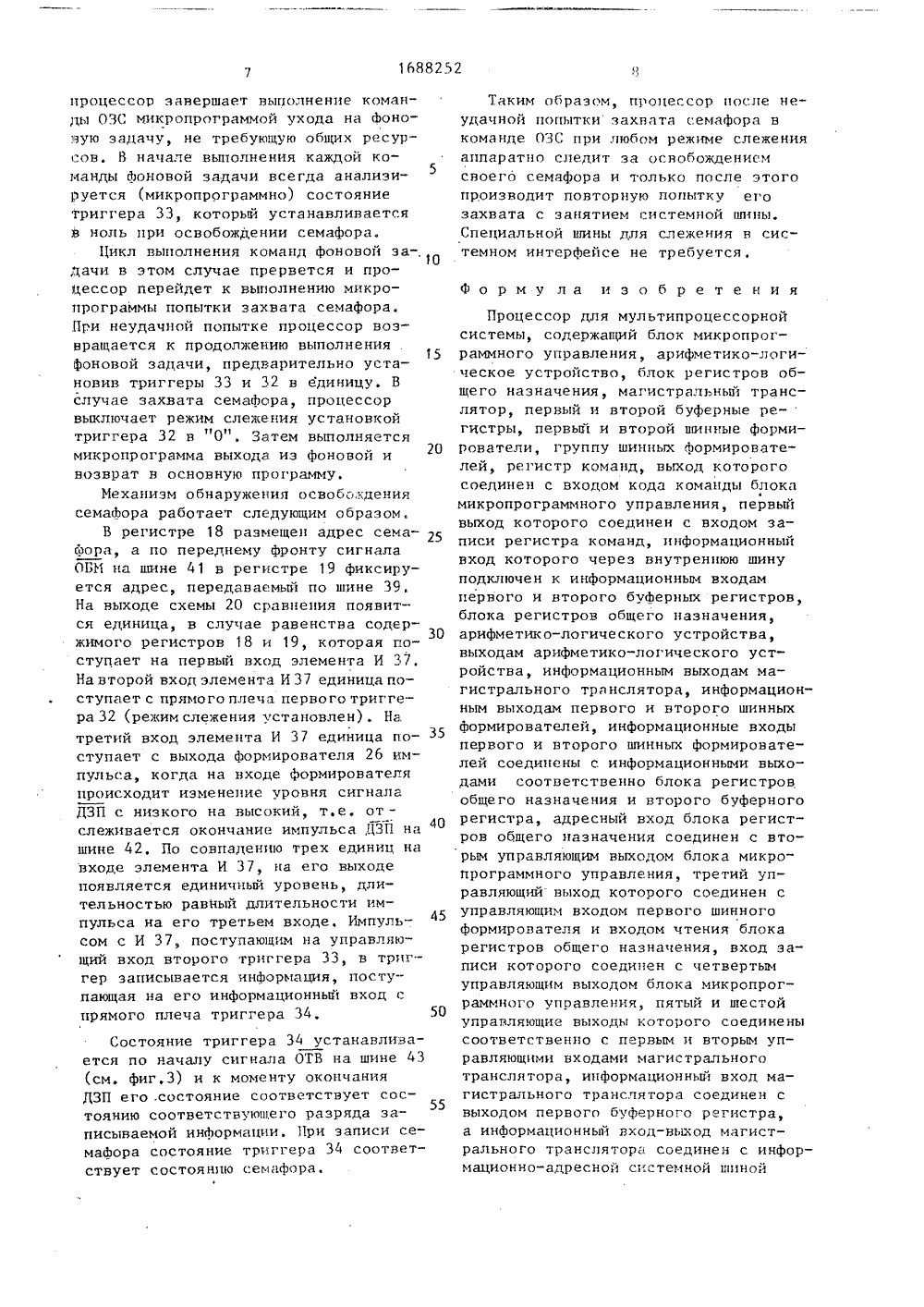

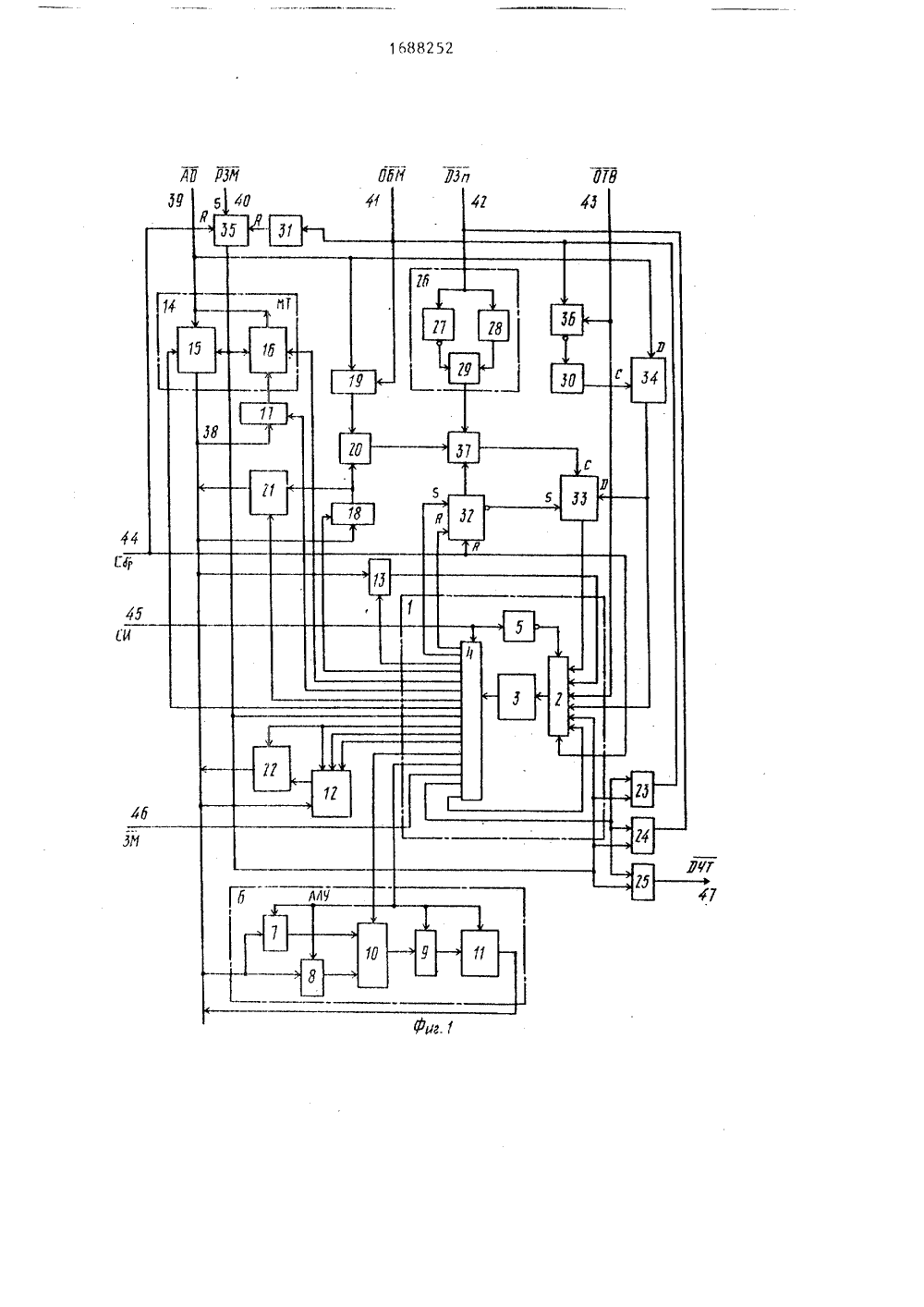

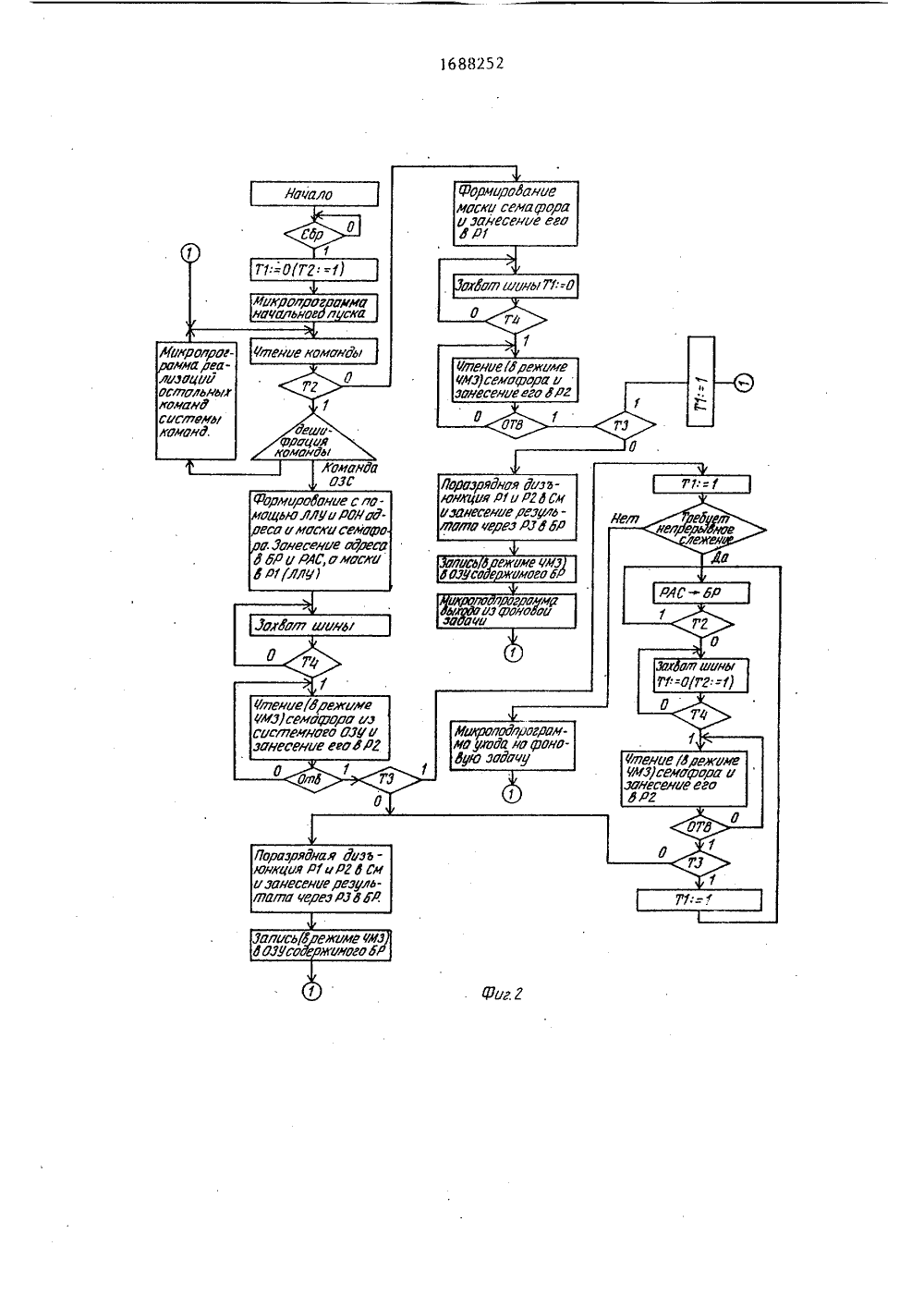

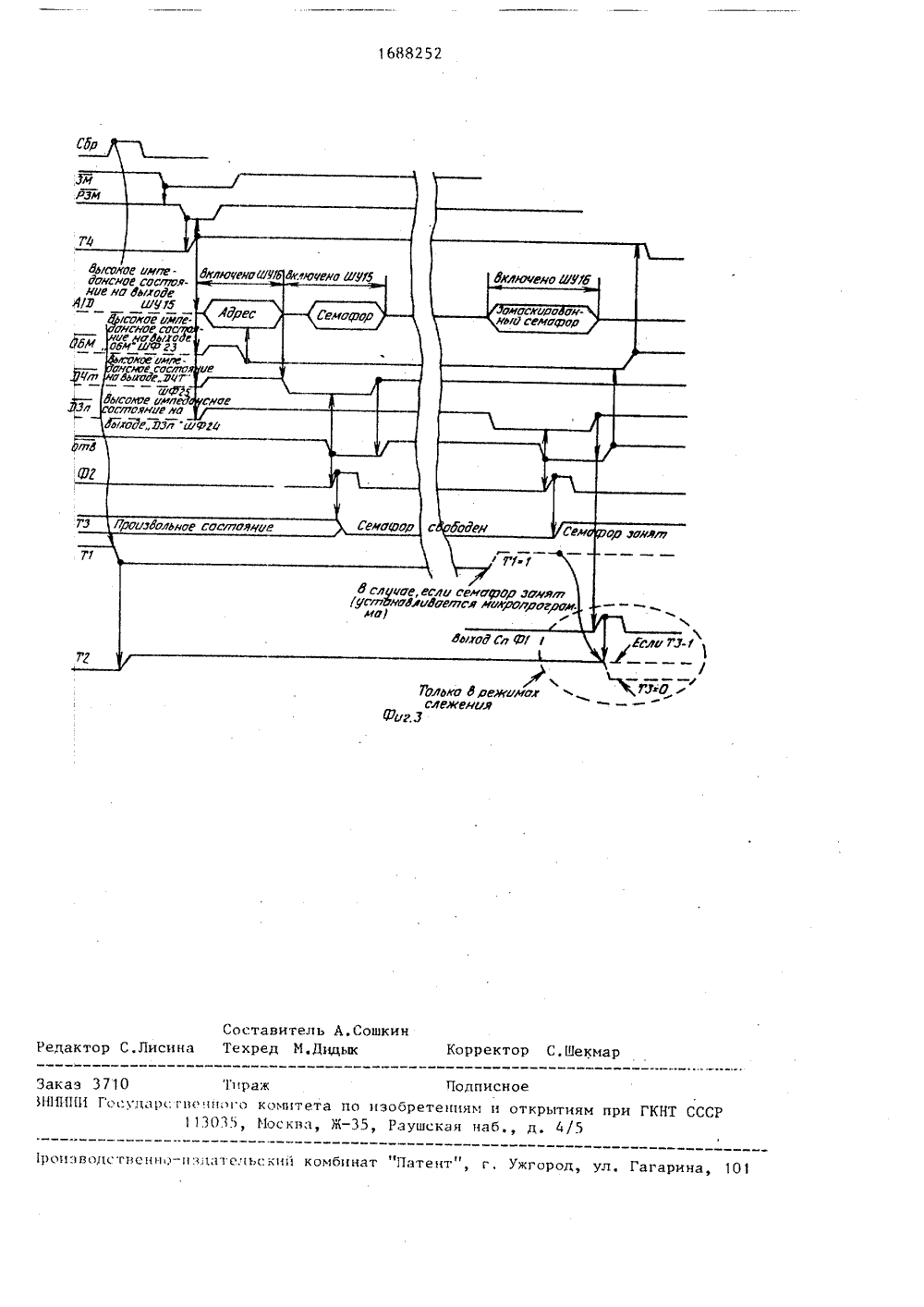

,а а а ИСАЙИ БРЕТЕНИЯ ВТСРСНОМУ СВ ЛЬСТ 2магистраль для доступа к общим ресурсам системы, или в однопроцессорных системах, работающих в мультипрограммном режиме. Цель изобретения - повышение быстродействия. Для этого процессор содержит блок микропрограммного управления, арифметико-логическое устройство, регистр команд, магистральный транслятор, буферные регистры, регистр системного адреса, схему сравнения, два шинных формирователя, группу шинных формирователей, три формирователя импульсов, четыре триггера, элемент ИЛИ-НЕ и элемент И. Это позволяет процессору реализовать. возможность выполнения текущей задачи и одновременно аппаратно следить за освобождением только своего семафора, не занимая при этом системную шину и не расходуя программные вставки. электна"(57) Изобретен тельной техникработы в мультобработки данн е относится к вычислии предназначено дляпроцессорной системеи, использующей общую схема алго фиг.3 - вр Изобретение относится к вычислительной технике и предназначено для работы в мультипроцессорной системе обработки данных, использующей общуюагистраль для, доступа к общим ресур сам системы, или в однопроцессорных системах, работающих в мультипрограммном режимеЦелью изобретения является повыше ние быстродействия процессора (путем исключения повторных опросов при освобождении семафоров, управляющих другими частями общих ресурсов систе мы и уменьшение внешних управляющихсигналов процессора).На фиг. 1 изображена схема предл гаемого устройства; на фиг,2 - граф устроиства.Устройство (фиг. 1) содержит блок микропрограммного управления, который может состоять из регистра 2 адреса микрокоманд, памяти микрокоманд (П) 3, регистра микрокоманд (РГ 1 К) 4 элемента НЕ 5, арифметико-логическое устройство (АЛУ) 6, которое может состоять из первого 7, второго 8, третьего 9 регистров (Р), сумматора (См) 10, группы шинных формирователей (Шф) 11, блок регистров общего назначения (РОН) 12, регистр команд (РК) 13, магистральный транслятор (МТ) 4, который может состоять из м ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГННТ СССР(71) Ленинградское объединениронного приборостроения "Свепервой 15 и второй 16 групп шинныхусилителей (ШУ), первый 17 и второй18 буферные регистры (ВР), регистрСистемного адреса (РСА) 19, схему 220Сравнения, второй шинный формирователь 21 и первый шинный формироваТель 22, первый, второй и третий шинные формирователи 23-25 группы, первый 26 Формирователь импульсов (ФИ),Который может состоять из элементаг 1 Е 27, элемента 28 задержки, элемента ИЛИ-НЕ 29, второй 30 и третий 31Формирователи импульсов, первый 32,второй 33, третий 34 и четвертый 35триггеры (Т 1-Т 4), элемент ИЛИ-НЕ 36,элемент И 37, внутреннюю общую шину38, информационно-адресную системнуюшину 39 (АД), вход 40 разрешения назахват магистрали (РЗМ), шину 41синхронизации обмена (ОЕМ), цгину 42записи данных (ДЗп), вход 43 ответа(ОТВ), вход 44 сброса (Сбр), вход 45синхронизации (СИ), выход 46 запросамагистрали (ЗМ) и выход 47 чтенияданных (ДЧТ).Процессор (фиг.1) при выполнениикоманды опроса и захвата семафор работает в соответствии с граф-схемойалгоритма (ГСА) функционирования,приведенной на фиг,2, и временной диаграммой, изображенной на фиг.3. Навременной диаграмме логическая единица изображается высоким уровнем, следовательно, активные уровни инверсных сигналов - низким уровням.Рабочая программа может хранитьсякак в системном ЗУ, подключенном ксистемным шинам 39, 41, 42, 43, 47,так и в местном ЗУ, подключенном квнутренней шине 38. Цикл выполнениявсех команд (системы команд) в ГСА(Фиг,2) изображен для случая хранения программы в местном ЗУ. В случаехранения программы в системном ЗУ вцикл выполнения команд необходимовключить этап захвата системной магистрали. СемаФоры всегда хранятся всистемном ЗУ,По сигналу "Сброс" на входе 441первый 32 и четвертый 35 триггеры устанавливаются в нулевое состояние,а регистр адреса микрокоманд(РАМ) 2 - в начальное состояние.При нулевом состоянии первого триггера 32 сигнал с его инверсного плеча,поступая на Б-вход второго триггера33, устанавливает последний в ециничное состояние, которое не изменяется до тех пор, пока триггер 32 находится в нулевом состоянии.В процессе выгголнения команды ОЗС(см. ГСА, фиг.3) производится чтение семафора из системного ЗУ по шине 39, анализ его состояния с помощью третьего триггера 34 и захват семафора, если он оказался свободным. Если семафор оказался занятым, то в команде ОЗС установкой первого триггера 32 в единичное состояние включается механизм аппаратного слежения за освобождением требуемого семаФора. Врежиме слежения момент освобождения требуемого семафора фиксируетсянулевым состоянием триггера 33.Чтение и захват семафора осуществляются следующим образом.По сигналам из блока 1 адрес требуемого семафора, например предварительно занесенный в блок 12, переписывается из блока 12 в регистры 17 и18 по внутренней шине 38, Затем блок 25 1 формирует сигнал запроса магистрали(ЗМ) на выходе 46 и сигнал разрешенияпередачи на первых управляющих входахшинных усилителей 16. Однако шинныеусилители 15 и 16 продолжают сохранять на своих выходах высокоимпедансное состояние вследствие того, что наих вторые управляющие входы поступаетзапрещающий включение уровень с выхо.да четвертого триггера 35. Высокоимпедансное состояние сохраняют такжевыходы Формирователей 23-25, так какна их управляющие входы сигнал, запрещающий включение, тоже поступаетс четвертого триггера 35.По переднему фронту сигнала разрешения захвата магистрали (РЗМ), поступающему по входу 40, триггер 35устанавливается в единичное состояние,что переводит усилители 15, 16 и Формирователи 23-25 из высокоимпедансно-го во включенное состояние.Вследствие этого на шинах 41,42 и .выходе 47 устанавливается высокийуровень, соответствующий отсутствиювыдачи сигналов из процессора по этимнинам, В то же время вследствие того,что на первых управляющих входах усилителя 16 с помощью блока 1 установлен сигнал разрешения передачи, происходит передача содержимого регистра 55 17 (адреса семафора) на системную инФормационно-адресную шину 39. Затемблок 1, не прекращая выдачи адреса,Формирует сигнал ОБМ (низким уровнем).1688252На шине 4 1 по1 п цени: первый разряд две- .ванного семафора на прежнее место внаццатого управляющего выхода блока 1, системном ЗУ. Блок 1 засылает маскуинформационный вход формирователя 23, в регистр 8, возбуждая второй разрядВ следующем такте блок 1 прекращаетдесятого управляющего выхода, Маскапередачу адреса снятием сигнала с может быть преднарительно например3 Фпервых управляющих входов усилителя в начальном пуске сформирована и эа 16 и формирует сигнал ДЧТ низким " несена в блок 12, Тогда, одновременуровнем на выходе 47 по цепи: третий но с сигналом записи, в регистре 8разряд двенадцатого управляющего вы О возбуждаются соответствующие сигналыхода блока 1, информационный вход на соответствующих управляющих выхойормирователя 25, Системное ЗУ при дах блока 1, определяющих режим чтеналичии низких уровней на шине 41 ния соответствующего регистра блока(ОБ 1) и выходе 47 (ДЧТ) выставляет 12 на шину 38. Кодом на девятом упна шину 39 (АД) содержимое ячейки по 15 равляющем выходе блока 1 сумматорадресу семайора и сопровождает его 10 настраивается например на пораэсигналом низкого уровня на входе 43 рядную дизъюнкцию. Сигналом с третье( 1 В)(ОТВ го разряда десятого управляющего выОдновременно с сигналом ДЧТ блок хода блока 1 результат диэъюнкции1 возбуждает свой шестой управляющий 2 О маски и семафора фиксируется в региныход, который, поступая на вторые стре 9. В дальнейшем замаскированныйуправляющие входы усилителей 15, от- семафор передается из регистра 9 чекрывает их для передачи семафора с ) Рез формирователь 11 - шину 38 - решины 39 на шину 38. Одновременно блок гистр 17 - усилитель, 16 на шину 39.1 возбуждает первый разряд десятого 25 Одновременно возбуждается второй разуправляющего выхода, который соединен Ряд двенадцатого управляющего выходас управляющим входом записи в регистр ,блока 1, в результате чего через фор 7, Семафор по цепи: шина 39 - усили- мирователь 24 эанулится шина 42 чтчтотель 15 - шина 38 - регистр 7 записы- соответствует выдаче сигнала ДЗП.нается в регистр 7 для возможного по О Этой записью в системное ЗУ эавершаследующего маскирования. По переднему ется режимЧтение - модификация -йронту сигнала ОТВ на входе 43 (при запись" и захват семафора,наличии низкого уровня на шине 41) на Возможнозможно два режима слежения, чтовыходе Формирователя 30 импульсов отражено в ГСАотражено в А на фиг,2. Первый реФормируетсЯ импУльс, который поступа- жим слежени - н " Вжим слежения - непрерывный. В этомет на управляющий вход триггера 34.режиме блок 1 н кажн каждом такте анализиЭтим импульсом фиксируется в триггере рует состояние триггера 33. При обну 34 состояние семафора, поступающего с лении триггера 33 процессор осуществшины 39 на информационный вход триг- ляет чтение семафора и его анализ сгера 33. помощью триггера 34, Если семафор наВ триггере 34 фиксируется состояние момент чтения оказался уже занятымсоответствующего разряда шины 39 по(триггер 34 находится в единичномпереднему фронту сигнала ОТВ на вхо- состоянии), происходит возврат к неде 43 при любом (своем/чужом чтении прерывному слежению эа состояниемили записи) обращении к системному 45 триггера 33, который предварительноЗУ. Процессор в команде ОЗС или в ре- Устанавливается в "1" путем обнуленияжиме слежения производит чтение сема- триггера 32, Затем триггер 32 долженфора н режиме чтение-модификация быть установлен в единицу для разре(пауза) - запись. Поэтому после чте- шения аппаратного слежения. Если сения семафора процессор, приступая к 50 майор при чтении оказался свободным,его анализу, не освобождает системную то процессор захватывает его и вышину, а удерживает ее низким уровнем ключает механизм слежения обнулениемна шине 41, триггера 32,Состояние семафора при его чте- Второй режим слежения - микрограмнии определяется с помощью анализа мный. Процессор, прочитав в командев локе 1 состояния триггера 34, Ес- ОЗС эанятьи семафор, анализирует полеб55ли триггер 34 в нулевом состоянии в фоРмате команды ОЗС, предписывающее(семафор свободен), то захват семафо- непрерывный или микропрограммный рера осуществляется записью эамаскиро- жим. В случае второго реюпча микро 1688252процессор завершает выполнение команды ОЗС микропрограммой ухода ня фоновую задачу, не требующую общих ресурсов. В начале выполнения каждой команды фоновой задачи всегда анализи 5 Руется (микропрограммно) состояние триггера 33, который устанавливается В ноль при освобождении семафора.Пикл выполнения команд фоновой за-, Дачи в этом случае прервется и процессор перейдет к выполнению микропрограммы попытки захвата семафора.При неудачной попытке процессор возВращается к продолжению выполнения фоновой задачи, предварительно установив триггеры 33 и 32 в единицу. В случае захвата семафора, процессор выключает режим слежения установкой триггера 32 в "О", Заем выполняется микропрограмма выхода из фоновой и возврат в основную программу.Механизм обнаружения освобо,кдения семафора работает следующим образом.В регистре 18 размещен адрес сема Йоря, а по переднему фронту сигнала ОБИ ца шине 41 в регистре 19 фиксируется адрес, передаваемый по шине 39, На выходе схемы 20 сравнения появится единица в случае равенства содерУ30 жимого регистров 18 и 19, которая поступает на первый вход элемента И 37. На второй вход элемента И 37 единица поступает с прямого плеча первого триггера 32 (режим слежения установлен) . На.третий вход элемента И 37 единица по ступает с выхода формирователя 26 импульса, когда на входе формирователя происходит изменение уровня сигнала ЛЗП с низкого на высокий, т.е. от 40 слеживается окончание импульса ДЗП ня шине 42. По совпадению трех единиц на входе элемента И 37, ца его выходе появляется единичный уровень, длительностью равный длительности импульса на его третьем входе, Импуль 45 сом с И 37, поступающим ца управляющий вход второго триггера 33, в триггер записывается информация, поступающая на его информационный вход с прямого плеча триггера 34. 50Состояние триггера 34 устанавливается по началу сигнала ОТВ на шине 43 (см. фиг,3) и к моменту окончания ДЗП его,состояние соответствует сос 55 тоянию соответствующего разряда записываемой информации. 11 ри записи семафора состояние триггера 34 соответствует состоянию семафора. Таким образом, процессор после неудачной попытки захвата семафора в команде ОЗС при любом режиме слежения аппаратно следит за освобождением своего семафора и только после этого производит повторную попытку его захвата с занятием системной шины. Специальной шины для слежения в системном интерфейсе не требуется,Форму ла изобретенияПроцессор для мультипроцессорной системы, содержащий блок микропрограммного управления, арифметико-логическое устройство, блок регистров общего назначения, магистральный транс - лятор, первый и второй буферные регнстры, первый и второй шинные формирователи, группу шинных формирователей, регистр команд выход которого соединен с входом кода команды блока микропрограммного управления, первый выход которого соединен с входом записи регистра команд, информационный вход которого через внутреннюю шину подключен к информационным входам первого и второго буферных регистров, блока регистров общего назначения, арифметико-логического устройства, выходам арифметико-логического устройства, информационным выходам магистрального транслятора, информационным выходам первого и второго шинных формирователей, информационные входы первого и второго шинных формирователей соединены с информационными выходами соответственно блока регистров общего назначения и второго буферного регистра, адресный вход блока регистров общего назначения соединен с вторым управляющим выходом блока микропрограммного управления, третий управляющий выход которого соединен с управляющим входом первого шинного формирователя и входом чтения блока регистров общего назначения, вход записи которого соединен с четвертым управляющим выходом блока микропрограммного управления, пятый и шестой управляющие выходы которого соединены соответственно с первым и вторым управляющими входами магистрального транслятора, информационный вход магистрального транслятора соединен с выходом первого буферного регистра, а информационный вход-выход магистрального транслятора соединен с информационно-адресной системной шинойпроцессора, управляющий вход первого буферного регистра соединен с седьмым управляющим выходом блока микропрограммнбго управления, восьмой управляющий выход которого соединен с управляющим входом второго шинного формирователя, девятый и десятый управляющие выходы блока микропрограммного управления соединены соответственно . с входами кода операции и управления передачей информации арифметико-логи- ческого устройства, одиннадцатый управляющий выход блока микропрограммного управления соединен с выходом запроса магистрали процессора, двенадцатый управляющий выход блока микропрограммного управления соединен с информационными входами шинных формирователей группы, информационные вы 20 ходы первого, второго и третьего шинных формирователей группы соединены соответственно с шинами синхронизации обмена, записи данных и выходом чтения данных процессора, первый вход условий блока микропрограммного управления соединен с входом ответа процессора, тактовый вход синхронизации процессора соединен с тактовым входом блока микропрограммного управления, вход сброса которого соединен с входом сброса процессора, о т л ич а ю щ и й с я .тем, что, с целью повышения быстродействия, в него введены регистр системного адреса, схема сравнения, с первого по четвертый 35 триггеры, с первого по третий формирователи импульсов, элемент И, элемент ИЛИ-НЕ, первый вход которого подключен к шине синхронизации обмена процессора, а второй вход соединен 40 с входом ответа устройства, выход элемента ИЛИ-НЕ через второй формирователь импульсов соединен с тактовым входом третьего триггера, информационный вход которого соединен с одним 4 из разрядов информационно-адресной системной шины процессора, прямой выход третьего триггера соединен с информационным входом второго триггераи с вторым входом условий блока микропрограммного управления, третийвход условий которого соединен с прямым выходом второго триггера, входустановки в "1" которого соединен синверсным выходом первого триггера,первый вход установки в нОн первоготриггера соединен с входом сбросапроцессора, второй вход установки в"О" и вход установки в "1 н первоготриггера соединены соответственно стринадцатым и четырнадцатым управляющими выходами блока микропрограммногоуправления, прямой выход первого триггера соединен с первым входом элемента И, второй и третий входы которогосоединены соответственно с выходомсхемы сравнения и выходом первогоформирователя импульсов, выход элемента И соединен с тактовым входомвторого триггера, вход первого формирователя импульсов подключен к шинезаписи данных процессора, шина синхронизации обмена которого подключенак входу третьего формирователя импульсов и входу записи регистра системного адреса, информационный входкоторого соединен с информационно-адресной системной шиной процессора,выход регистра системного адреса соединен с первым входом схемы сравнения, второй вход которой соединен свыходом второго буферного регистра,выход третьего формирователя импульсов соединен с первым входом установки в "0" четвертого триггера, второйвход установки в 0 и вход установки в ".1" четвертого триггера соединены соответственно с входом сброса ивходом разрешения на захват магистрали процессора, прямой выход четвертого триггера соединен с третьим управляющим входом магистрального транслятора с управляющими входами шинныхформирователей группы и четвертым входом условий блока микропрограммного,управления.T1=1 ЛЕ-бр тг0 Фикропрог- ммареалоллий остальных команд системы команд. микропрограмма начальноеОл ска Чтение команды Формирование с ломяцью Пти ОСНад. реса имаскц семаго а, 2 анесение офеса б бр и РАЕ, о москиР 1(ЯЛу) Задаат швы Чп 7 ение(брежиме ЧМ 4 семацора из гостемнаго ОЗу и занесение ееабРЕ И аб тю1О Поразрядная Жаьюнкцоя Р 1 цр 20 См и занесение резульщаща через РЗб бР,Запись(брежомР чмз 603 усобе жииого бр Рорвробаниемоски семарораи занесение егобр 1 агап шины т 1:=0 Чп 1 еиие(б режиме ЧИЗ)семафора и занесениеегобрг(1 оразрядноя битьюнпря Р 1 и Р 26 см изанегение резульл 1 ааа через р.7 б БР яись брюкве чу003 УсОЙ омого 6 адюю паогроммампйоизцюногоизааачи Иш 9 опобпрогРоммаудВа но ранофю задачиЛи алисины т 1=а(тг:=1) Чтение(бремиме УмЗ)семафора и занесшие его юря ая тГ1688252 а Составитель А.СощкинЛисина Техред М.Дидык ктор С.Шекь едак Чодп 1 раж е крытиям при ГКНТ ССС ого комцтета по изобретениям и 35, Москва, Ж, Раушская наб/5 роцзводствонно - изиатечьскиц комбинат "Патент", г. Ужгоро Гагарина, 10 Заказ 3710 ЗНМ 1 ПИ Государе гвен 113(

СмотретьЗаявка

4751307, 19.10.1989

ЛЕНИНГРАДСКОЕ ОБЪЕДИНЕНИЕ ЭЛЕКТРОННОГО ПРИБОРОСТРОЕНИЯ "СВЕТЛАНА"

ДРЯПАК АНАТОЛИЙ ФЕДОРОВИЧ, НОСОВА ЕЛЕНА НИКОЛАЕВНА, БЕЛИЦКИЙ РОБЕРТ ИЗРАИЛЕВИЧ, ПАЛАГИН АЛЕКСАНДР ВАСИЛЬЕВИЧ, ЗАЙОНЧКОВСКИЙ АНАТОЛИЙ ИОСИФОВИЧ, ГОРОДЕЦКИЙ ВАЛЕРИЙ ВИКТОРОВИЧ

МПК / Метки

МПК: G06F 13/36, G06F 15/00, G06F 15/78

Метки: мультипроцессорной, процессор, системы

Опубликовано: 30.10.1991

Код ссылки

<a href="https://patents.su/8-1688252-processor-dlya-multiprocessornojj-sistemy.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для мультипроцессорной системы</a>

Предыдущий патент: Многоканальное устройство для подключения абонентов к общей магистрали

Следующий патент: Устройство для реализации подстановок слов

Случайный патент: Способ измерения переходного сопротивления