Синтезатор сигналов с заданным законом изменения фазы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

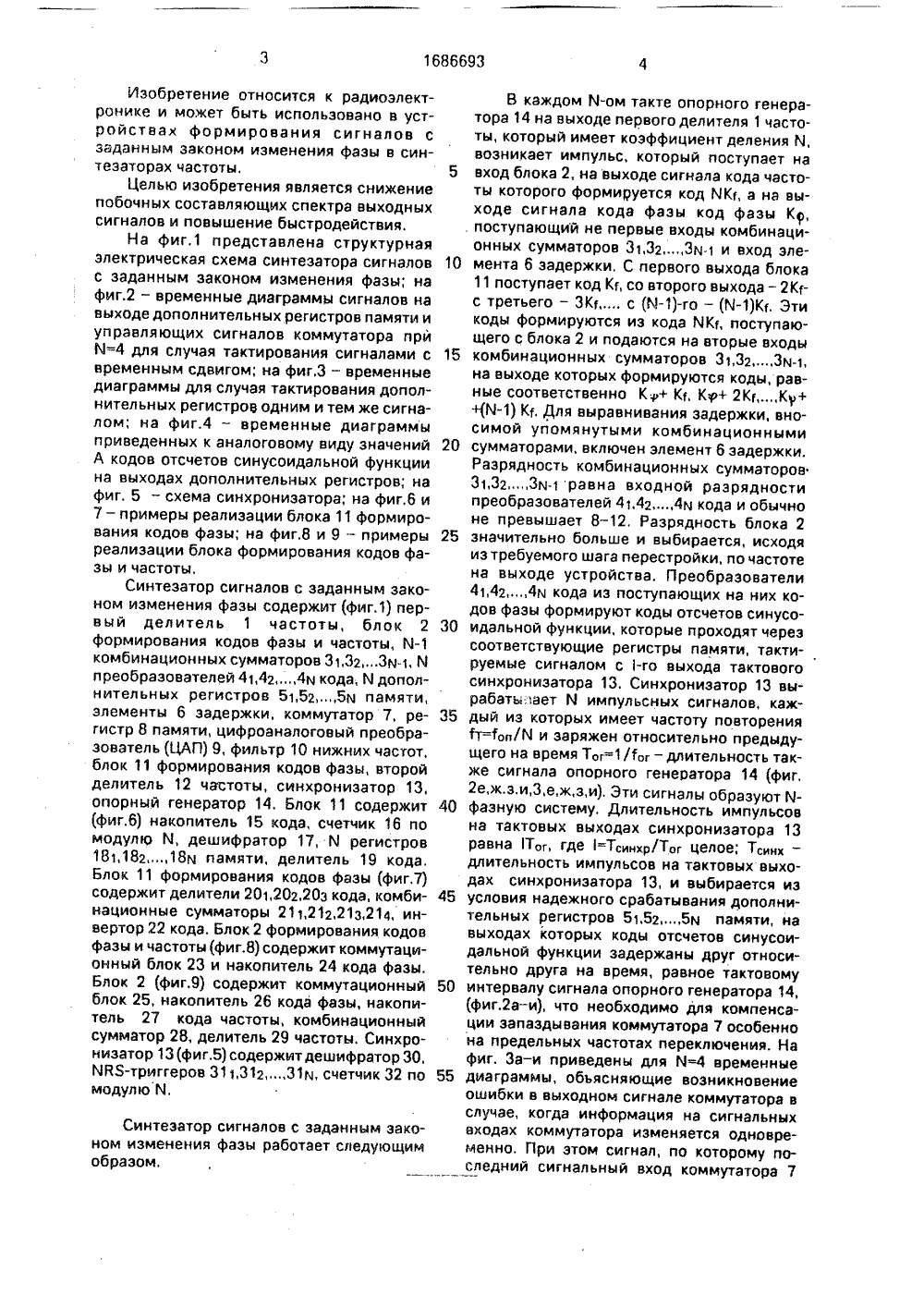

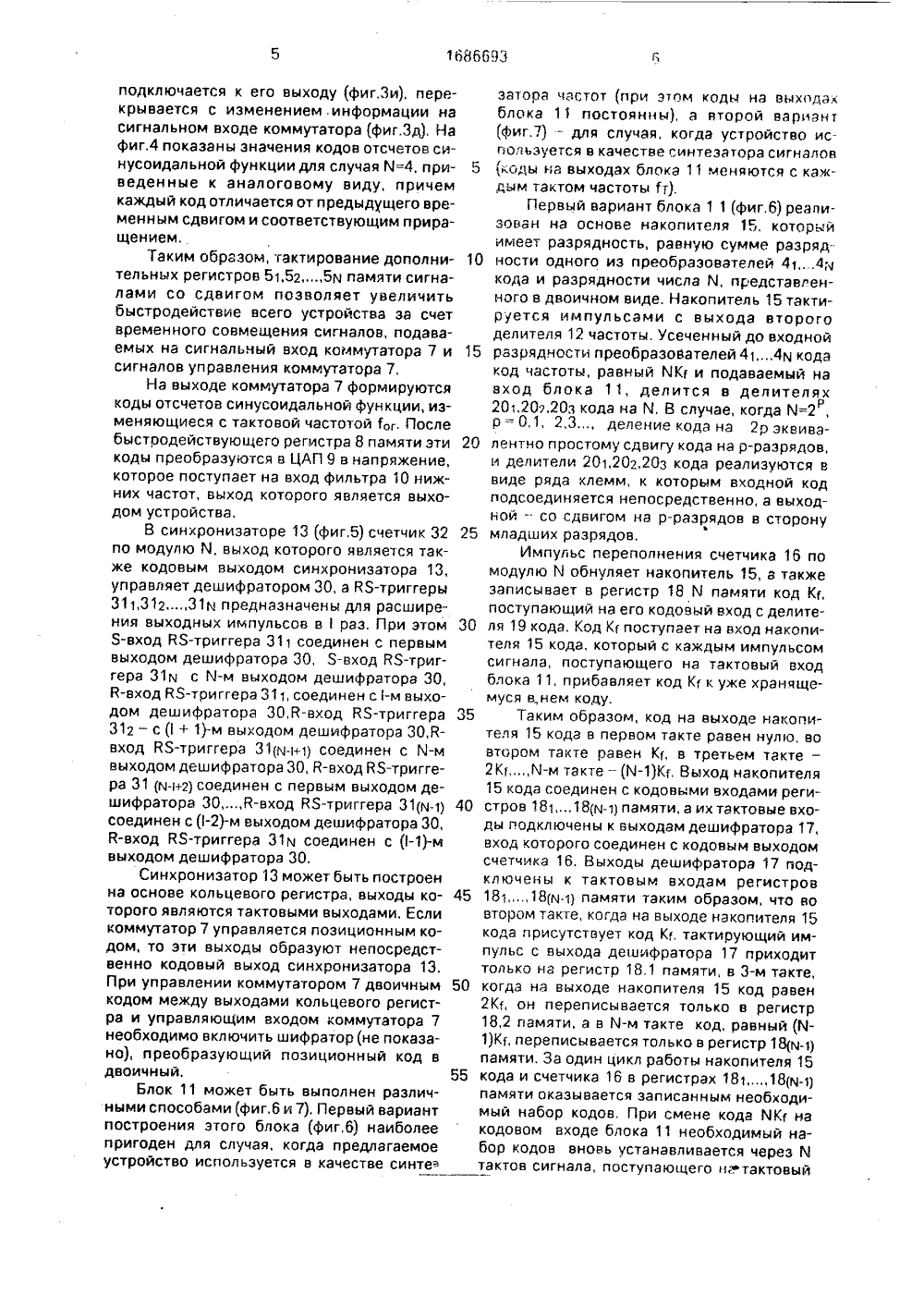

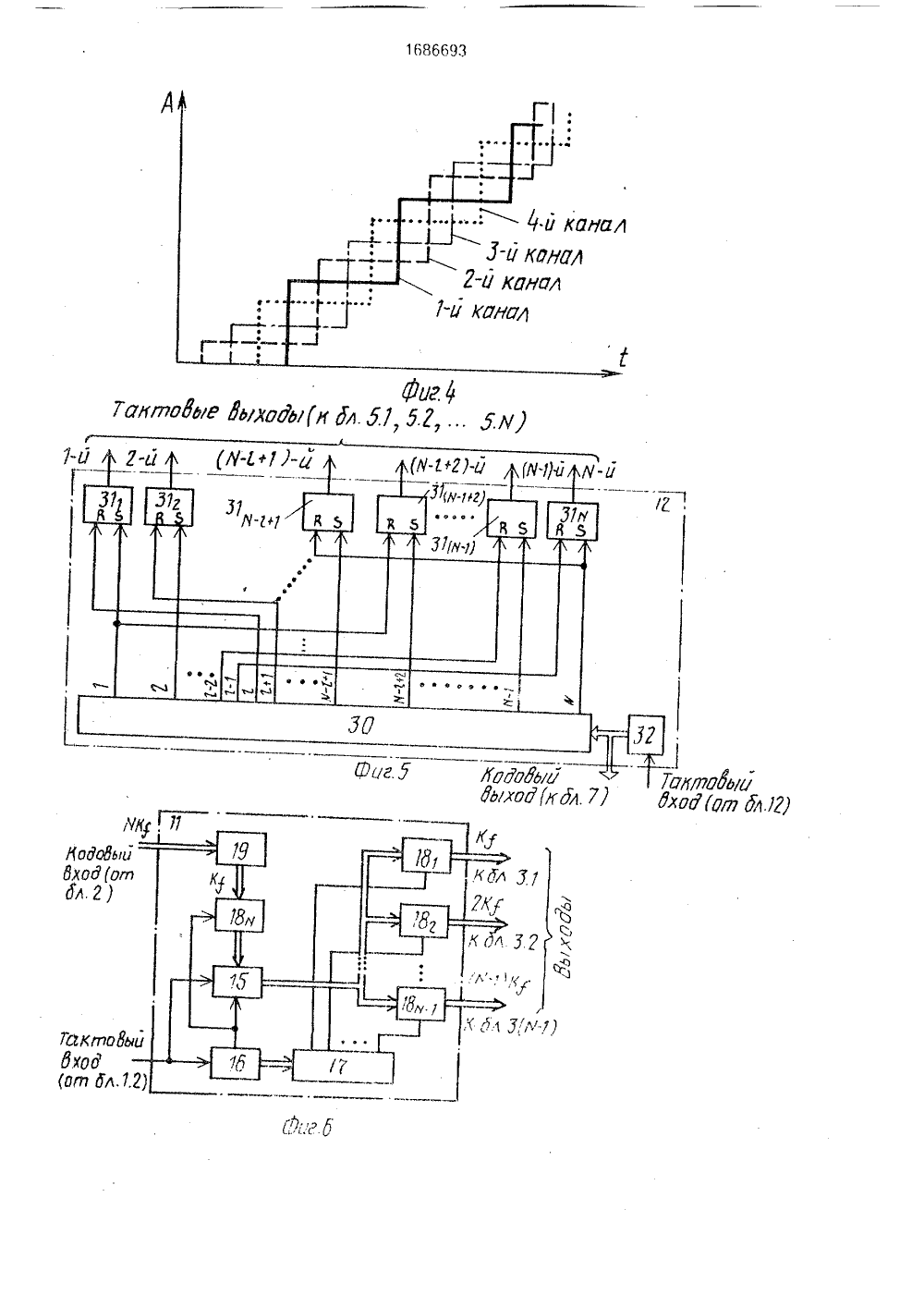

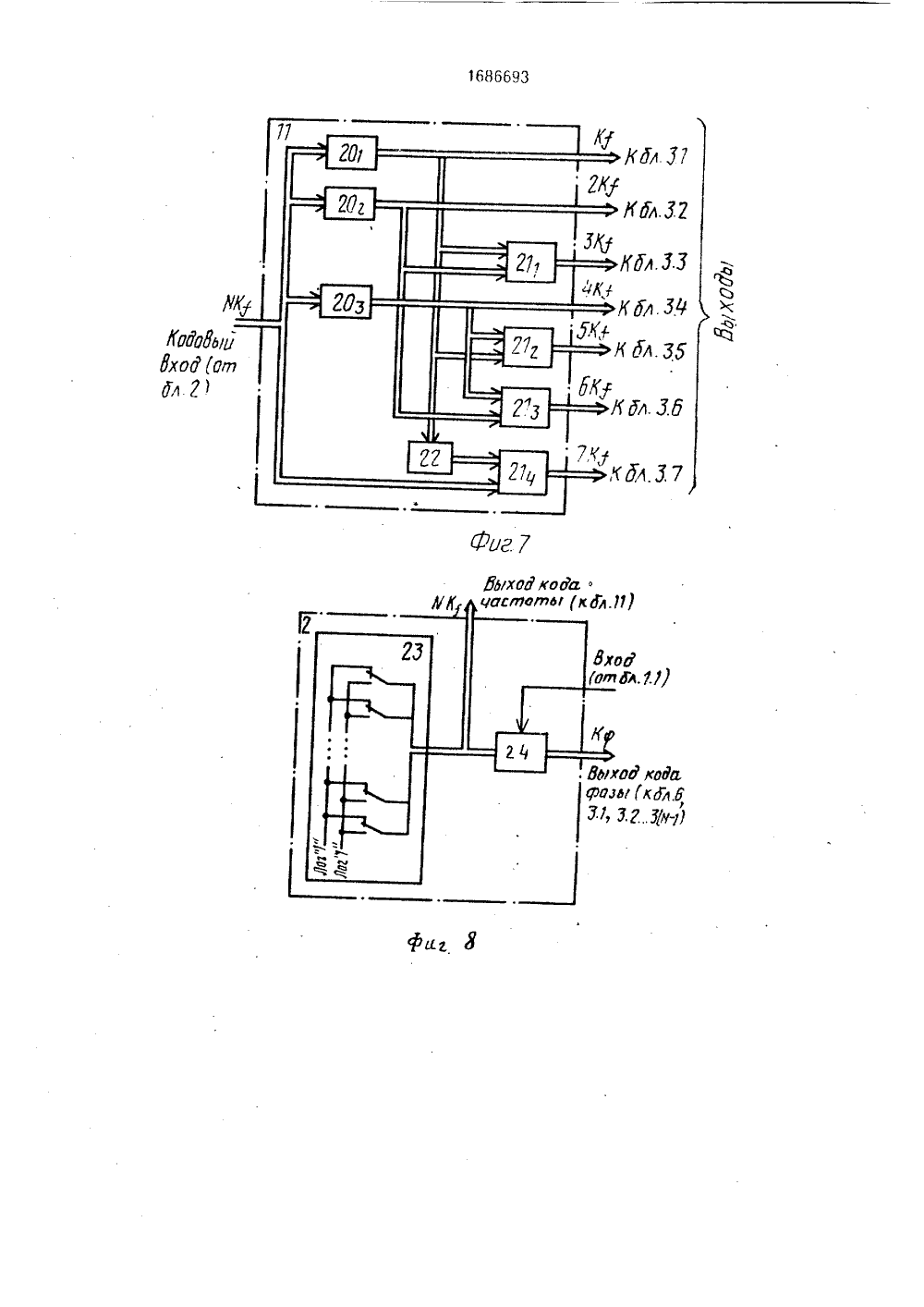

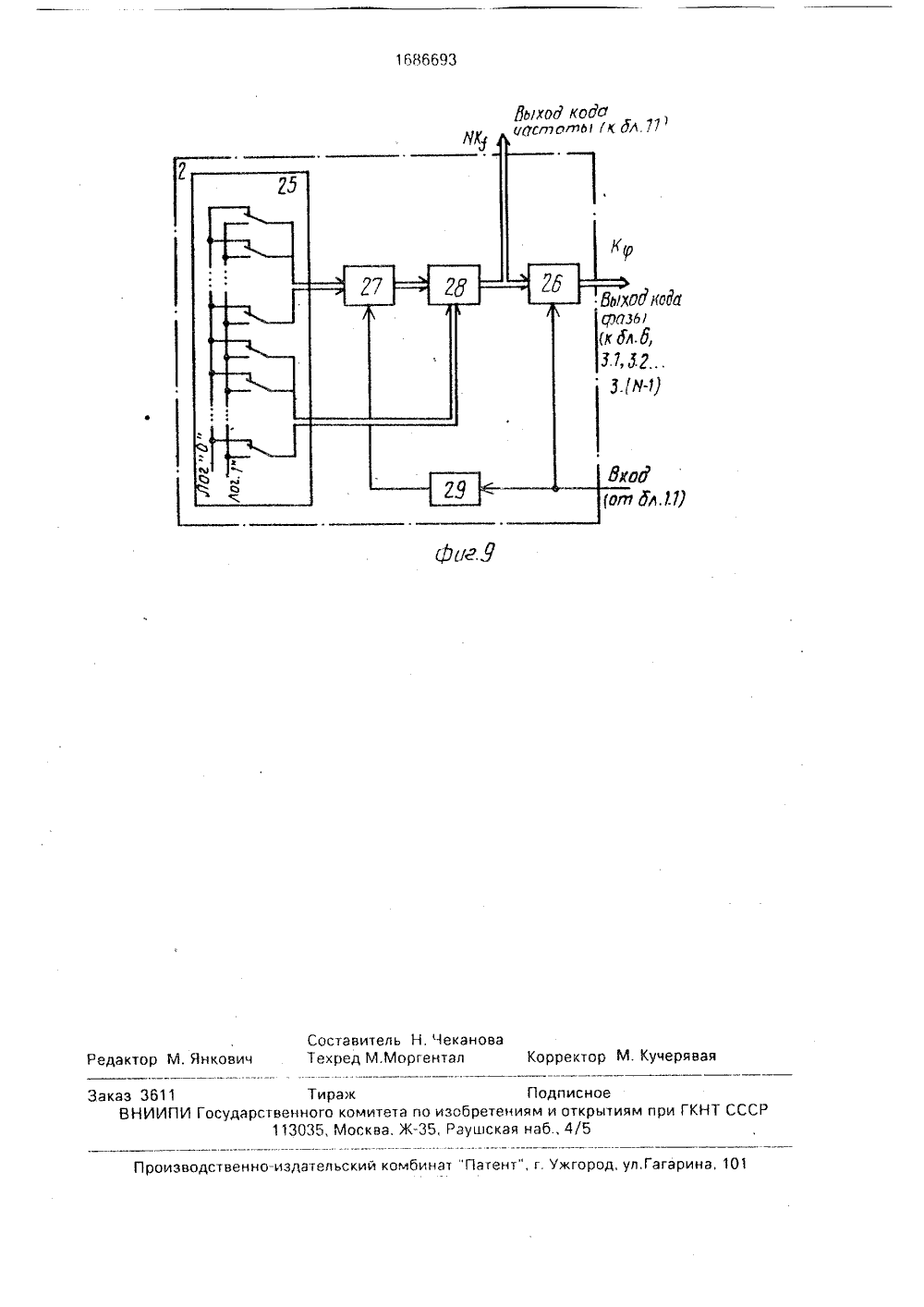

.Кочемасов и В.П.Буд ельство СССРС 3/00, 20.2.86 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР ПИСАНИЕ ИЗОБ(54) СИНТЕЗАТОР СИГНАЛОВ С ЗАДАННЫМ ЗАКОНОМ ИЗМЕНЕНИЯ ФАЗЫ (57) Изобретение относится к радиоэлектронике. Целью изобретения является снижение побочных составляющих спектра выходных сигналов и повышение быстродействия, Синтезатор сигналов с заданным законом изменения фазы содержит первый делитель 1 частоты, блок 2 формирования кодов фазы и частоты, Мкомбинационных сумматоров 31,32,3 м,й преобразователей кода 41,424 и,й дополнительных регистров памяти 51,525 и, элемент задержки 6, коммутатор 7, регистр памяти 8, цифроаналоговый преобразователь (ЦАП) 9, фильтр нижних частот 10, блок 11 формирования кодов фазы, второй делитель 12 частоты, синхронизатор 13, опорный генератор 14. На выходе блока 2 формируются коды фазы и частоты, которые после преобразований в комбинационных сумматорах 31,32,3 н, преобразователях кода 41,42,4 и, в дополнительных регистрах памяти 51,525 м поступают через коммутатор 7 в виде кодов отсчетов синусоидальной функции в регистр памяти 8, После быстродействующего регистра памяти 8 эти коды преобразуются в ЦАП 9" в напряжение, которое поступает на вход фильтра нижних частот 10, Блоки 11,2, элемент задержки 6, синхронизатор 13 позволяют снизить побочные составляющие спектра и повысить быстродействие. 9 ил.10 20 ЗО 40 50 Изобретение относится к радиоэлектронике и может быть использовано в устройствах формирования сигналов с заданным законом изменения фазы в синтезаторах частоты.Целью изобретения является снижение побочных составляющих спектра выходных сигналов и повышение быстродействия.На фиг.1 представлена структурная электрическая схема синтезатора сигналов с заданным законом изменения фазы; на фиг.2 - временные диаграммы сигналов на выходе дополнительных регистров памяти и управляющих сигналов коммутатора при й=4 для случая тактирования сигналами с временным сдвигом; на фиг.З - временные диаграммы для случая тактирования дополнительных регистров одним и тем же сигналом; на фиг.4 - временные диаграммы приведенных к аналоговому виду значений А кодов отсчетов синусоидальной функции на выходах дополнительных регистров; на фиг. 5 - схема синхронизатора; на фиг,6 и 7 - примеры реализации блока 11 формирования кодов фазы; нэ фиг.8 и 9 - примеры реализации блока формирования кодов фазы и частоты,Синтезатор сигналов с заданным законом изменения фазы содержит (фиг.1) первый делитель 1 частоты, блок 2 формирования кодов фазы и частоты, йкомбинационных сумматоров 31,323 н, й преобразователей 41,42.41 ч кода, й дополнительных регистров 51,52,5 н памяти, элементы 6 задержки, коммутатор 7, регистр 8 памяти, цифроаналоговый преобразователь (ЦАП) 9, фильтр 10 нижних частот, блок 11 формирования кодов фазы, второй делитель 12 частоты, синхронизатор 13, опорный генератор 14. Блок 11 содержит (фиг,6) накопитель 15 кода, счетчик 16 по модулю й, дешифратор 17, й регистров 181,182.,18 й памяти, делитель 19 кода. Блок 11 формирования кодов фазы (фиг.7) содержит делители 201,202,20 э кода, комбинационные сумматоры 211,212,21 з,214, инвертор 22 кода. Блок 2 формирования кодов фазы и частоты (фиг,8) содержит коммутационный блок 23 и накопитель 24 кода фазы, Блок 2 (фиг,9) содержит коммутационный блок 25, накопитель 26 кода фазы, накопитель 27 кода частоты, комбинационный сумматор 28, делитель 29 частоты. Синхронизатор 13 (фиг,5) содержит дешифратор 30, ййЯ-триггеров 311,312311 ч, счетчик 32 по модулю й,Синтезатор сигналов с заданным законом изменения фазы работает следующим образом,В каждом й-ом такте опорного генератора 14 на выходе первого делителя 1 частоты, который имеет коэффициент деления й, возникает импульс, который поступает на вход блока 2, на выходе сигнала кода частоты которого формируется код ЙК, а на выходе сигнала кода фазы код фазы К,поступающий не первые входы комбинационных сумматоров 31,323 ии вход элемента 6 задержки, С первого выхода блока 11 поступает код К, со второго выхода - 2 К 1- с третьего - ЗК 1 с (й)-го - (М)К, Эти коды формируются из кода йК 1, поступающего с блока 2 и подаются на вторые входы комбинационных сумматоров 31,32,3 и, на выходе которых формируются коды, равные соответственно К+ К 1, Ку+ 2 КгКу+ +(й) К 1, Для выравнивания задержки, вносимой упомянутыми комбинационными сумматорами, включен элемент 6 задержки. Разрядность комбинационных сумматоров 31,32,.,3 ю равна входной разрядности преобразователей 41,424 м кода и обычно не превышает 8 - 12, Разрядность блока 2 значительно больше и выбирается, исходя из требуемого шага перестройки, но частоте на выходе устройства. Преобразователи 41,42,4 и кода из поступающих на них кодов фазы формируют коды отсчетов синусоидальной функции, которые проходят через соответствующие регистры памяти, тактируемые сигналом с 1-го выхода тактового синхронизатора 13, Синхронизатор 13 вырабаты,1 ает й импульсных сигналов, каждый из которых имеет частоту повторения 1 т=1 оп/й и заряжен относительно предыдущего на время Тог=1/гог - длительность также сигнала опорного генератора 14 (фиг,2 е,ж,з,и,З,е,ж,з,и). Эти сигналы образуют йфазную систему. Длительность импульсов на тактовых выходах синхронизатора 13 равна 1 Тог, где 1=Тсинхр/Тог целое; Тсиих - длительность импульсов на тактовых выходах синхронизатора 13, и выбирается иэ условия надежного срабатывания дополнительных регистров 51,52,5 и памяти, на выходах которых коды отсчетов синусоидальной функции задержаны друг относительно друга на время, равное тактовому интервалу сигнала опорного генератора 14, (фиг.2 а - и), что необходимо для компенсации запаздывания коммутатора 7 особенно на предельных частотах переключения, На фиг. За - и приведены для й=4 временные диаграммы, объясняющие возникновение ошибки в выходном сигнале коммутатора в случае, когда информация на сигнальных входах коммутатора изменяется одновременно. При этом сигнал, по которому последний сигнальный вход коммутатора 750 подключается к его выходу (фиг.Зи), перекрывается с изменением, информации насигнальном входе коммутатора (фиг.Зд), Нафиг.4 показаны значения кодов отсчетов синусоидальной функции для случая 8=4, приведенные к аналоговому виду, причемкаждый код отличается от предыдущего временным сдвигом и соответствующим приращением.Таким образом, тактирование дополнительных регистров 51,525)ч памяти сигналами со сдвигом позволяет увеличитьбыстродействие всего устройства за счетвременного совмещения сигналов, подаваемых на сигнальный вход коммутатора 7 исигналов управления коммутатора 7,На выходе коммутатора 7 формируютсякоды отсчетов синусоидальной функции, изменяющиеся с тактовой частотой аког. Послебыстродействующего регистра 8 памяти этикоды преобразуются в ЦАП 9 в напряжение,которое поступает на вход фильтра 10 нижних частот, выход которого является выходом устройства,В синхронизаторе 13 (фиг,5) счетчик 32по модулю М, выход которого является также кодовым выходом синхронизатора 13,управляет дешифратором 30, а ВЗ-триггеры311,312,".,31 и предназначены для расширения выходных импульсов враэ. При этомЯ-вход ВЗ-триггера 311 соединен с первымвыходом дешифратора 30, Я-вход ВЯ-триггера 31 ы с И-м выходом дешифратора 30,й-вход ВЯ-триггера 311, соединен с )-м выходом дешифратора 30,й-вход ВЯ-триггера312 - с ( + 1)-м выходом дешифратора ЗОЯвход ЯЯ-триггера 31 лщ+1) соединен с Ы-мвыходом дешифратора 30, Я-вход ЯЯ-триггера 31 (ил+2) соединен с первым выходом дешифратора ЗОй-вход ВЯ-триггера 31(ы)соединен с -2)-м выходом дешифратора 30,й-вход ЯЯ-триггера 31 и соединен с -1)-мвыходом дешифратора 30,Синхронизатор 13 может быть построенна основе кольцевого регистра, выходы которого являются тактовыми выходами. Есликоммутатор 7 управляется позиционным кодом, то эти выходы образуют непосредственно кодовый выход синхронизатора 13.При управлении коммутатором 7 двоичнымкодом между выходами кольцевого регистра и управляющим входом коммутатора 7необходимо включить шифратор (не показано), преобразующий позиционный код вдвоичный,Блок 11 может быть выполнен различными способами (фиг,6 и 7). Первый вариантпостроения этого блока (фиг,б) наиболеепригоден для случая, когда предлагаемоеустройство используется в качестве синтез 10 15 20 25 30 35 40 затооа частот (при этом коды на выходах блока 11 постоянны), а второй вариант (фиг.7) - для случая, когда устройство используется в качестве синтезатора сигналов (коды нэ выходах блока 11 меняются с каждым тактом частоты 1 т).Первый вариант блока 1 1 (фиг,6) реализован на основе накопителя 15, который имеет разрядность, равную сумме разрядности одного иэ преобразователей 41,.4 и кода и разрядности числа М, представленного в двоичном виде. Накопитель 15 тактируется импульсами с выхода второго делителя 12 частоты, Усеченный до входной разрядности преобразователей 41,4 и кода код частоты, равный МК и подаваемый на вход блока 11, делится в делителях 20;.20.20 з кода на И, В случае, когда 8=2 ,Р р = 0,1, 2,3, деление кода на 2 р эквивалентно простому сдвигу кода на р-разрядов, и делители 201,202,20 э кода реализуются в виде ряда клемм, к которым входной код подсоединяется непосредственно, а выходной - со сдвигом на р-разрядов в сторону младших разрядов.Импульс переполнения счетчика 16 по модулю М обнуляет накопитель 15, а также записывает в регистр 18 М памяти код Кг, поступающий на его кодовый вход с делителя 19 кода, Код Кг поступает на вход накопителя 15 кода, который с каждым импульсом сигнала, поступающего на тактовый вход блока 11, прибавляет код Кг к уже хранящемуся внем коду.Таким образом, код на выходе накопителя 15 кода в первом такте равен нулю, во втором такте равен К, в третьем такте - 2 К.М-м такте - (М)К, Выход накопителя 15 кода соединен с кодовыми входами регистров 18118(и) памяти, а их тактовые входы подключены к выходам дешифратора 17, вход которого соединен с кодовым выходом счетчика 16, Выходы дешифратора 17 подключены к тактовым входам регистров 181,18 и) памяти таким образом, что во втором такте, когда на выходе накопителя 15 кода присутствует код Кг, тактирующий импульс с выхода дешифратора 17 приходиттолько на регистр 18.1 памяти, в 3-м такте, когда на выходе накопителя 15 код равен 2 К, он переписывается только в регистр 18,2 памяти, а в М-м такте код, равный (й)К, переписывается только в регистр 18(и)памяти. За один цикл работы накопителя 15 кода и счетчика 16 в регистрах 181,. 18(ы) памяти оказывается записанным необходимый набор кодов, При смене кода МК на кодовом входе блока 11 необходимый набор кодов вновь устанавливается через Йтактов сигнала, поступающего нгтактовыйвход блока 11, т,е, за один цикл работы накопителя 15 кода и счетчика 16.В блоке 11 по схеме 7, построенном для случая И=8, использованы делители 20,20 г,20 з кода с коэффициентами деления 8,4 и 2 соответственно, которые реализованы в виде ряда клемм, не вносящих задержки. При этом входной код подсоединен к клеммам непосредственно, а выходной - со сдвигом соответственно на 3,2 и 1 разряд (в сторону младших разрядов), Таким образом, задержка срабатывания блока 11 (фиг,7) равна суммарной задержке одного иэ комбинационных сумматоров 21,2121 а и инвертора 22 кода. Если применить комбинационные сумматоры, которые могут работать как на суммирование, так и на вычитание, инвертор 22 кода можно исключить, Таким образом, вариант реализации блока 11, представленный на фиг,7, является наиболее быстродействующим. Его целесообразнее использовать, когда предлагаемое устройство предназначено для синтеза сигналов,Блок 2 при использовании устройства в качестве синтезатора частот выполнен (фиг,8) на основе коммутационного блока 23 и накопителя 24 кода фазы.УКаждый из переключателей коммутационного блока 23 имеет два положения, в одном из которых на соответствующий выход блока поступает напряжение логического нуля, а в другом - логической единицы. Меняя положение переключателей коммутационного блока 23 можно сформировать различные коды МК, поступающие на выход кода частоты блока 2 и на входнакопителя 24 фазы, выход которого является выходом кода фазы блока 2. С каждым тактовым импульсом, которые следуют с частотой аког/М и поступают на вход блока 2, к коду, записанному в накопителе 24 кода фазы, прибавляется код, установленный на коммутационном блоке 23, в результате чего на выходе формируется линейно-ступенчатый нарастающий код фазы К, равный в каждом М-м такте требуемому коду фазы, который соответствует необходимому значению синтезирующей частоты.В остальных йтактах требуемый код фазы формируется на выходах комбинационных сумматоров 31.3(ы) и после преобразования в коды выборки синусоидального сигнала мультиплексируется с соответствующим временным сдвигом, В результате этого значение на выходе элемента 6 задержки и на выходах комбинационных сумматоров 33(пи) в соответствующие моменты с необходимой точностью совпадают с кодом на выходе накопителя 24 кода фазы, работающего с тактовой частотой 1 О,при условии, что на его вход подается кодчастоты К,При использовании устройства в качест 5 ве синтезатора сигналов с линейной частотной модуляцией(фиг,9) в накопителе 27 кодачастоты формируется код частоты, изменяющийся по ступенчато-линейному закону,Этот код суммируется с кодом начальной10 частоты, поступающим с коммутационногоблока 23, в комбинационном сумматоре 28,выход которого является выходом кода частоты блока 2, В накопителе 26 кода фазы,выход которого является выходом кода фа 15 зы блока 2 формируется код, изменяющийсяпо ступенчато-параболическому закону,При этом при медленном изменении частоты накопитель 27 кода частоты работает наболее низкой тактовой частоте, чем накопи 20 тель 26 кода фазы, что позволяет применитьв нем микросхемы с малым потреблениемэнергии и низким быстродействием, Снижение тактовой частоты достигается использованием делителя 29 частоты.25 Такие блоки, как комбинационный сумматор, накопитель кодов, преобразователькодов и коммутатор, при условии их реализации на одной серии микросхем имеютзначительные отличия в быстродействии,30 Так, при использовании микросхем 100-йсерии 32 разрядный комбинационный сумматор с ускоренным переносом имеет типовую за,гержку 18 нс, накопитель кодов тойже разрядности на 4 нс (задержка регистра35 памяти) больше, преобразователь кода (наоснове ПЗУ 100 РЕ 149) типовую задержку25 нс.Таким образом при И=8 введение временной задержки элементом 6 задержки,40 которая компенсирует влияние запаздывания срабатывания коммутатора, позволяетреализовать устройство, работающее на частотах, предельных для коммутатора, что недостижимо в прототипе, поскольку там все сигналы подаются на сигнальнЫе входы коммутатора одновременно из-эа запаздывания его срабатывания, выборка из сигнала, поступающего на последний сигнальный вход коммутатора, произойдет в момент50смены информации, что приведет кошибке,На выходе формирователя сигналов сзаданным законом изменения фазы спектра ближайшая побочная составляющая спектра расположена на частоте аког - Г. что обеспечивает фильтрацию, таким образом снижается уровень побочных дискретных составляющих спектра при условии увеличения полосы синтезируемых частот.1686693 а о г д е Я Формула изобретения Синтезатор сигналов с заданным законом изменения фазы, содержащий последовательно соединенные опорный генератор, первый делитель частоты, блок формирования кода фазы и частоты, последовательно соединенные коммутатор, регистр памяти, цифроаналоговый преобразователь и фильтр нижних частот, й преобразователей кода, при этом тактовый вход регистра памяти подключен к выходу опорного генератора, о т л и ч а ю щ и й с я тем, что, с целью снижения побочных составляющих спектра выходных сигналов и повышения быстродействия, введены элемент задержки, Мкомбинационных сумматоров, й дополнительных регистров памяти, последовательно соединенные второй делитель частоты и блок формирования кодов фазы, а также синхронизатор, при этом выход сигнала кода частоты блока формирования кодов фазы и частоты подключен к кодовому входу блока формирования кодов фазы, выход сигнала кода фазы блока формирования кодов фазы и частоты соединен с первыми входами Мкомбинационных сумматоров, выход каждого из которых подключен к входу соответствующего преобразователя кодов, выход 5 каждого из й преобразователей кодов подключен к кодовому входу соответствующего из М дополнительных регистров памяти, выходы которых соединены с соответствующими входами коммутатора, вход элемента 10 задержки подключен к выходу сигнала кодафазы блока формирования кода фазы и частоты, вход второго делителя частоты подключен к выходу первого делителя частоты, вторые входы йкомбинационных сумма торов подключены к соответствующим выходам блока формирования кодов фазы, тактовый вход синхронизатора подключен к выходу опорного генератора, управляющий вход коммутатора подключен к кодовому 20 выходу синхронизатора, тактовые входы Идополнительных регистров памяти подключены к соответствующим выходам синхронизатора, выход элемента задержки соединен с входом соответствующего из Й 25 преобразователей кода,1686693 ВихоИ кода чОстогпы И дЛ 11 9 иг Составитель Н, Чеканова едактор М. Янкович Техред М.Моргентал Корректор М. Кучерявая каз 3611 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5ат "Патент", г, Ужгород, ул,Гагарина, 10роизводственно-издательский ко

СмотретьЗаявка

4702669, 07.06.1989

МОСКОВСКИЙ ИНСТИТУТ СВЯЗИ

ЖАРОВ АЛЕКСЕЙ НИКОЛАЕВИЧ, КОЧЕМАСОВ ВИКТОР НЕОФИДОВИЧ, БУДИШОВ ВЯЧЕСЛАВ ПЕТРОВИЧ

МПК / Метки

МПК: H03C 3/00

Метки: заданным, законом, изменения, сигналов, синтезатор, фазы

Опубликовано: 23.10.1991

Код ссылки

<a href="https://patents.su/8-1686693-sintezator-signalov-s-zadannym-zakonom-izmeneniya-fazy.html" target="_blank" rel="follow" title="База патентов СССР">Синтезатор сигналов с заданным законом изменения фазы</a>

Предыдущий патент: Устройство для возбуждения бесщеточного синхронного генератора

Следующий патент: Транзисторный фазоинвертор

Случайный патент: Машина для фрезерования закустаренных земель