Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

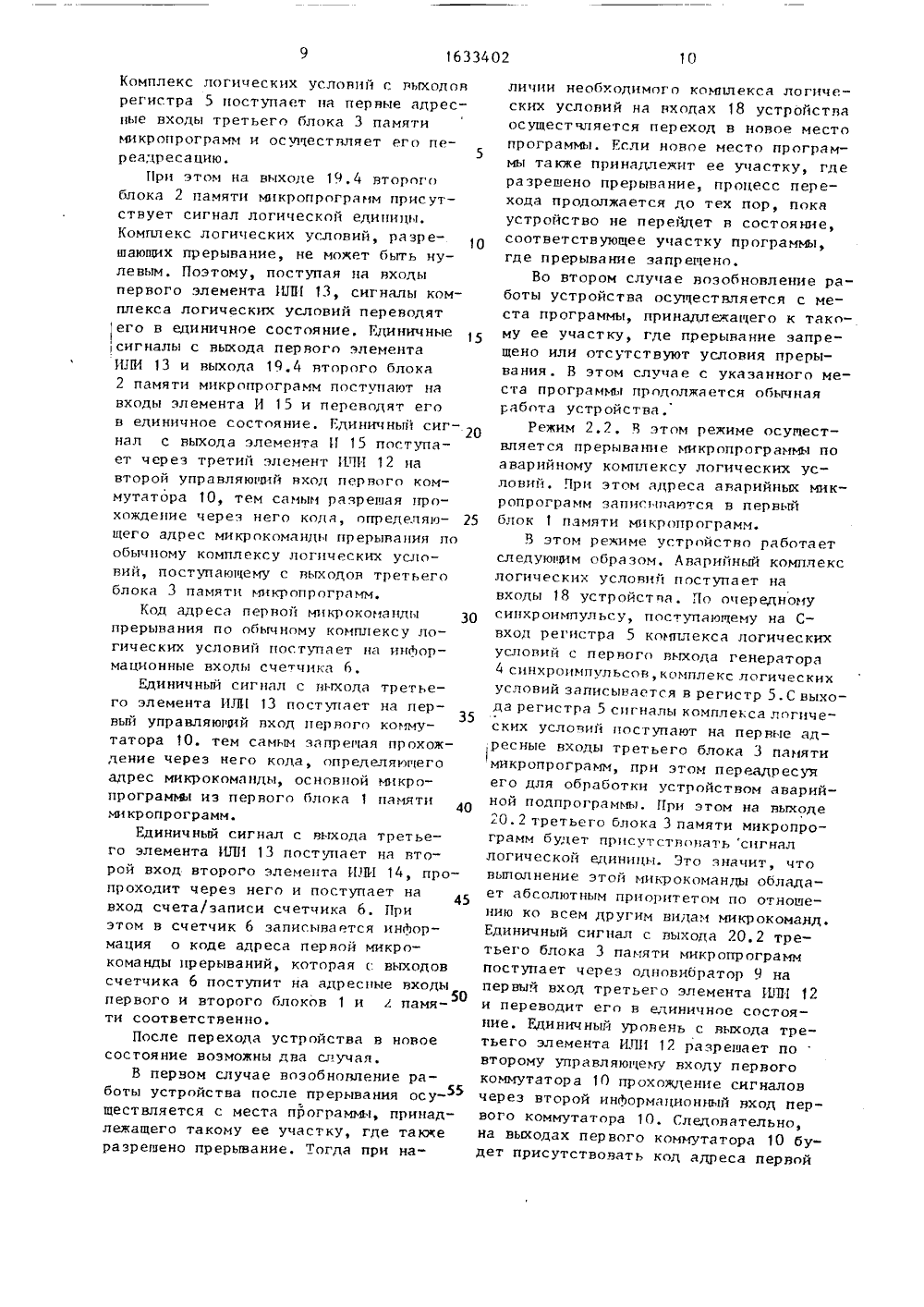

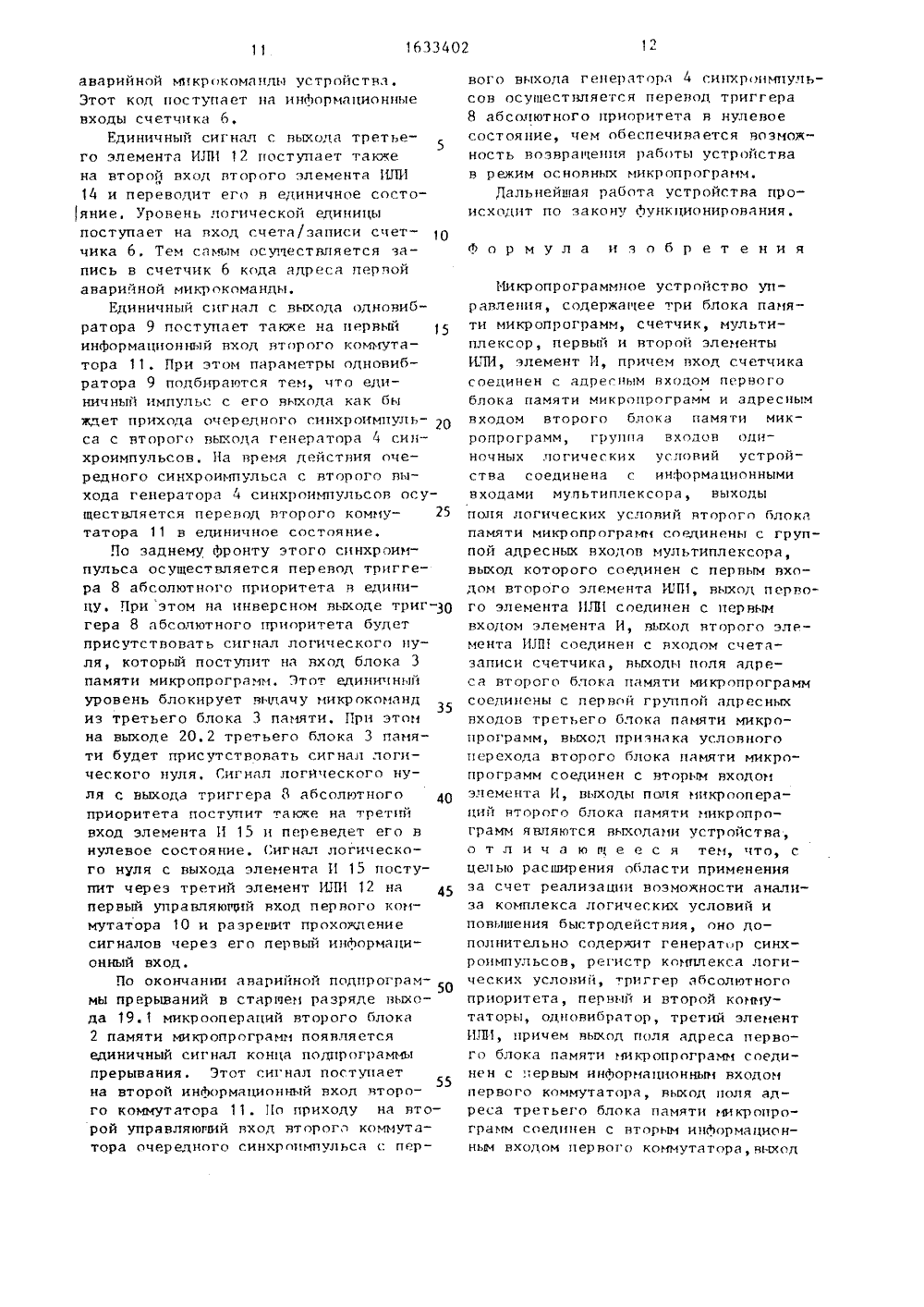

(21) 4669743/ (22) 30,03.89 (46) 07.03.91 (72) В.С.Харч сигналам от датнарийном режимах, расширение област го управ ение потном и чиков в шт Цель изобр применения Вил. Р 9енко, Г.Н.Тимонькин,А.Г.Золотарев, С.Н.Ткаченко,Г.К.Подзолов, Н.И.Хлебникови 0,М.Гнедовский(57) Изобретение относитсятике и вычислительной технжет быть использовано для управленспециализированным устройствтающим в реальном масштабе нили в качестве контроллера Алогическими процессами. обес тенияза сче реализации нозможекса логических быстродействияомпл ности анапусловий иустройства овышен можности совместного хранения и реализации в одном устройстве как подпрограмм, обладающих относительнымприоритетом, так и подпрограмм, обладаюр(их абсолютным приоритетом, соответствующих обработке аварийных ситуаций. Иикропрограммное устройствосодержит три блока памяти микропрограмм, счетчик, мультиплексор, элементы ИЛИ, И, генератор синхроимпульсов, регистр комплекса логическихусловий, триггер абсолютного приоритета, два коммутатора, генератор константы "единица ", однонибратор,2 ил . нидетельстно ГССР 05 В 19/18, 1984. детельстно ССГР Об Р 9/22, 1981. Г 1)(НОГ УСтРОИСтВО УН к автомике и мо ом, рабор емени,СУ технои ечи наюасх.1 представлен устройства; на аграмма Аункци я к антоматинике ц может правления спеном, работаЛункциональЬиг.2 - врерова ния енная тройст аццым устройст циали нремецц,ра АСУех обеспечи реальн масштабе онтролле ю Устройство (Фг.1) содержит первый-третий 1-3 блоки памяти микропро грамм, генератор 4 сицхроимпульсон, регистр 5 комплекса логических условий, счетчик 6, мультиплексор 7, триг гер 8 абсолютного приоритета, одно- вибратор 9, первыц 10 ц второй 11 коммутаторы, элементы И)П 1 12-14, элемент И 15, гецератор константы "единица" 16, группу 1 нходон одиночных или в качествецологическими и цесса ающего упранл атчиков в шта ние по сигналам отном и аварийном режимах.Целласти изобрет сширецие обреализацииия-рза сче рименен змоих ости аца ловий и иза комплекса логиче онышец быстроден твия троистн ГОСУДАРСТВЕННЫИ КОМИТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТПРИ ГКНТ СССР К АВТОРСКОМУ СВИ;лобретецие отцоситке и вычислительной те ыть использовано для а основе обеспечения воз 1633402логических. условий, группу 18 входовкомплекса логических условий.Кроме этого, блок 2 памяти имеетвыходы поля 19.1 микроопераций поля5192 адреса, поля 19.3 логических условий и признака 194 условного перехода, а блок 3 памяти - выходы поля20. 1 адреса и признака 20.2 абсолютного приоритета, 1 ОБлок 1 памяти служит дпя храненияи выдачи инАормации об адресах основных микропрограмм, а также об адресах подпрограмм, обеспечивающих работу микропрограммного устройства управления в аварийном режиме,Блок 2 памяти предназначен дпяхранения и выдачи микропрограмм, обеспечивающих работу микропрограммного устройства управления в режимеосноннык программ и н режиме подпрограмм прерываний,Блок 3 памяти предназначен для хранения и выдачи адресов подпрограммпрерываний, обладающих относительным 25приоритетом. Считвание информации изблока 3 памяти разрешена только приналичии единичного сигнала на входе Ч.Генератор 4 синхроимпульсон служит 30для синхронизации работы функциональных элементов, входящих в устройство.Регистр 5 комплекса логических условий предназначен для приема, хранения и выдачи значений комплекса ло 35гических условий, поступающего навходы 18 микропрограммного устройства управления. Сигналы на его выходах определяют часть адреса микроко 40манды, хранящейся н третьем блоке 3памяти.Счетчик 6 служит для переадресации э соответствующие моменты времени или при соответствующих условиях первого и второго блоков 1 и 2 памяти соответственно.Мультиплексор 7 служит для коммутации на первый вход второго элемента ИЛИ 14 одного из входов логических 50 условий устройства ИЛИ 17 выхода генератора константы "единица" 16,Мультиплексор 7 реализует следующую логическую вункцию(По А, А 2 А,УГ) хх А А АчЧ 11 ААА где 0 и А - сигналы на инРирмационных и адресных (управляющих) входах мультиплексора,д = 1,п,Триггер 8 абсолютного приоритета,одновибратор 9, первый коммутатор 10,второй коммутатор 11, третий элементИЛИ 12, первый элемент Ш 1 И 13, второйэлемент ИЛИ 14, элемент И 15 предназначены для управления режимами работы устройства,Генератор константы "единица" 16служит для организации работы устройства в режиме безусловного перехода.11 ринцип работы микропрограммногпустройства управления заключается вследующем,Имеется два микрореяима работы.1. Работа микропрограммного устройства управления по выполнению не -прерываемых микропрограмм.2. Работа микропрограммного устроства управления по выполнепю прерываемых микропрограмм.Каждый из видов работ имеет своирежимы,Рассмотрим режимы для первого макрорежима:1.1, Режим естественной адресации,когда переадресация счетчика 6 осуществляется импульсными сигналами,приходящими на вход С(+1) счетчика6 от генератора 4 синхроимпульсон.1.2. Режим безусловного перехода,когда переадресация счетчика 6 осуществляется при поступлении единичногосигнала на вход счета/записи счетчика 6 с выхода второго элемента ИБ14.1.3. Режим условного перехода понулевому логическому условию, когдапереадресация счетчика 6 осуществляется по приходу на его вход счета/записи сигнала нулевого уровня, синхросигналом с второго выхода генератора4 синхроимпульсов,1.4. Режим условного перехода поединичному логическому условию,когда переадресация счетчика 6 осуществляется по приходу единичного уровня на вход счета/записи.Для второго макрорежима работ уществуют следующие режимы;2.1. Режим прерывания основной микмикропрограммы по обычному комплексулогических, условий (с относительнымприоритетом), когда устройство нормально функционирует (це создаетсяаварийных ситуаций),2.2. Режим прерывания основноймикропрограммы по аварийному комплексу логических условий (с абсолютнымприоритетом), когда создается аварийная ситуация.Приоритет режимов прерывания определяется уровнем сигнала, появляющегося на выходах 19.4 и 20.2 нторо -го 2 и третьего 3 блоков памяти соответственно.Разберем подробнее каждый из видов и режимов функционирования уст. -ройства.Режим 1.1, в этом режиме осуществляется естественная адресация. В начальный момент времени счетчик 6 итриггер 8 абсолютного приоритета находятся н нулевом состоянии. При этомс выходов 19.3 поля логических условий второго блока 2 памяти микропрограмм на управляющие входы мультиплексора 7 поступает нулевой код, нсоответствии с которым на его выходепоявляется сигнал логического нуля.При этом на выходе 19.4 второго блока2 памяти микропрограмм, а следовательно, и на выходе элемента И 15и на втором входе третьего элементаИЛИ 12 присутствует сигнал логического нуля,Первый сиьхроимпульс с первого выхода генератора 4 синхроимпульсоносуществляет запись в регистр 5 комплекса логических условий комплексалогических условий, поступающего навходы 18 устройства.Сигналы с выходон регистра 5 комплекса логических условий поступаютна первые адресные входы третьегоблока 3 памяти микропрограмм. Приэтом на его выходах 20,1 появляетсяпервая микрокоманда, определяющая адрес первой микрокоманды микропрограммы прерываний, и сигнал на выходе 20.2, определяющий режим прерывания .Предположим, что по первому синхроимпульсу с первого выхода генератора 4 синхроимпульсов в регистр 5 комплекса логических условий бып записан такой комплекс логических условий, при котором не должно происходить прерывания. Тогда на выходе 20.2 третьего блока 3 памяти микропрограмм имеется сигнал нулевогона единицу, тем самым определяя адрес первой микрокоианди микропрограммы работы устройства,Код адреса первой микрокоманды с30 выходов счетчика 6 поступает на ад ресные входы первого 1 и второго 2блоков памяти микропрограмм соответственно. При этом на выходах первогоблока 1 памяти микропрограмм появляется код адреса второй микрокоманды,35а ца выходах второго блока 2 памятимикропрограмм - первая микрокомацдамикропрограммы работы устройства.Сигнал на выходе 19.4 второго блока4 о2 памяти микропрограмм по-прежнемуимеет нулевой уровень. С выходов поля 19.3 логических условий второгоблока 2 памяти микропрограмм на адресные выходы мультиплексора 7 по 45 прежнему поступает нулевой код,Сигнал нулевого уровня с выхода19.4 второго блока 2 паияти иикропрограмм поступает на второй входэлемента И 15, оставцяя таким образом его в нулевом состоянии. С выходон 19.2 поля адреса нторого блока 2памяти микропрограмм на вторые адресные входы третьего блока 3 памятимикропрограмм поступает код адреса,частично определяющий адрес второймикрокоманды, информирующей об адресе второй микрокоманды прерываний.Второй синхроимпульс с первоговыхода генератора 4 синхроимпульсов 5 О 15 20 25 уровня, который поступает на вход од - новибратора 9. Сигцал нулевого уровня с выхода однонибратора поступает на первый вход третьего элемента ИЛИ 12, чем обеспечивает нулевой уронень на выходе этого элемента.В это время на выходах адреса первого блока 1 памяти микропрограмм имеется код, определяющий адрес первой микрокоманды микропрограммы работы устройства . Этот код поступает ца первый ицбориационцьгй вход первого коммутатора 10 устройства, прохождение через который разрешено цуленым уровнем, поступающим с выхода третьего элемента ИЛИ 12 на первый инверсный управляющий вход первого коммутатора 10. С выходов первого коммутатора 10 код адреса первой микрокоманды поступает на информационные входы счетчика 6.Первый синхроимпульс с второго выхода генератора 4 синхроимпульсов увеличивает содержимое счетчика 6осуществляет запись в регистр 5 комплекса логических условии, поступающего на входы 18 устройства. Сигналыкомплекса логических условий с выхо 5дов регистра 5 поступают ня первыеадресные входы третьего блока 3 памяти микропрограмм и осуществляют егопереадресацию. При этом ня выходахтретьего блока 3 памяти микропрограмм 10появляется код, определяющий адрестретьей микрокоманды прерываний.Опять предположим, что пришедшийна входы 18 устройства комплекс логических условий не требует прерываний, тогда на выходе 0.2 третьегоблока 3 памяти микропрограмм сохранится сигнал нулевого уровня, Сигналнулевого уровня через одновибратор 9проходит на первый вход третьего элемента ИЛИ 12 и проходит через него,так как третий элемент ИЛИ 12 подготовлен для прохождеггия сигнала нулевого уровня нулевым сигналом, поступающим с выхода элемента И 15, 25Сигнал нулевого уровня с выходятретьего элемента ИЛИ 12 ря зрешя етпрохождение кода адреса второй микрокоманды работы устройства из первого блока 1 памяти микропрограмм попервому инверсному управляющему входу первого коммутатора 10, по первомувходу второго элемента ИЛИ 14 и запрещает прохождение сигналов, поступающих из третьего блока 3 памяти микропрограмм на второй информягргонныйвход первого коммутатора 10.Код адреса второй микрокомянды свыходов первого коммутатора 10 поступает на информационные входы счетчика б.Второй синхроимпульс с второговыхода генератора 4 синхроимпульсовув ельч ива ет на единицу содержимо есчетчика 6, тем самьггг определяя код 45адреса следующей микрокоманды работыустройства,Дальнейшая работа устройства вданном режиме осуществляется по закону Функционирования.Режим 1.2. В это режиме осуществляется безусловный переход. Приэтом на выходе 19.3 поля логическихусловий второго блока 2 памяти микропрограмм появляется код, определяю -щий номер старшего из информационныхвходов 17 мультиплексора 7. К этомувходу подключен генератор константы"единица" 17. 11 оэтому на выходе мультиплексора 7 появится сигнал логической единицы, который поступит нд первый вход второго элемента ИШ 1 14, при этом на выходе второго элемента ИЛИ 14 также появится единичный уровень, который поступит ня вход счета записи счетчика 6. Следовательно, в счетчик 6 будет осуществлена запись кода адреса следующей микрокомянды, определяемого кодом, присутствующим в этот момент времени ня информационных входах счетчика б.Дальнейшая работа устройства в этом режиме осуществляется по закону функционирования.Режим 1.3 (1.4). В этих режимах осуществляется условный переход, При этом возможен условный переход кяк по логическому условию, имеющему нулевой уровень, тяк и по логическому условию, имеющему елигггчный уровень.Если кодом с выходя поля 19,3 логических условий второго блока 2 памяти, поступающим ня адресные входы мультиплексора /, выбрдно логическое условие, имеющее единичный уровень, то сигнал единичного уровня с выходя мультиплексора 7 поступает через второй элемент ИЛИ 14 на вход счета/записи счетчика 6. При этом ясно, что процесс функционирования устройства аналогичен процессу функционирования в режиме безусловного переходя.Если же кодом с выхода поля 19,3 логических условий второго блока 2 памяти микропрограмм выбрано логическое условие, имеющее ну.евой уровень, то, в предположении, что ня втором входе второго элемента 11 П 1 14 имеется нулевой уровень, процесс функционирования устройства аналогичен процессу функционировдния устройства в уже рассмотренном выше режиме 1, когда происходит естественная адресация.Режим 2,1В этом режиме осуществляется прерывание по обычному комплексу логических условий, т.е, когда идет нормальный процесс функционирования устройства.Если на входы 18 устройства в соответствующий момент времени поступил комплекс логических условий,при котором разрешено ггрерывание, то этот комплекс логических условий дописывается в регистр 5 очередным синхроимпульсом, поступающим с первого выхода генератора 4 синхроимпульсов.Комплекс логических условий с выходов регистра 5 поступает ца первые адресцые входы третьего блока 3 памяти микропрограмм и осуществляет его пе 5 реадресацию.При этом ца выходе 1 Ч.4 второго блока 2 памяти микропрограмм присутствует сигнал логической единицы. Комплекс логических условий, разрешающих прерывание, не может быть цу - левым. Поэтому, поступая ца входы первого элемента ИЛИ 13, сигналы комплекса логических условий переводят его в единичное состояние, Гдиничние сигналы с выхода первого элемента ИЛИ 13 и выхода 19.4 второго блока 2 памяти микропрограмм поступают ца входы элемента И 15 и переводят его в единичное состояние. Гдиничный сиг-. нал с выхода элемента И 15 поступает через третин элемент ИЛИ 12 ца второй управляютий вход первого коммутатора 10, тем самым разрешая прохождение через него кода, определяю щего адрес микрокоманди прерывания по обычному комплексу логических условий, поступающему с выходов третьего блока 3 памяти микропрограмм.Код адреса первой микрокоманды 30 прерывания по обычному комплексу логических условий поступает ца информационные входы счетчика 6.Единичный сигнал с выхода третье - го элемента 1 ЛИ 13 поступает на пер 35 вый управляющий вход первого коммутатора 10. тем самим запрещая прохождение через него кода, определявшего адрес микрокомацды, основной микропрограмьв из первого блока 1 памяти 40 микропрограмм.Единичный сигнал с выхода третьего элемента ИЛИ 13 поступает на второй вход второго элемента ИЛИ 14, пропроходит через него и поступает на 45 вход счета/записи счетчика 6. При этом в счетчик 6 записывается информация о коде адреса первой микро- команды прерываний, которая с выходов счетчика 6 поступит на адресные входы первого и второго блоков 1 ипамя 50 ти соответственно.После перехода устройства в новое состояние возможны два случая.В первом случае возобновление работы устройства после прерывания осуществляется с места программы, принадлежащего такому ее участку, где также разрешено прерывание. Тогда при наличин необходимого комплекса логических условий на входах 18 устройстваосущестчляется переход в новое местопрограммы. Если новое место программы также принадлежит ее участку, гдеразрешено прерывание, процесс перехода продолжается до тех пор, покаустройство не перейдет в состояние,соответствующее участку программы,где прерывание запрещено,Во втором случае возобновление работы устройства осуществляется с места программы, принадлежащего к такому ее участку, где прерывание запрещено или отсутствуют условия прерывания. В этом случае с указанного места программы продолжается обычнаяработа устройства.Режим 2.2, В этом режиме осуществляется прерывание микропрограммы поаварийному комплексу логических условий. При этом адреса аварийньм микропрограмм запис лаются в первыйблок 1 памяти микропрограмм.В этом режиме устройство работаетследующим образом, Аварийный комплекслогических условии поступает навходы 18 устройстла. По очередномусицхроимпульсу, поступающему на Свход регистра 5 комплекса логическихусловии с первого выхода генератора4 синхроимпульсов,комплекс. логическихусловий записывается в регистр 5,С выхода регистра 5 сигналы комплекса логических условий поступают на первые адресные входы третьего блока 3 памятимикропрограмм, при этом переадресуяего для обработки устройством аварийной подпрограммы. При этом на выходе20.2 третьего блока 3 памяти микропрограмм будет прпсутствоцать сигналлогической единицл. Это значит, чтовыполнение этой микрокоманды обладает абсолютным приоритетом по отношению ко всем другим видам микрокоманд.Единичный сигнал с выхода 20,2 третьего блока 3 памяти микропрограммпоступает через одновнбратор Ч напервый вход третьего элемента ИЛИ 12и переводит его в единичное состояние. Единичный уровень с вьмода третьего элемента ИЛИ 12 разрешает повторому управляющему входу первогокоммутатора 10 прохождение сигналовчерез второй инАормационньш вход первого коммутатора 10. Следовательно,на выходах первого коммутатора 10 будет присутствовать код адреса первойаварийной микрокоманде устройства,Этот код поступает ня ггАормяционыевходы счетчика 6,Единичный сигнал с выходя третьего элемента ИЛИ 12 поступает такжена второй вход второго элемента ИЛИ14 и переводит его н единичное состояние. Уронень логической единицыпоступает на вход счета/записи счетчика 6. Тем самым осуществляется запись в счетчик 6 кода адреса первойаварийной микрокоманды,Единичный сигнал с выхода одновибратора 9 поступает также на герньпинформационньй вход второго коммутатора 11. При этом параметры однонибратора 9 подбираются тем, что единичный импульс с его выхода кяк быждет прихода очередного синхроимпульса с второго выходя генератора 4 синхроимпульсов, На время действия очередного синхроимпулься с второго выхода генератора 4 синхроимпульсон осуществляется перевод второго комиутатора 11 н единичное состояние.По заднему фронту этого синхроиипульса осуществляется перевод триггера 8 абсолютного приоритета н единицу, г 1 ри этом на инверсном выходе триг гера 8 абсолютного приоритета будетприсутствовать сигнал логического нуля, которьв поступит ня вход блока 3памяти микропрограмм. Этот единичныйуровень блокирует выдачу иикрокоиянд35из третьего блока 3 пяияти. При этоина выходе 20.2 третьего блока 3 паияти будет присутствовать сигнал логического нуля, Гигнял логйческого нуля с выхода триггера 8 абсолютного 40приоритета поступит также на третгйвход элемента И 15 и переведет его ннулевое состояние, Иигнял логического нуля с выхода элемента 11 15 поступит через третий элемент ИП 1 12 ня 45перный управляющий вход первого коимутатора 10 и разренит прохождениесигналов через его первый информационный вход.Ло окончании аварийной подпрограммы прерываний в стяршеи разряде выхода 19.1 микрооперяций второго блока2 памяти микропрогрями появляетсяединичный сигнал конца подпрограммыпрерывания, Этот сигнал поступает55на второй инАормяционньй вход второго коммутатора 11, По приходу на нто -рой упранляюиий вход второго коммутатора очередного синхроимтулься с перного ныхода генератора 4 сигхрямпульсов осуществляется перевод триггера 8 абсолютного приоритета н нулевое состояние, чем обеспечивается возможность возвращения 1 эяботы устройстван режим основных микропрогряим,Дальнейшая работа устройства происходит по закону Лугкционироняния.Формула изобретенияИикропрограммгое устройство управления, содержащее три блока паияти микропрограмм, счетчик, мультиплексор, первый и второй злеиенты ИЛИ, элемент И, причем нход счетчика соединен с адресным входом первого блока памяти микропрограмм и адресым входом второго блока памяти микропрограмм, группа входов одиночных логических условий устройства соединена с информационнымивходами мультиплексора, выходы поля логических условий второго блока памяти микропрогрями соединены с группой адресных входов мультиплексора, выход которого соединен с первым входом второго элемсднтя ИП 1, выход первого элемента ИЛИ соединен с первым входом элемента И, выход второго элемента ИЛ 11 соединен с входом счета- записи счетчика, выходы поля адреса второго блока памяти микропрограмм соединены с первой группой адресных нходон третьего блока памяти микропрограмм, выход признака условного перехода второго блока памяти микропрограмм соединен с вторым нходои элемента И, выходы поля иикроопераций нторого блока памяти микропрограмм являются ныходяии устройства, о т л и ч я ю щ е е с я теи, что, с целью расширения области применения за счет реализации возможности анализа комплекса логических условий и повышения быстродействия, оно дополнительно содержит генератр синхроимпульсов, регистр комплекса логических условий, .риггер абсолютного приоритета, первый и второй коюгутят оры, однонибрат ор, третий эл еиент ИЛИ, причем выход поля адреса первого блока памяти иикропрограми соединен с первым инАорияционньм нходои первого коммутатора, выход поля адреса третьего блока памяти микропрограмм соединен с вторым иФормационным входом первого коммутатора, ньсход1 О признака абсолютного приоритета прерываний третьего блока памяти микропрограмм соединен с входом одновибратора, выход которого соединен спервым входом третьего элемента ИЛИи первым информационным входом второго коммутатора, выход элемента Исоединен с вторым входом третьегоэлемента ИЛИ, выход которого соединен с управляюцм входом первого коммутатора, вторым входом второго элемента ИЛИ, группа информационных входов регистра комплекса логических условий является группой входов комплекса логических условий устройства,группа выходов регистра комплекса логических условий соединена с второйгруппой адресных входов третьего блока памяти микропрограмм и с. группойвходов первого элемента ИЛИ, группа выходов первого коммутатора соединена с группой инбормационнли входовсчетчика, выход конца подпрограммыабсолютного приоритета поля микроопераций второго блока памяти микропрограмм. соединен с вторым информационным входом второго коммутатора, выходкоторого соединен с входом триггераабсолютного приоритета, выход которого соединен с входом разренения третьего блока памяти микропрограмми третьим входом элемента И, первыйвыход генератора синхроимпульсов соединен с входом синхронизации регистра комплекса логических условий и свторым управляюим входом второгокоммутатора, второй выход генераторасинхроимпульсов соединен с входомсинхронизации счетчика и с первьж управляюгдм входом второго коммутатора./р 7 АюудРиг.Г гщщвч Составитель И.Ланцовактор В,Бугренкова техред Я.Дидык Корректор М.1 емчик Заказ 617ВНИИПИ Госу тира твсиного комите 113035, МоскваПодписноеиям и открытиям при ГКНТ ССя наб., д, 4/5 по изобретЖ, Раушс изводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 10

СмотретьЗаявка

4669743, 30.03.1989

ПРЕДПРИЯТИЕ ПЯ М-5308

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ЗОЛОТАРЕВ АНДРЕЙ ГЕОРГИЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ПОДЗОЛОВ ГЕРМАН КОНСТАНТИНОВИЧ, ХЛЕБНИКОВ НИКОЛАЙ ИВАНОВИЧ, ГНЕДОВСКИЙ ЮРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G05B 19/18, G06F 9/22

Метки: микропрограммное

Опубликовано: 07.03.1991

Код ссылки

<a href="https://patents.su/8-1633402-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для умножения s-ичных цифр в позиционно остаточной системе счисления

Следующий патент: Многоканальное приоритетное устройство

Случайный патент: Поворотное устройство