Микропрограммное устройство для сопряжения процессора с абонентами

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1539787

Авторы: Гришин, Ярошевский

Текст

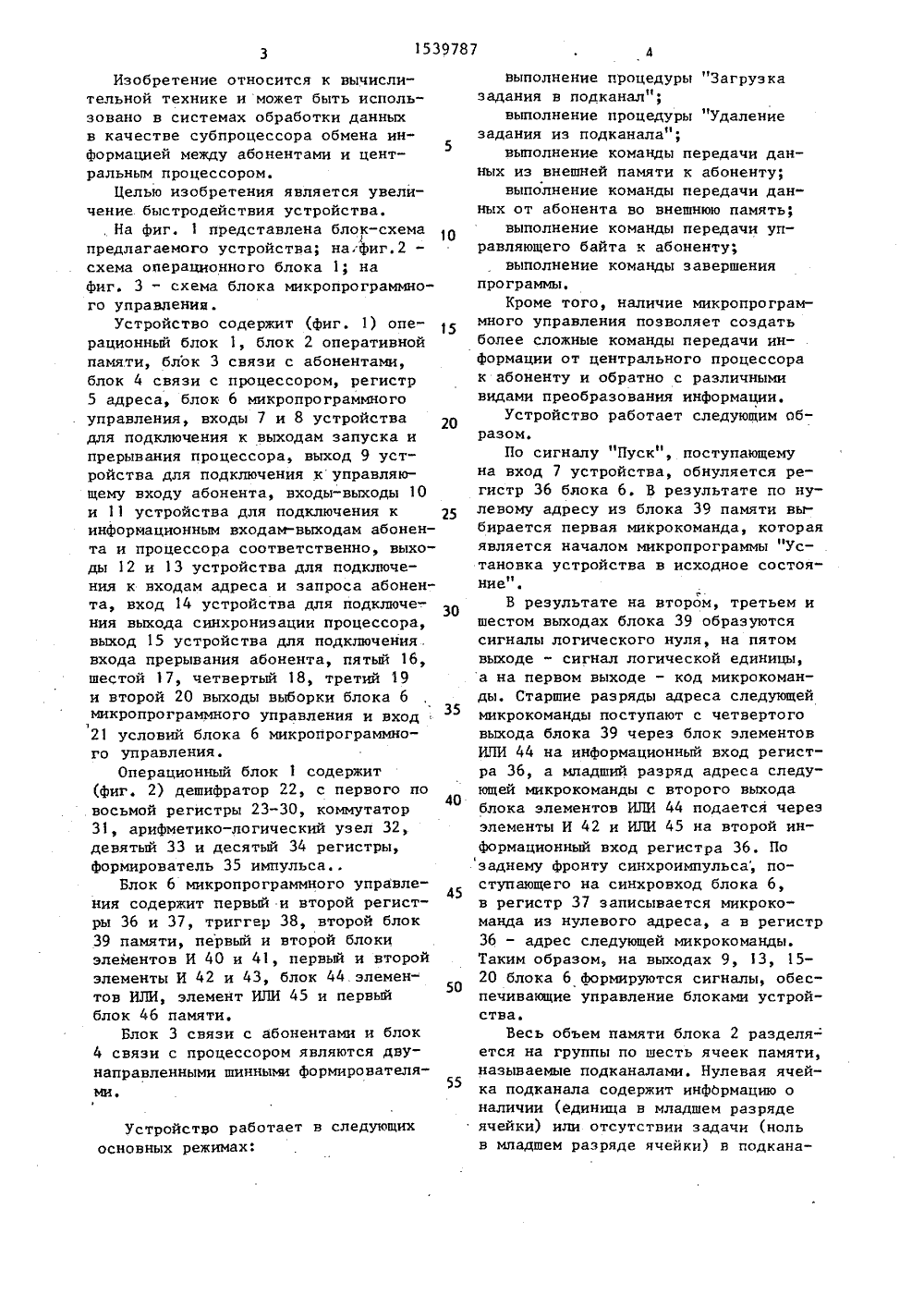

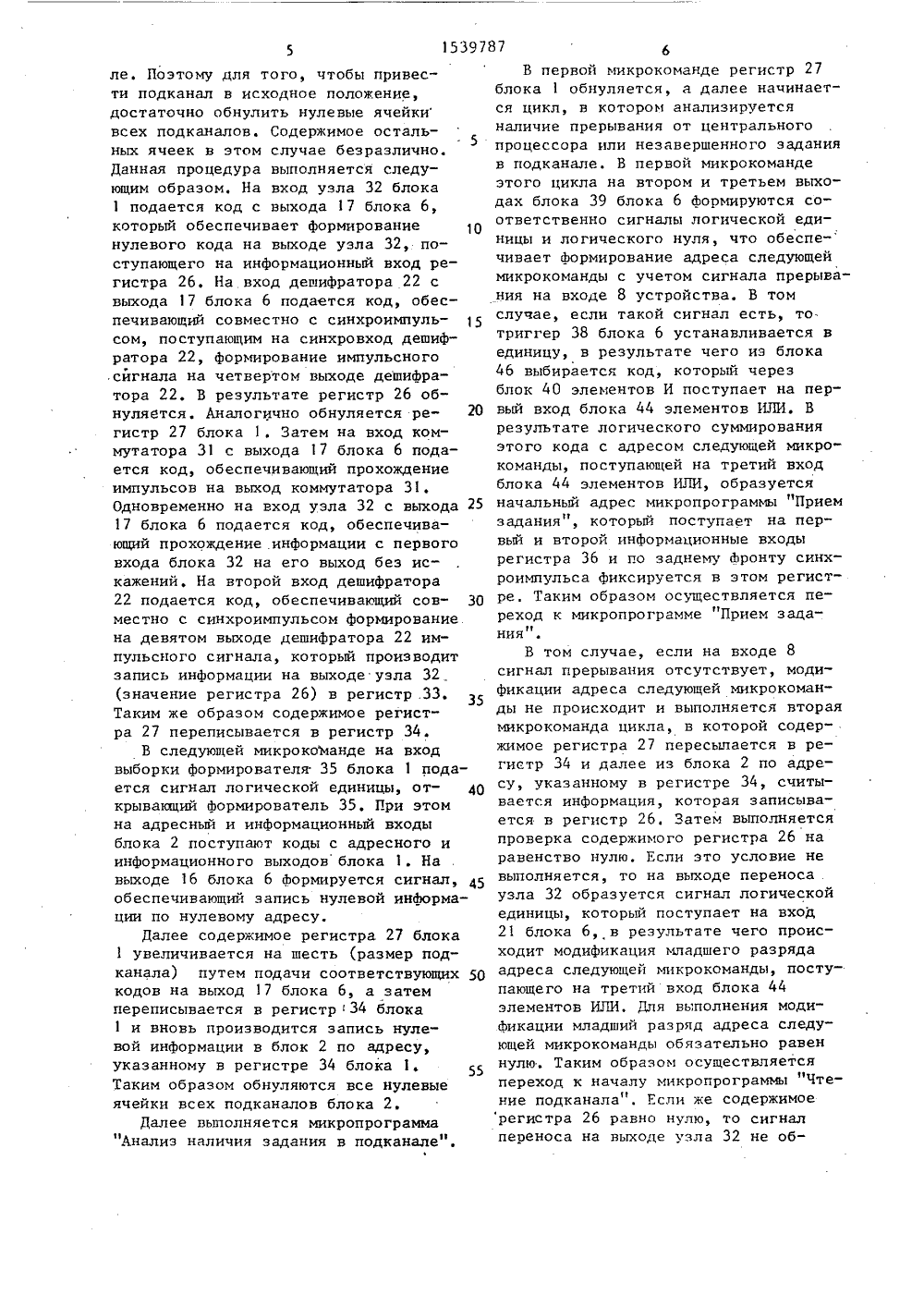

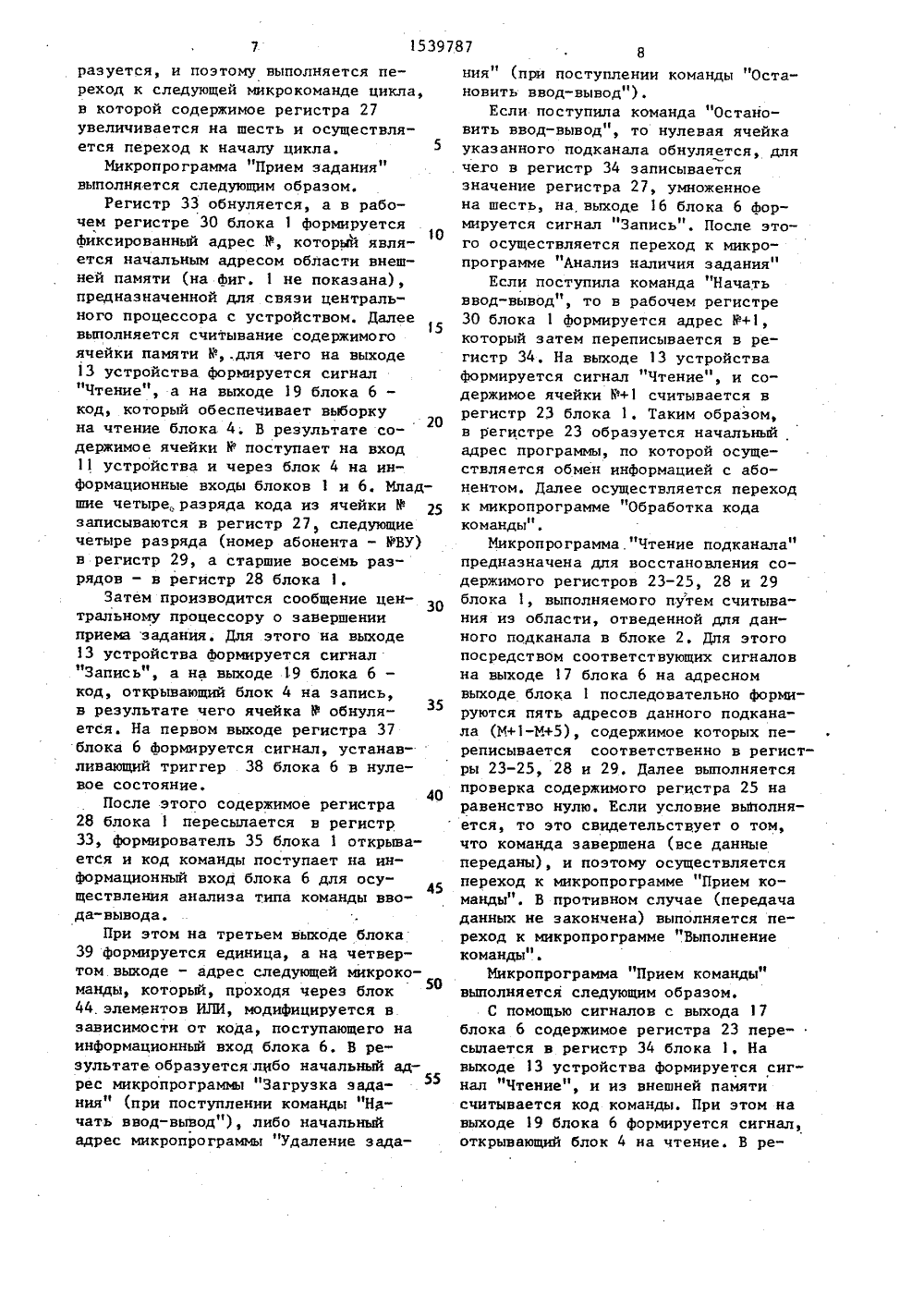

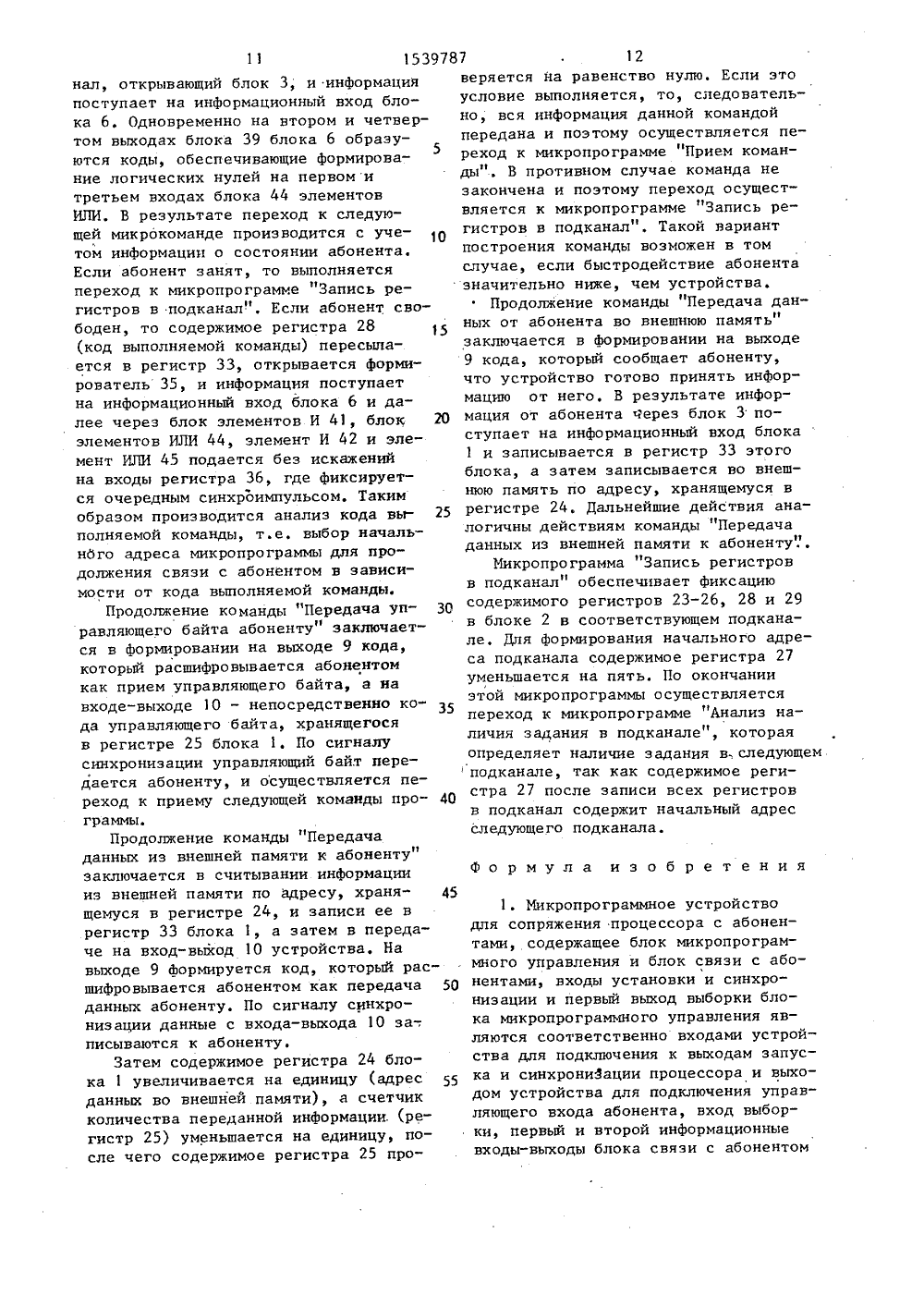

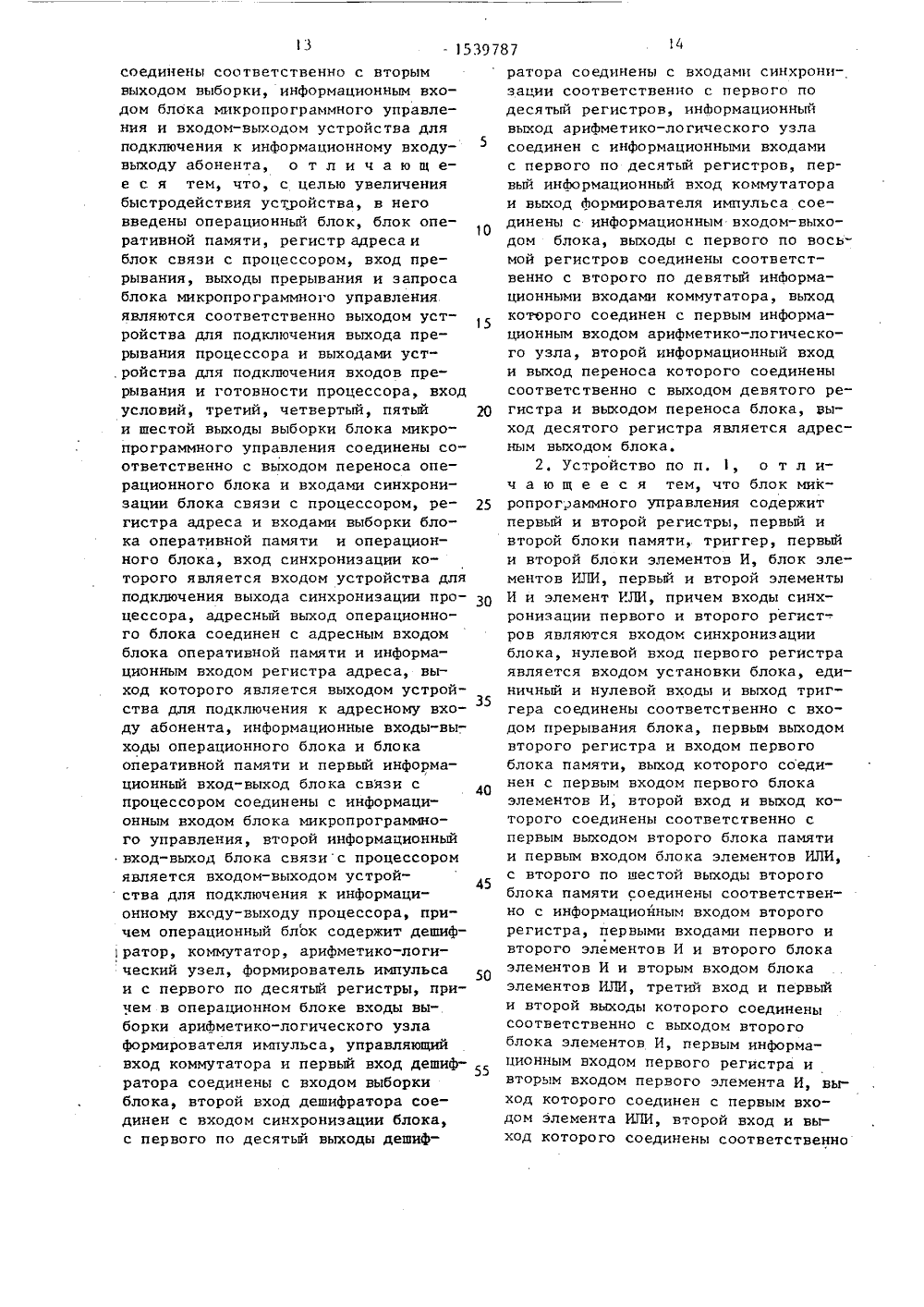

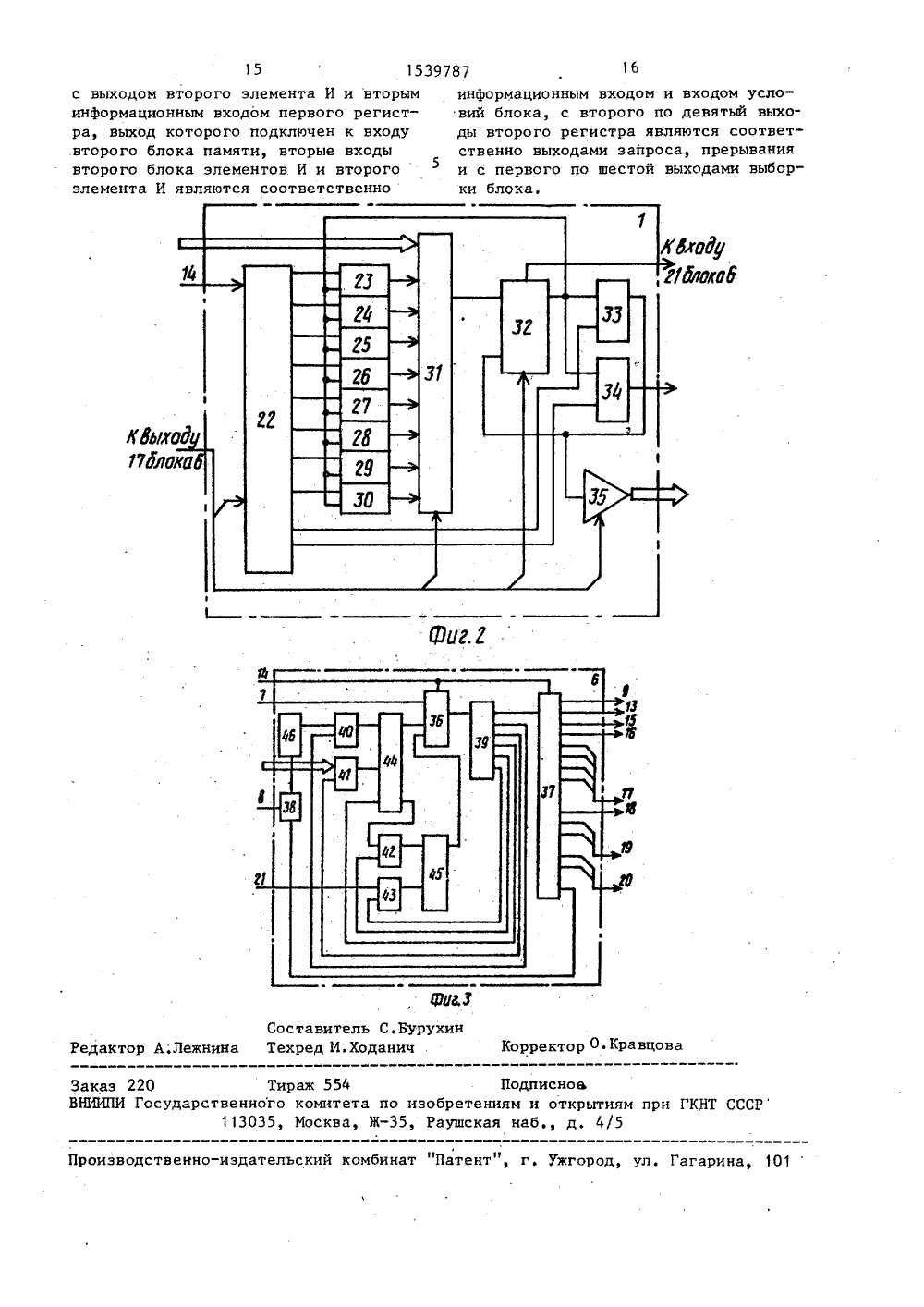

(51) 5 С 06 Р 13/00 ОПИСАНИЕ ИЗОБРЕТЕНК А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ СЕ 1: Е г",Ю И ОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯПРИ ГННТ СССР(21) 4344451/24-24 (22) 15.12,87 (46) .30.01.90. Вюл. У 4 (72) В.А.Гришин и П.Ю.Ярошевский (53) 681.3(088.8) (56) Авторское свидетельство СССР У 1252788, кл. С 06 Р 13/10, 1984.Авторское свидетельство СССР . М 1114099, кл. С 06 Р 300, 1982, (54) И 1 КРОПРОГРАЖШОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С АБОНЕНТАИИ (57) Изобретение относится к вычислительной технике н может быть использовано в системах обработки дан 7 2ных в качестве субпроцессора обмена информацией между абонентами и центральным процессором. Целью изобретения является повышение быстродействия устройства. Устройство содержит операционный блок 1, блок 2 оперативной памяти, блок 3 связи с абонентами, блок 4 связи с процессором; регистр 5 адреса, блок 6 микропрограммного управления. Устройство обеспечивает под управлением микропрограммы в блоке 6 скоростной двунаправленный обмен информацией между процессором и абонентом. 1 з.п. Ф-лы, 3 ил.Изобретение относится к вычислительной технике и может быть использовано в системах обработки данных в качестве субпроцессора обмена информацией между абонентами и цент 5 ральным процессором.Целью изобретения является увеличение быстродействия устройства., На Фиг, 1 представлена блок-схема предлагаемого устройства; нафиг.2 - схема операционного блока 1; на фиг. 3 " схема блока микропрограммно" го управления.Устройство содержит (фиг. 1) операционный блок 1, блок 2 оперативной памяти, блок 3 связи с абонентами, блок 4 связи с процессором, регистр 5 адреса, блок 6 микропрограммного управления, входы 7 и 8 устройства для подключения к выходам запуска и прерывания процессора, выход 9 устройства для подключения к управляющему входу абонента, входы"выходы 10 и 11 устройства для подключения к 25 информационным входам-выходам абонента и процессора соответственно, выходы 12 и 13 устройства для подключения к входам адреса и запроса абонента, вход 14 устройства для подключе-. ния выхода синхронизации процессора, выход 15 устройства для подключения. входа прерывания абонента, пятый 16, шестой 17, четвертый 18, третий 19 и второй 20 выходы выборки блока бмикропрограммного управления и вход 21 условий блока 6 микропрограммного управления.Операционный блок 1 содержит (фиг. 2) дешифратор 22, с первого по40 восьмой регистры 23-30, коммутатор 31, арифметико-логический узел 32, девятый 33 и десятый 34 регистры, формирователь 35 импульсаБлок б микропрограммного управления содержит первый и второй регистры 36 и 37, триггер 38, второй блок 39 памяти, первый и второй блоки элементов И 40 и 41, первый и второй элементы И 42 и 43, блок 44 элементов ИЛИ, элемент ИЛИ 45 и первый50 блок 46 памяти.Блок 3 связи с абонентами и блок 4 связи с процессором являются двунаправленными шинныьы формирователя 55 Устройство работает в следующихосновных режимах: выполнение процедуры "Загрузка задания в подканал";выполнение процедуры "Удаление задания из подканала";выполнение команды передачи данных из внешней памяти к абоненту;выполнение команды передачи данных от абонента во внешнюю память;выполнение команды передачи управляющего байта к абоненту;выполнение команды завершения программы.Кроме того, наличие микропрограммного управления позволяет создать более сложные команды передачи информации от центрального процессора к абоненту и обратно с различными видами преобразования информации.Устройство работает следующим образом.По сигналу "Пуск", поступающему на вход 7 устройства, обнуляется регистр 36 блока 6. В результате по нулевому адресу из блока 39 памяти вьг бирается первая микрокоманда, которая является началом микропрограммы "Установка устройства в исходное состояние".гВ результате на втором, третьем и шестом выходах блока 39 образуются сигналы логического нуля, на пятом выходе - сигнал логической единицы, а на первом выходе - код микрокоманды. Старшие разряды адреса следующей микрокоманды поступают с четвертого выхода блока 39 через блок элементов ИЛИ 44 на информационный вход регистра Зб, а младший разряд адреса следующей микрокоманды с второго выхода блока элементов ИЛИ 44 подается через элементы И 42 и ИЛИ 45 на второй информационный вход регистра 36, По заднему фронту синхроимпульса, поступающего на синхровход блока 6, в регистр 37 записывается микрокоманда из нулевого адреса, а в регистр Зб - адрес следующей микрокоманды. Таким образом, на выходах 9, 13, 15- 20 блока 6 формируются сигналы, обеспечивающие управление блоками устройства.Весь объем памяти блока 2 разделя- ется на группы по шесть ячеек памяти, называемые подканалами. Нулевая ячейка подканала содержит инфбрмацию о наличии (единица в младшем разряде ячейки) или отсутствии задачи (ноль в младшем разряде ячейки) в подкана1539787 6 В первой микрокоманде регистр 27блока 1 обнуляется, а далее начинается цикл, в котором анализируетсяналичие прерывания от центрального процессора или незавершенного задания в подканале. В первой микрокомандеэтого цикла на втором и третьем выходах блока 39 блока 6 формируются соответственно сигналы логической единицы и логического нуля, что обеспечивает формирование адреса следующей микрокоманды с учетом сигнала прерывания на входе 8 устройства. В томслучае, если такой сигнал есть, то.триггер 38 блока 6 устанавливается в единицу, в результате чего из блока46 выбирается код, который через блок 40 элементов И поступает на первый вход блока 44 элементов ИЛИ. Врезультате логического суммирования этого кода с адресом следующей микрокоманды, поступающей на третий входблока 44 элементов ИЛИ, образуется начальный адрес микропрограммы "Приемзадания", который поступает на первый и второй информационные входы регистра 36 и по заднему фронту синхроимпульса фиксируется в этом регистре. Таким образом осуществляется переход к микропрограмме "Прием задания".В том случае, если на входе 8 сигнал прерывания отсутствует, модификации адреса следующей микрокоманды не происходит и выполняется вторая микрокоманда цикла, в которой содержимое регистра 27 пересылается в регистр 34 и далее из блока 2 по адресу, указанному в регистре 34, считывается информация, которая записывается в регистр 26, Затем выполняется проверка содержимого регистра 26 наравенство нулю. Если это условие невыполняется, то на выходе переноса .узла 32 образуется сигнал логическойединицы, который поступает на вход21 блока 6, в результате чего происходит модификация младшего разряда адреса следующей микрокоманды, поступающего на третий вход блока 44элементов ИЛИ. Для вь:полнения модификации младший разряд адреса следующей микрокомандь 1 обязательно равеннулю, Таким образом осуществляется переход к началу микропрограммы "Чтение подканала . Если же содержимое регистра 26 равно нулю, то сигнал переноса на выходе узла 32 не обле. Поэтому для того, чтобы привести подканал в исходное положение, достаточно обнулить нулевые ячейки всех подканалов. Содержимое остальных ячеек в этом случае безразлично. Данная процедура выполняется следующим образом. На вход узла 32 блока 1 подается код с выхода 17 блока 6, который обеспечивает формирование нулевого кода на выходе узла 32, поступающего на информационный вход регистра 26. На вход дешифратора 22 с выхода 17 блока 6 подается код, обеспечивающий совместно с синхроимпуль сом, поступающим на синхровход дешифратора 22, формирование импульсного сйгнала на четвертом выходе дешифратора 22. В результате регистр 26 обнуляется. Аналогично обнуляется ре гистр 27 блока 1. Затем на вход коммутатора 31 с выхода 17 блока 6 подается код, обеспечивающий прохождение импульсов на выход коммутатора 31. Одновременно на вход узла 32 с выхода 25 17 блока 6 подается код, обеспечивающий прохождение .информации с первого входа блока 32 на его выход без искажений, На второй вход дешифратора 22 подается код, обеспечивающий сов местно с синхроимпульсом Формирование на девятом выходе дешифратора 22 импульсного сигнала, который производит запись информации на выходе узла 32. (значение регистра 26) в регистр .33. Таким же образом содержимое регистра 27 переписывается в регистр 34.В следующей микрокоманде на вход выборки формирователя блока 1 подается сигнал логической единицы, от крывающий формирователь 35, При этом на адресный и информационный входы блока 2 поступают коды с адресного и информационного выходов блока 1. На выходе 16 блока 6 формируется сигнал, 45 обеспечивающий запись нулевой информации по нулевому адресу.Далее содержимое регистра 27 блока 1 увеличивается на шесть (размер подканала) путем подачи соответствующих 50 кодов на выход 17 блока 6, а затем переписывается в регистр 34 блоха 1 и вновь производится запись нулевой информации в блок 2 по адресу, указанному в регистре 34 блока 1. Таким образом обнуляются все нулевые ячейки всех подканалов блока 2.Далее выполняется микропрограмма "Анализ наличия задания в подканале".разуется, и поэтому выполняется переход к следующей микрокоманде цикла,в которой содержимое регистра 27увеличивается на шесть и осуществляется переход к началу цикла.Микропрограмма "Прием задания"выполняется следующим образом,Регистр 33 обнуляется, а в рабочем регистре 30 блока 1 формируетсяфиксированный адрес У, которыи являОется начальным адресом области внешней памяти (на фиг. 1 не показана),предназначенной для связи центрального процессора с устройством. Далее15выполняется считывание содержимогоячейки памяти Р,.для чего на выходе13 устройства формируется сигнал"Чтение", а на выходе 19 блока 6 -код, который обеспечивает выборкуна чтение блока 4, В результате со 20держимое ячейки Р поступает на вход11 устройства и через блок 4 на инФормационные входы блоков 1 и 6. Младшие четыре разряда кода из ячейки 11 25записываются в регистр 27 следующиечетыре разряда (номер абонента - РВУ)в регистр 29, а старшие восемь разрядов - в регистр 28 блока 1.Затем производится сообщение центральному процессору о завершенииприема задания. Для этого на выходе13 устройства формируется сигнал"Запись", а на выходе 19 блока 6 -код, открывающий блок 4 на запись,в результате чего ячейка У обнуляется. На первом выходе регистра 37блока 6 формируется сигнал, устанавливающий триггер 38 блока 6 в нулевое состояние.После этого содержимое регистра28 блока 1 пересылается в регистр33, Формирователь 35 блока 1 открывается и код команды поступает на информационный вход блока 6 для осуществления анализа типа команды ввода-вывода.При этом на третьем выходе блока39 формируется единица, а на четвертом выходе - адрес следующей микрокоманды, который, проходя через блок44, элементов ИЛИ, модифицируется взависимости от кода, поступающего наинформационный вход блока 6, В результате образуется либо начальный адрес микропрограммы "Загрузка задания" (при поступлении команды "Начать ввод-вывод"), либо начальныйадрес микропрограммы "Удаление зада 15397878ния" (при поступлении команды "Остановить ввод-вывод),Если поступила команда "Остановить ввод-вывод", то нулевая ячейкауказанного подканала обнуляется, длячего в регистр 34 записываетсязначение регистра 27, умноженноена шесть, на выходе 16 блока 6 формируется сигнал "Запись", После этого осуществляется переход к микропрограмме "Анализ наличия задания"Если поступила команда "Начатьввод-вывод", то в рабочем регистре30 блока 1 формируется адрес 9+1,который затем переписывается в регистр 34, На выходе 13 устройстваформируется сигнал "Чтение", и содержимое ячейки 9+1 считывается врегистр 23 блока 1, Таким образом,в регистре 23 образуется начальныйадрес программы, по которой осуществляется обмен информацией с абонентом. Далее осуществляется переходк микропрограмме "Обработка кодакоманды".Микропрограмма."Чтение подканала"предназначена для восстановления содержимого регистров 23-25, 28 и 29блока 1, выполняемого путем считывания из области, отведенной для данного подканала в блоке 2. Для этогопосредством соответствующих сигналовна выходе 17 блока 6 на адресномвыходе блока 1 последовательно формируются пять адресов данного подканала (М+1-М+5), содержимое которых переписывается соответственно в регистры 23-25, 28 и 29. Далее выполняетсяпроверка содержимого регистра 25 наравенство нулю. Если условие выполня ется, то это свидетельствует о том,что команда завершена (все данныепереданы), и поэтому осуществляетсяпереход к микропрограмме "Прием команды". В противном случае (передачаданных не закончена) выполняется переход к микропрограмме "Выполнениекоманды",Микропрограмма "Прием команды"выполняется следующим образом.С помощью сигналов с выхода 17блока 6 содержимое регистра 23 пересылается в регистр 34 блока 1. Навыходе 13 устройства формируется сигнал "Чтение", и из внешней памятисчитывается код команды, При этом навыходе 19 блока 6 формируется сигнал,открывающий блок 4 на чтение. В ре1539787 1 О 15 20 25 30 35 45 50 зультате код команды поступает на информационные входы блоков 1 и 6. Старшие восемь разрядов записываются в регистр 28, а младшие восемь - в регистр 25 блока 1, Адрес следующей микрокоманды определяется кодом, поступающим на информационный вход блока 6, для чего на,вторые входы блока 41 элементов И подается сигнал логической единицы с соответствующего выхода блока 39.В том случае, если поступила команда безусловного перехода, переход осуществляется к микропрограмме "Безусловный переход", Во втором слове этой команды указывается адрес .следующей команды программы. Поэтомус помощью сигналов на выходе 17 блока 6 содержимое регистра 23 блока 1 увеличивается на единицу и записывается в регистр 34, Далее выполняется операция чтения внешней памяти по адресу в регистре 34, и инФормация записывается в регистр 23 блока 1, т.е, записывается адрес, следующей команды программы. На этом действия команды заканчиваются и осуществляется пере- . ход к микропрограмме "Прием команды"В том случае, если поступили команды "Передача данных из внешней памяти к абоненту" или "Передача данных от абонента во внешнюю память", переход осуществляется к началу микропрограммы, в которой содержимое регистра 23 блокаувеличивается на единицу, а затем из внешней памяти по адресу, указанному в регистре 23, считывается информация и записывается в регистр 24 блока 1. По смыслу эта информация представляет собой начальный адрес зоны внешней памяти, в которую или из которой дан-. ные передаются соответственно от абонента или к абоненту. Далее содержимое регистра 23 увеличивается на единицу и осуществляется переход к микропрограмме "Выполнение команды".Если поступила команда "Передача управляющего, байта абоненту", то осуществляется переход к микропрограьще, где содержимое регистра 23 увеличивается на единицу, а затем выполняется переход к микропрограмме "Выполнение команды".Если поступила команда "Завершение программы ввода-вывода", то осуществляется переход к микропрограмме, которая выполняется следующим обраОзом. В регистре 34 формируется адрес 9+2, по которому во внешнюю память записывается предварительно сформированное содержимое регистра 33, представляющее собой код завершения программы ввода-вывода по команде "Завершение программы ввода-вывода". Регистр 26 обнуляется, т.е. аннулируется признак наличия задания в подканале. Кроме того, на выходе 15 формируется сигнал "Прерывание", которым центральный процессор оповещается о завершении программы ввода-вывода, причем в ячейке 9+2 внешней памяти указана причина, по которой ввод-вывод завершен. Затем осуществляется переход к микропрограмме "Запись регистров в подканал"Микропрограмма "Выполнение команды" производит действия по организации связи между устройством и абонентом и передачу данных. По сигналу синхронизации, поступающему по одной из линий на выход 9(на остальных линиях код "Номер абонента" ), абонент, чей номер сформирован на входе-выходе 10, включается для дальнейшего продолжения сеанса связи. Затем на выходе 9 устанавливается код, который расшифровывается абонентом как признак необходимости сформировать ответ о том, что он включен. В результате на входе-выходе О образуется номер включившегося абонента, который поступает через блок 3 на информацион" ный вход блокаи записывается в регистр 30. Далее сравниваются номера включившегося и затребованного абонентов путем сравнения содержимого регистров 29 и 30. В том случае, если эти номера не совпадают, в регистре 33 формируется код ошибки "Неверная адресация"На этом действия программы заканчиваются, так как продолжение сеанса связи невозможно. Выполняется переход К микропрограмме, где производятся действия по доведению этого сообщения до центрального процессора.Если переданный номер и принятый номер абонента совпадают, то это свидетельствует о правильном включении абонента, и на выходе 9 формируется код, который абонентом расшифровывается" как сигнал о выдаче информации на вход"выход 10 о состоянии (свободен - занят) абонента. При этом на вход выборки блока 3 поступает сиг-, 1539787 1210 20 25 30 35 40 50 55 нал, открывающий блок 3, и информацияпоступает на информационный вход блока 6. Одновременно на втором и четвертом выходах блока 39 блока 6 образуются коды, обеспечивающие формирование логических нулей на первом итретьем входах блока 44 элементовИЛИ, В результате переход к следующей микрокоманде производится с учетом информации о состоянии абонента.Если абонент занят, то выполняетсяпереход к микропрограмме "Запись регистров в подканал". Если абонент свободен, то содержимое регистра 28(код выполняемой команды) пересылается в регистр 33, открывается формирователь 35, и информация поступаетна информационный вход блока 6 и далее через блок элементов И 41, блокэлементов ИЛИ 44, элемент И 42 и элемент ИЛИ 45 подается без искаженийна входы регистра 36, где Фиксируется очередным синхроимпульсом. Такимобразом производится анализ кода вьгполняемой команды, т.е, выбор начальнбго адреса микропрограммы для продолжения связи с абонентом в зависимости от кода выполняемой команды,Продолжение команды "Передача управляющего байта абоненту" заключается в формировании на выходе 9 кода,который расшифровывается абонентомкак прием управляющего байта, а навходе-выходе 10 - непосредственно кода управляющего байта, хранящегосяв регистре 25 блока 1. По сигналусинхронизации управляющий байт передается абоненту, и осуществляется переход к приему следующей команды программы,Продолжение команды "Передачаданных из внешней памяти к абоненту"заключается в считывании информациииз внешней памяти по адресу, хранящемуся в регистре 24, и записи ее врегистр 33 блока 1, а затем в передаче на вход-выход 10 устройства, Навыходе 9 формируется код, который расшифровывается абонентом как передачаданных абоненту. По сигналу синхронизации данные с входа-выхода 10 за-,писываются к абоненту.Затем содержимое регистра 24 блока 1 увеличивается на единицу (адресданных во внешней памяти), а счетчикколичества переданной информации. (регистр 25) уменьшается на единицу, после чего содержимое регистра 25 проверяется на равенство нулю. Если это условие выполняется, то, следовательно, вся информация данной командой передана и поэтому осуществляется переход к микропрограмме Прием команды", В противном случае команда незакончена и поэтому переход осуществляется к микропрограмме "Запись регистров в подканал". Такой вариантпостроения команды возможен в томслучае, если быстродействие абонентазначительно ниже, чем устройства,Продолжение команды "Передача данных от абонента во внешнюю память" заключается в Формировании на выходе 9 кода, который сообщает абоненту, что устройство готово принять информацию от него. В результате информация от абонента через блок 3 поступает на информационный вход блока 1 и записывается в регистр 33 этого блока, а затем записывается во внешнюю память по адресу, хранящемуся в регистре 24. Дальнейшие действия аналогичны действиям команды "Передачаданных из внешней памяти к абоненту"Микропрограмма "Запись регистров в подканал" обеспечивает фиксацию содержимого регистров 23-26, 28 и 29 в блоке 2 в соответствующем подканале. Для формирования начального адреса подканала содержимое регистра 27 уменьшается на пять, По окончании этой микропрограммы осуществляется переход к микропрограмме "Анализ наличия задания в подканале", которая определяет наличие задания в.,следующемподканале, так как содержимое регистра 27 после записи всех регистровв подканал содержит начальный адресследующего подканала.Формула изобретения1, Микропрограммное устройство для сопряжения процессора с абонентами, содержащее блок микропрограммного управления и блок связи с абонентами, входы установки и синхронизации и первый выход выборки блока микропрограммного управления являются соответственно входами устройства для подключения к выходам запуска и синхронизации процессора и выходом устройства для подключения управляющего входа абонента, вход выборки, первый и второй информационные входы-выходы блока связи с абонентомсоединены соответственно с вторым выходом выборки, информационным входом блока микропрограммного управления и входом-выходом устройства для подключения к информационному входу- выходу абонента, о т л и ч а ю щ ее с я тем, что, с целью увеличения быстродействия устройства, в него введены операционный блок, блок оперативной памяти, регистр адреса и блок связи с процессором, вход прерывания, выходы прерывания и запроса блока микропрограммного управления являются соответственно выходом устройства для подключения выхода прерывания процессора и выходами уст.ройства для подключения входов прерывания и готовности процессора, вход условий, третий, четвертый, пятый и шестой выходы выборки блока микропрограммного управления соединены соответственно с выходом переноса операционного блока и входами синхронизации блока связи с процессором, регистра адреса и входами выборки блока оперативной памяти и операционного блока, вход синхронизации которого является входом устройства для подключения выхода синхронизации процессора, адресный выход операционного блока соединен с адресным входом блока оперативной памяти и информационным входом регистра адреса, выход которого является выходом устройства для подключения к адресному входу абонента, информационные входы-выходы операционного блока и блока оперативной памяти и первый информационный вход-выход блока связи с процессором соединены с информационным входом блока микропрограммного управления, второй информационный вход-выход блока связис процессором является входом-выходом устрой ства для подключения к информационному входу-выходу процессора, причем операционный блок содержит дешифратор, коммутатор, арифметико-логический узел, формирователь импульса и с первого по десятый регистры, причем в операционном блоке входы выборки арифметико-логического узла формирователя импульса, управляющий вход коммутатора и первый вход дешифратора соединены с входом выборки блока, второй вход дешифратора соединен с входом синхронизации блока, с первого по десятый выходы дешиф 5 1 О 15 20 25 30 35 40 45 50 55 ратора соединены с входами синхронизации соответственно с первого подесятый регистров, информационныйвыход арифметико-логического узласоединен с информационными входамис первого по десятый регистров, первый информационный вход коммутатораи выход формирователя импульса соединены с информационным входом-выходом блока, выходы с первого по восьмой регистров соединены соответственно с второго по девятый информационными входами коммутатора, выходкоторого соединен с первым информационным входом арифметико-логического узла, второй информационный входи выход переноса которого соединенысоответственно с выходом девятого регистра и выходом переноса блока, выход десятого регистра является адресным выходом блока,2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок микропрограммного управления содержитпервый и второй регистры, первый ивторой блоки памяти, триггер, первыйи второй блоки элементов И, блок элементов ИЛИ, первый и второй элементыИ и элемент ИЛИ, причем входы синхронизации первого и второго регистров являются входом синхронизацииблока, нулевой вход первого регистраявляется входом установки блока, единичный и нулевой входы и выход триггера соединены соответственно с входом прерывания блока, первым выходомвторого регистра и входом первогоблока памяти, выход которого соединен с первым входом первого блокаэлементов И, второй вход и выход которого соединены соответственно спервым выходом второго блока памятии первым входом блока элементов ИЛИ,с второго по шестой выходы второгоблока памяти соединены соответственно с информационным входом второгорегистра, первыми входами первого ивторого элементов И и второго блокаэлементов И и вторым входом блокаэлементов ИЛИ, третий вход и первыйи второй выходы которого соединенысоответственно с выходом второгоблока элементов И, первым информационным входом первого регистра ивторым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно.Ходанич Корректор О. Кравцова Соста Редактор А.Лежнина ТехреЗаказ 220 Тираж 554 ПодписноьВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д, 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 10 с выходом второго элемента И и вторыминформационным входом первого регистра, выход которого подключен к входувторого блока памяти, вторые входывторого блока элементов И и второгоэлемента И являются соответственно информационным входом и входом условий блока, с второго по девятый выходы второго регистра являются соответственно выходами запроса, прерыванияи с первого по шестой выходами выборки блока,

СмотретьЗаявка

4344451, 15.12.1987

ПРЕДПРИЯТИЕ ПЯ В-8185

ГРИШИН ВЛАДИМИР АЛЕКСЕЕВИЧ, ЯРОШЕВСКИЙ ПАВЕЛ ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 13/00

Метки: абонентами, микропрограммное, процессора, сопряжения

Опубликовано: 30.01.1990

Код ссылки

<a href="https://patents.su/8-1539787-mikroprogrammnoe-ustrojjstvo-dlya-sopryazheniya-processora-s-abonentami.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство для сопряжения процессора с абонентами</a>

Предыдущий патент: Устройство для приоритетного обращения к общей многомодульной памяти

Следующий патент: Устройство для сопряжения двух магистралей

Случайный патент: Устройство для контроля дискретных объектов