Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

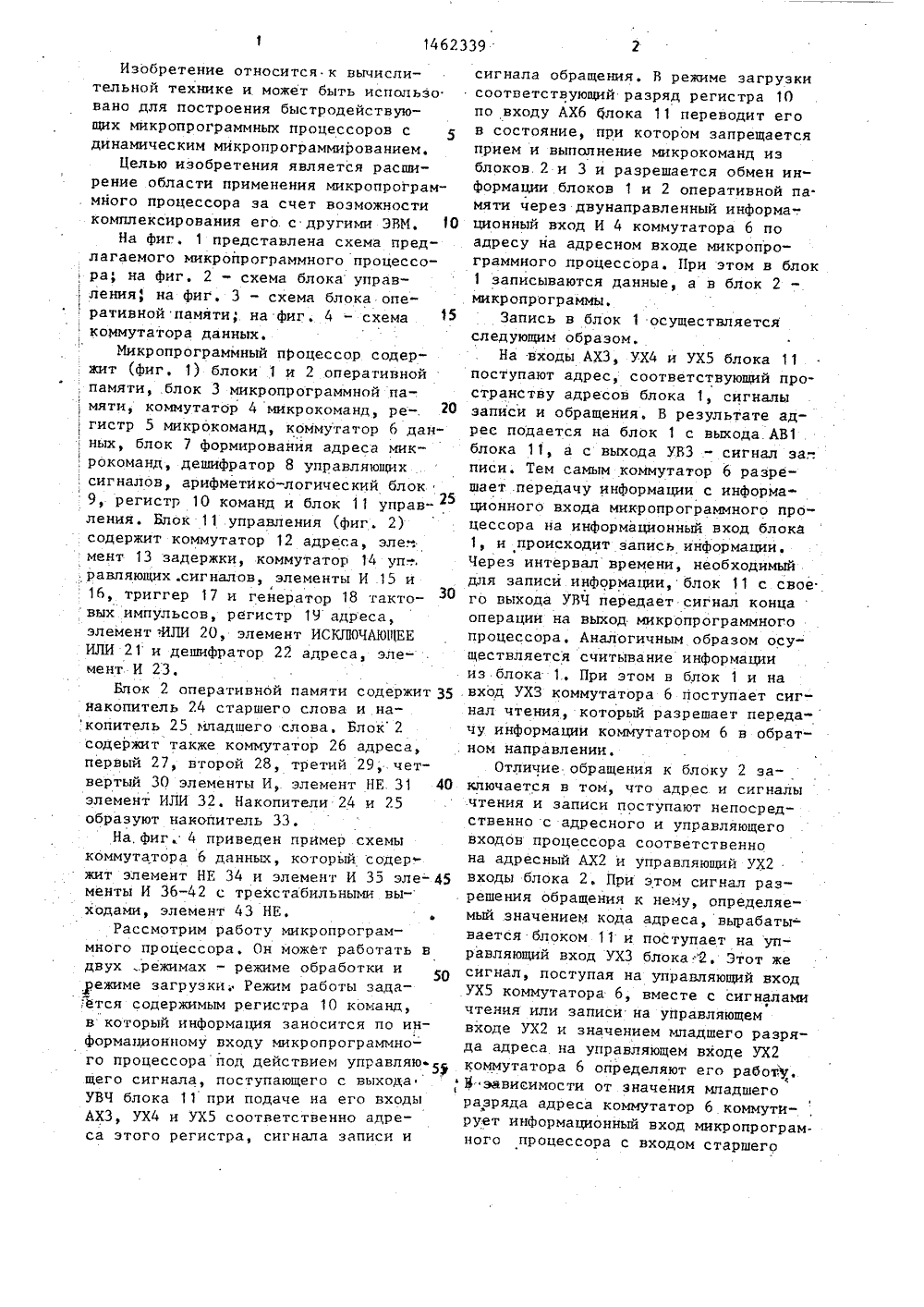

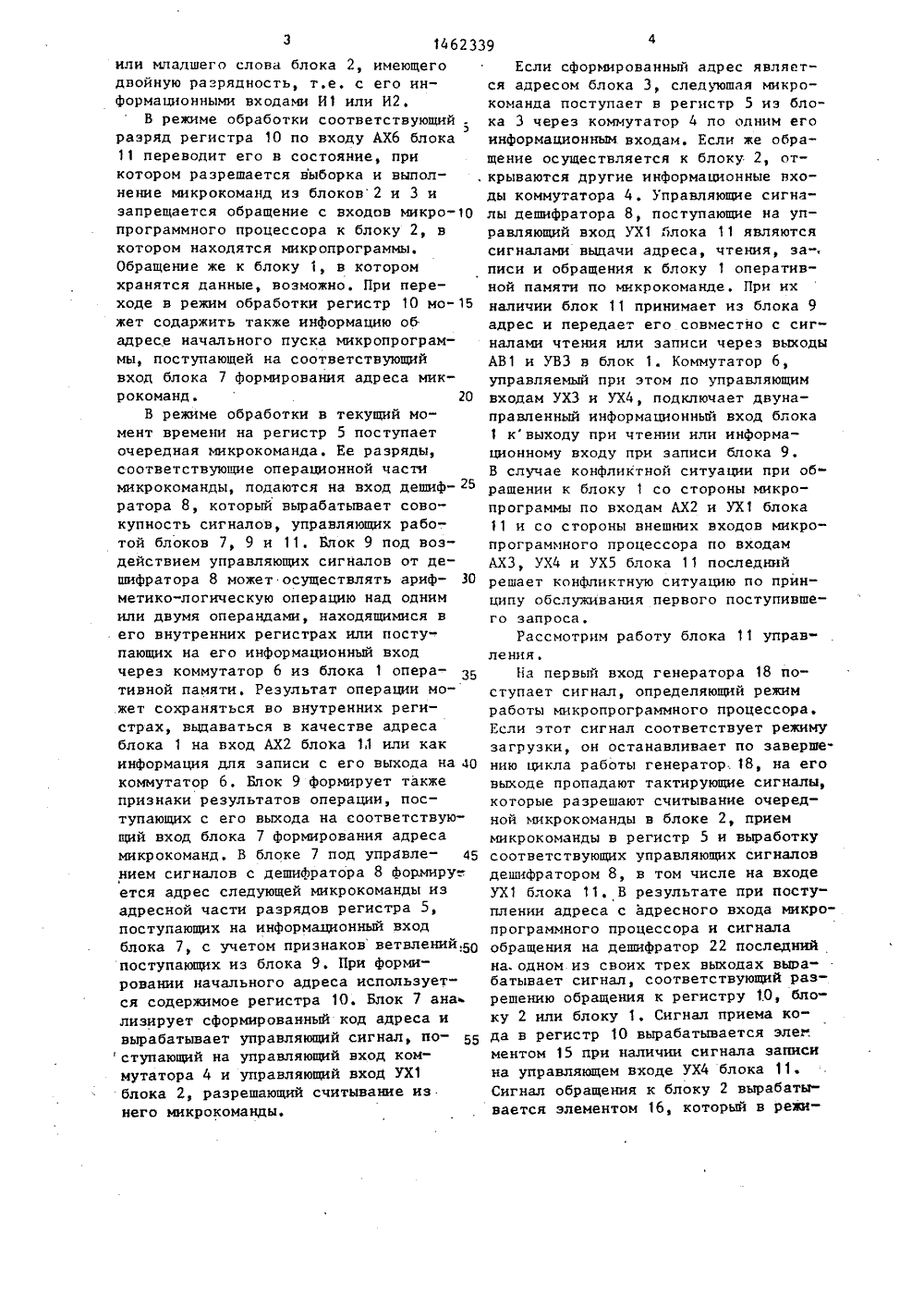

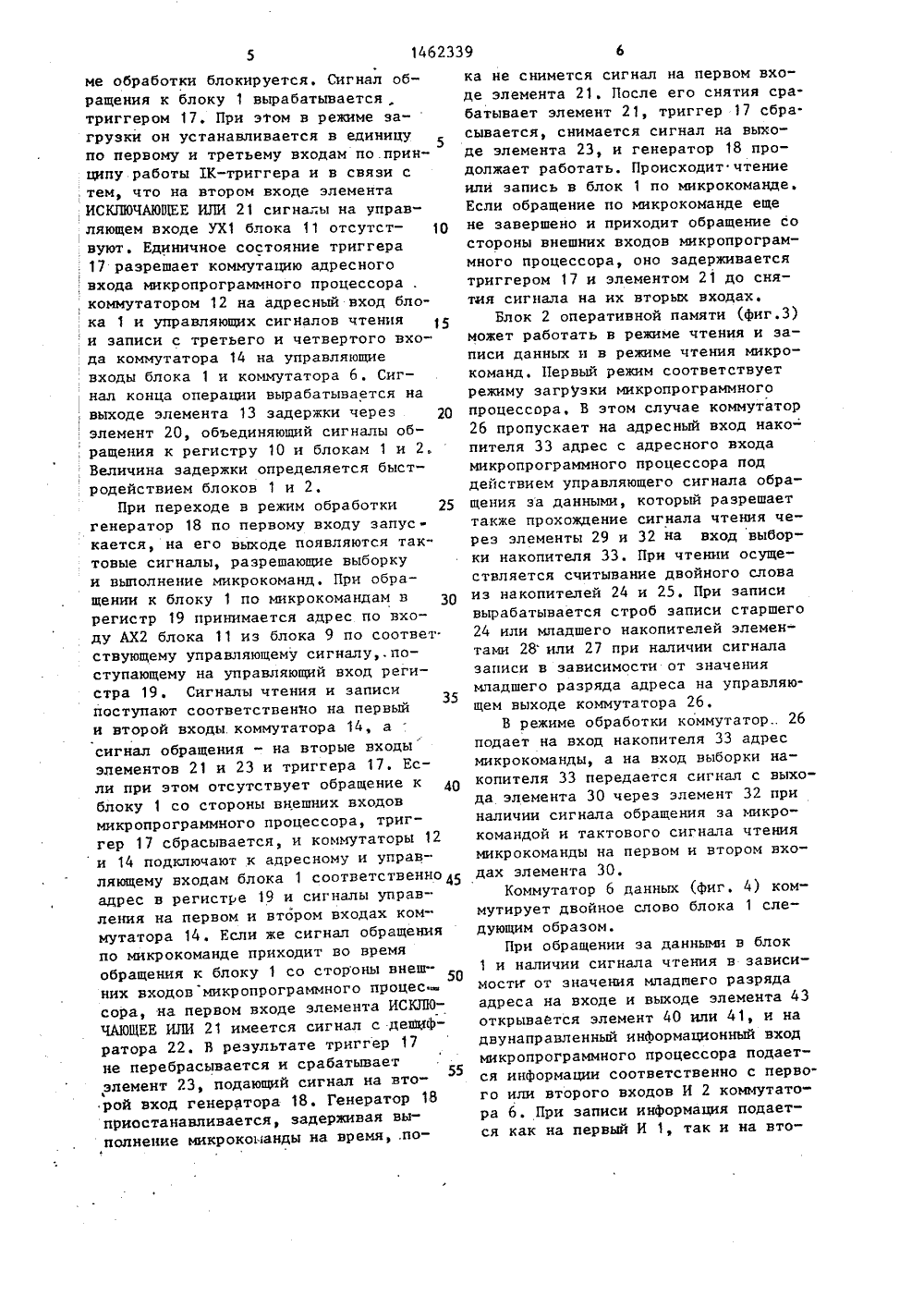

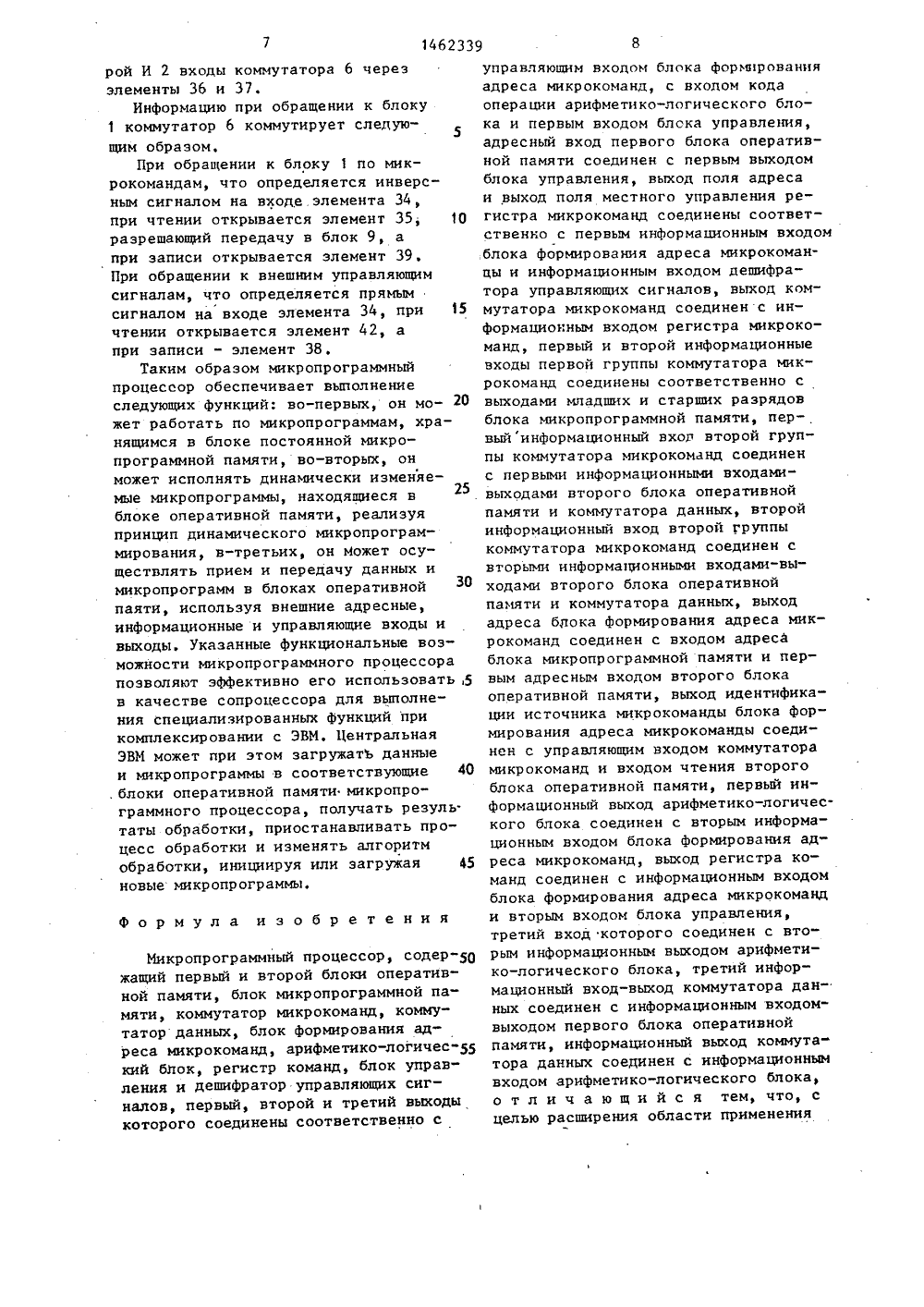

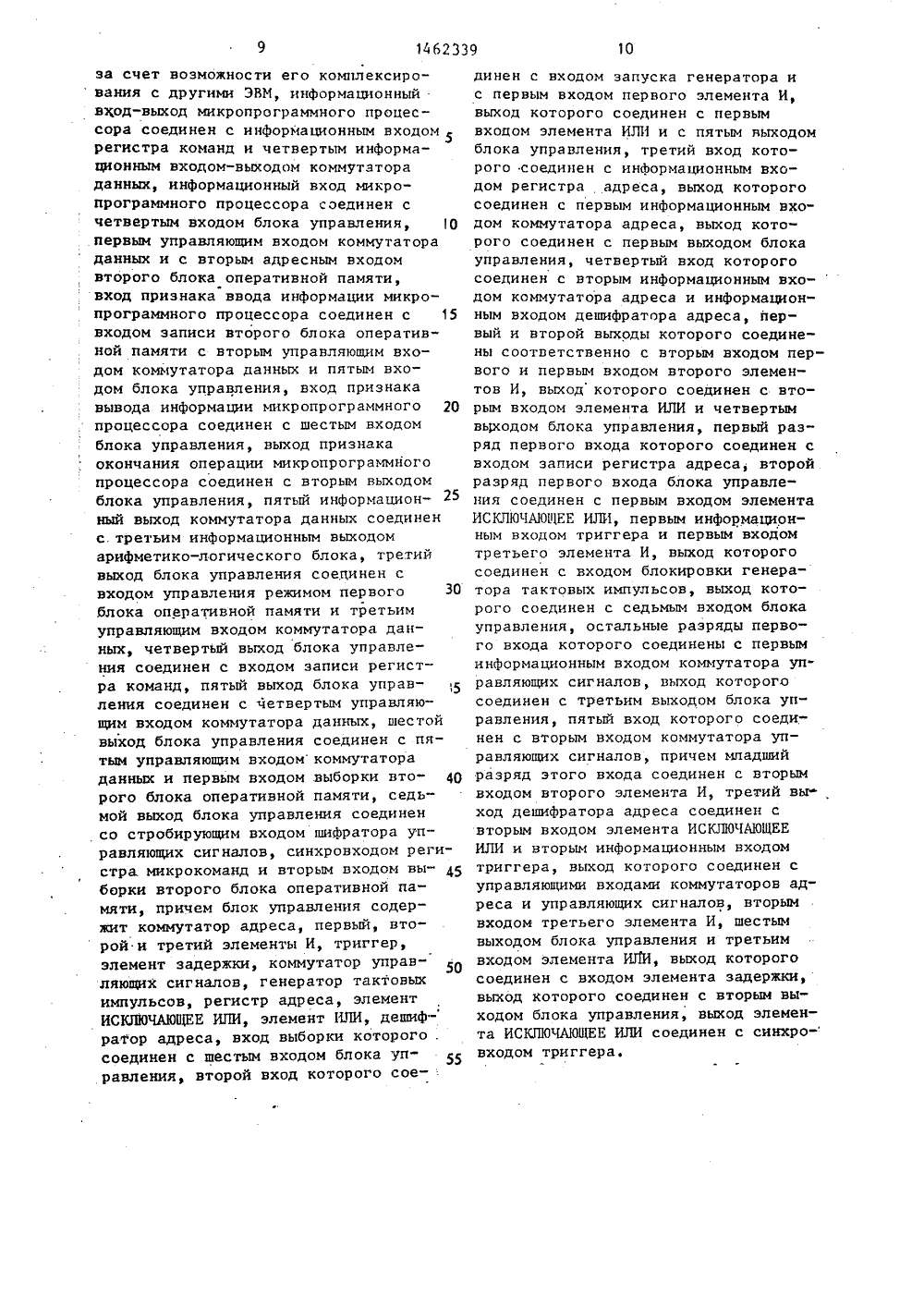

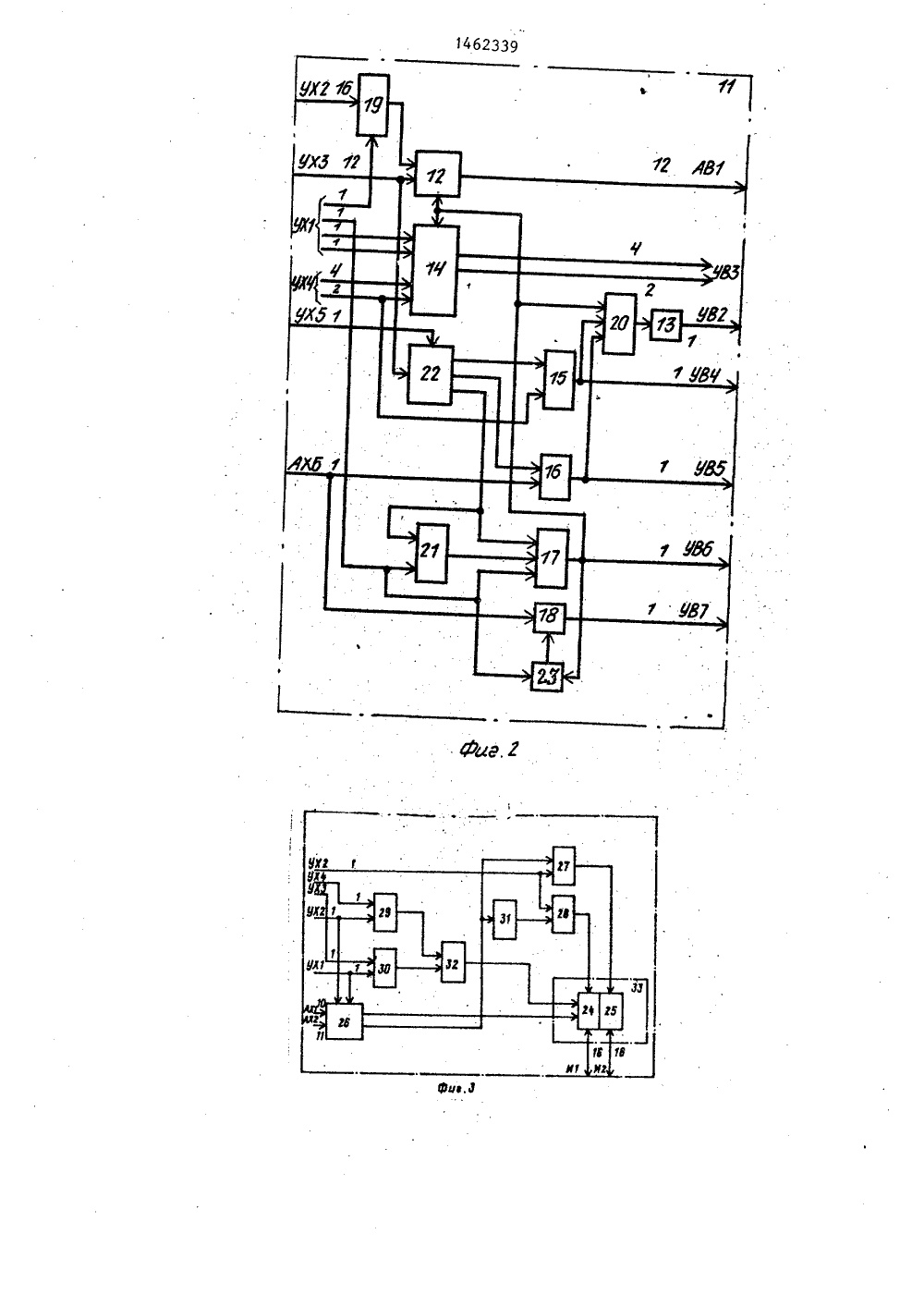

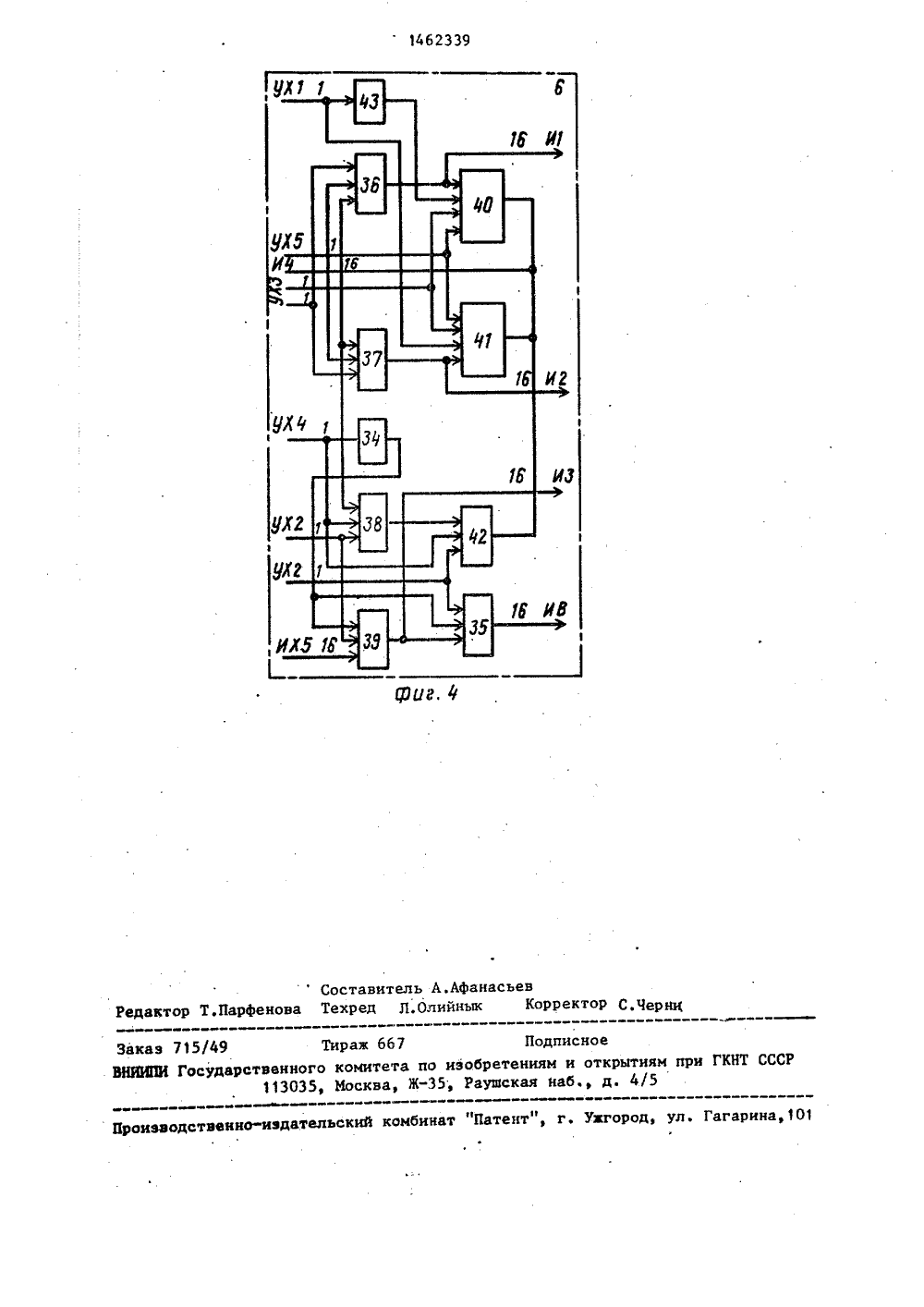

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1 (И) Я 94 С 06 Р 15/О 3 "ЕОЕо",",.,3АТЕ Лз" ь ЛЕБЫкЛ Ь 1":)д 1"3ИСАНИЕ ИЗОБРЕТЕНИЯ ГОСУДАРСТВЕННЫЙ КОМИТЕТ ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение относится к вычислительной технике и может быть использовано для построения быстродействуюших микропрограммных процессоров с динамическим микропрограммированием. Цель изобретения - расширение области нрименения микропрограммного процессора засчет комплексирования его с другим ЭВМ. Микропрограммный процессор содержит блоки 1 и 2 оперативной памяти, блок 3 микропрограммной памяти, коммутатор 4 микрокоманд, регистр 5 микрокоманд, коммутатор 6 данных, блок 7 формирования адреса микрокоманд, дешифратор 8 управлякщих сигналов, арифметико-логический блок 9, регистр 10 команд и блок 11 управлеж. ния, 4 ил.Изобретение относится к вычислительной технике и может быть использовано для построения быстродействуюшнх микРопрограммных процессоров с 5динамическим микропрограммированием.Целью изобретения является расширение области применения микропрограммного процессора за счет возможностикомплексирования его с другими ЭВМ, 1 ОНа фиг. 1 представлена схема предлагаемого микропрограммного процессо: ра, на фиг. 2 - схема блока управ ления, на фиг. 3 - схема блока опе ративной памяти, на фиг, 4 - схемакоммутатора данных.Микропрограммный процессор содержит (фиг. 1) блоки 1 и 2 оперативной. Равляющих .сигналов, элементы И 15 и16, триггер 17 и генератор 18 тактовых.импульсов, регистр 19 адреса,элемент ФИЛИ 20, элемент ИСКЛЮЧАЮЩЕЕИЛИ 21 и дешифратор 22 адреса, элемент И 23,Елок 2 оперативной памяти содержит 35накопитель 24 старшего слова и накопитель 25 младшего слова. Блок 2содержит также коммутатор 26 адреса,первый 27, второй 28, третий 29 четвертый 30 элементы И,. элемент НЕ 31 40элемент ИЛИ 32. Накопители 24 и 25образуют накопитель 33.На, фиг. 4 приведен прнмер схемыкоммутатора 6 данных, который содержит элемент НЕ 34 и элемент И 35 элементы И 36-42 с трехстабильными выходами, элемент 43 НЕ,Рассмотрим работу микропрограммного процессора, Он может работать вдвух .режимах - режиме обработки иРежиме загрузки. Режим работы зада.:ется содержимым регистра 10 команд,в который информация заносится по информанионному входу микропрограммного процессора под действием управляю 5щего сигнала, поступающего с выходаУВЧ блока 11 при подаче на его входыАХЗ, УХ 4 и УХ 5 соответственно адреса этого регистра, сигнала записи и сигнала обращения. В режиме загрузки соответствующий разряд регистра 10 по входу АХ 6 Члока 11 переводит его в состояние, при котором запрещается прием и выполнение микрокоманд из блоков. 2 и 3 и разрешается обмен информации блоков 1 и 2 оперативной па. мяти через двунаправленный информа. ционный вход И 4 коммутатора 6 по адресу на адресном входе микропрограммного лроцессора. При этом в блок 1 записываются данные, а в блок 2 микропрограммы,Запись в блок 1 осуществляется следующим образом.На входы АХЗ, УХ 4 и УХ 5 блока 11 поступают адрес, соответствующий пространству адресов блока 1, сигналы записи и обращения, В результате адрес подается на блок 1 с выхода. АВ 1 блока 11, а с выхода УВЗ " сигнал за.". писи. Тем самым коммутатор 6 разрешает .передачу информации с информационного входа микропрограммного процессора на информационный вход блока 1, и происходит запись информации. Через интервал времени, необходимый для записи информации, блок 11 с свое го выхода УВЧ передает сигнал конца операции на выход микропрограммного процессора. Аналогичным образом осуществляется считывание информации из блока 1. При этом в блок 1 и на вход УХЗ коммутатора 6 поступает сигнал чтения, который разрешает передачу информации коммутатором б в обрат. ном направлении.Отличие обращения к блоку 2 заключается в том, что адрес и сигналычтения и записи поступают непосредственно с адресного и управляющеговходов процессора соответственнона адресный АХ 2 и управляющий УХ 2входы блока 2. При этом сигнал разрешения обращения к нему, определяемый значением кода адреса, вырабаты-вается блоком 11 и поступает на управляющий вход УХЗ блока 2. Этот жесигнал, поступая на управляющий входУХ 5 коммутатора 6, вместе с сигналамичтения или записи на управляющемвходе УХ 2 и значением младшего разряда адреса на управляющем входе УХ 2коммутатора 6 определяют его работУ.с , М эависимости от значения младшегоразряда адреса коммутатор б коммутирует информационный вход микропрограмного процессора с входом старшегоЕсли сформированный адрес является адресом блока 3, следуюшая микро- команда поступает в регистр 5 иэ блока 3 через коммутатор 4 по одним его информационным входам. Если же обращение осуществляется к блоку 2, открываются другие информационные входы коммутатора 4. Управляющие сигналы дешифратора 8, поступающие на управляющий вход УХ 1 блока 11 являются сигналами выдачи адреса, чтения, за-, писи и обращения к блоку 1 оперативной памяти по микрокоманде. При их наличии блок 11 принимает из блока 9 адрес и передает его совместно с сигналами чтения или записи через выходы АВ и УВЗ в блок 1. Коммутатор 6, управляемый при этом по управляющим входам УХЗ и УХ 4, подключает двунаправленный информационный вход блока 1 квыходу при чтении или информационному входу при эаписи блока 9.В случае конфликтной ситуации при обращении к блокусо стороны микропрограммы по входам АХ 2 и УХ 1 блока 1 и со стороны внешних входов микропрограммного процессора по входам АХЗ, УХ 4 и УХ 5 блока 11 последний решает конфликтную ситуацию по принципу обслуживания первого поступившего запроса.Рассмотрим работу блока 11 управления.На первый вход генератора 18 поступает сигнал, определяющий режим работы микропрограммного процессора, Если этот сигнал соответствует режиму загрузки, он останавливает по заверше" нию цикла работы генератор. 8, на его выходе пропадают тактирующие сигналы, которые разрешают считывание очередной микрокоманды в блоке 2, прием микрокоманды в регистр 5 и выработку соответствующих управляющих сигналов дешифратором 8, в том числе на входе УХ 1 блока 11. В результате при поступлении адреса с адресного входа микропрограммного процессора и сигнала обращения на дешифратор 22 последний на. одном из своих трех выходах вырабатывает сигнал, соответствующий разрешению обращения к регистру 10, блоку 2 или блоку 1, Сигнал приема кода в регистр 10 вырабатывается эле. ментом 15 при наличии сигнала записи на управляющем входе УХ 4 блока 11, Сигнал обращения к блоку 2 вырабатывается элементом 16, который в резиз 146233 или младшего слова блока 2, имеющего двойную разрядность, т.е. с его информационными входами И 1 или И 2.В режиме обработки соответствующий .3 разряд регистра 10 по входу АХ 6 блока11 переводит его в состояние, при котором разрешается выборка и выполнение микрокоманд иэ блоков 2 и 3 изапрещается обращение с входов микропрограммного процессора к блоку 2, в котором находятся микропрограммы. Обращение же к блоку 1, в котором хранятся данные, возможно. При переходе в режим обработки регистр 10 мо жет содаржить также информацию об адресе начального пуска микропрограммы, поступающей на соответствующий вход блока 7 формирования адреса микрокоманд. 20В режиме обработки в текущий момент времени на регистр 5 поступаеточередная микрокоманда. Ее разряды, соответствующие операционной части микрокоманды, подаются на вход дешиф ратора 8, который вырабатывает совокупность сигналов, управляющих работой блоков 7, 9 и 11, Блок 9 под воздействием управляющих сигналов от дешифратора 8 может осуществлять ариф метико-логическую операцию над одним или двумя операндами, находящимися в его внутренних регистрах или поступающих на его информационный вход через коммутатор 6 из блока 1 оперативной памяти. Результат операции может сохраняться во внутренних регистрах, выдаваться в качестве адреса блока 1 на вход АХ 2 блока 1,1 или как информация для записи с его выхода на 40 коммутатор 6, Блок 9 формирует также признаки результатов операции, поступающих с его выхода на соответствующий вход блока 7 формирования адреса микрокоманд. В блоке 7 под управле нием сигналов с дешифратора 8 формиру- ется адрес следующей микрокоманды иэ адресной части разрядов регистра 5, поступающих на информационный вход блока 7, с учетом признаковветвлений.5 О поступающих из блока 9. При формировании начального адреса используется содержимое регистра 10. Блок 7 ана лизирует сформированный код адреса и вырабатывает управляющий сигнал, по ступающий на управляющий вход коммутатора 4 и управляющий вход УХ 1 блока 2, разрешающий считывание из него микрокоманды.. тем, что на втором входе элементаИСКЛЮЧАЮЩЕЕ ИЛИ 21 сигналы на управляющем входе УХ 1 блока 11 отсутствуют. Единичное состояние триггера, 17 разрешает коммутацию адресного; коммутатором 12 на адресный вход блока 1 и управляющих сигналов чтенияи записи с третьего и четвертого входа коммутатора 14 на управляющиевходы блока 1 и коммутатора 6Сиг. нал конца операции вырабатывается на: элемент 20, объединяющий сигналы об: ращения к регистру 10 и блокам 1 и 2Величина задержки определяется быстродействием блоков 1 и 2,При переходе в режим обработки 25генератор 18 по первому входу запускается, на его выходе появляются тактовые сигналы, разрешающие выборкуи выполнение микрокоманд. При обращении к блоку 1 по микрокомандам врегистр 19 принимается адрес по входу АХ 2 блока 11 из блока 9 по соответ.ствующему управляющему сигналу,.поступающему на управляющий вход регистра 19. Сигналы чтения и записипоступают соответственно на первыйи второй входы. коммутатора 14, асигнал обращения - на вторые входыэлементов 21 и 23 и триггера 17. Если при этом отсутствует обращение кблоку 1 со стороны внешних входовмикропрограммного процессора, триггер 17 сбрасывается, и коммутаторы 12и 14 подключают к адресному и управляющему входам блока 1 соответственно 45адрес в регистре 19 и сигналы управления на первом и втором входах коммутатора 14. Если же сигнал обращенияпо микрокоманде приходит во времяобращения к блоку 1 со стороны внешних входов микропрограммного процессора, на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 21 имеется сигнал с деапратора 22, В результате триггер 17не перебрасывается и срабатываетэлемент 23, подающий сигнал на второй вход генератора 18. Генератор 18приостанавливается, задерживая выполнение микрокоыанды на время, .пока не снимется сигнал на первом вхо" де элемента 21. После его снятия срабатывает элемент 21, триггер 17 сбрасывается, снимается сигнал на выходе элемента 23, и генератор 18 продолжает работать. Происходит чтение или запись в блок 1 по микрокоманде. Если обращение по микрокоманде еще не завершено и приходит обращение со стороны внешних входов микропрограммного процессора, оно задерживается триггером 17 и элементом 21 до снятия сигнала на их вторых входах.Блок 2 оперативной памяти (фиг.3) может работать в режиме чтения и записи данных н в режиме чтения микро- команд, Первый режим соответствует режиму загрузки микропрограммного процессора. В этом случае коммутатор 26 пропускает на адресный вход нако- пителя 33 адрес с адресного входа микропрограммного процессора под действием управляющего сигнала обращения за данными, который разрешает также прохождение сигнала чтения через элементы 29 и 32 на вход выборки накопителя 33При чтении осуществляется считывание двойного слова из накопителей 24 и 25. При записи вырабатывается строб записи старшего 24 или младшего накопителей элементами 28 или 27 при наличии сигнала записи в зависимости от значениямладшего разряда адреса на управляющем выходе коммутатора 26.В режиме обработки коммутатор 26 подает на вход накопителя 33 адрес микрокоманды, а на вход выборки накопителя 33 передается сигнал с выхода элемента 30 через элемент 32 при наличии сигнала обращения за микро- командой и тактового сигнала чтения микрокоманды на первом и втором входах элемента 30,Коммутатор 6 данных (фиг, 4) коммутирует двойное слово блока 1 следующим образом.При обращении за данными в блок 1 и наличии сигнала чтения в зависимости от значения младшего разряда адреса на входе и выходе элемента 43 открывается элемент 40 или 41, и на двунаправленный информационный вход микропрограммного процессора подается информации соответственно с первого или второго входов И 2 коммутатора 6. При записи информация подается как на первый И 1, так и на вто 1462339рой И 2 входы коммутатора 6 черезэлементы 36 и 37.Информацию при обращении к блоку1 коммутатор Ь коммутирует следую 5щим образом,При обращении к блокупо микрокомандам, что определяется инверсным сигналом на входе. элемента 34,при чтении открывается элемент 35, 10разрешающий передачу в блок 9, апри записи открывается элемент 39.При обращении к внешним управляющимсигналам, что определяется прямымсигналом на входе элемента 34, при 15чтении открывается элемент 42, апри записи - элемент 38,Таким образом микропрограммныйпроцессор обеспечивает выполнениеследующих функций: во-первых, он может работать по микропрограммам, хранящимся в блоке постоянной микропрограммной памяти, во-вторых, онможет исполнять динамически изменяемые микропрограммы, находящиеся вблоке оперативной памяти, реализуяпринцип динамического микропрограммирования, в-третьих, он может осуществлять прием и передачу данных имикропрограмм в блоках оперативнойпаяти, используя внешние адресные,информационные и управляющие входы ивыходы. Указанные функциональные возможности микропрограммного процессорапозволяют эффективно его использовать,5в качестве сопроцессора для выполнения специализированных функций прикомплексировании с ЭВМ. ЦентральнаяЭВМ может при этом загружать данныеи микропрограммы в соответствующие 40. блоки оперативной памяти микропрограммного процессора, получать резуль.таты обработки, приостанавливать процесс обработки и изменять алгоритмобработки, инициируя или загружая 45новые микропрограммы.формула изобретенияМикропрограммный процессоР, сойеР "50 жащий первый и второй блоки оперативной памяти, блок микропрограммной памяти, коммутатор микрокоманд, коммутатор данных, блок формирования адРеса микрокоманд, арифметико-логический блок, регистр команд, блок управления и дешифратор управляющих сигналов, первый, второй и третий выходы которого соединены соответственно с управляющим входом блока формированияадреса микрокоманд, с входом кодаоперации арифметико-логического блока и первым входом блока управления,адресный вход первого блока оперативной памяти соединен с первым выходомблока управления, выход поля адресаи выход поля местного управления регистра микрокоманд соединены соответственно с первым информационным входомблока формирования адреса микрокоманцы и информационным входом дешифратора управляющих сигналов, выход коммутатора микрокоманд соединен с информационным входом регистра микрокоманд, первый и второй информационныевходы первой группы коммутатора микрокоманд соединены соответственно свыходами младших и старших разрядовблока микропрограммной памяти, первый информационный вход второй группы коммутатора микрокоманд соединенс первыми информационными входамивыходами второго блока оперативнойпамяти и коммутатора данных, второйинформационный вход второй группыкоммутатора микрокоманд соединен свторыми информационными входами-выходами второго блока оперативнойпамяти и коммутатора данных, выходадреса бЛока формирования адреса микрокоманд соединен с входом адресаблока микропрограммной памяти и первым адресным входом второго блокаоперативной памяти, выход идентификации источника микрокоманды блока формирования адреса микрокоманды соединен с управляющим входом коммутаторамикрокоманд и входом чтения второгоблока оперативной памяти, первый информационный выход арифметико-логического блока соединен с вторым информационным входом блока формирования адреса микрокоманд, выход регистра команд соединен с информационным входомблока формирования адреса микрокоманди вторым входом блока управления,третий вход которого соединен с вторым информационным выходом арифметико-логического блока, третий информационный вход-выход коммутатора данных соединен с информационным входомвыходом первого блока оперативнойпамяти, информационный выход коммутатора данных соединен с информационнымвходом арифметико-логического блока,о т л и ч а ю щ и й с я тем, что, сцелью расширения области примененияза счет воэможности его комплексиро вания с другими ЗВИ, информационныйвход-выход микропрограммного процессора соединен с информационным входом5регистра команд и четвертым информационным входом-выходом коммутатораданных, информационный вход микропрограммного процессора соединен счетвертым входом блока управления, 1 Опервым управляющим входом коммутатораданных и с вторым адресным входомвторого блока оперативной памяти,вход признака ввода информации микропрограммного процессора соединен с 15входом записи второго блока оперативной памяти с вторым управляющим входом коммутатора данных и пятым входом блока управления, вход признака вывода информации микропрограммного 20 процессора соединен с шестым входомблока управления, выход признакаокончания операции микропрограммного процессора соединен с вторым выходомблока управления, пятый информационный выход коммутатора данных соединенс.третьим информационным выходомарифметико-логического блока, третийвыход блока управления соединен свходом управления режимом первого 30 блока оперативной памяти и третьим управляющим входом коммутатора данных, четвертый выход блока управления соединен с входом записи регистра команд, пятый выход блока управления соединен с четвертым управляющим входом коммутатора данных, шестой выход блока управления соединен с пятым управляющим входом коммутатора данных и первым входом выборки вто рого блока оперативной памяти, седьмой выход блока управления соединен со стробирующим входом шифратора управляющих сигналов, синхровходом регистра. микрокоманд и вторым входом вы борки второго блока оперативной памяти, причем блок управления содержит коммутатор адреса, первый, вто рой и третий элементы И, триггер,элемент задержки, коммУтатоР Управляющих сигналов, генератор тактовых импульсов, регистр адреса, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ, дешиф- ратор адреса, вход выборки которого . соединен с шестым входом блока управления, второй вход которого сое-: динен с входом запуска генератора ис первым входом первого элемента И,выход которого соединен с первымвходом элемента ИЛИ и с пятым выходомблока управления, третий вход которого соединен с информационным входом регистра адреса, выход которогосоединен с первым информационным входом коммутатора адреса, выход которого соединен с первым выходом блокауправления, четвертый вход которогосоединен с вторым информационным вхо-дом коммутатора адреса и информационным входом дешифратора адреса, первый и второй выходы которого соединены соответственно с вторым входом первого и первым входом второго элементов И, выход которого соединен с вторым входом элемента ИЛИ и четвертымвыходом блока управления, первый разряд первого входа которого соединен свходом записи регистра адреса, второйразряд первого входа блока управления соединен с первым входом элементаИСКЛЮЧАЮЩЕЕ ИЛИ, первым информационным входом триггера и первым входомтретьего элемента И, выход которогосоединен с входом блокировки генератора тактовых импульсов, выход которого соединен с седьмым входом блокауправления, остальные разряды первого входа которого соединены с первыминформационным входом коммутатора управляющих сигналов, выход которогосоединен с третьим выходом блока управления, пятый вход которого соединен с вторым входом коммутатора управляющих сигналов, причем младшийразряд этого входа соединен с вторымвходом второго элемента И, третий выход дешифратора адреса соединен свторым входом элемента ИСКЛЮЧАЮЩЕЕИЛИ и вторым информационным входомтриггера, выход которого соединен суправляющими входами коммутаторов адреса и управляющих сигналов, вторымвходом третьего элемента И, шестымвыходом блока управления и третьимвходом элемента ИЙ 4, выход которогосоединен с входом элемента задержки,выход которого соединен с вторым выходом блока управления, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с синхро-входом триггера.1462339 Составитель А.АфанасьевТ.Парфенова Техред Д.Олийнык Корректор С.Черни едакт Подписно СССР ственно-издательский комбинат "Патент", г. ужгород, ул. Гагарина, 10 Про ЗаказВНИИИИ 15/49Госуда Тираж 667 венного комитет 113035, Москва,изобретениям и открытиям при5, Раушская наб., д. 4/5

СмотретьЗаявка

4105418, 09.06.1986

ПРЕДПРИЯТИЕ ПЯ А-7358

АСТАХОВ ГЕННАДИЙ БОРИСОВИЧ, ГАЛИЧ ВАДИМ ПЕТРОВИЧ, ИВАНОВ ВЛАДИМИР АНДРЕЕВИЧ, СЫРОВ ВИКТОР ВАЛЕНТИНОВИЧ, ТРУФАНОВ СЕРГЕЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 28.02.1989

Код ссылки

<a href="https://patents.su/8-1462339-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Многоканальное устройство для подключения абонентов к общей магистрали

Следующий патент: Устройство сопряжения вычислительных машин

Случайный патент: Датчик влажности