Процессор для выполнения математических операций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

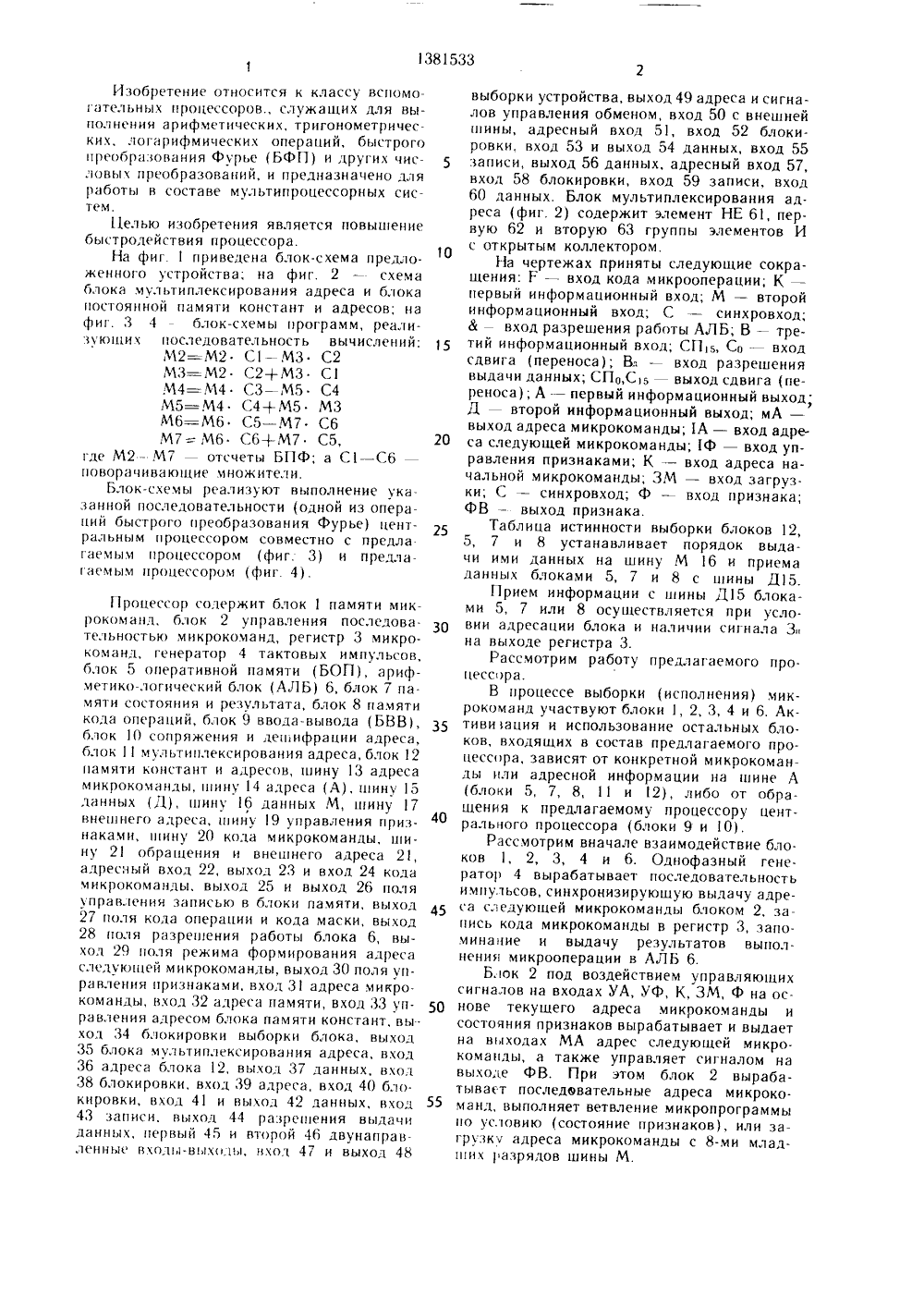

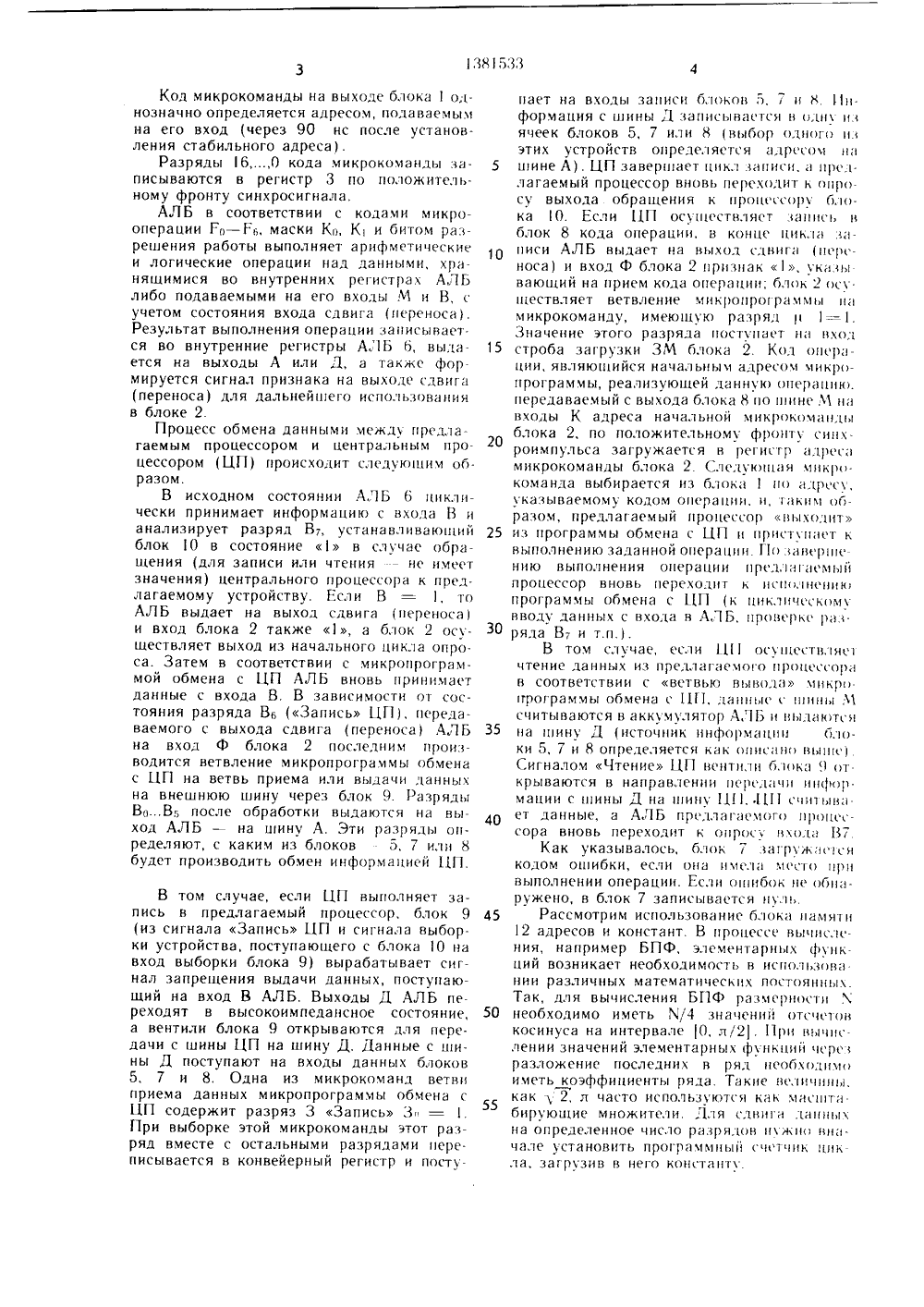

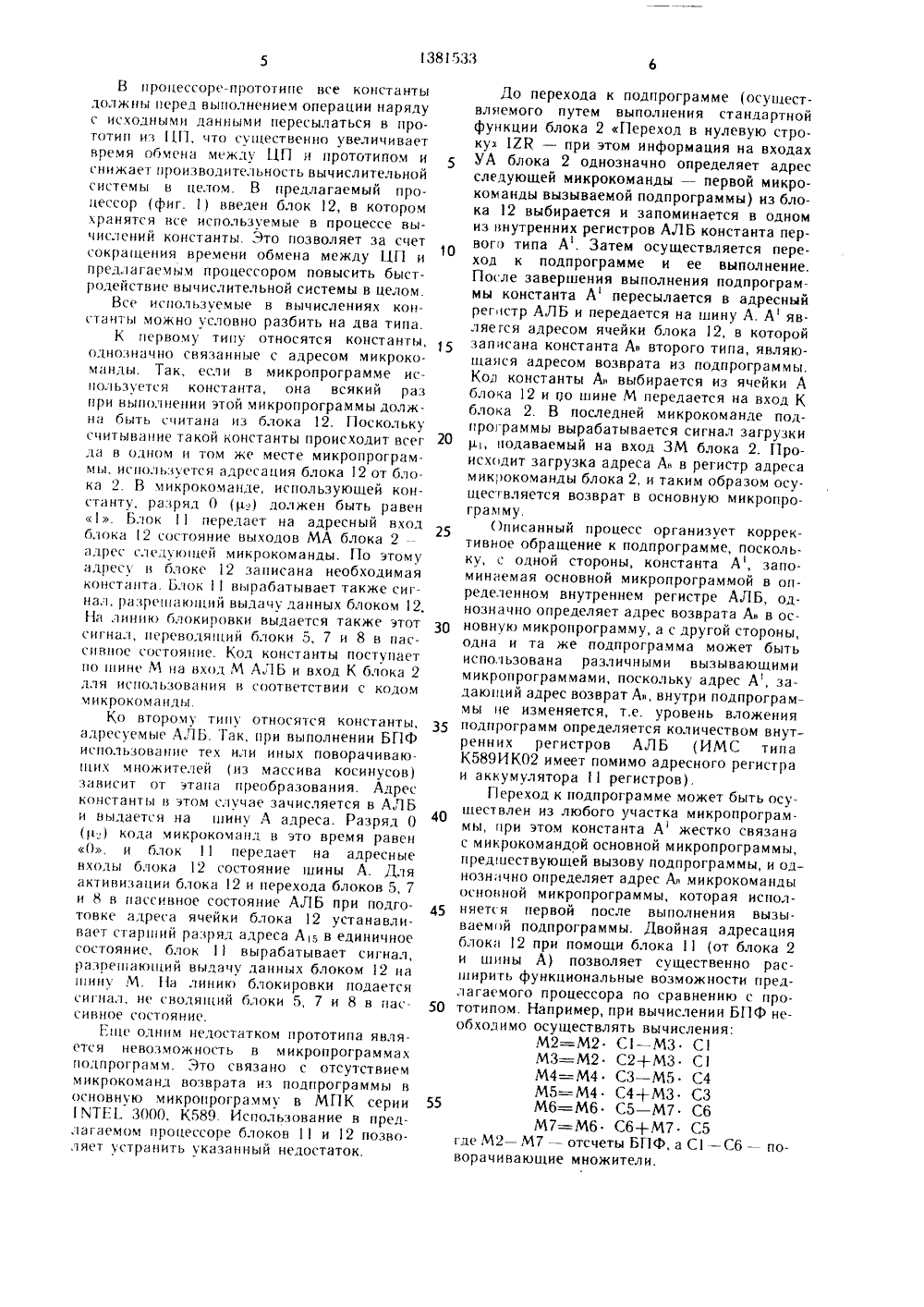

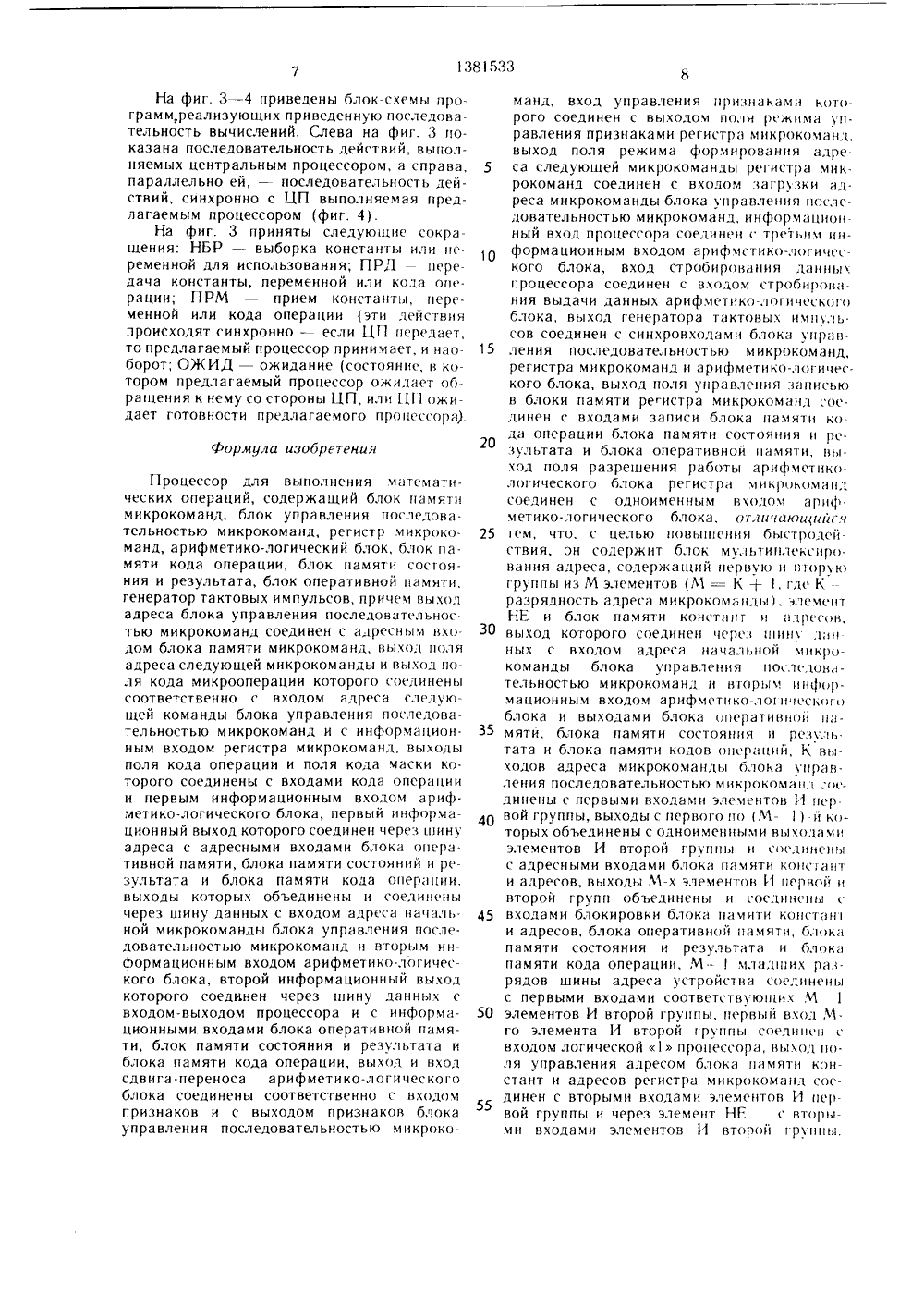

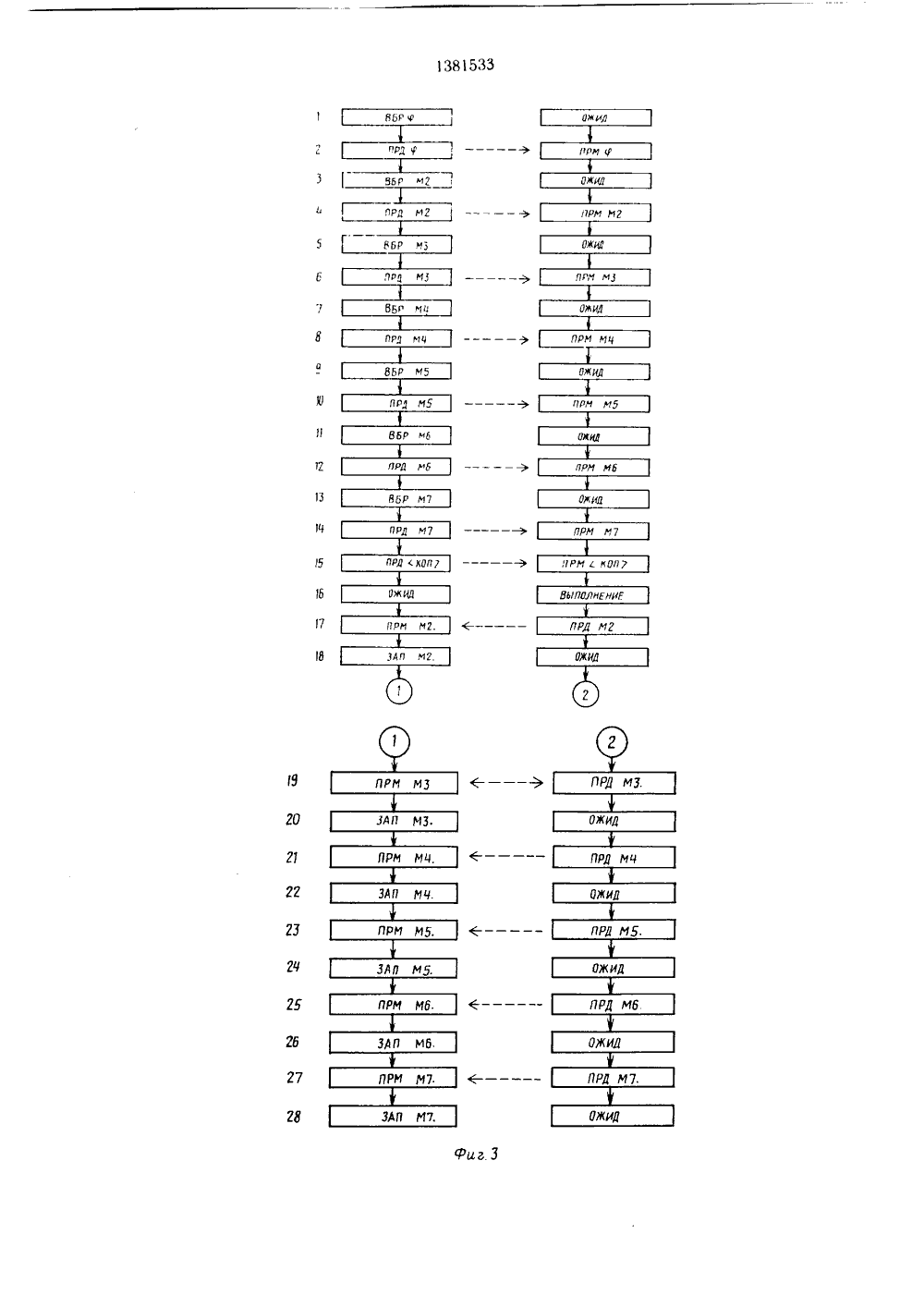

(50 4 6 15 0 АНИЕ ИЗОБРЕТЕН асьянов цессоры для тических опесистемах. интегральные бовского, М.: Микропроцесго быстродей 1 и др ышенно язь, 198 кадит ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ВТОРСНОМ,Ф СВИДЕТЕЛЬСТ(56) Вспомогательные прбыстрого выполнения арифмраций в микропроцессорныхЭлектроника, 1980,10.Аналоговые и цифровыесхемы./ Под ред, С. В. ЯкСоветское радио, 1979Березенко А. И.сорные комплекты повствия М: Радио и св(54) ПРОЦЕССОР ДЛЯ ВЫПОЛНЕНИЯ МАТЕМАТИЧЕСКИХ ОПЕРАЦИГ 1(57) Изобретение относится к классу вспомогательных процессоров, служащих для выполнения арифметических, тригонометрических, логарифмических операций, быстрого преобразования Фурье и других числовых преобразований, и предназначено для работы в составе мультипроцессорных систем. Цель изобретения - повышение быстродействия процессора. Процессор содержит блок 1 па. мяти микрокоманд, блок 2 управления последовательностью микрокоманд, регистр 3 микрокоманд, генератор 4 тактовых имп)льсов, блок 5 оперативной памяти, арифметикологический блок 6, блок 7 памяти состоя. ния и результата, блок 8 памяти кода операции, блок 9 ввода-вывода, блок О сопряжения и дешифрации адреса. Введение блока 11 мультиплексирования адреса и б 1 о 12 памяти констант и адресов привок достижению цели. 4 илИзобретение относится к классу вспомогательных процессоров., служащих для выполнения арифметических, тригонометрических, логарифмических операций, быстрого преобразования Фурье (БФП) и других числовых преобразований, и предназначено для работы в составе мультипроцессорных систем.Целью изобретения является повышение быстродействия процессора.На фиг. 1 приведена блок-схема предложенного устройства; на фиг. 2 - схема блока мультиплексирования адреса и блока постоянной памяти констант и адресов; на фиг. 3 4 блок-схемы программ, реализукщих последовательность вычислений:М 2=М 2 С -- МЗ С 2М 3= М 2 С 2+МЗ СМ 4=М 4 СЗ - М 5 С 4М 5=М 4 С 4+М 5 МЗМ 6=М 6 С 5 - М 7 СбМ 7= Мб Сб+М 7 С 5, 20 где М 2 - М 7 отсчеты БПФ; а С 1 - Сб поворачивающие множители.Блок-схемы реализуют выполнение указанной последовательности (одной из операций быстрого преобразования Фурье) центральным процессором совместно с предла гаемым процессором (фиг. 3) и предлагаемым процессором (фиг. 4). Процессор содержит блок 1 памяти микрокоманд, блок 2 управления последовательностью микрокоманд, регистр 3 микро- команд, генератор 4 тактовых импульсов, блок 5 оперативной памяти (БОП), арифметико-логический блок (АЛБ) 6, блок 7 памяти состояния и результата, блок 8 памяти кола операций, блок 9 ввода-вывода (БВВ), блок 10 сопряжения и дешифрации адреса, блок 11 мультиплексирования адреса, блок 12 памяти констант и адресов, шину 13 адреса микрокоманды, шину 14 адреса (А), шину 15 данных (Д), шину 16 данных М, шину 17 внешнего адреса, шину 19 управления приз наками, шину 20 кода микрокоманды, шину 21 обращения и внешнего адреса 21, адресный вход 22, выход 23 и вход 24 кода микрокоманды, выход 25 и выход 26 поля управления записью в блоки памяти, выход 45 27 поля кода операции и кода маски, выход 28 поля разрешения работы блока 6, выход 29 поля режима формирования адреса следукнцей микрокоманды, выход 30 поля управления признаками, вход 31 адреса микро- команды, вход 32 адреса памяти, вход 33 управления адресом блока памяти констант, выход 34 блокировки выборки блока, выход 35 блока мультиплексирования адреса, вход 36 адреса блока 12, выход 37 данных, вход 38 блокировки, вход 39 адреса, вход 40 бло.кировки, вход 41 и выход 42 данных, вход 55 43 записи, выход 44 разрешения выдачи данных, первый 45 и второй 46 двунаправленные входы-выходы, вход 47 и выход 48 выборки устройства, выход 49 адреса и сигналов управления обменом, вход 50 с внешней шины, адресный вход 51, вход 52 блокировки, вход 53 и выход 54 данных, вход 55 записи, выход 56 данных, адресный вход 57, вход 58 блокировки, вход 59 записи, вход 60 данных. Блок мультиплексирования адреса (фиг. 2) содержит элемент НЕ 61, первую 62 и вторую 63 группы элементов И с открытым коллектором.На чертежах приняты следующие сокращения: Г - вход кода микрооперации; К - первый информационный вход; М - второй информационный вход; С - синхровход; Ь вход разрешения работы АЛБ; В - третий информационный вход; СП, Со - вход сдвига (переноса); В -- вход разрешения выдачи данных; СПО,С выход сдвига (переноса); А - первый информационный выход; Д второй информационный выход; мА - выход адреса микрокоманды; 1 А - вход адреса следующей микрокоманды; 1 Ф - вход управления признаками; К - вход адреса начальной микрокоманды; ЗМ - вход загрузки; С - синхровход; Ф - вход признака; ФВ - выход признака.Таблица истинности выборки блоков 12, 5, 7 и 8 устанавливает порядок выдачи ими данных на шину М б и приема данных блоками 5, 7 и 8 с шины Д 15.Прием информации с шины Д 15 блоками 5, 7 или 8 осуществляется при условии адресации блока и наличии сигнала 3 на выходе регистра 3.Рассмотрим работу предлагаемого процессра.В процессе выборки (исполнения) микрокоманд участвуют блоки 1, 2, 3, 4 и 6. Активиация и использование остальных блоков, входящих в состав предлагаемого процессора, зависят от конкретной микрокоманды или адресной информации на шине А (блоки 5, 7, 8, 11 и 2), либо от обращения к предлагаемому процессору центрального процессора (блоки 9 и 10).Рассмотрим вначале взаимодействие блоков 1, 2, 3, 4 и 6. Однофазный генератор 4 вырабатывает последовательность импульсов, синхронизирующую выдачу адреса следующей микрокоманды блоком 2, запись кода микрокоманды в регистр 3, запоминание и выдачу результатов выполнения микрооперации в АЛБ 6.Блок 2 под воздействием управляюгцих сигналов на входах УА, УФ, К, ЗМ, Ф на основе текущего адреса микрокоманды и состояния признаков вырабатывает и выдает на выходах МА адрес следующей микро- команды, а также управляет сигналом на выходе ФВ. При этом блок 2 вырабатывает последввательные адреса микрокоманд, выполняет ветвление микропрограммы по условию (состояние признаков), или загрузку адреса микрокоманды с 8-ми младших )азрядов шины М.Код микрокоманды на выходе блокаоднозначно определяется адресом, подаваемым на его вход (через 90 нс после установления стабильного адреса).Разряды 160 кода микрокоманды записываются в регистр 3 по положительному фронту синхросигнала.АЛБ в соответствии с кодами микро- операции Го - Егмаски Ко, К и битом разрешения работы выполняет арифметические и логические операции над данными, хранящимися во внутренних регистрах А:1 Ь либо подаваемыми на его входы М и В, с учетом состояния входа сдвига (переноса). Результат выполнения операции записывает. ся во внутренние регистры АЛБ 6, выдается на выходы А или Д, а также формируется сигнал признака на выходе сдвига (переноса) для дальнейшего использования в блоке 2.Процесс обмена данными междл предлагаемым процессором и центральным процессором (ЦП) происходит следуюцим образом.В исходном состоянии АЛЬ 6 циклически принимает информацию с входа В и анализирует разряд В 7, устанзвл ива югций блок 10 в состояние 1 в случае обращения (для записи или чтения - не имеет значения) центрального процессора к предлагаемому устройству. Если В = 1, то АЛБ выдает на выход сдвига (цереносз) и вход блока 2 также 1, а блок 2 осуществляет выход из начального цикла опроса. Затем в соответствии с микропрограммой обмена с ЦП АЛБ вновь принимает данные с входа В. В зависимости от состояния разряда В (Запись ЦП), передаваемого с выхода сдвига (переноса) АЛБ на вход Ф блока 2 последним производится ветвление микропрограммы обмена с ЦП на ветвь приема или выдачи данных на внешнюю шину через блок 9. Разряды ВВ;, после обработки выдаются нз выход АЛБ - на шину А. Эти разряды определяют, с каким из блоков 5, 7 или 8 будет производить обмен информацией ЦП. В том случае, если ЦП выполняет запись в предлагаемый процессор, блок 9 (из сигнала Запись ЦП и сигнала выборки устройства, поступающего с блока О на вход выборки блока 9) вырабатывает сигнал запрещения выдачи данных, поступающий на вход В АЛБ. Выходы Д АЛБ переходят в высокоимпедансное состояние, а вентили блока 9 открываются для передачи с шины ЦП на шину Д. Данные с шины Д поступают на входы данных блоков 5, 7 и 8. Одна из микрокоманд ветви приема данных микропрограммы обмена с ЦП содержит разряз 3 Запись 3 = . При выборке этой микрокоманды этот разряд вместе с остальными разрядами переписывается в конвейерный регистр и поступает на входы записи блкоц 5, 7 и 8. 1 иформация с шины Д записывзтся в одцл из ячеек блоков 5, 7 или 8 (выбор однго цз этих устройств определяется адрсоч цз 5 шине А). ЦП завершает цикл записи, и прдлагаемый процессор вновь переходит к оцр- су выхода обращения к процссору блока 10. Если ЦП осуществляет запись в блок 8 кода операции, в конце цикла записи АЛБ выдает на выход сдвига (цр- носа) и вход Ф блока 2 признак 1, указывающий на прием кода операции; блок 2 осчществляет ветвление микропрогра ч м ы цз микрокоманду, имеющую разряд= Значение этого разряда поступает цз вход 15 строба загрузки ЗМ блока 2. Код опрации, являющийся начальныч адресоч чикропрограммы, реализующей даннун операцин.передаваемый с выхода блока 8 по шине Ч цз входы К адреса начальной микрокомзцды блока 2, по положительномл фроцтл сицхроимпульса загружается в регистр адреса микрокоманды блока 2. Следунццзя чцкр- команда выбирается из блока 1 ц здрсл, указываемому кодом операции, и, гзкнм о 6- разом, предлагаемый процессор вьходит 25 из программы обмена с ЦП ц приступает квыполнению заданной операции Г зав рцнию выполнения операции прдлзгзмый процессор вновь переходит к цсвлцеццн программы обмена с ЦП (к цикличскму вводу данных с входа в АЛБ, проврк. рзз- ЗО ряда Вт и т.п.).В том случае, если 111 осуществлячтение данных из предлагаемого процори в соответствии с ветвью вывода чикр- грограммы обмена с ЦГ 1, даццьц с цицы Ц считываются в аккумулятор АЛБ и ныдзютсц З 5 на шину Д (источник инфорлации блоки 5, 7 и 8 определяется как оцис;и цыц ) Сигналом Чтение ЦП вентили блкз 9 открываются в направлении цердзчц ццфрлации с шины Д на шину Ц 11 ЦП очиывз ет данные, а АЛБ пр;лагамого прои- сора вновь переходит к опросу входа В 7Как указывалось, блок 7 ззгруж;гсцкодом ошибки, если оцз ичла мело црц выполнении операции. Если оцибок це обнаружено, в блок 7 записывается цуль.45 Рассмотрим использование блока памяти12 адресов и констант. В процессвычисл- ния, например БПФ, элементарных функций возникает необходимость в использовании различных математических постоянных.Так, для вычисления БПФ разчернстц Х 50 необходимо иметь Х/4 значений отсчтоцкосинуса на интервале О, л 2. 11 рц вычислении значений элементарных функций через разложение последних в ряд цсобходичо ичеть коэффициенты ряда. Такие величины, как2, л часто использунтся кзк мзсцтзбирующие множители. Для сдвига дзццых на определенное число разрядв ц) жцо вцзчале установить программный ччик ццкла, загрузив в него константу.10 15 20 25 30 35 40 45 50 55 В процессоре-прототице все константы должны перед выполнением операции наряду с исходными данными пересылаться в прототип из 1),П, что существенно увеличивает время обмена между ЦП и прототипом и снижает производительность вычислительной системы в целом. В предлагаемый процессор (фиг. ) введен блок 12, в котором хранятся все используемые в процессе вычислений константы. Это позволяет за счет сокращения времени обмена между ЦП и предлагаемым процессором повысить быстродействие вычислительной системы в целом.Все используемые в вычислениях константы можно условно разбить на два типа.К первому типу относятся константы, однозначно связанные с адресом микрокомднды. Так, если в микропрограмме используется константа, она всякий раз при выполнении этой микропрограммы должна быть считана цз блока 12. Поскольку считывание такой константы происходит всег дд в одном и том же месте микропрограммы, используется адресация блока 12 от блока 2. В микрокоманде, использующей константу, разряд О ,.) должен быть равен 1. Блок 11 передает на адресный вход блока2 состояние выходов МА блока 2 - адрес следукщей микрокоманды. По этому адресу в блоке 12 записана необходимая коцстдцтд. Блок 11 вырабатывает также сигнал, разрешдкцций выдачу данных блоком 12, Нд лиццк блокировки выдается также этот сигнал, переводящий блоки 5, 7 и 8 в пассивное состояние. Код константы поступает по шине М ца вход М АЛБ и вход К блока 2 для использования в соответствии с кодом микрокомдцды.Ко второму типу относятся константы, адресуемые АЛЬ. Тдк, при выполнении БПФ использование тех или иных поворачиваю. ших множителей (из массива косинусов) зависит от этапа преобразования. Адрес константы в этом случае зачисляется в АЛБ и выдается на шину А адреса. Разряд О (р ) кода микроколдцд в это время равен О, и блок 11 передает на адресные входы блока 12 состояние шины А. Для активизации блока 2 и перехода блоков 5, 7 и 8 в пассивное состояние АЛБ при подготовке адреса ячейки блока 12 устанавливает старший разряд адреса Ав единичное состояние, блок 1 вырабатывает сигнал, разрешающий выдачу данных блоком 12 на шину М. На линию блокировки подается сигнал, не сводящий блоки 5, 7 и 8 в пассивное состояние.Еще одним недостатком прототипа является невозможность в микропрограммах подпрограмм. Это связано с отсутствием микрокомацд возврата из подпрограммы в основную микропрограмму в МПК серии АЙТЕ ЗООО, К 589. Использование в предлдгдемол процессоре блоков 11 и 12 позволяет устранить указанный недостаток. До перехода к подпрограмме (осуществляемого путем выполнения стандартной функции блока 2 Переход в нулевую строкух 1 УК - при этом информация на входах УА блока 2 однозначно определяет адрес следующей микрокоманды - первой микро- команды вызываемой подпрограммы) из блока 12 выбирается и запоминается в одном из внутренних регистров АЛБ константа первого типа А . Затем осуществляется пере 1ход к подпрограмме и ее выполнение. Поле завершения выполнения подпрограммы константа А пересылается в адресный регистр АЛБ и передается на шину А. А являегся адресом ячейки блока 12, в которой зап кана константа Ав второго типа, являющаяся адресом возврата из подпрограммы, Код константы А выбирается из ячейки А блока 12 и по шине М передается на вход К блока 2. В последней микрокоманде подпрограммы вырабатывается сигнал загрузки )., подаваемый на вход ЗМ блока 2. Происходит загрузка адреса А. в регистр адреса микрокоманды блока 2, и таким образом осуществляется возврат в основную микропрограмму.писанный процесс организует коррективное обращение к подпрограмме, поскольку, с одной стороны, константа А, запоминаемая основной микропрограммой в определенном внутреннем регистре АЛБ, однозначно определяет адрес возврата А. в основнук микропрограмму, а с другой стороны, одна и та же подпрограмма может быть использована различными вызывающими микропрограммами, поскольку адрес А, задающий адрес возврат А., внутри подпрограммы це изменяется, т.е, уровень вложения подпрограмм определяется количеством внутренних регистров АЛБ (ИМС типа К 589 ИК 02 имеет помимо адресного регистра и аккумулятора 11 регистров).Переход к подпрограмме может быть осуществлен из любого участка микропрограммы, при этом константа А жестко связана с микрокомандой основной микропрограммы, предцествующей вызову подпрограммы, и одцозндчно определяет адрес А. микрокоманды основной микропрограммы, которая исполняется первой после выполнения вызываемй подпрограммы. Двойная адресация блоки 12 при помощи блока 11 (от блока 2 и шины А) позволяет существенно расширить функциональные возможности предлагаемого процессора по сравнению с прототипом. Например, при вычислении БПФ необходимо осуществлять вычисления:М 2=М 2 С - МЗ С 1МЗ=М 2 С 2+МЗСМ 4=М 4СЗ - М 5 С 4М 5=М 4 С 4+МЗ СЗМ 6=М 6 С 5 - М 7 СбМ 7=М 6 Сб+М 7 С 5где М 2 - М 7 - отсчеты БПФ, а С - Сб - поворачивающие множители.На фиг. 3 - 4 приведены блок-схемы программ, реализующих приведенную последовательность вычислений, Слева на фиг. 3 показана последовательность действий, выполняемых центральным процессором, а справа, параллельно ей, - последовательность действий, синхронно с ЦП выполняемая предлагаемым процессором (фиг. 4).На фиг. 3 приняты следующие сокращения: НБР - выборка константы или переменной для использования; ПРЛ - передача константы, переменной или кода оп- рации; ПРМ - прием константы, переменной или кода операции (эти действия происходят синхронно - если ЦП передает, то предлагаемый процессор принимает, и наоборот; ОЖИД - ожидание (состояни, в котором предлагаемый процессор ожидает обращения к нему со стороны ЦП, или Ц 1 ожидает готовности предлагаемого процссора).Формула изобретенияПроцессор для выполнения математических операций, содержащий блок памяти микрокоманд, блок управления последовательностью микрокоманд, регистр микрокоманд, арифметико-логический блок, блок памяти кода операции, блок памяти состояния и результата, блок оперативной памяти, генератор тактовых импульсов, причем выход адреса блока управления последовзтльностью микрокоманд соединен с адресным входом блока памяти микрокоманд, выход поля адреса следующей микрокоманды и выход поля кода микрооперации которого соединены соответственно с входом адреса следующей команды блока управления последовательностью микрокоманд и с информационным входом регистра микрокоманд, выходы поля кода операции и поля кода маски которого соединены с входами кода операции и первым информационным входом арифметико-логического блока, первый информационный выход которого соединен через шину адреса с адресными входами блока оперативной памяти, блока памяти состояний и результата и блока памяти кода операции, выходы которы объединены и соедини ны через шину данных с входом адреса начальной микрокоманды блока управления последовательностью микрокоманд и вторым информационным входом арифметико-логического блока, второй информационный выход которого соединен через шину данных с входом-выходом процессора и с информационными входами блока оперативной памяти, блок памяти состояния и результата и блока памяти кода операции, выход и вход сдвига-переноса арифметико-логического блока соединены соответственно с входоч признаков и с выходом признаков блока управления последовательностью микрокоманд, вход управления признаками которого соединен с выходоч поля ржима у правления признаками регистра микрокочанд, выход поля режима форчирования адре са следующей микрокоманды регистра микрокоманд соединен с входом загрузки адреса микрокоманды блока управления последовательностью микрокоманд, информационный вход процессора соединн с тртьпч информационным входом арифчтико-логичского блока, вход строби рова ния данны х процессора соединен с входом стробировзния выдачи данных арифметико-логичского блока, выход генератора тактовых импульсов соединен с синхровходами блока упрзв ления последовательностью микрокоманд,регистра микрокоманд и арифметико-логического блока, выход поля управления записью в блоки памяти регистра микрокоманд со- динен с входами записи блока памяти кода операции блока памяти состояния и р- зультата и блока оперативной памяти, выход поля разрешения работы арифчтико- логического блока регистра микрокомзнд соединен с одноименным входоч зрифметико-логического блока, отлинактииигя 25 тм, что, с целью повышения быстродйствия, он содержит блок мультиплкснрп.вания адреса, содержащий первую и вгорук группы из М элементов (М = - К + 1, гдК - разрядность адреса микрокомзнды), элемент НЕ и блок памяти констант н здрсов, З 0 выход которого соединен через пшну данных с входом адреса начальной микро- команды блока управления послдовзтельностью микрокоманд и нторыч инфорчационныч входом арифмтико-логичского блока и выходами блока оперативнои пзЗ 5 мяти, блока памяти состояния и рзуль.тата и блока памяти кодов опраций, К выходов адреса микрокоманды блока х правления последовательностью микрокоманл си динены с первыми входами элечентов И пр вой группы, выходы с первого по (М) й которых объединены с одноименными выходзчи элементов И второй группы и соднены с адресными входами блока пзчяти констант и адресов, выходы М-х элементов И первой и второй групп объединены и содинпы с 45 входами блокировки блока пачяти констзни адресов, блока оперативной памяти, блоки памяти состояния и результата и блока памяти кода операции, М-хлздших разрядов шиныадреса устройства содинены с первыми входами соответствующих М 1 50 элементов И второй группы, первый вход Мго элемента И второй группы соединн с входом логической 1 процессора, выход поля управления адресом блока памяти констант и адресов регистра микрокоманд соединен с вторыми входами элементов И первой группы и через элемент НЕ с вторыми входами элементов И второй группы.1 Зо 533 1 О А э Аи А 12 (адресшины А) Х Разряды шины адреса А,Разряд Омикрокоманды1381533 2 Г 2 Ф Сост сааре ираж анасье коми а, Ж ческ лам изоя наб.,г. Ужгор Род;)ктор М. Келсмегпкакая 844;46ВП 111 ПИ Государственногс113035, МоскПроизвдс)венно.полиграф иг 1витель А. Лфд И. Верее704та СССР по д35, Ра ушекпречприятие Корректор 1 ПилипенкоПодписное ретении и открыти 45 д, ул. Проектная,

СмотретьЗаявка

4107839, 23.06.1986

ПРЕДПРИЯТИЕ ПЯ Г-4367

ЧЕПУРНОВ АЛЕКСЕЙ ВИКТОРОВИЧ, КАСЬЯНОВ ВАЛЕРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: выполнения, математических, операций, процессор

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/8-1381533-processor-dlya-vypolneniya-matematicheskikh-operacijj.html" target="_blank" rel="follow" title="База патентов СССР">Процессор для выполнения математических операций</a>

Предыдущий патент: Процессор для обработки массивов данных

Следующий патент: Устройство для сопряжения эвм

Случайный патент: Способ получения производных цефалоспорина