Специализированный процессор для вычисления элементарных функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

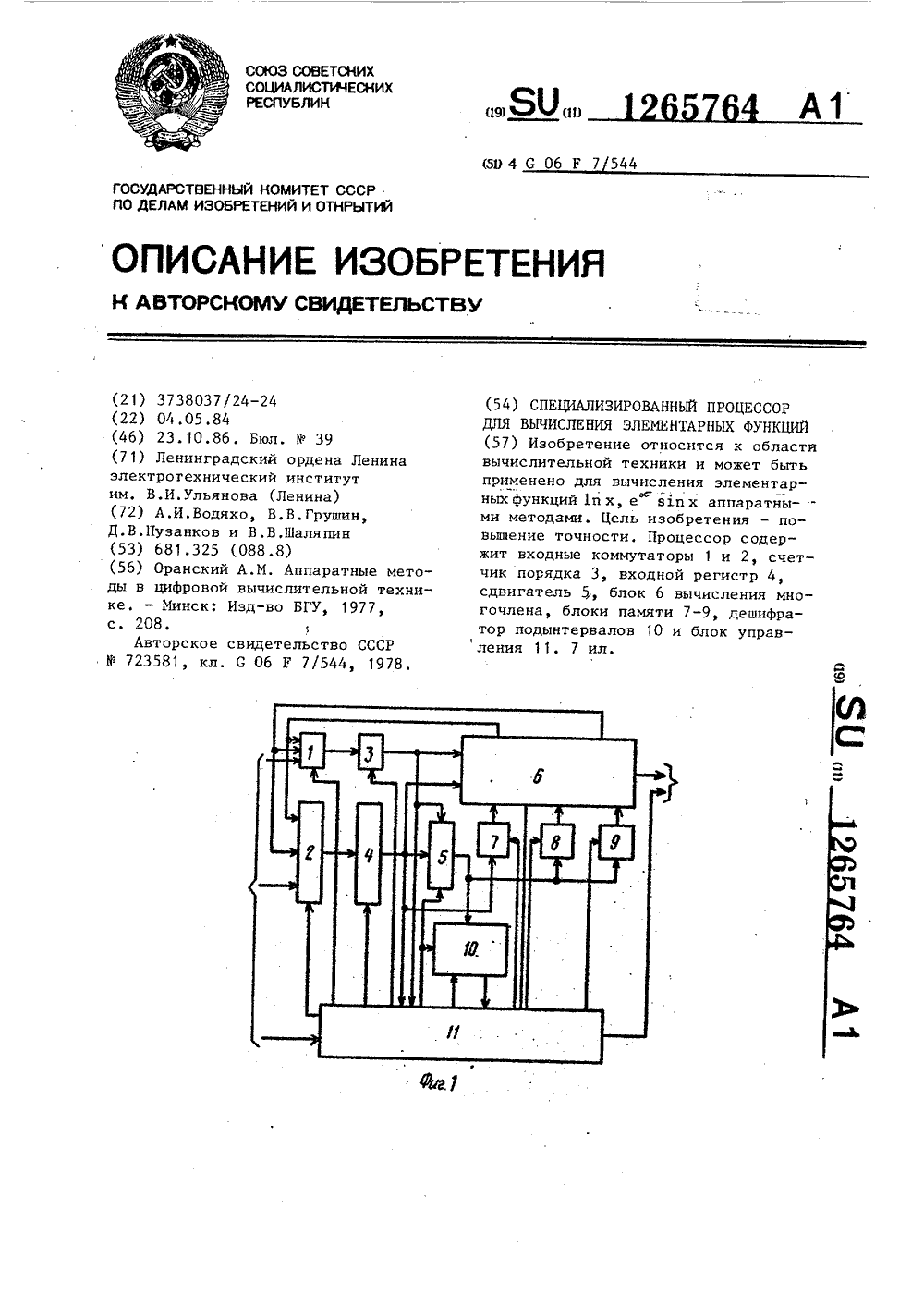

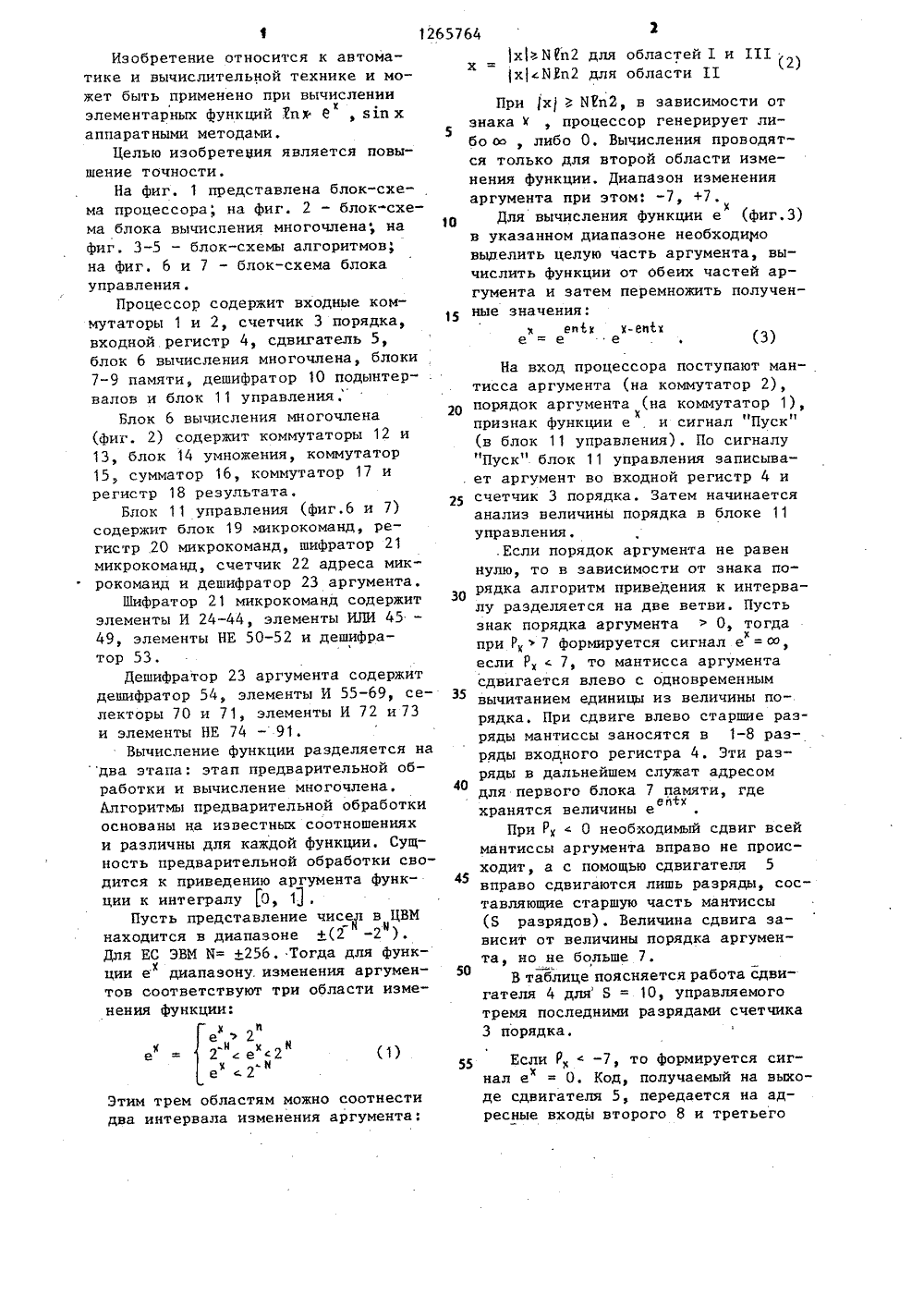

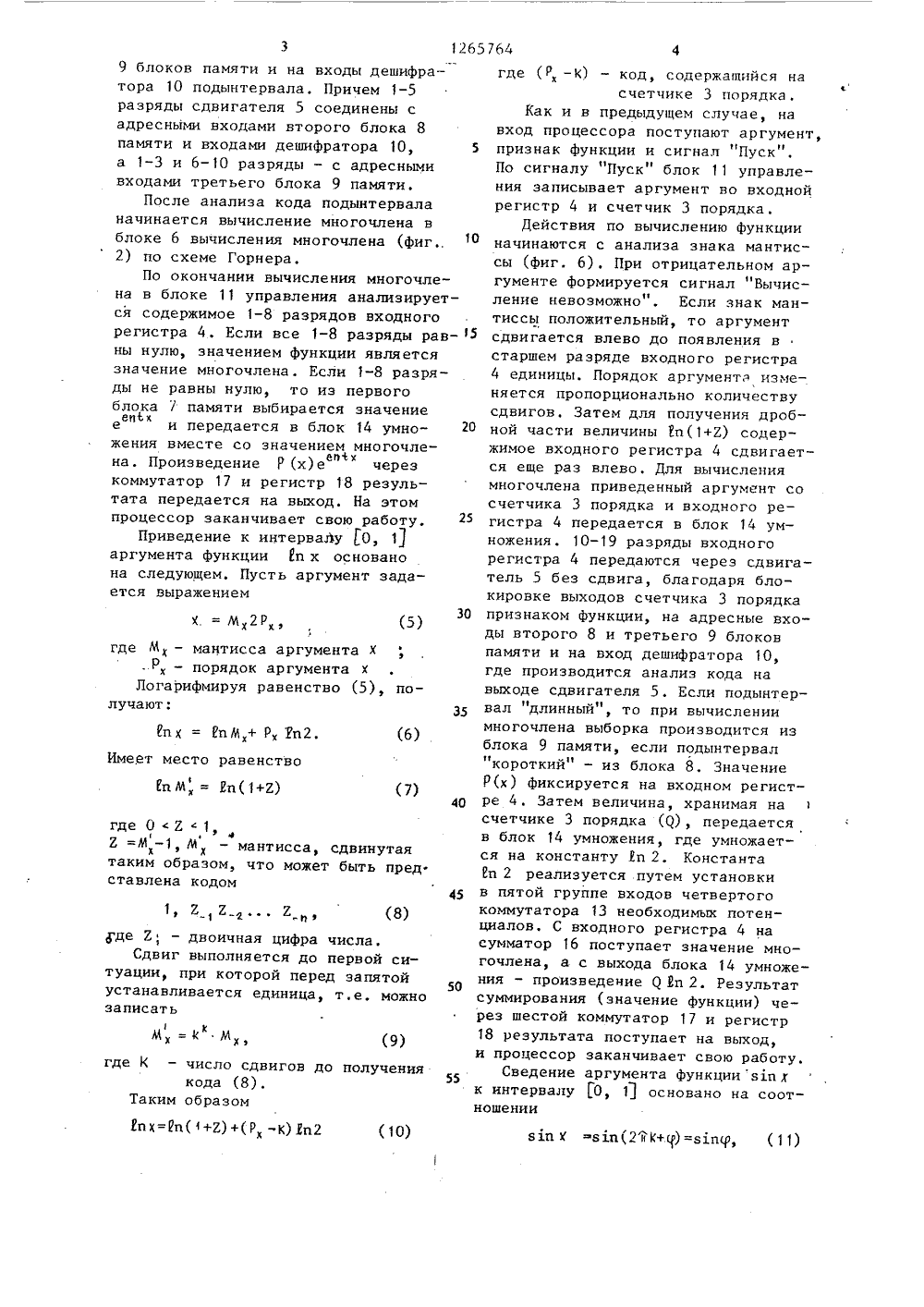

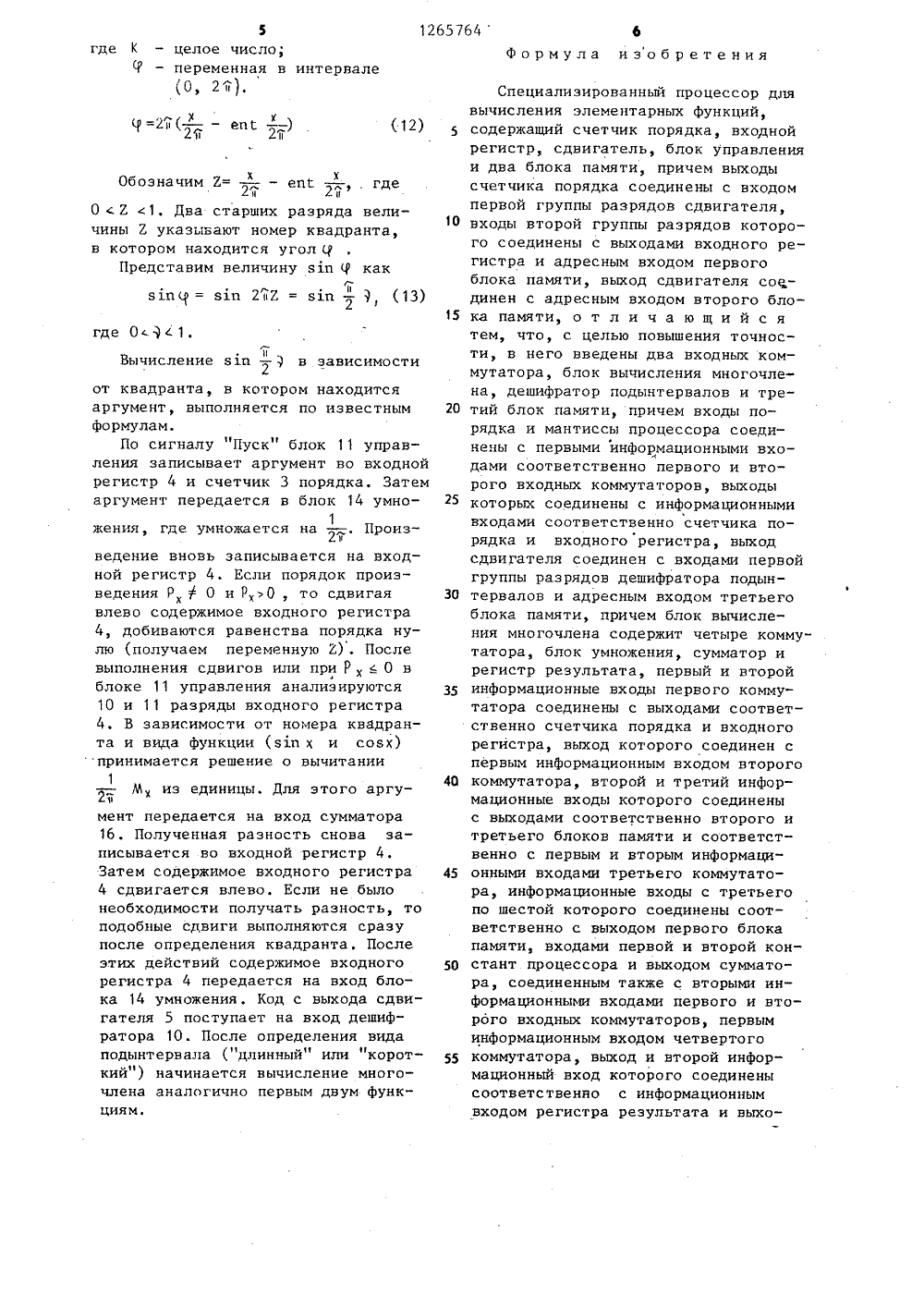

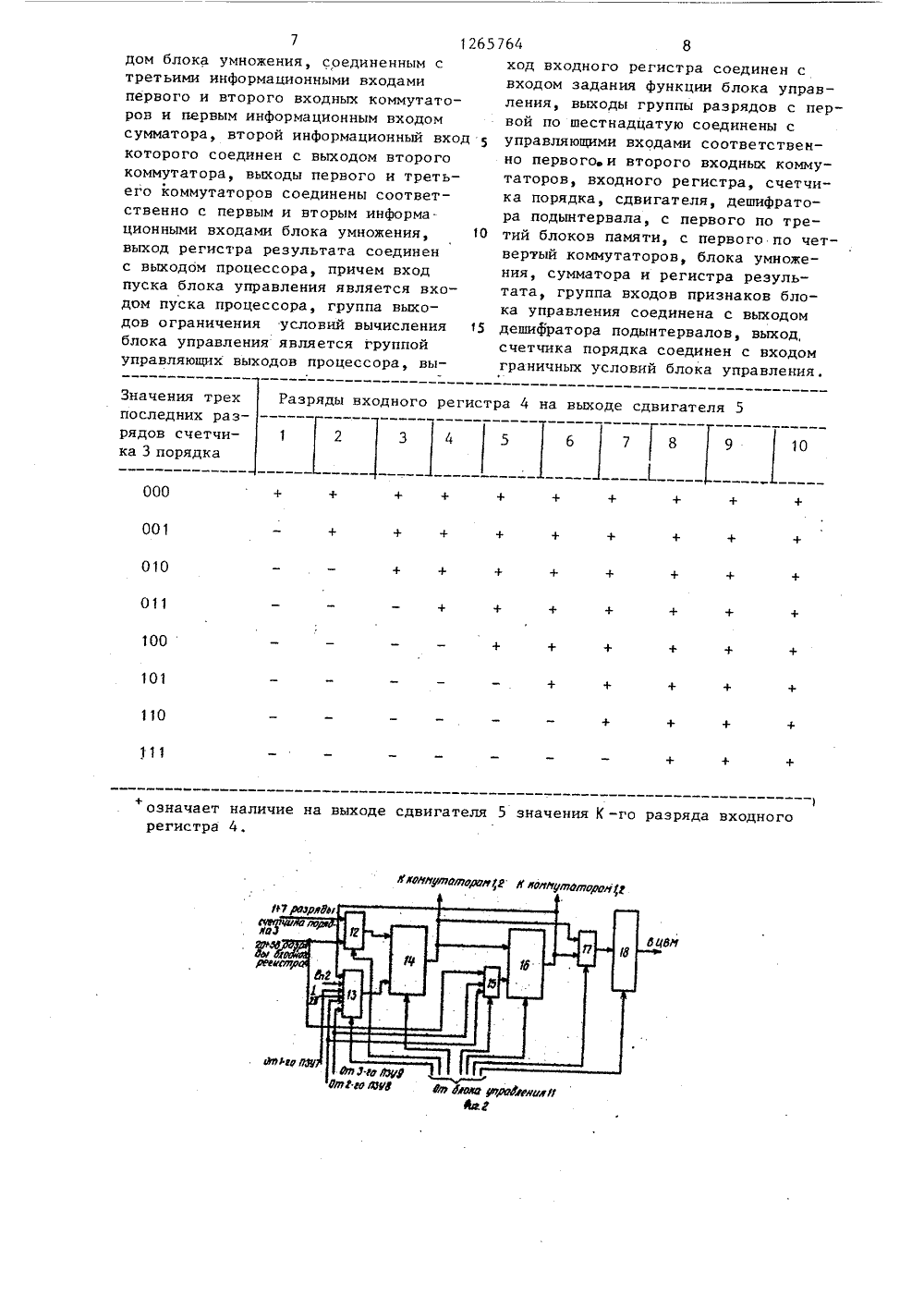

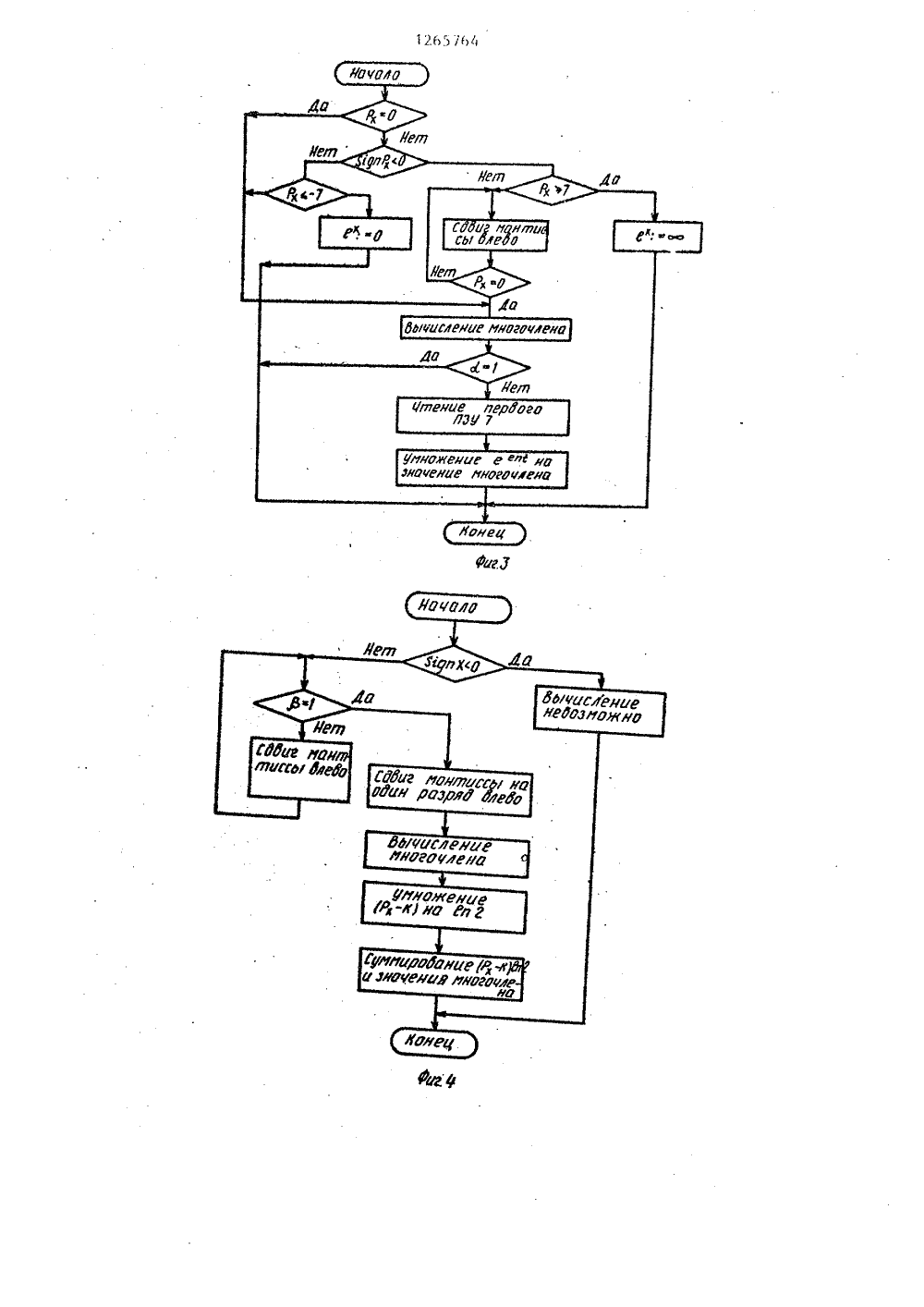

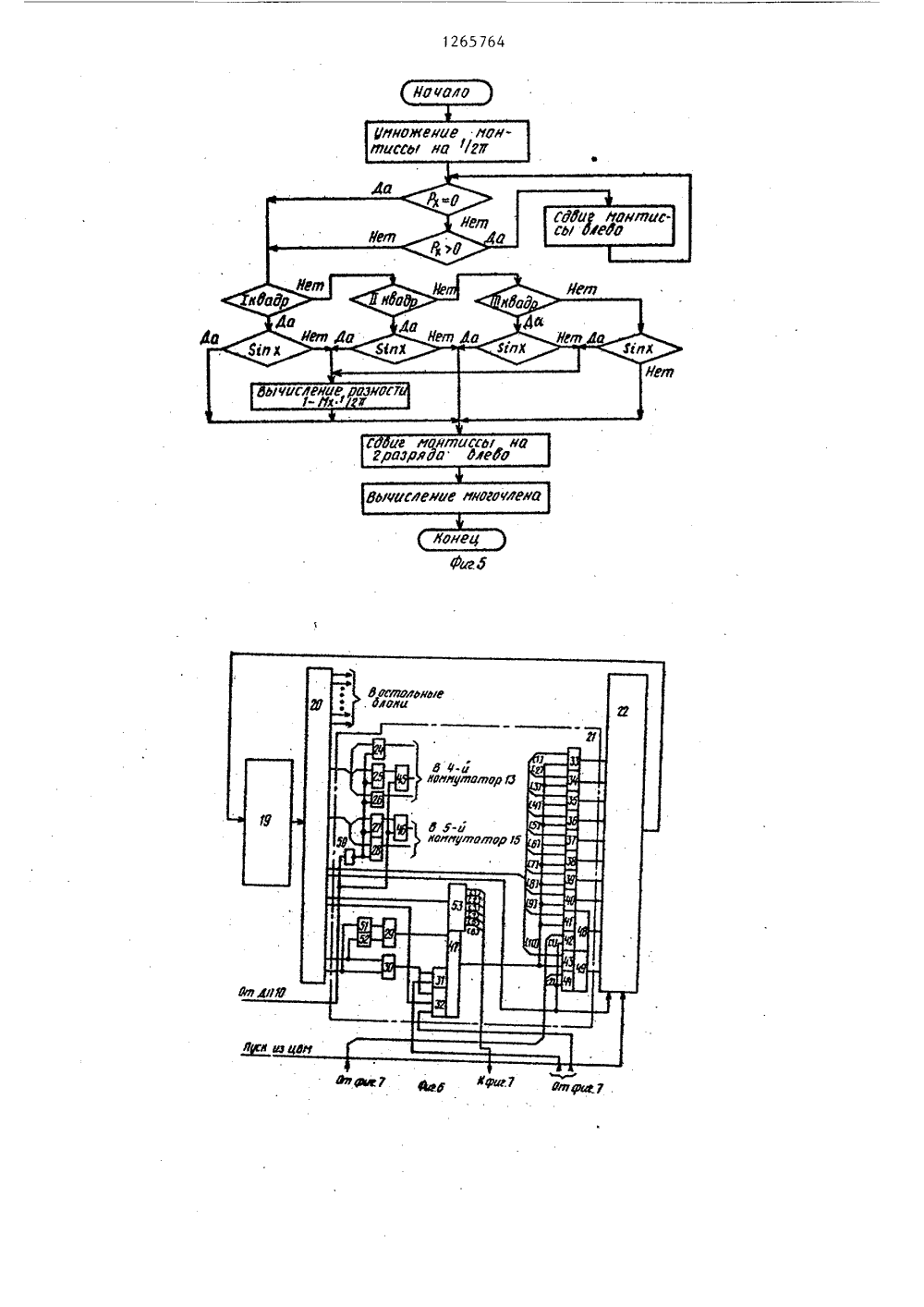

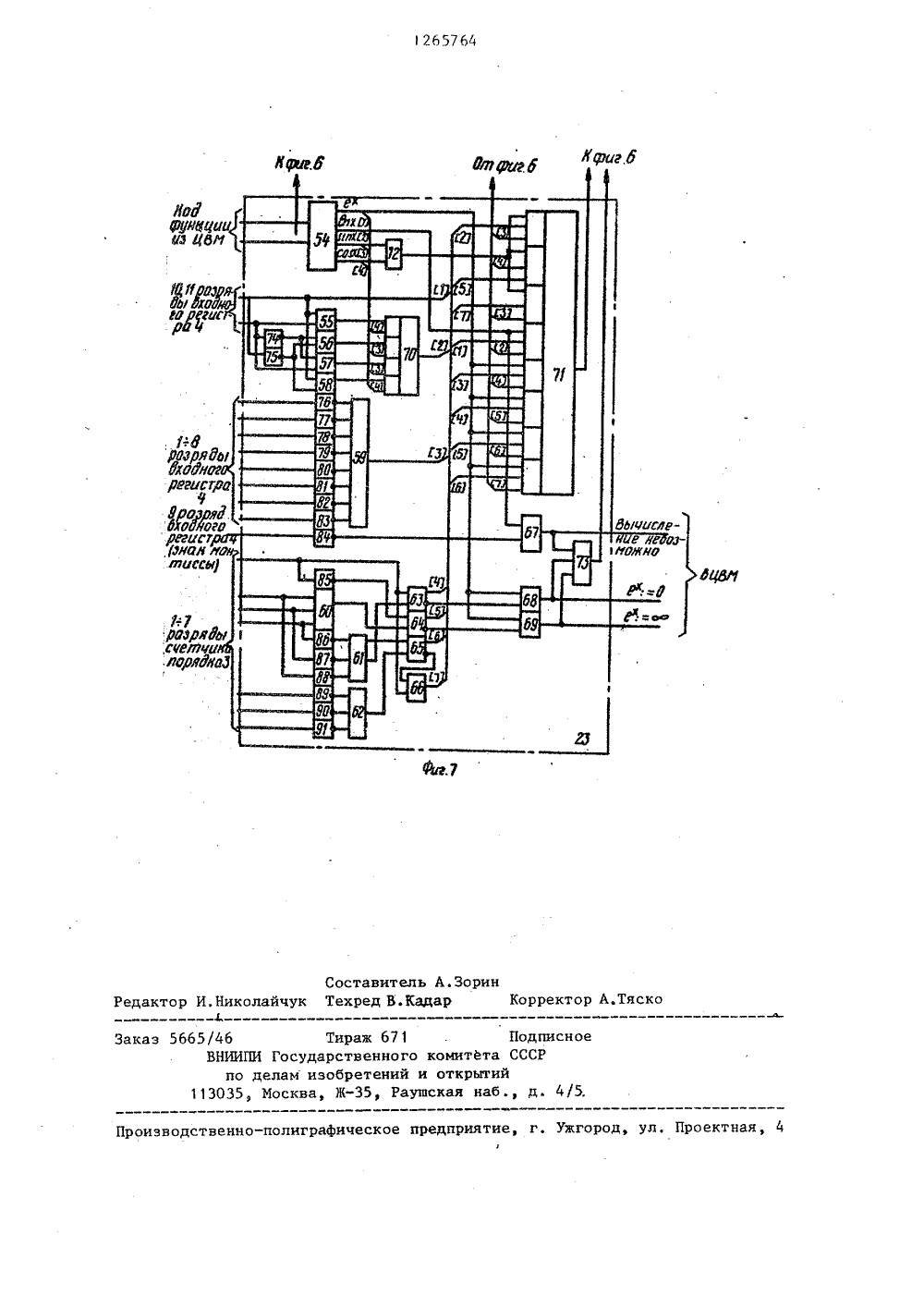

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИК А 1 504006 Р 7 544 ОМИТЕТ СССЕНИЙ И ОТНРЫ ГОСУДАРСТВЕННЫ ПО ДЕЛАМ ИЗОБРЕ ИСАНИЕ ИЗОБРЕТЕНИЯВУ(46) (71) элек на Ленинитут м,) ратные м льнои тех 1977, етельство СССР 6 Г 7/544, 197 ск р кл. К АВТОРСКОМУ СВИДЕТЕЛЬСТ 3738037/24-2404.05.8423.10.86. Бюл, РЛенинградский ордротехнический инс(54) СПЕЦИАЛИЗИРОВАННЫЙ ПРОЦЕССОР ДЛЯ ВЫЧИСЛЕНИЯ ЭЛЕМЕНТАРНЫХ ФУНКЦИЙ (57) Изобретение относится к области вычислительной техники и может быть применено для вычисления элементарб "ных функций 1 п х, е вдпх аппаратными методами. Цель изобретения - повышение точности. Процессор содержит входные коммутаторы 1 и 2, счетчик порядка 3, входной регистр 4, сдвигатель Ъ, блок 6 вычисления многочлена, блоки памяти 7-9, дешифратор подынтервалов 10 и блок управления 11. 7 ил.( е 2 -И х й Этим трем областям можно соотнести два интервала изменения аргумента: Изобретение относится к автоматике и вычислительной технике и может быть применено при вычислениик элементарных функций 7 пх 6, зхп х аппаратными методами.Целью изобретения является повышение точности.На фиг. 1 представлена блок-схема процессора; на фиг. 2 - блок-схема блока вычисления многочлена; на фиг. 3-5 - блок-схемы алгоритмов; на Фиг. б и 7 - блок-схема блока управления.Процессор содержит входные коммутаторы 1 и 2, счетчик 3 порядка, входной регистр 4, сдвигатель 5, блок 6 вычисления многочлена, блоки 7-9 памяти, дешифратор 10 подынтервалов и блок 11 управления,Блок 6 вычисления многочлена (фиг. 2) содержит коммутаторы 12 и 13, блок 14 умножения, коммутатор 15, сумматор 16, коммутатор 17 и регистр 18 результата.Блок 11 управления (фиг.б и 7) содержит блок 19 микрокоманд, регистр .20 микрокоманд, шифратор 21 микрокоманд, счетчик 22 адреса микрокоманд и дешифратор 23 аргумента.Шифратор 21 микрокоманд содержит элементы И 24-44, элементы ИЛИ 45 - 49, элементы НЕ 50-52 и дешифратор 53.Дешифратор 23 аргумента содержит дешифратор 54, элементы И 55-69, селекторы 70 и 71, элементы И 72 и 73 и элементы НЕ 74 - 91.Вычисление функции разделяется на два этапа: этап предварительной обработки и вычисление многочлена. Алгоритмы предварительной обработки основаны на известных соотношениях и различны для каждой Функции. Сущность предварительной обработки сводится к приведению аргумента функции к интегралу (О, 13Пусть представление чисел в ЦВМ,.ч ц находится в диапазоне +(2 -2 ). Для ЕС ЭВМ Б= +256, Тогда для функции е диапазону. изменения аргументов соответствуют три области изменения Функции:1 х Икп 2 для областей 1 и 111х = хБ 1 п 2 для области ТТ При х ) МУп 2, в зависимости от знака к , процессор генерирует либо оо , либо О, Вычисления проводятся только для второй области изменения функции. Диапазон изменения аргумента при этом: -7, +7.Для вычисления функции е (фиг.3) в указанном диапазоне необходимо выделить целую часть аргумента, вычислить функции от обеих частей аргумента и затем перемножить полученные значения:х еп 1 к-еоЬе=е е О 15(3) Если 1 х-7, то Формируется сигнал е = О. Код, получаемый на выхохде сдвигателя 5, передается на адресные входы второго 8 и третьего 55 На вход процессора поступают мантисса аргумента (на коммутатор 2),порядок аргумента (на коммутатор 1),признак функции е и сигнал "Пуск""Пуск" блок 11 управления записыва. ет аргумент во входной регистр 4 исчетчик 3 порядка. Затем начинаетсяанализ величины порядка в блоке 11 управления.Если порядок аргумента не равеннулю, то в зависимости от знака порядка алгоритм приведения к интервалу разделяется на две ветви. Пустьзнак порядка аргументаО, тогдапри 17 Формируется сигнал е = оо,кесли Р с 7, то мантисса аргументасдвигается влево с одновременным 35вычитанием единицы из величины порядка, При сдвиге влево старшие разряды мантиссы заносятся в 1-8 разряды входного регистра 4. Эти разряды в дальнейшем служат адресомдля первого блока 7 памяти, гдееНххранятся величины еПрис 0 необходимый сдвиг всеймантиссы аргумента вправо не происходит, а с помощью сдвигателя 5вправо сдвигаются лишь разряды, составляющие старшую часть мантиссы(8 разрядов). Величина сдвига зависит от величины порядка аргумента, но не больше 7.В таблице поясняется работа сдвигателя 4 для Б = 10, управляемоготремя последними разрядами счетчика3 порядка.3 1265764 9 блоков памяти и на входы дешифра - г тора 10 подынтервала. Причем 1-5 разряды сдвигателя 5 соединены с адресными входами второго блока 8 в памяти и входами дешифратора 10, 5 и а 1-3 и 6 - 1 О разряды - с адресными П входами третьего блока 9 памяти. н После анализа кода подынтервала ре начинается вычисление многочлена в блоке 6 вычисления многочлена (фиг., 1 О на 2) по схеме Горнера. сы По окончании вычисления многочле- гу на в блоке 11 управления анализирует- ле ся содержимое 1-8 разрядов входного ти регистра 4. Если все 1-8 разряды рав сд ны нулю, значением функции является ст значение многочлена. Если 1-8 разря ды не равны нулю, то из первого ня блока / памяти выбирается значение сд ея 6 х е и передается в блок 14 умно но жения вместе со значением многочле- жи на. Произведение Р (х)е через еМх ся коммутатор 17 и регистр 18 резуль-мн тата передается на выход, На этом сч процессор заканчивает свою работу.ги Приведение к интерваЛу 0, 11 но аргумента функции 1 п х основано ре на следующем, Пусть аргумент зада- те ется выражением ки. р - порядок аргумента х Логарифмируя равенство (5), получают: Ь х = Еп М+ РУп 2. Имеет место равенство Ь Мх = 2 п(1+Е) где 0 Ес 1иЕ =М, М - мантисса, сдвинутаятаким образом, что может быть пред.ставлена кодом,где Е, - двоичная цифра числа,Сдвиг выполняется до первой ситуации, при которой перед запятой устанавливается единица, т.е. можно записать кМк =К М, (9)где К - число сдвигов до получениякода (8).Таким образом де (Р - К) - код, содержащийся насчетчике 3 порядка,Как и в предыдущем случае, наход процессора поступают аргумент,ризнак функции и сигнал нПуск .о сигналу "Пуск" блок 11 управле -ия записывает аргумент во входнойгистр 4 и счетчик 3 порядка.Действия по вычислению функциичинаются с анализа знака мантис(фиг, 6). При отрицательном арменте формируется сигнал "Вычисние невозможно". Если знак манссы положительный, то аргументвигается влево до появления варшем разряде входного регистраединицы. Порядок аргумента измеется пропорционально количествувигов. Затем для получения дробй части величины 1 п(1+Е) содермое входного регистра 4 сдвигаетеще раз влево, Для вычисленияогочлена приведенный аргумент соетчика 3 порядка и входного рестра 4 передается в блок 14 умжения. 10-19 разряды входногогистра 4 передаются через сдвигаль 5 без сдвига, благодаря блоровке выходов счетчика 3 порядкаЗО признаком функции, на адресные входы второго 8 и третьего 9 блоковпамяти и на вход дешифратора 10,где производится анализ кода навыходе сдвигателя 5. Если подынтервал "длинный", то при вычислении (б)многочлена выборка производится изблока 9 памяти, если подынтервал"короткий" - из блока 8. Значение (7)Г(х) фиксируется на входном регист 40 ре 4. Затем величина, хранимая насчетчике 3 порядка (ф, передаетсяв блок 14 умножения, где умножается на константу 1 п 2. Константа1 п 2 реализуется путем установки45 в пятой группе входов четвертогокоммутатора 13 необходимых потенциалов. С входного регистра 4 насумматор 16 поступает значение многочлена, а с выхода блока 14 умножения - произведение Я 2 п 2. Результатсуммирования (значение функции) через шестой коммутатор 17 и регистр18 результата поступает на выход,и процессор заканчивает свою работу.Сведение аргумента функции здп хк интервалу 0, 11 основано на соот- ношении1265764Специализированный процессор для вычисления элементарных функций, содержащий счетчик порядка, входной регистр, сдвигатель, блок управления и два блока памяти, причем выходы счетчика порядка соединены с входом первой группы разрядов сдвигателя, входы второй группы разрядов которого соединены с выходами входного регистра и адресным входом первого блока памяти, выход сдвигателя соединен с адресным входом второго блока памяти, о т л и ч а ю щ и й с я тем, что, с целью повышения точности, в него введены два входных коммутатора, блок вычисления многочлена, дешифратор подынтервалов и третий блок памяти, причем входы порядка и мантиссы процессора соединены с первыми информационными входами соответственно первого и второго входных коммутаторов, выходы которых соединены с информационными входами соответственно счетчика порядка и входного регистра, выход сдвигателя соединен с входами первой группы разрядов дешифратора подынтервалов и адресным входом третьего блока памяти, причем блок вычисления многочлена содержит четыре коммутатора, блок умножения, сумматор и регистр результата, первый и второй информационные входы первого коммутатора соединены с выходами соответственно счетчика порядка и входного регистра, выход которого соединен с первым информационным входом второго коммутатора, второй и третий информационные входы которого соединены с выходами соответственно второго и третьего блоков памяти и соответственно с первым и вторым информационными входами третьего коммутатора, информационные входы с третьего по шестой которого соединены соответственно с выходом первого блока памяти, входами первой и второй кон( =2 и ( -- епс - )к к2 г 27(12) стант процессора и выходом сумматора, соединенным также с вторыми информационными входами первого и второго входных коммутаторов, первым информационным входом четвертого 50 коммутатора, выход и второй информационный вход которого соединены соответственно с информационным входом регистра результата и выхоциям. 5где 1 - целое число;Ч - переменная в интервале(О, 2 ),Обозначим 2= -- еп - . гдек2 л 27 ф0 с 2 с 1. Два старших разряда величины Е указывают номер квадранта, в котором находится угол ЦПредставим величину зп ч как11з 1 п = 81 п 27 Е = 81 п -(13)2 где Ос. (1. И Вычисление зы -в зависимости 2от квадранта, в котором находится аргумент, выполняется по известным формулам.По сигналу "Пуск" блок 11 управ - ления записывает аргумент во входной регистр 4 и счетчик 3 порядка. Затем аргумент передается в блок 14 умно 1жения, где умножается на в , Произ 2 к ведение вновь записывается на входной регистр 4. Если порядок произведения Р Ф 0 и Р О, то сдвигаяквлево содержимое входного регистра 4, добиваются равенства порядка нулю (получаем переменную 2) . После выполнения сдвигов или при Рс 0 в4блоке 11 управления анализируются 10 и 11 разряды входного регистра 4. В зависимости от номера квадранта и вида функции (зхп х и созх) принимается решение о вычитании 1Мк из единицы. Для этого аргумент передается на вход сумматора 16. Полученная разность снова записывается во входной регистр 4. Затем содержимое входного регистра 4 сдвигается влево. Если не было необходимости получать разность, то подобные сдвиги выполняются сразу после определения квадранта. После этих действий содержимое входного регистра 4 передается на вход блока 14 умножения. Код с выхода сдвигателя 5 поступает на вход дешифратора 10. После определения вида подынтервала (длинный" или "короткий") начинается вычисление много- члена аналогично первым двум функ 5 1 О 15 20 25 30 35 40 45 Формула изобретения1265764 10 Разряды входного регистра 4 на выходе сдвигателя 5 Значения трехпоследних разрядов счетчика 3 порядка 1 2 3 4 5 6 7 10 000 001 010 011 100 101 110 означает наличие на выходе сдвигателя 5 значения М -го разряда входногорегистра 4. дом блока умножения, соединенным стретьими информационными входамипервого и второго входных коммутаторов и первым информационным входомсумматора, второй информационный входкоторого соединен с выходом второгокоммутатора, выходы первого и третьего коммутаторов соединены соответственно с первым и вторым информационными входами блока умножения,выход регистра результата соединенс выходом процессора, причем входпуска блока управления является входом пуска процессора, группа выходов ограничения условий вычисления 15блока управления является группойуправляющих выходов процессора, выход входного регистра соединен свходом задания функции блока управ -ления, выходы группы разрядов с первой по шестнадцатую соединены суправляющими входами соответственно первого,и второго входных коммутаторов, входного регистра, счетчика порядка, сдвигателя, дешифратора подынтервала, с первого по третий блоков памяти, с первого по четвертый коммутаторов, блока умножения, сумматора и регистра результата, группа входов признаков блока управления соединена с выходомдешифратора подынтервалов, выход,счетчика порядка соединен с входомграничных условий блока управления.265764 Вал ШОСТУ Составитель А.Зоедактор И.Николайчук Техред В.Кадар ректор А.Тяс 1 Подписноего комитета СССРй и открытий аущская наб., д. 4/5. аз 5665/4 дприятие кое РИТОРРхоФаюРГРЖФюГоУГ й 7раАмдСИМАмий НИИПИ Госуд по делам и 3035, Москва оизводственно-полиграф ираж 6ственнбретенЖ,Ужгород, ул. Проектна

СмотретьЗаявка

3738037, 04.05.1984

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

ВОДЯХО АЛЕКСАНДР ИВАНОВИЧ, ГРУШИН ВЯЧЕСЛАВ ВАСИЛЬЕВИЧ, ПУЗАНКОВ ДМИТРИЙ ВИКТОРОВИЧ, ШАЛЯПИН ВЛАДИМИР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычисления, процессор, специализированный, функций, элементарных

Опубликовано: 23.10.1986

Код ссылки

<a href="https://patents.su/8-1265764-specializirovannyjj-processor-dlya-vychisleniya-ehlementarnykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Специализированный процессор для вычисления элементарных функций</a>

Предыдущий патент: Устройство для деления

Следующий патент: Матричный вычислитель

Случайный патент: Способ ориентирования подэтажной горной выработки через одну вертикальную выработку