Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

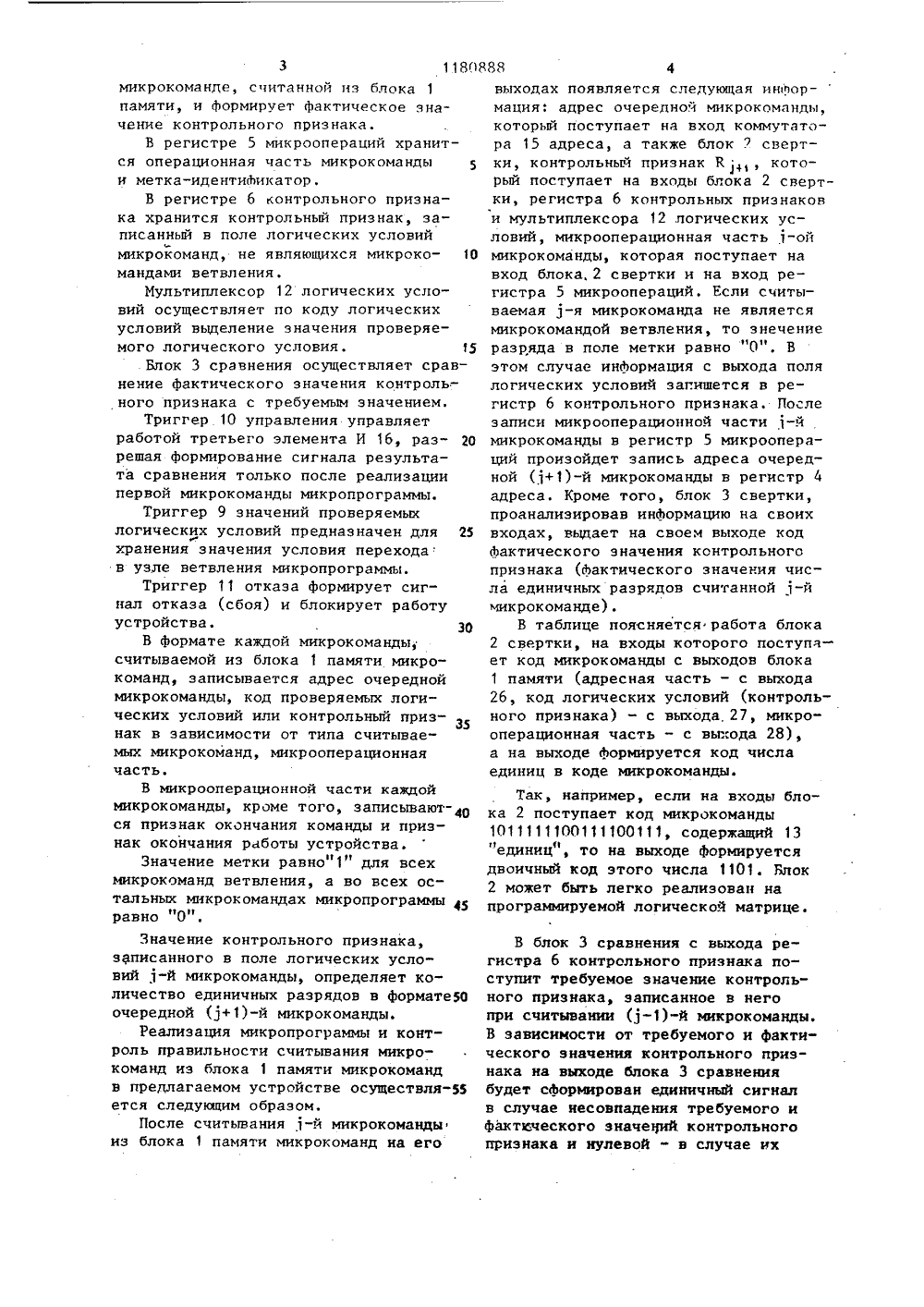

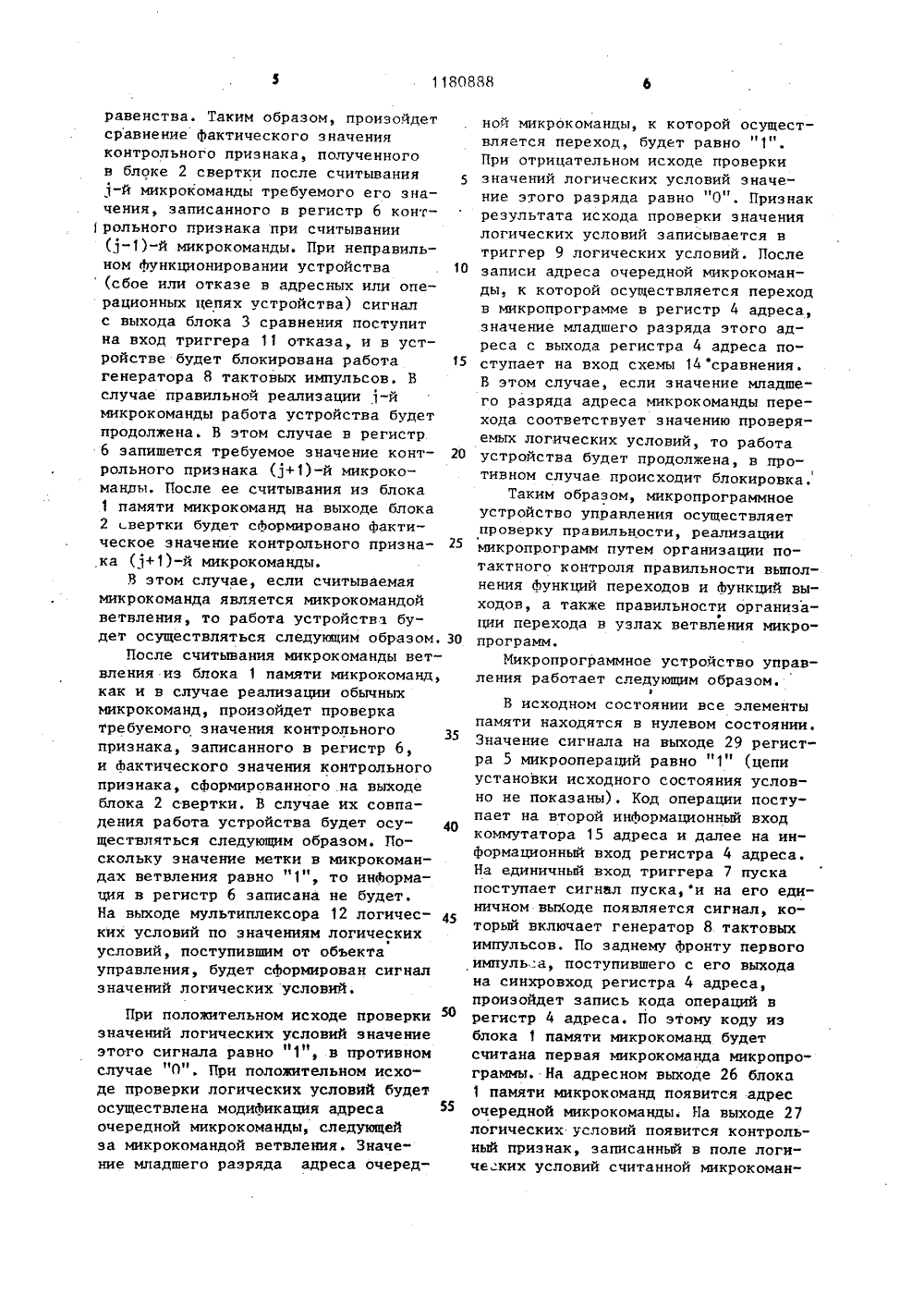

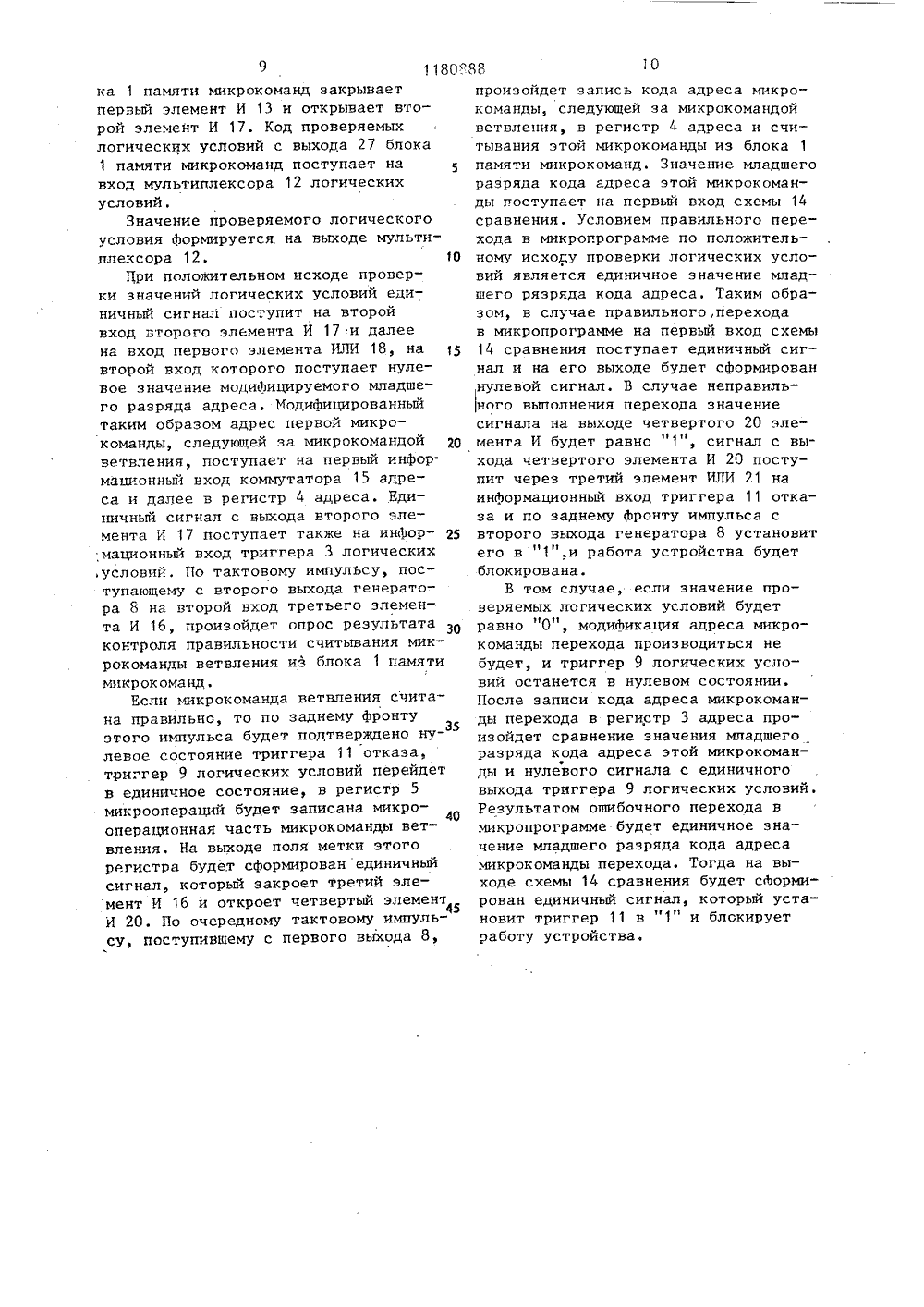

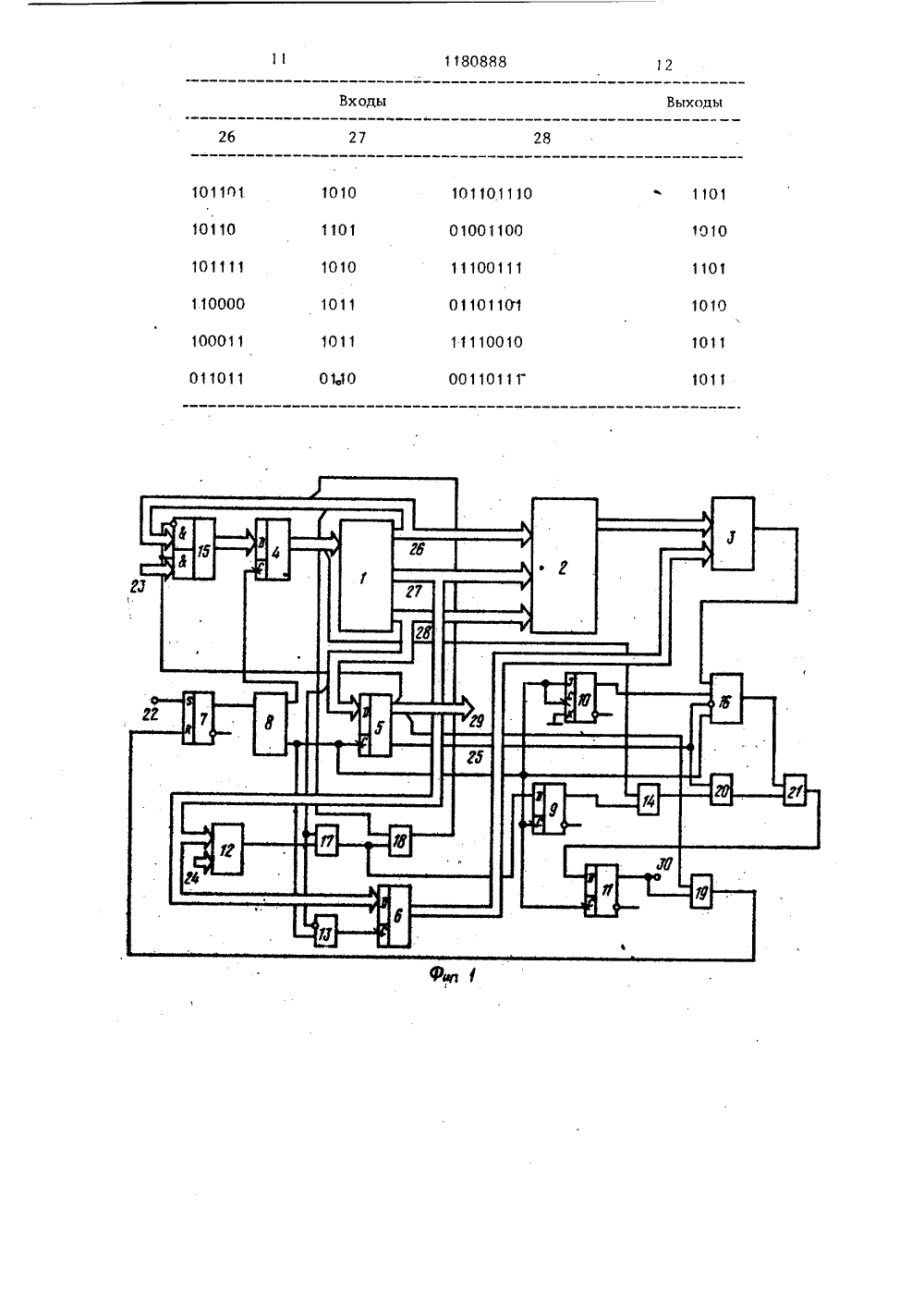

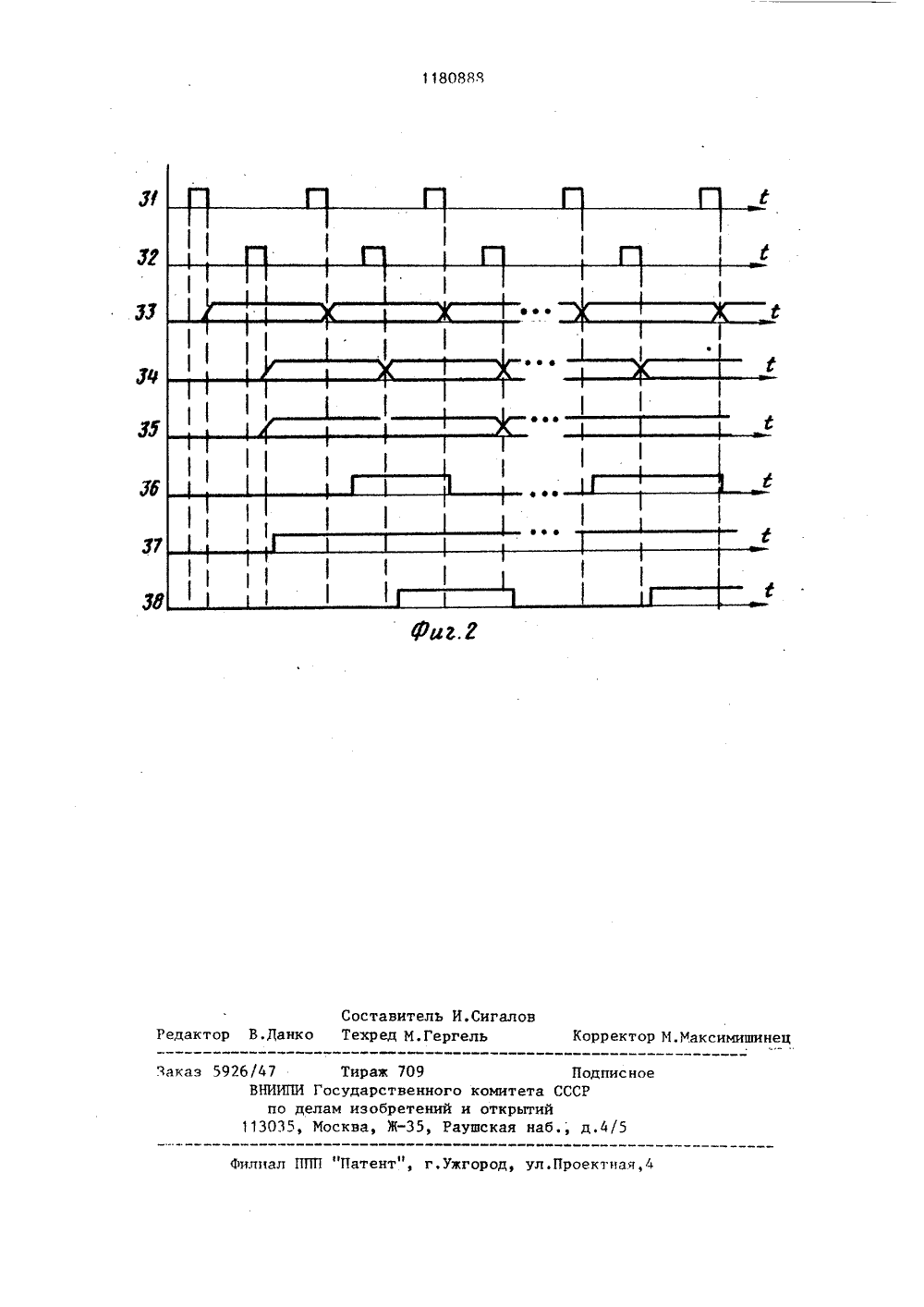

)4 С 06 Г 9/22 11 ГОСУДАРСПО ДЕЛ К АВ КОМУ СВ ВУ оединен с втор выход младшего мационного вхо вход кода опер ен с вторым ищ вхо ом микрокоманд первого эл :оединен с первого ин гора адрес ройства со которогоаэрядаа коммутаций устформациента ИЛИходом дин,выход ационций яв- рочст ННЫЙ НОМИТЕТ СССРЗОБРЕТЕНИЙ И ОТНРЫТИИ САНИЕ ИЗ(56) Авторское свидетельство СССРР 1020827, кл, С 06 Р 9/22, 1983.Авторское свидетельство СССРР 1015384, кл. С 06 Р 11/00, 1983.Авторское свидетельство СССРУ 1007109, кл. С 06 Г 11/00, 1983.(54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ, содержащее блок памятимикрокоманд, регистр адреса, регистрмикроопераций, блок сравнения, блоксвертки, триггер отказа, первый ивторой элементы И, первый, второй итретий элементы ИЛИ, причем выходрегистра адреса соединен с адреснымвходом блока памяти микрокоманд, регистр микроопераций которого соединенс информационным входом регистра микроопераций, о т л и ч а ю щ е е с ятем, что, с целью повышения достоверности функционирования, в него введены регистр тактовых импульсов, триггер пуска, триггер управления, триггер значений проверяемых логическихусловий, схема сравнения, мультиплексор логических условий, третий и четвертый элементы И, причем вход запуска устройства соединен с единичнымвходбм триггера пуска, единичный выход которого соединен с входом генератора тактовых импульсов, второй ипервый выходы генератора тактовыхимпульсов соединены соответственно с входом синхронизации регистра адреса, с входом синхронизации регистра микроопераций, выход поля метки блока памяти микрокоманд соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен с входом синхронизации регистра контрольного признака, выход второго элемента И соединен с первым входом первого элемента ИЛИ и информационным входом триггера значений проверяемых логических условий, выход микроопераций блока памяти микрокоманд соединен с первым входом блока свертки, выход которого соединен с первым входом е блока сравнения, выход контрольного признака блока памяти микрокоманд соединен с управляющим входом мультиплексора логических условий, с вторым входом блока свертки, с информационным входом регистра контрольного признака, выход которого соединен с вторым входом блока сравнения, выход адреса очередной микрокоманды блока микрокоманд соединен с третьим входом блока свертки и с первым информационным входом коммутатора адреса, выход младшего разряда выхода адреса очередной микрокоманды блока памяти онным входом коммутатора адрес которого соединен с информацио входом регистра адреса, информ ный выход регистра микроопера ляется выходом микроопераций уст118 РРЯ 8 10 ва,выход конца команды выхода микроопераций регистра микроопераций соединен с управляющйм входом коммутатора адреса, выход конца работы выхода микро- . операций регистра микроопераций соединен с первым входом второго элемента ИЛИ, вход логических условий устройства соединен с информационным входом мультиплексора логических условий, выход которого соединен с вторым входом второго элемента И, выход метки регистра микроопераций соединен с первыми входами третьего и четвертого элемента И, второй выход генератора тактовых импульсов соединен с входами 3 и С триггера управле" ния, вторым входом третьего элемента И, синхровходами триггера значений проверяемых логических условий и триггера отказа, выход блока сравнения соединен с третьим входом третьИзобретение относится к цифровойвычислительной технике и может быть использовано при проектировании ипостроении управляющих устройств иустройств контроля ЦВМ.Целью изобретения является повышение достоверности функционирования устройства,На фиг. 1 представлена функциональная схема микропрограммногоустройства управления; на фиг. 2 -време",ные диаграммы его работы. Микропрограммное устройствоуправления содержит блок 1 памяти 1 микрокоманд, блок 2 свертки, блок 3 сравнения, регистр 4 адреса, регистр 5 микроопераций, регистр 6 контрольного признака, триггер 7 пуска, генератор 8 тактовых импульсов, триггер 9 2 О значений проверяемых логических условий, триггер 10 управления, триггер 11 отказа, мультиплексор 12 логических условий, первый элемент И 13, схема 14 сравнения, коммутатор 15 адре са, третий элемент И 16, второй элемент И 17, первый элемент ИЛИ 18,вто-, рой элемент ИЛИ 19, четвертый элемент И 20, третий элемент ИЛИ 21, вход 22 пуска устройства, вход 23 кода опера- ЗО его элемента И, выход которого соеди-:нен с первым входом третьего нулевогопотенциала, выход которого соединенс К-входом триггера управления, выход которого соединен с четвертымвходом третьего элемента И, выходмладшего разряда регистра адреса соединен с первым входом схемы сравнения,единичный выход триггера управлениясоединен с вторым входом схемы сравнения, выход которой соединен с вторымвходом четвертого элемента И, выходчетвертого элемента И соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с информационным входом триггера отказа единичныйвыход триггера отказа соединен с выходом отказа устройства и с вторымвходом второго элемента ИЛИ, выходкоторого соединен с нулевым входомтриггера пуска. 2ь ций устройства, вход 24 логических условий устройства, выход 25 поля метки регистра 5 микроопераций, выход 26 адреса очередной микрокоманды выход 27 блока контрольного признака блока 1 выход 28 микроопераций блока 1 памяти микрокоманд, выход 29 микроопераций устройства, выход 30 отказа устройства.На фиг. 2 обозначены: первый и второй выходы 31 и 32 генератора 8 тактовых импульсов соответственно, выход 33 регистра 4 адреса, выход 34 . регистра 5 микроопераций, выход 35 регистра 6 контрольного признака, значение 36 метки на первом выходе 28 блока 1 памяти микрокоманд, единичный выход 37 триггера 10 управления, единичный выход 38 триггера 9 значений проверяемых логических условий.В блоке 1 памяти микрокоманд хранятся реализуемые устройством микропрограммы. Формат микрокоманд, считываемых из блока 1 памяти микрокоманд, разбит на три поля: адресное поле, микрооперационное поле и поле логических условий.Блок 2 свертки осуществляет определение числа единичных разрядов вмикрокоманде, считанной из блока 1 памяти, и Формирует фактическое значение контрольного признака.В регистре 5 микроопераций хранится операционная часть микрокоманды и метка-идентификатор.В регистре 6 контрольного признака хранится контрольный признак, записанный в поле логических условий микрокоманд, не являющихся микрско О мандами ветвления.Мультиплексор 12 логических условий осуществляет по коду логических условий выделение значения проверяемого логического условия. 15Блок 3 сравнения осуществляет сравнение фактического значения контрольного признака с требуемым значением.Триггер 10 управления управляет работой третьего элемента И 16, раз решая формирование сигнала результа - та сравнения только после реализации первой микрокоманды микропрограммы.Триггер 9 значений проверяемых логических условий предназначен для 25 хранения значения условия перехода: в узле ветвления микропрограммы.Триггер 11 отказа формирует сигнал отказа (сбоя) и блокирует работу устройства. 30В формате каждой микрокоманды; считываемой из блока 1 памяти микро" команд, записывается адрес очередной микрокоманды, код проверяемых логических условии или контрольныи приз 35 нак в зависимости от типа считываемых микрокоманд, микрооперационная часть.В микрооперационной части каждой микрокоманды, кроме того, записываютО ся признак окончания команды и признак окончания работы устройства.Значение метки равно"1" для всех микрокоманд ветвления, а во всех остальных микрокомандах микропрограммы 5 равно "0".Значение контрольного признака, записанного в поле логических условий 1-й микрокоманды, определяет количество единичных разрядов в формате 50 очередной Ц+1)-й микрокоманды.Реализация микропрограммы и контроль правильности считывания микро- команд из блока 1 памяти микрокоманд в предлагаемом устройстве осуществляется следующим образом.После считывания 1-й микрокоманды из блока 1 памяти микрокоманд на его выходах появляется следующая информация: адрес очередной микрокоманды, который поступает на вход коммутатора 15 адреса, а также блоксвертки, контрольный признак Ккоторый поступает на входы блока 2 свертки, регистра 6 контрольных признаков и мультиплексора 12 логических условий, микрооперационная часть 1-ой микрокоманды, которая поступает на вход блока, 2 свертки и на вход регистра 5 микроопераций. Если считываемая 3-я микрокоманда не является микрокомандой ветвления, то знечение разряда в поле метки равно "0", В этом случае информация с выхода поля логических условий загишется в регистр 6 контрольного признака. После записи микрооперационной части 1-й микрокоманды в регистр 5 микроопераций произойдет запись адреса очередной (1+1)-й микрокоманды в регистр 4 адреса, Кроме того, блок 3 свертки, проанализировав информацию на своих входах, выдает на своем выходе код фактического значения контрольного признака (фактического значения числа единичных разрядов считанной 1-й микрокоманде).В таблице поясняется работа блока 2 свертки, на входы которого поступает код микрокоманды с выходов блока 1 памяти (адресная часть - с выхода 26, код логических условий (контрольного признака) - с выхода, 27, микро- операционная часть - с вьгьода 28), а на выходе формируется код числа единиц в коде микрокоманды.Так, например, если на входы блока 2 поступает код микрокоманды 1011111100111100111, содержащий 3 "единиц", то на выходе формируется двоичный код этого числа 1101. Блок 2 может быть легко реализован на программируемой логической матрице. В блок 3 сравнения с выхода регистра 6 контрольного признака поступит требуемое значение контрольного признака, записанное в него при считывании Ц)-й микрокоманды. В зависимости от требуемого и фактического значения контрольного Аризнака на выходе блока 3 сравнения будет сформирован единичньй сигнал в случае несовпадения требуемого и фактического значений контрольного признака и нулевой - в случае ихравенства. Таким образом, произойдет сравнение фактического значения контрольного признака, полученного в блоке 2 свертки после считывания 1-й микрокоманды требуемого его значения, записанного в регистр 6 конт рольного признака при считывании (,1-1)-й микрокоманды. При неправильном Функционировании устройства . 10(сбое или отказе в адресных или операционных цепях устройства) сигнал с выхода блока 3 сравнения поступит на вход триггера 11 отказа, и в устройстве будет блокирована работа 15 генератора 8 тактовых импульсов. В случае правильной реализации 1-й микрокоманды работа устройства будет продолжена. В этом случае в регистр. б запишется требуемое значение конт рольного признака Ц+1)-й микрокоманры. После ее считывания из блока 1 памяти микрокоманд на выходе блока 2 завертки будет сформировано фактическое значение контрольного призна ка (1+1)-й микрокоманды.В этом случае, если считываемая микрокоманда является микрокомандой ветвления, то работа устройства будет осуществляться следующим образом, 30После считывания микрокоманды ветвления из блока 1 памяти микрокоманд, как и в случае реализации обычных микрокоманд, произойдет проверка требуемого значения контрольного признака, записанного в регистр 6, и Фактического значения контрольного признака, сформированного .на выходе блока 2 свертки. В случае их совпадения работа устройства будет осу ществляться следующим образом. Поскольку значение метки в микрокомандах ветвления равно "1", то информация в регистр 6 записана не будет. На выходе мультиплексора 12 логичес ких условий по значениям логических условий, поступившим от объекта управления, будет сформирован сигнал значений логических условий.При положительном исходе проверки 50 значений логических условий значение этого сигнала равно 1", в противном случае "П". При положительном исходе проверки логических условий будет осуществлена модификация адреса 55 очередной микрокомаиды, следующей за микрокомандой ветвления. Значение младшего разряда адреса очередной микрокоманды, к которой осуществляется переход, будет равно "1".При отрицательном исходе проверки значений логических условий значение этого разряда равно 0. Признак результата исхода проверки значения логических условий записывается в триггер 9 логических условий. После записи адреса очередной микрокоманды, к которой осуществляется переход в микропрограмме в регистр 4 адреса, значение младшего разряда этого адреса с выхода регистра 4 адреса поступает на вход схемы 14 сравнения. В этом случае, если значение младшего разряда адреса микрокоманды перехода соответствует значению проверяемых логических условий, то работа устройства будет продолжена, в противном случае происходит блокировка.Таким образом, микропрограммное устройство управления осуществляет проверку правильности, реализации микропрограмм путем организации потактного контроля правильности выполнения Функций переходов и функций выходов, а также правильности организации перехода в узлах ветвления микропрограмм.Микропрограммное устройство управления работает следующим образом.В исходном состоянии все элементы памяти находятся в нулевом состоянии. Значение сигнала на выходе 29 регистра 5 микроопераций равно "1" (цепи установки исходного состояния условно не показаны), Код операции поступает на второй информационный вход коммутатора 15 адреса и далее на информационный вход регистра 4 адреса. На единичный вход триггера 7 пуска поступает сигнал пуска,и на его единичном выходе появляется сигнал, который включает генератор 8 тактовых импульсов. По заднему Фронту первого импуль а, поступившего с его выхода на синхровход регистра 4 адреса, произойдет запись кода операций в регистр 4 адреса. По этому коду из блока 1 памяти микрокоманд будет считана первая микрокоманда микропрограммы. На адресном выходе 26 блока 1 памяти микрокоманд появится адрес очередной микрокоманды. На выходе 27 логических условий появится контрольный признак, записанный в поле логиче ких условий считанной микрокоман7 118 П 888 8ды. На выходе 27 микроопераций - мик- сов на синхровход регистра 4 адреса,рооперационная часть первой микро- произойдет запись адреса второйкоманды. Информация с этих выходов микрокоманды в этот регистр и ееблока 1 памяти микрокоманд поступит е из лока памяти микро 1этом значение младшеготакже на соответствующие входы блока 5 команд. При этом значе2 свертки, на выходе которого будет разряда кода адреса микрокоманды ф сформировано фактическое значение пает на первьы вход схемы 1контрольного признака. ения, на второи вход которой.Поскольку в исходном состоянии поступает нулевой иулевой сигнал с единичнлвсе элементы памяти находятся в нуле О го выхода тригге 9ггера логических усвом состоянии, то на выходе поля мет- ловий Сигнал рнал результата сравненияки регистра 5 микроопераций и на еди- поступает с выхода схемы 14 сравненичных выходах триггеров 9-11 будет ния на. второи вх. второй вход четвертого элеприсутствовать нулевой сигнал. Нуле- мента И 20 которьй ивкоторьй по-прежнему завой сигнал, поступающий с единичного 15 крыт нулевым сигналом с выхода полявыхода триггера 10 управления на чет- метки регистра 5 кр ". Нмикрооперации. Навертый вход третьего элемента И 16, выходе четвертого элемента И 20 будетблокирует его. Нулевой сйгнал, посту- сформирован нулевоч сигнал, С выхопающий с поля метки регистра 5 на пер- дов 26-28 блоков 1 памяти микровьй входчетвертого элемента И 20, 20 команд информация поступит на соотблокирует работу этого элемента. По ветствующие входы блока 2 свертки,синхроимпульсу, поступающему с второ- а также на входы коммутатора 15 адго выхода генератора 8 тактовых им- реса регистра 5 микроо е9микроопераций и репульсов, на выходах третьего 16 и гистра 6 контрольного признака, соотчетвертого 20 элементов И будет сфор ветственно.мирован нулевой сигнал, которьй,прой- На выходе блока 2 свертки будетдя через третий элемент ИЛИ 21 посту- сформировано фактическое значениепит на.информационный вход триггера контрольного признака, которое посту 11 отказа. По этому же импульсу на пит на первый информационный входвыходе первого элемента И 13 будет ЗО блока 3 сравнения. На второй входсформирован единичный сигнал, кото- этого блока поступит требуемое знаый поступит на синхровход регистра чение К контрольного признака. При6 контрольного признака и разрешит правильном функционировании устройсттем самым запись в него контрольного ва на третий вход открытого третьегопризнака, поступающего с второго выхо- элемента И 16 поступит нулевой сиг 35да 27 блока 1 памяти микрокоманд и нал, который закрывает его. В томзаписанного в поле логических усло- случае, если на выходе блока 3 сраввий первой микрокоманды. По заднему нения будет единичный сигнал чтоу Эфронту этого импульса микроопераци- говорит о неравенстве К и К , послеонная часть первой микрокоманды и поступления импульса опроса на вто 40метка запишутся в регистр 5 микро-рой вход третьего элемента И 16 едиопераций, триггер 10 управления пе- ничный сигнал через третий элементрейдет в единичное состояние, а в ИЛИ 21 поступит на вход триггера 11 триггере 9 и триггере 11 по заднему отказа, По заднему фронту этого шефронту этого импульса будет под 45импульса триггер 11 отказа перейдеттверждено их нулевое состояние, в единичное состояние и через второйЗначения сигналов микроопера Ий элемент ИЛИ 19 установит в "0" триг-, поступят с выхода 29 регистра 5 мик- гер 7 пУска. В результате работа Роопераций на выход устройства, Ну Устройства будет блокирована.левой сигнал с выхода конца команды 50 В этом случае, если микрокомандасчитана правильно, устройство будетпоступит на первый управляющий вход функционировать до тех пор, пока некоммутатора 15 адреса, и адрес оче- будет считана из блока 1 памяти микреднрй микрокоманды поступит на ин- рокомапд микрокоманда ветвления.формационный вход регистра 4 адреса. 55 При этом произойдет контроль правильПо заднему фронту очередного тактово- ности ее считывания из блока памятиго импульса, поступившего с первого микрокоманд по рассмотренному алговыхода генератора 8 тактовых импуль- ритму, Сигнал метки с выхода 28 бло 1180."88ка 1 памяти микрокоманд закрывает первьй элемент И 13 и открывает второй элемент И 17. Код проверяемых логических условий с выхода 27 блока 1 памяти микрокоманд поступает на вход мультиплексора 12 логических условий.Значение проверяемого логического условия Формируется. на выходе мультиплексора 12. 10При положительном исходе проверки значений логических условий единичный сигнал поступит на второй вход второго элемента И 17 и далее на вход первого элемента ИЛИ 18, на второй вход которого поступает нулевое значение модифицируемого младшего разряда адреса. Модифицированньй таким образом адрес первой микро- команды, следующей за микрокомандой 2 О ветвления, поступает на первый информационньй вход коммутатора 15 адреса и далее в регистр 4 адреса. Единичный сигнал с выхода второго элемента И 17 поступает также на инфор мационньй вход триггера 3 логических условий, По тактовому импульсу, поступающему с второго выхода генератора 8 на второй вход третьего элемента И 16, произойдет опрос результата контроля правильности считывания микрокоманды ветвления из блока 1 памяти микр ок оманд.Если микрокоманда ветвления считана правильно, то по заднему Фронту35 этого импульса будет подтверждено нулевое состояние триггера 11 отказа, триггер 9 логических условий перейдет в единичное состояние, в регистр 5 микроопераций будет записана микро- операционная часть микрокоманды ветвления. На выходе поля метки этого регистра будет сформирован единичный сигнал, который закроет третий элемент И 16 и откроет четвертый элемент И 20. По очередному тактовому импульсу, поступившему с первого вьйода 8,произойдет запись кода адреса микро- команды, следующей за микрокомандой ветвления, в регистр 4 адреса и считывания этой микрокоманды из блока 1 памяти микрокоманд. Значение младшего разряда кода адреса этой микрокоманды поступает на первый вход схемы 14 сравнения, Условием правильного перехода в микропрограмме по положительному исходу проверки логических условий является единичное значение младшего рязряда кода адреса. Таким образом, в случае правильного, перехода в микропрограмме на первый вход схемы 14 сравнения поступает единичный сигнал и на его выходе будет сформирован нулевой сигнал. В случае неправильного выполнения перехода значение сигнала на выходе четвертого 20 элемента И будет равно "1", сигнал с выхода четвертого элемента И 20 поступит через третий элемент ИЛИ 21 на информационньй вход триггера 11 отка" за и по заднему Фронту импульса с второго выхода генератора 8 установит его в "1",и работа устройства будет блокирована.В том случае, если значение проверяемых логических условий будет равно "0", модификация адреса микро- команды перехода производиться не будет, и триггер 9 логических условий останется в нулевом состоянии. После записи кода адреса микрокоманды перехода в регистр 3 адреса произойдет сравнение значения младшего разряда кода адреса этой микрокоманды и нулевого сигнала с единичного выхода триггера 9 логических условий, Результатом ошибочного перехода в микропрограмме будет единичное значение младшего разряда кода адреса микрокоманды перехода. Тогда на выходе схемы 14 сравнения будет сформирован единичный сигнал, которьй установит триггер 11 в "1" и блокирует работу устройства.1180888 иг,8 Составитель И.СигалТехред М.Гергель Зака.з одписно Пат г,ужгород, ул,Проектная,4 1 илпа едактор В.Да 47НИИПИпо дЗОЗ 5 Тираж 709 осударственног ам изобретений осква, Ж, Р коми отк шска

СмотретьЗаявка

3708705, 11.03.1984

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, САМАРСКИЙ ВИКТОР БОРИСОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, КОРОЛЕВ АНАТОЛИЙ ВИКТОРОВИЧ, СОРОКА ЛЕОНИД СТЕПАНОВИЧ

МПК / Метки

МПК: G06F 11/00, G06F 9/22

Метки: микропрограммное

Опубликовано: 23.09.1985

Код ссылки

<a href="https://patents.su/8-1180888-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Генератор случайных последовательностей

Следующий патент: Многоканальное устройство для обслуживания запросов со сменными кодами приоритетов

Случайный патент: Устройство для получения холода