Устройство для формирования адресов операндов процессора быстрого преобразования фурье

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

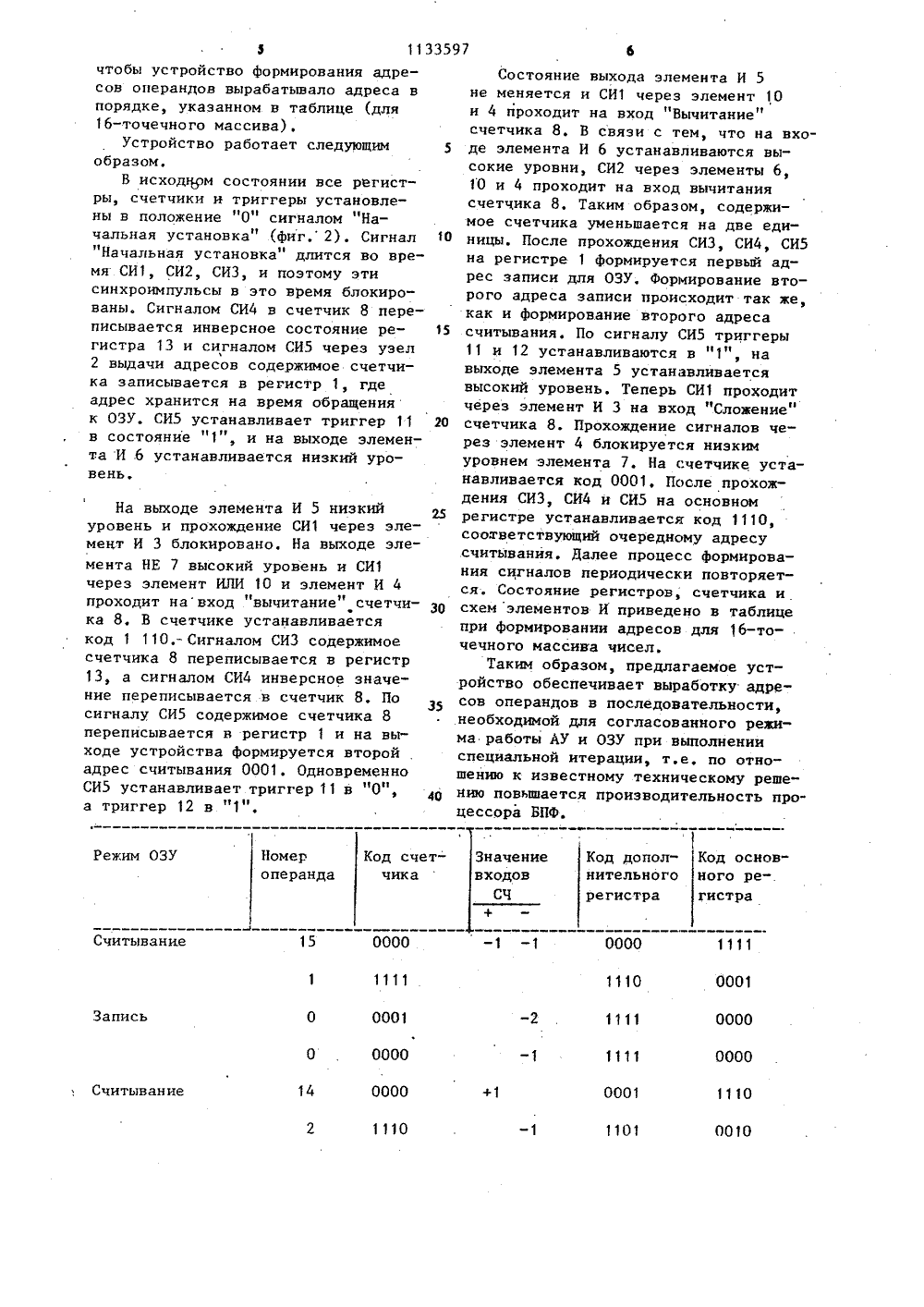

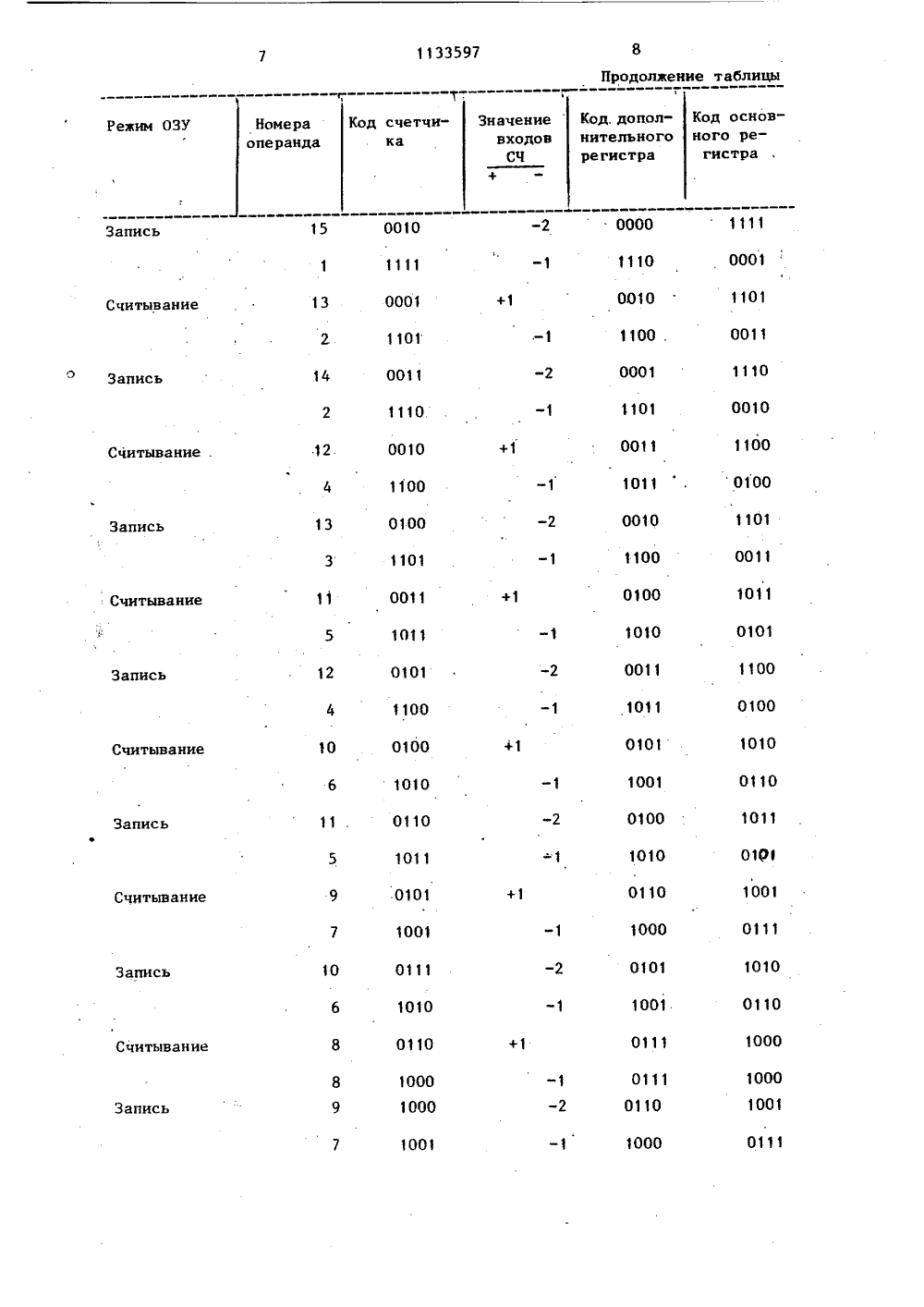

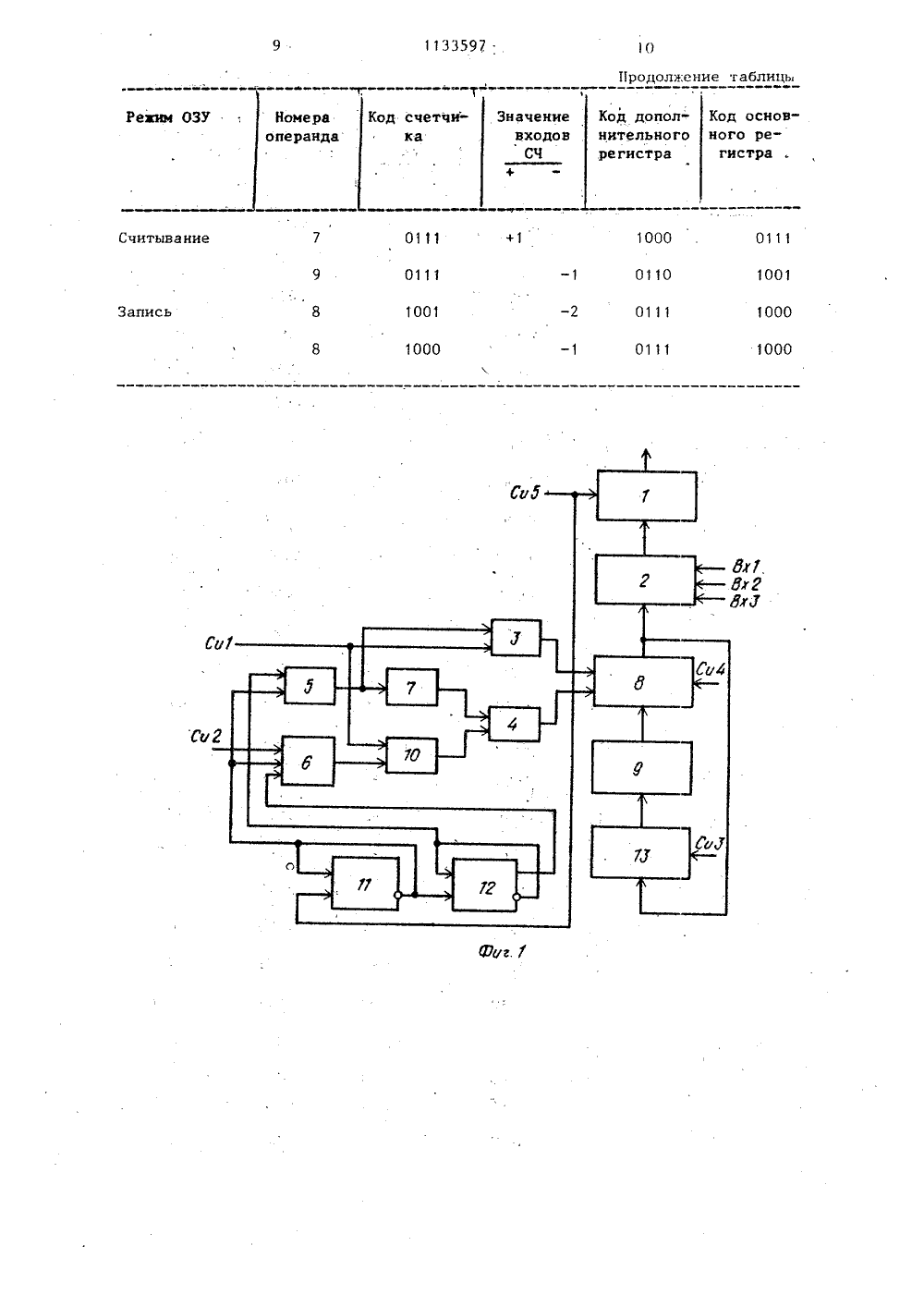

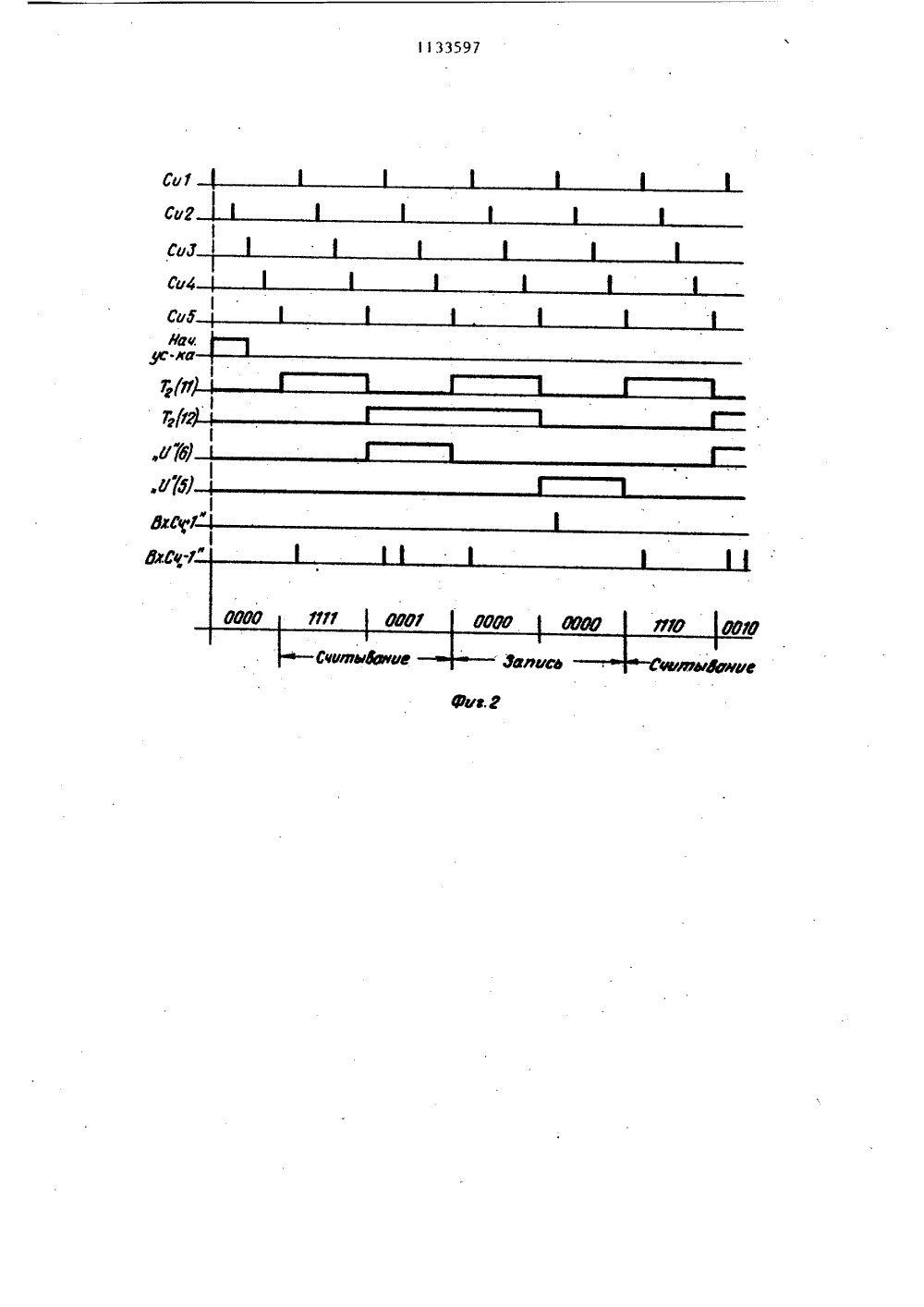

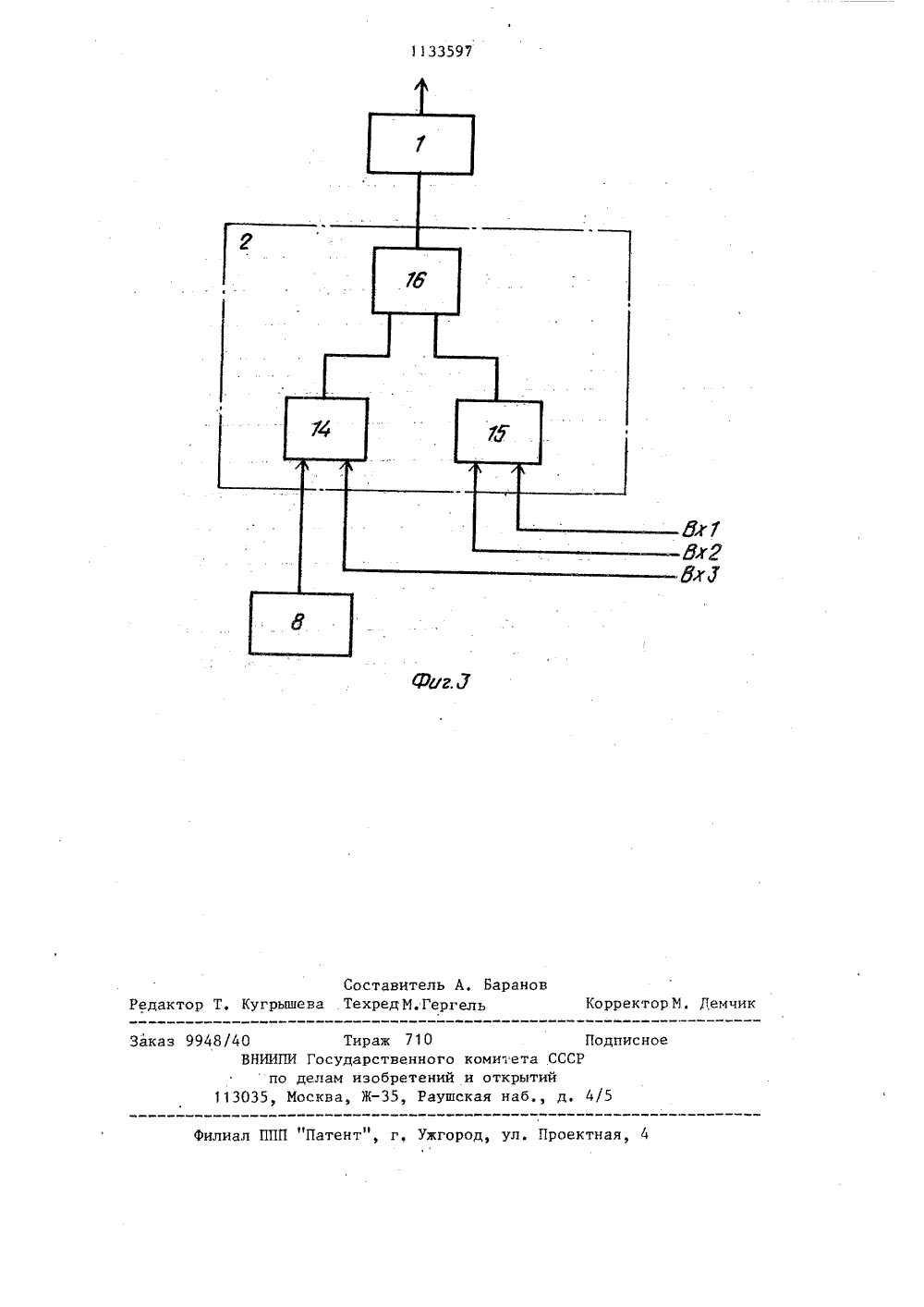

)к ПИСАНИЕ ИЗОБРЕТЕ ЕЛЬСТ ОМЪ/ СВ ВТ ГОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(56) 1. Авторское свидетельство ССС Ф 888130, кл. С 01 Р 15/332, 1980.2, Авторское свидетельство СССР У 788114, кл, С 06 Р 15/31, 1979.3. Авторское свидетельство СССР К 548863, кл, С 06 Г 15/332, 1976 (прототип).(54)(57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ОПЕРАНДОВ ПРОЦЕССОРА БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее первую и вторую группы элементов И, выходы которых подключены к первому и второму входам соответствующих элементов ИЛИ группы, выходы которых подключены к информационным входам соответствующих разрядов первого регистра адреса, информационный выход которого является информационным выходом устройства, первые входы элементов И первой группы объединены и являются входом запрещения формирования адреса устройства, а первые входы элементов И второй группы соединены и являются входом разрешения формирования адреса устройства, группой информационных входов которого являются вторые входы соответствующих элементов И второй группы, второй регистр адреса, о т л и ч а ю щ е - е с я тем, что, с целью повышения быстродействия, в него введены первый, второй, третий и четвертый элементы И, элемент НЕ, элемент ИЛИ, первый и второй Э -триггеры, группа элементов НЕ, реверсивный счетчик,. информационные выходы разрядов второго регистра адреса подключены квходам соответствующих элементов НЕгруппы, выходы которых подключены кинформационным входам соответствующихразрядов реверсивного счетчика, информационные выходы разрядов которого подключены к вторым. входам соответствующих элементов И первой группы и информационным входам соответствующих разрядов второго регистраадреса, суммирующий вход реверсивного счетчика подключен к выходу первого элемента И, первый вход которогосоединен с входом элемента НЕ и подключен к выходу второго элемента И,первый вход которого соединен с2-входом первого 2-триггера и подключен к инверсному выходу первогоЗ-триггера, прямой выход которогоподключен к первому входу третьегоэлемента И, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к первому входу четвертого элемента И, выход которого подключен к вычитающему входу реверсивного счетчика, второйвход четвертого элемента И подключенк выходу элемента НЕ, инверсныйвыход второго 2 -триггера подключен кО-входу второго 2 -триггера, счетномувходу первого З-триггера, второмувходу второго элемента И и второмувходу третьего элемента И, третийвход которого является первым тактовым входом устройства, вторым итретьим тактовыми входами которогоявляются тактовые входы соответственно реверсивного счетчика и второгорегистра адреса, второй вход элемента ИЛИ и второй вход первого злемен 1133597та И соединены и являются четвертым счетный вход второго Х 1 -триггера и тактовым входом устройства, пятым тактовых вход первого регистра адретактовым входом которого является са.1Изобретение относится к вычислительной технике и может быть использовано в специализированных процессорах, реализующих алгоритм быстрогопреобразования Фурье (БПФ) для адресации операндов при обработке действительных сигналов,Известно индексное устройствопроцессора быСтрого преобразованияФурье, содержащее счетчики, сдвиговый регистр, регистры, адресный переключатель и устройство управления Я .Недостатком данного устройстваявляется то, что при вычислении спект-.ров действительных сигналов производится повышенное число арифметических операций.Известен процессор быстрого преобразования Фурье, содержащий арифметическое устройство, блокг памяти, 20регистры, формирователь сигналовприращений регистров, счетчики, узегформирования дополнительного кода,блока сравнения и устройства управления.25В данном процессоре блок сравненияпри появлении адресов комплексносопряженных гармоник вырабатываетсигнал запрета выполнения арифметических операций, и происходит формирование следующего адреса. Такимобразом, в процессоре за счет исключения избыточных операций, связанныхс вычислением комплексно-сопряженныхгармоник, увеличивается быстродейст- З 5вие в два раза 2 .Недостатком данного устройстваявляется то, что оно не позволяетобеспечить согласованный режим работы оперативного запоминающего устройства и арифметического устройства.Кроме того, оперативная память данного процессора используется неэффективно.45Наиболее близким по техническойсущности к изобретению являетсяблок формирования адресов для уст 2,ройства, реализующего быстрое преобразование Фурье, который содержит узел реконфигурации счетчика, счетчик-регистр, группу элементов ИЛИ и блок выдачи адресов.Входной информацией для блока являются признаки итерации. Блок вырабатывает адреса операндов для реализации алгЬритма БПФ с помощью узла реконфигурации, счетчика элементов ИЛИ, которые поступают на узел выдачи адресов. Для формирования адресов операндов специальной итерации, реализующей так называемый безызбыточный алгоритм БПФ, используется дополнительный регистр и вход узла выдачи адресов 3,Недостатком известного устройства является то, что оно формирует адреса операндов только в прямой пос-. ледовательности, поэтому не позволяет обеспечить согласованный режим работы оперативного запоминающего устройства и арифметического устройства в процессоре БПФ.Целью изобретения является повышение быстродействия (за счет формирования адресов операндов для согласованного режима работы ОЗУ и АУ процессора БПФ при выполнении специальной итерации безызбыточного. алгоритма БПФ).Поставленная цель достигается тем, что в устройство для формирования адресов операндов процессора быстрого преобразования Фурье, содержащее первую и вторую группы элементов И, выходы которых подключены соответственно к первому и второму входам соответствующих элементов ИЛИ группы, выводы которых подключены к информационным входам соответствующих разрядов первого регистра адреса, информационный выхсд которого является информационным выходом устройства, первые входы элементов И первой группы объединены и являются входом запрещения формирования адре1 133597 х(п)+х(И-и) у(п) с= 4 с а чс 11)ф.1 ЙстВ;1 а 11 ернье Входь эле-.ментов И Второй группы соединены иЯ ВЛЯЮТС Я ВХОДОМ РЯЗ РЕИ 1 Е 11 ЙЯ фОРМИРО -вания адреса устройства, группой инфОРМаЦИОННЫХ ВХОДОВ КОТорОГО ЯВЛЯЮТся вторые входы соответствующих элементов И второй группы, второй регистр адреса, введены первь 1 й, второй,третий и четвертый элементы И, элемент НЕ, элемент ИЛИ, первый и второй 1)-триггеры, группа элементов НЕ,реверсивный счетчик 1 информационныевыходы разрядов второго регистраадреса подключены к входам соответствующих элементов НЕ группы, выходы 15которых подключены к информационным входам соответствующих разрядовреверсивного счетчика, информационные выходы разрядов которого подключены к вторым входам соответствующих элементов И первой группы и информационным входам соответствующихразрядов второго регистра, адреса,суммирующий вход реверсивного счетчика подключен к выходу первого элемента И, первый вход которого соединен с входом элемента НЕ и подключенк выходу Второго элемента И, первый вход которого соединен с 3 -входом первого 3-триггера и подключен кинверсному выходу первого 3 -триггера, прямой выход которого. подключенк первому входу третьего элемента И,выход которого подключен к первомувходу элемента ИЛИ, выход которогоподключен к первому входу четвертогоэлемента И; выход которого подключенк вычитающему входу реверсивногосчетчика, второй вход четвертогоэлемента И подключен к выходу элемен та НЕ, инверсный выход второгоЗ-триг.гера подключен к Р-входу второгоР-триггера, счетному входу первого3-триггера, второму входу второгоэлемента И и второму входу третьегоэлемента И, третий вход которогоявляется первым тактовым входом устройства, вторым и третьим тактовымивходами которого являются тактовыевходы соответственно реверсивногосчетчика и второго регистра адреса,второй вход элемента ИЛИ и второйвход первого элемента И соединеныи являются четвертым тактовым входомустройства, пятым тактовым входом которого является счетный вход второго 2 -триггера и тактовый вход первого регистра адреса. 4На фиг. 1 представлена функциональная схема предлагаемого устройства; Ва фиг, 2 - временная диаграмма работы предлагаемого устройства;на фиг. 3 - блок-схема узла выдачи адресов.Устройство для формирования адресов содержит регистр 1 адреса, узел 2 Выдачи адресов, элементы И 3-6, элемент НЕ 7, реверсивный счетчик 8, группу 9 элементов НЕ, элемент ИЛИ 10, триггеры 11 и 12, регистр 13 адреса.Узел 2 содержит группы 14 и 15 элементов И, группу 16 элементов ИЛИ. При выполнении итерации БПФ на вход 1 узла 2 поступают адреса операндов,. На вход 1 подан разрешающий потенциал, а на вход 3 - запрещающий, Адреса операндов через узел 2 поступают на регистр 1 адреса, а далее к ОЗУ. При выполнении специальной итерации БПФ на вход 3 поступает разрешающий потенциал, а на вход 1 - запрещающий, В этом случае адреса операндов поступают на регистр 1 адреса через Вход 4 от счетчика 8.Известно, что специальная итерация алгоритма БПФ для действительных массивов имеет,вид 4Ф х (и) -х(М-и)у (11-и)2 Яг"е п=1 до -- 12 ф- знак комплексно-сопряженных чисел.Таким образом, для выполнения специальной итерации необходимо считать два.числа х(п) и х(И-п), произвести вычисления в АУ и записать результаты у(п) и у(М-и) по тем же адресам в ОЗУ.Для обеспечения согласованного режима работы ОЗУ и АУ должно выполняться соотношение где 1 - время выполнения вычисле 1 уний в АУ;- время обращения к ОЗУ,При выполнении этого соотношения АУ и ОЗУ будут работать одновременно, обеспечивая максимальную производительность процессора. Для обеспечения такого режима необходимо,1133597 Код основного ре-. Код допол- нительного ЗначениевходовСЧ Код счетчикаНомероперанда Режим ОЗУ гистра регистра 0000 ОООО Считывание 0001 1110 0000 0001 0 Запись 0000 0 0000 0000 0001 1110 Считывание 0010 1101 1 110 чтобы устройство формирования адресов операндов вырабатывало адреса в порядке, указанном в таблице (для 16-точечного массива).Устройство работает следующим 5 образом.В исходном состоянии все регистры, счетчики и триггеры установлены в положение "0" сигналом "Начальная установка" (фиг, 2), Сигнал 1 О "Начальная установка" длится во время СИ 1, СИ 2, СИЗ, и поэтому эти синхронмпульсы в это время блокированы, Сигналом СИ 4 в счетчик 8 переписывается инверсное состояние ре гистра 13 и сигналом СИ 5 через узел 2 выдачи адресов содержимое счетчика записывается в регистр 1, где адрес хранится на время обращения к ОЗУ. СИ 5 устанавливает триггер 11 20 в состояние "1", и на выходе элемента И 6 устанавливается низкий уровень. На выходе элемента И 5 низкий уровень и прохождение СИ 1 через элемент И 3 блокировано, На выходе элемента НЕ 7 высокий уровень и СИ 1 через элемент ИЛИ 10 и элемент И 4 проходит навход "вычитание" счетчика 8, В счетчике устанавливается код 1 110. - Сигналом СИЗ содержимое счетчика 8 переписывается в регистр 13, а сигналом СИ 4 инверсное значение переписывается в счетчик 8, По сигналу СИ 5 содержимое счетчика 8 переписывается в регистр 1 и на выходе устройства формируется второй адрес считывания 0001. Одновременно СИ 5 устанавливает триггер 11 в "0", а триггер 12 в "1". Состояние выхода элемента И 5 не меняется и СИ 1 через элемент 10 и 4 проходит на вход "Вычитание" счетчика 8. В связи с тем, что на входе элемента И 6 устанавливаются высокие уровни, СИ 2 через элементы 6, 10 и 4 проходит на вход вычитания счетчика 8, Таким образом, содержимое счетчика уменьшается на две единицы, После прохождения СИЗ, СИ 4, СИ 5 на регистре 1 формируется первый адрес записи для ОЗУ, Формирование второго адреса записи происходит так же, как и формирование второго адреса считывания, По сигналу СИ 5 триггеры 11 и 12 устанавливаются в "1", на выходе элемента 5 устанавливается высокий уровень, Теперь СИ 1 проходит через элемент И 3 на вход "Сложение" счетчика 8. Прохождение сигналов через элемент 4 блокируется низким уровнем элемента 7, На счетчике устанавливается код 0001, После прохождения СИЗ, СИ 4 и СИ 5 на основном регистре устанавливается код 1110, соответствующий очередному адресу считывания. Далее процесс формирования сигналов периодически повторяется. Состояние регистров, счетчика и схем элементов И приведено в таблице при формировании адресов для 16-точечного массива чисел.Таким образом, предлагаемое устройство обеспечивает выработку адресов операндов в последовательности, необходимой для согласованного режима работы АУ и ОЗУ при выполнении специальной итерации, т,е, по отношению к известному техническому реше" нию повышается производительность процессора БПФ.Значение Режим ОЗУ 0010 Запись 0000 15 1110 0001 1101 0010 13 СчитываниеКод дополнительногорегистра Код основного ре- гистра1133597 но Заказ 9948 4/ шская наб илиал ППП Патент", г. Ужгород, ул. Проект Составитель едактор Т, Кугрышева .ТехредМ,ГерТираж 710 ИИПИ Государственногпо делам изобретени 5, Москва, Ж, Рау комитета Си открытий Корректор М, ДемПодписное

СмотретьЗаявка

3658228, 09.08.1983

ПРЕДПРИЯТИЕ ПЯ В-2962

ВУКОЛОВА ЗОЯ АНАТОЛЬЕВНА, ШАНЬГИН ВЛАДИМИР АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 17/14, G06F 9/34

Метки: адресов, быстрого, операндов, преобразования, процессора, формирования, фурье

Опубликовано: 07.01.1985

Код ссылки

<a href="https://patents.su/8-1133597-ustrojjstvo-dlya-formirovaniya-adresov-operandov-processora-bystrogo-preobrazovaniya-fure.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования адресов операндов процессора быстрого преобразования фурье</a>

Предыдущий патент: Устройство для определения характеристик связности ориентированного графа

Следующий патент: Вычислительное устройство для первичной обработки сигналов

Случайный патент: Магнитная головка