Система обработки данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 849219

Автор: Антимиров

Текст

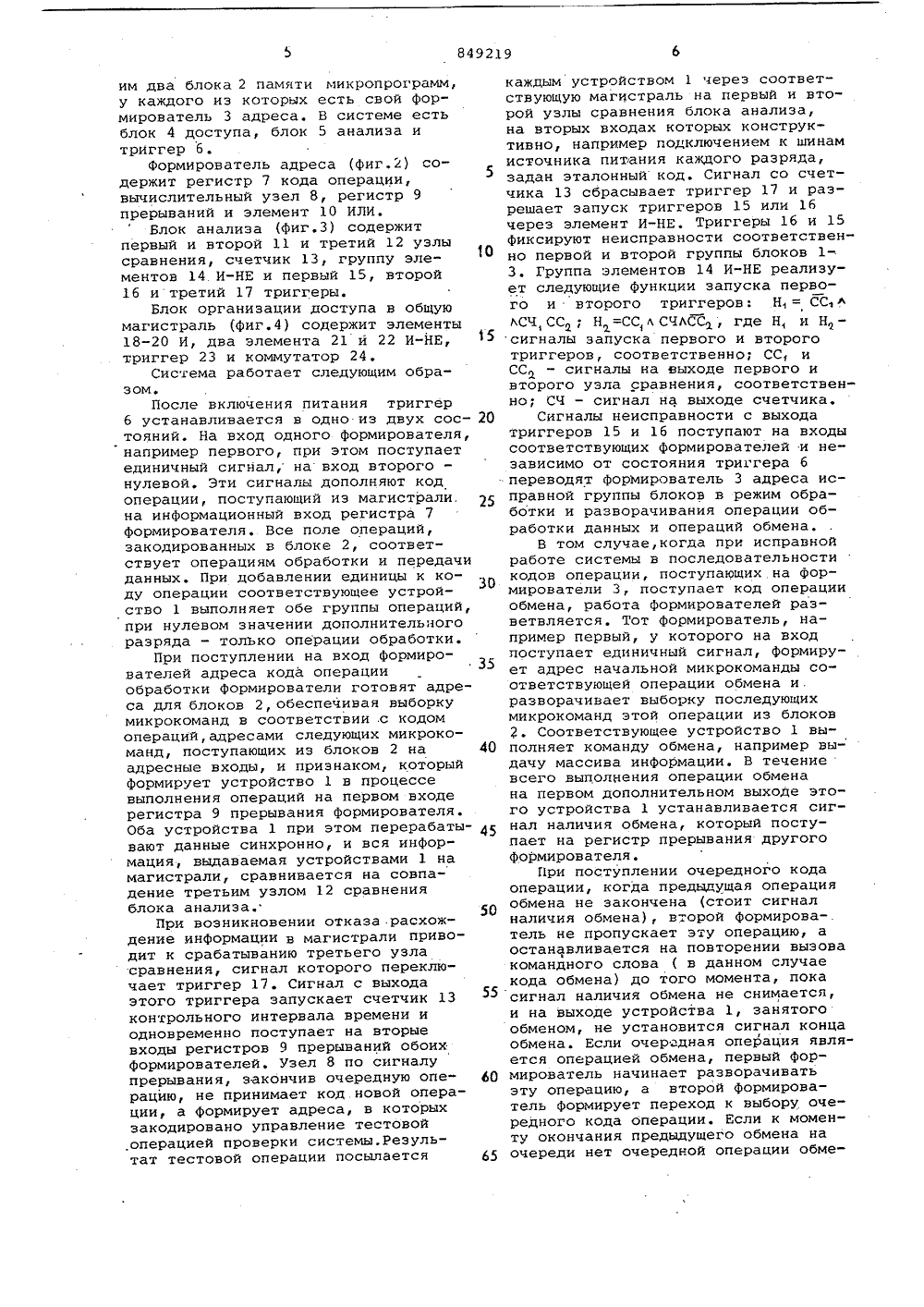

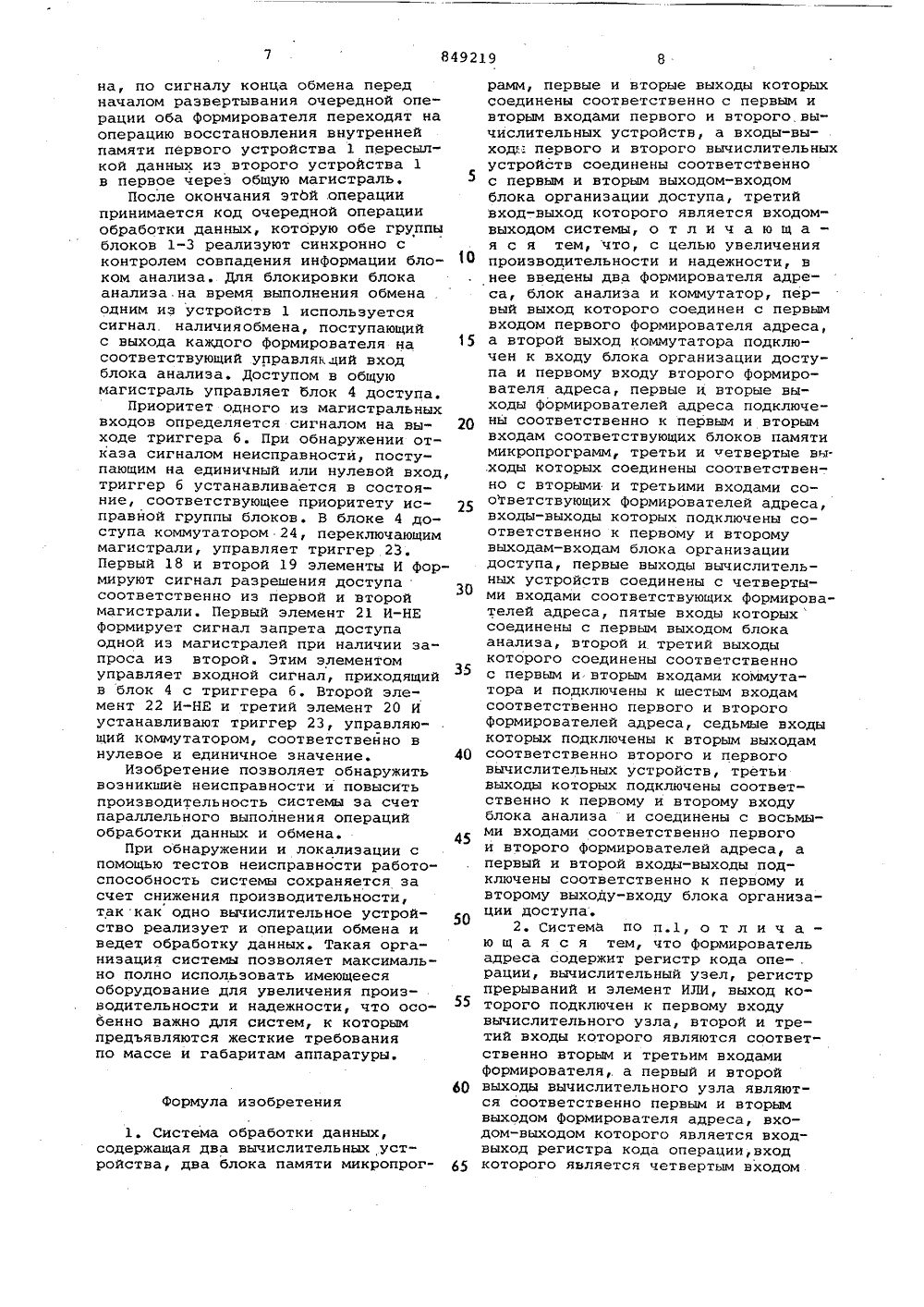

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик) Дополнительное к авт.сви 51 М. К 22) Заявлено 250679 присоединением заявк 23) Приоритет 6/18-24 1) 2787 б Г 15 осуда рственнын комитетСССРлам изобретенийн открытий ень М 27. Бюлл исанкя публиковано 23,(53) УДК 681,(088.) Заяви 4) СИСТЕМА ОБРАБОТКИ ДАНН 5 0 ва - при испулей создается дительность, а перерабатыации. та ва Изобретение относится к вычислительной технике и может быть использовано при построении систем переработки цифровой информации.Известна управляющая цифровая вычислительная машина, содержащая двегруппы резервных модулей (арифметическое устройство, запоминающее устройство и устройство управления),связанные через коммутаторы. При отхазе одного из модулей работоспособ-,ность сохраняется, так как вместоотказавшего подключается резервныймодуль 1,Недостаток устройстравной работе всех моднеиспользуемая произвок как ЦВМ не способнть два потока информ Известна также система, содержащая два идентичных процессора со схемами доступа к ним. Один из процессоров является активным и только его. схема доступа обеспечизает выход процессора на внешние шины. Второй процессор является резервным (2.Однако при исправности обоих процессоров система имеет неиспользуемую вычислительную избыточность. 3 О Наиболее близкой к изобретению является модульная цифровая вычислительная система., в которой имеется несколько процессоров с соответствующими управляющими запоминающими устройствами, общее устройство управления и схема переключения признаков процессоров. В известной системе при отказе одного из процессоров формируется признак, по которому задачи отказавшего берет на себя исправный процессор (3.Недостатком системы является то, что для обнаружения отказа в каждый из процессоров должно устанавливаться дополнительное контрольное оборудование, которое не может использоваться для повышения производительности.Цель изобретения - увеличение надежности и производительности повышением полноты использования оборудования.Поставленная цель достигается тем, что в систему, содержащую два вычислительных устройства, два блока памяти микропрограмм, первые и вторые выходй которых соединены соответственно с первым и вторым входами первого и второго вычислительных60 устройств, а входы-выходы первого и второго вычислительных устройств соединены соответственно с первым и вторым выходом-входом блока организации доступа, третий вход-выход которого является входом-выходом системы, введены два формирователя5 адреса, блок анализа и коммутатор, первый выход которого соединен с первым входом первого формирователя адреса, а второй выход коммутатора подключен к входу блока организации доступа и первому входу второго Формирователя адреса, первые и вторые выходы формирователей адреса подключены соответственно к первым и вторым входам соответствующих блоков памяти микропрограм , третьи и четвертые выходы которых соединены соответственно с вторыми и третьими входами соответствующих формирователей адреса, входы-выходы которых 20 подключены соответственно к первому и второму выходам-входам блока организации доступа, первые выходы вычислительных устройств соединены с четвертыми входами соответствующих 25 формирователей адреса, пятые входы которых соединены с первым выходом блока анализа, второй и третий выходы которого соединены соответственно с первым и вторым входами комму- З 0 татора и подключены кшестым входам соответственно первого и второго формирователей адреса, седьмые входы которых подключены к вторым выходам соответственно второго и первого вычислительных устройств, третьи выходы которых подключены соответственно к первому и второму входу блока анализа и соединены с восьмыми входами соответственно первого и второго формирователей адреса, а первый 40 и второй входы-выходы подключены соответственно к первому и второму выходу-входу блока организации доступа.Кроме того, формирователь адреса 45 содержит регистр кода операции, вычислительный узел, регистр прерываний и элемент ИЛИ, выход которого подключен к первому входу вычислительного узла, второй и третий входы 50 которого являются соответственно вторым и третьим входами формирователя, а первый и второй выходы вычислительного узла являются соответственно первым и вторым выходомФормирователя адреса, входом-выходом которого является вход-выход регистра кода операции, вход которого является четвертым входом формирователя адреса, первый, второй, третий, четвертый и пятый входы регистра прерываний являются соответственно первым, пятым, шестым, седьмым и восьмым входами формирователя адреса, второй вход-выход регистра кода операции подключен к выходу-входу 65 вычислительного узла и выходу-входу регистра прерываний, первый и второй выходЬ которого подключены соответственно к первому и второму входам элемента ИЛИ.При этом блок анализа содержит три триггера, три узла сравнения, счетчик и группу элементов И-НЕ, первый и второй выходы которых соединены с входами соответственно первого и второго триггеров, выходы которых являются соответственно вторым и третьим выходами блока анализа, выходы первого и второго узлов сравнения и счетчика соедийены соответственно с первыми, вторыми и третьими входами элементЬв,.И-НЕ группы, выход счетчика соединен с первым входом третьего триггера, выход которого. соединен с входом счетчика и является первым выходом блока, второй вход третьего триггера подключен к выходу третьего узла сравнения, первый и второй входы которого являются соответственно первым и вторым входами блока, вход- выход первого узла сравнения и первый вход-выход третьего узла сравнения являются первым выходом-входом блока анализа, а вход-выход второго узла сравнения и второй вход-выход третьего узла сравнения являются вторым входом-выходом блока.Кроме того, блок организации доступа содержит три элемента И, два элемента И-НЕ, триггер и коммутатор, первый и второй вход-выход которого являются соответственно первым и вторым входами-выходами блока, а третий вход-выход коммутатора является третьим входом-выходом блока, выход первого элемента И-НЕ подключен к первому входу второго элемента И-НЕ, выход которого подключен к первому входу триггера и первому входу первого элемента И, выход которого соединен с вторым входом триггера, первый выход которого подключен к входу коммутатора и первому входу второго элемента И, вторые входы первого и второго элементов И, первый вход первого элемента И-НЕ и выход второго элемента И соединены с первым входом-выходом коммутатора, второй выход триггера подключен к первому входу третьего элемента И, а вторые входы третьего элемента И и второго элемента И-НЕ и выход третьего элемента И соединены с вторым входом-выходом коммутатора, а второй вход первого элемента И-НЕ является входом блока.На фиг,1 приведена структурная схема предлагаемой системы; на фиг,2 - схема формирователя адреса; на фиг.З = схема блока анализа;на фиг,4 - схема блока доступа.Система содержит два вычислительных устройства 1, соответствующиеим два блока 2 памяти микропрограмм,у каждого из которых есть свой формирователь 3 адреса. В системе естьблок 4 доступа, блок 5 анализа итриггер 6.Формирователь адреса (фиг,2) содержит регистр 7 кода операции,вычислительный узел 8, регистр 9прерываний и элемент 10 ИЛИ.Блок анализа (фиг.3) содержитпервый и второй 11 и третий 12 узлысравнения, счетчик 13, группу элементов 14 И-НЕ и первый 15, второй16 итретий 17 триггеры.Блок организации доступа в общуюмагистраль (фиг.4) содержит элементы18-20 И, два элемента 21 и 22 И-НЕ,триггер 23 и коммутатор 24.Система работает следующим образом.После включения питания триггер6 устанавливается в одно из двух состояний. На вход одного формирователя,например первого, при этом поступаетединичный сигнал, на вход второгонулевой, Эти сигналы дополняют кодоперации, поступающий из магистрали.на информационный вход регистра 7формирователя. Все поле операций,закодированных в блоке 2, соответствует операциям обработки и передачиданных. При добавлении единицы к коду операции соответствующее устройство 1 выполняет обе группы операций,при нулевом значении дополнительногоразряда - только операции обработки.При поступлении на вход формирователей адреса кода операцииобработки Формирователи готовят адреса для блоков 2,обеспечивая выборкумикрокоманд в соответствии .с кодомопераций, адресами следующих микрокоманд, поступающих из блоков 2 на 40адресные входы, и признаком, которыйформирует устройство 1 в процессевыполнения операций на первом входерегистра 9 прерывания формирователя.Оба устройства 1 при этом перерабатывают данные синхронно, и вся информация, выдаваемая устройствами 1 намагистрали, сравнивается на совпадение третьим узлом 12 сравненияблока анализа.50При возникновении отказа .расхождение информации в магистрали приводит к срабатыванию третьего узласравнения, сигнал которого переключает триггер 17. Сигнал с выходаэтого триггера запускает счетчик 13контрольного интервала времени иодновременно поступает на вторыевходы регистров 9 прерываний обоихформирователей. Узел 8 по сигналупрерывания, закончив очередную операцию, не принимает код новой операции, а формирует адреса, в которыхзакодировано управление тестовой.операцией проверки системы.Результат тестовой операции посылается 65 каждым устройством 1 через соответствующую магистраль на первый и второй узлы сравнения блока анализа, на вторых входах которых конструктивно, например подключением к шинам источника питания каждого разряда, задан эталонный код. Сигнал со счетчика 13 сбрасывает триггер 17 и разрешает запуск триггеров 15 или 16 через элемент И-НЕ, Триггеры 16 и 15 фиксируют неисправности соответственно первой и второй группы блоков 1- 3. Группа элементов 14 И-НЕ реализует следующие Функции запуска первого и второго триггеров: Н, = СС 1лсч СС 2 Н=ССл СЧЬССх где Ни И- сигналы запуска первого и второготриггеров, соответственно; СС, иСС - сигналы на выходе первого ивторого узла сравнения, соответственно; СЧ - сигнал на выходе счетчика,Сигналы неисправности с выходатриггеров 15 и 16 поступают на входысоответствующих формирователей и независимо от состояния триггера 6переводят формирователь 3 адреса исправной группы блоков в режим обработки и разворачивания операции обработки данных и операций обмена,В том случае, когда при исправной работе системы в последовательности кодов операции, поступающих на формирователи 3, поступает код операции обмена, работа формирователей разветвляетсяТот формирователь, например первый, у которого на вход поступает единичный сигнал, формирует адрес начальной микрокоманды соответствующей операции обмена и. разворачивает выборку последующих микрокоманд этой операции из блоков 2. Соответствующее устройство 1 выполняет команду обмена, например выдачу массива информации. В течение всего выполнения операции обмена на первом дополнительном выходе этого устройства 1 устанавливается сигнал наличия обмена, который поступает на регистр прерывания другого формирователяПри поступлении очередного кода операции, когда предыдущая операция обмена не закончена (стоит сигнал наличия обмена), второй формирова-. тель не пропускает эту операцию, а останавливается на повторении вызова командного слова ( в данном случае кода обмена) до того момента, пока сигнал наличия обмена не снимается, и на выходе устройства 1, занятого обменом, не установится сигнал конца обмена. Если очерадная операция является операцией обмена, первый формирователь начинает разворачивать эту операцию, а второй формирователь формирует переход к выбору очередного кода операции. Если к моменту окончания предыдущего обмена на очереди нет очередной операции обме40 бО Формула изобретения 1. Система обработки данных, содержащая два вычислительных устройства, два блока памяти микропрогна, па сигналу конца обмена перед началам развертывания очередной операции оба формирователя переходят на операцию восстановления внутренней памяти первого устройства 1 пересылкой данных из второго устройства 1 в первое через общую магистраль.5После окончания этбй .операции принимается код очередной операции обработки данных, которую обе группы блоков 1-3 реализуют синхронно с контролем совпадения информации бло- О ком анализа. Для блокировки блока анализа.на время выполнения обмена . одним из устройств 1 используется сигнал. наличияобмена, поступающий с выхода каждого формирователя на соответствующий управлякций вход блока анализа, Доступом в общую магистраль управляет блок 4 доступа.Приоритет одного из магистральных входов определяется сигналом на вы ходе триггера б. При обнаружении отказа сигналом неисправности, поступающим на единичный или нулевой вход, триггер б устанавливается в состояние, соответствующее приоритету ис правной группы блоков. В блоке 4 доступа коммутатором 24, переключающим магистрали, управляет триггер 23. Первый 18 и второй 19 элементы И формируют сигнал разрешения доступа соответственно из первой и второй магистралиПервый элемент 21 И-НЕ формирует сигнал запрета доступа одной из магистралей при наличии запроса из второй. Этим элементом управляет входной сигнал, приходящий в блок 4 с триггера б. Второй элемент 22 И-НЕ и третий элемент 20 И устанавливают триггер 23, управляющий коммутатором, соответствейно в нулевое и единичное значение.Изобретение позволяет обнаружить возникшие неисправности и повысить производительность системы за счет параллельного выполнения операций обработки данных и обмена. 45При обнаружении и локализации с помощью тестов неисправности работоспособность системы сохраняется за счет снижения производительности, так как одно вычислительное устройство реализует и операции обмена и ведет обработку данных. Такая организация системы позволяет максимально полно испольэовать имеющееся оборудование для увеличения производительности и надежности, что особенно важно для систем, к которым предьявляются жесткие требования по массе и габаритам аппаратуры. рамм, первые и вторые выходы которых соединены соответственно с первым и вторым входами первого и второго,вычислительных устройств, а входы-выходь: первого и второго вычислительных устройств соединены соответственно с первым и вторым выходом-входом блока органиэации доступа, третий вход-.выход которого является входом- выходом системы, о т л и ч а ю щ а - я с я тем, что, с целью увеличения производительности и надежности, в нее введены два формирователя адреса, блок анализа и коммутатор, первый выход которого соединен с первым входом первого формирователя адреса, а второй выход коммутатора подключен к входу блока организации доступа и первому входу второго формирователя адреса, первые и, вторые выходы формирователей адреса подключены соответственно к первым и вторым входам соответствующих блоков памяти микропрограмм, третьи и четвертые вы. .ходы которых соединены соответственно с вторыми и третьими входами соо 1 тветствующих формирователей адреса, входы-выходы которых подключены соответственно к первому и второму выходам-входам блока организации доступа, первые выходы вычислительных устройств соединены с четвертыми входами соответствующих формирователей адреса, пятые входы которыхсоединены с первым выходом блока анализа, второй и третий выходы которого соединены соответственно с первым и вторым входами коммутатора и подключены к шестым входам соответственно первого и второго формирователей адреса, седьмые входы которых подключены к вторым выходам соответственно второго и первого вычислительных устройств, третьи выходы которых подключены соответственно к первому и второму входу блока анализа и соединены с восьмыми входами соответственно первого и второго формирователей адреса, а первый и второй входы-выходы подключены соответственно к первому и второму выходу-входу блока организации доступа.2. Система по п.1, о т л и ч а - ю щ а я с я тем, что формирователь адреса содержит регистр кода опе- . рации, вычислительный узел, регистр прерываний и элемент ИЛИ, выход которого подключен к первому входу вычислительного узла, второй и третий входы которого являются соответственно вторым и третьим входами формирователя, а первый и второй выходы вычислительного узла являются соответственно первым и вторым выходом формирователя адреса, входом-выходом которого является вход- выход регистра кода операции, вход которого является четвертым входомформирователя адреса, первый, второйи третий, четвертый и пятый входырегистра прерываний являются соответственно первым, пятым, шестым, седьмым и восьмым входами формирователяадреса, второй вход-выход регистракода операции подключен к выходувходу вычислительного узла и выходувходу регистра прерываний, первый ивторой выходы которого подключенысоответственно к первому и второмувходам элемента ИЛИ.03. Система по п.1, о т л и ч а -ю щ а я с я тем, что блок анализасодержит три триггера, три узласравнения, счетчик и группу элементов И-НЕ,.первый и второй выходы 15которых соединены с входами соответственно первого и второго триггеров, выходы которых являются соответственно вторым и третьим выхо: дами блока анализа, выходы первого Щ)и второго узлов сравнения и счетчика соединены соответственно Спервыми, вторыми и третьими входами элементов И-НЕ группы, выходсчетчика соединен с первым входомтретьего триггера, выход которогосоединен с входом счетчика и является первым выходом блока, второйвход третьего триггера подключен квыходу третьего узла сравнения,первый и второй входы которого являются соответственно первым и вторымвходами блока, вход-выход первогоузла сравнения и первый вход-выходтретьего узла сравнения являютсяпервым .выходом-входом блока анализа,а вход-выход второго узла сравненияи второй вход-выход третьего узласравнения являются вторым входомвыходом блока. 4. Система по п.1, о т л и ч а - ю щ а я с я тем, что блок организации доступа содержит три элемента И, два элемента И-НЕ, триггер и коммутатор, первый и второй вход- выход которого являются соответственно первым и вторым входами-выходами блока, а третий вход-выход коммутатора является третьим входом- выходом блока, выход первого элемента И-НЕ подключен к первому входу второго элемента И-НЕ, выход которого подключен к первому входу триггера и первому входу первого элемента И, выход которого соединен с вторым входом триггера, первый выход которого подключен к входу коммутатора и первому входу второго элемента И, вторые входы первого и второго элементов И, первый вход первого элемента И-ЙЕ и выход второго элемента И соединены с первым входом-выходом коммутатора, второй выход триггера подключен к первому входу третьего элемента И, а вторые входы третьего элемента И и второго элемента И-НЕ и выход третьего элемента И соединены с вторым входом- выходом коммутатора, а второй вход первого элемента И-НЕ является входом блока.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР Р 475145, кл. 6 06 Р 15/46, 1973. 2, ПатентСША Р 3806887,кл. С 06 Р 11/00, 1974.849219 по д 113035, Закаэ 6095/64 Подп ВНИИПИ Го ССР Тираж 745сударственного комитета С ам иэобретений и открытий осква, Ж, Раушская наб е

СмотретьЗаявка

2787656, 25.06.1979

ПРЕДПРИЯТИЕ ПЯ В-2969

АНТИМИРОВ ВЛАДИМИР МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: данных

Опубликовано: 23.07.1981

Код ссылки

<a href="https://patents.su/7-849219-sistema-obrabotki-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Система обработки данных</a>

Предыдущий патент: Устройство для отладки программ

Следующий патент: Цифровое устройство для обработкиинформации

Случайный патент: Система комбинированного автоматического управления шахтными подъемными машинами