Система для автоматизированногопроектирования и управления texho-логическими процессами b микроэлектро-нике

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

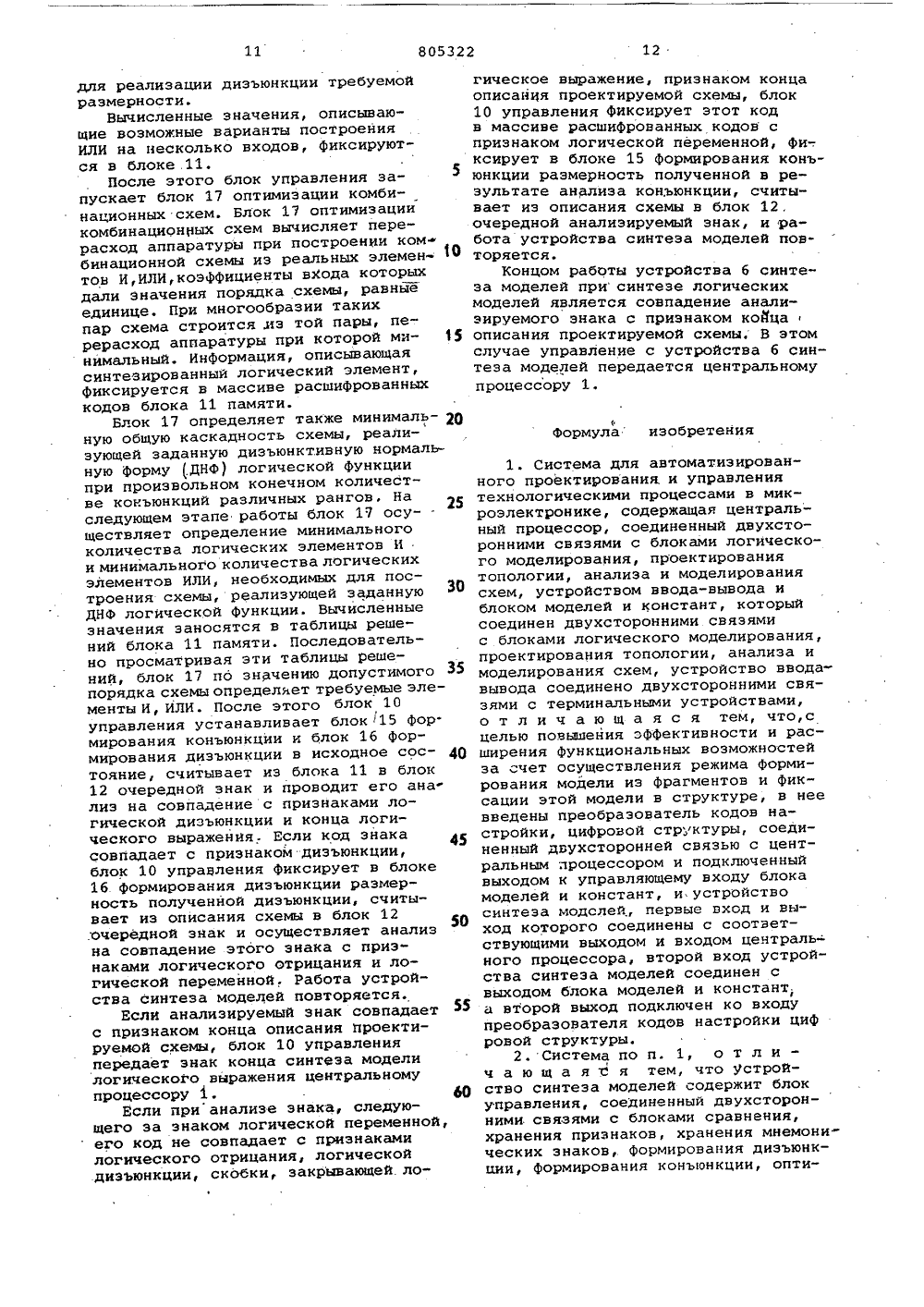

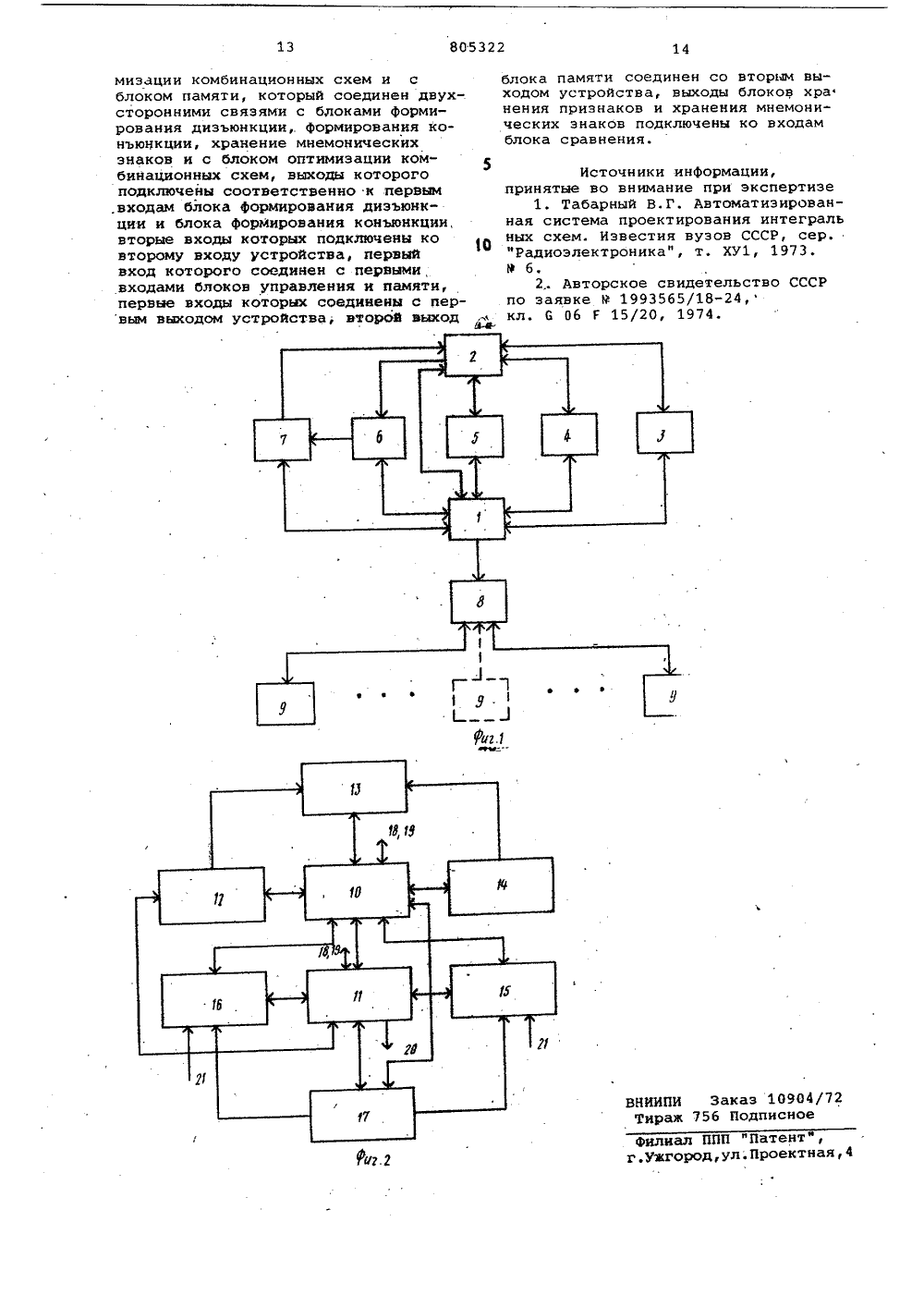

Союз Севеесвпк Соцнвлнстнчесимз РеспубликОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕТИЛЬСТВУ(22) Заявлена 09.03.76 (1) 2324152/16-24с присоединением заявки МУ(51 М. Кл. 6 06 Е 15/20 Гвеуаврствеввмй вемятет СССР вв делам взебретееея в втврытвй. 322 (038. 8) Дате опубеежа 64 ммя еттисемеа 17 02. 61 ТКМА ДПЯ АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯАВЛВНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИВ МИКРОЭЛККТРОИИКВФ2 СИС исли- спольпроек ия техИзобретение относится к вычтельной технике и может быть и зовано для автоматизированногоЯв. тирования узлов ЭВИ и управленнологическими процессамит например для проектирования больщйх интегральных схем ВИС) и управления процессами изготовления их методами электронной литограФии.Известна система автоматизированного.проектирования интеграль- .ных схем, содержащая универсальную ЭВИ н устройства подготовки программ, Эта система включает комплекс прог" раммных средств, привязанных к кои кретным конструкторским и технологи ческим решениям и предназначенных для электрического расчета и ана лиза, проектирования топологии, логического моделирования, подготов й ки управляющей инФормации для устройств изготовления Фотойаблонов и т.д. В основе автоматизированного проектирования устройств лежит тех,ника представления их в виде после- фф довательного ряда моделей, которые в процессе проектирования преобра зуются друг в друга. Основнымиоперациями при этом являются синтез моделей и моделирование. Операции 36 синтеза моделей позволяют осуществить построение проекта схемы, а моделирование - исследовать ее количественные и качественные параметры. При этом разработчиком вырабатывается комплекс коррекции модели в случае, если она не удовлетворяет наперед. заданным требованиям1.Ориентация известной системы на конкретные. схемно-конструкторские И технологические модели ограничивает возможности ее применения для новых технологичеаких методов изготовления ВИС.Наиболее близкой по технологической сущности к изобретению является система, содержащая центральный процессор, соединенный двухсторонними связями с блоками логического моделирования, проектирования топологии, анализа и моделирования схем, устройством ввода-вывода и блоком моделей и констант, который соединен двуистарониими связями с блоками логического моделирования,. проектирования топологии, анализа и моделировании схем, устройство ввода- вывода соединено двухсторонними связями с терминальными устройствами. Данная система позволяет осуществлять автоматическое проектирование интегральных схем по заранеезаданным моделям и управление процессами изготовления фотошаблоновили непосредственно компонентовсхем, например методом электроннойлитографии 2.Отсутствие возможности выполнятьавтоматизированный синтез моделииз Фрагментов и Фиксации этой модели в структуре является недостаткомизвестной системы, приводящим к снижению ее эффективности, особенно прииспользовании в системе коллективного пользования.Цель изобретения - повышение эффективности и расширение функциональных воэможностей за счет осуществления режима формирования модели изфрагментов и Фиксации этой моделив структуре.Поставленная цель достигаетсятем, что в систему введены преобразователь кодов настройки цифровойструктуры, соединенный двухсторонней связью с центральным процессором и подключенный выходом к управляющему входу блока моделей и констант, и устройство синтеза моделей,первые вход и выход которого соединены с соответствующими выходом ивходом центрального процессора, второй вход устройства синтеза моделейсоединен с выходом блока моделейи констант, а второй выход подключенко входу преобразователя кодов настройки цифровой структуры.Кроме того, в системе устройствосинтеза моделей содержит блок управления, соединенный двухстороннимисвязями с блоками сравнения, хранения признаков, хранения мнемоническихзнаков, формирования дизъюнкции, формирования конъюнкции, оптимизациикомбинационных схем и с блоком памяти, который соединен двухстороннимисвязями с блоками Формирования дизъюнкции, Формирования конъюнкции,хранения мнемонических знаков и сблоком оптимизации комбинационныхсхем, выходы которого подключенысоответственно к первым входам блока Формирования дизъюнкции и блокаформирования конъюнкции, вторые входыкоторых подключены ко второму входуустройства, первый вход которого соединен с первыми входами блоков управления и памяти, первые входы которыхсоединены с первым выходом устройствавторой выход блока памяти соединенсо вторым выходом устройства, выходыблоков хранения признаков й хранениямнемонических знаков подключены ковходам блока сравнения,На фиг, 1 представлена схемасистемы; на фиг. 2 показай примерреализации устройства синтеза моде.лей.160 65 мнемонических знаков описания проектируемой схемы. Блок 14 предназначен для хранения набора кодовзнаков алфавита описания схемы. Блок13 сравнения осуществляет проверкусовпадений содержимого блока 12 и В состав схемы устройства входят:центральный процессор 1, блок 2 моделей .и констант, блок 3 логическогомоделирования, блок 4 проектированиятопологии, блок 5 анализа и моделирования схем, устройство б синтеза .моделей, преобразователь 7 кодов настройки цифровой структуры, устройство 8 ввода-вывода, терминальныеустройства 9.Устройство б синтеза моделей.состоит иэ блока 10 управления, блока 11 памяти, блока 12 хранения.мне-монических знаков, блока 13 сравнения, блока 14 хранения признаков,блока 15 Формирования конъюнкции,блока 16 формирования дизъюнкции, блока17 оптимизации комбинационных схем,цифрами 18 и 19 обозначены первыевход и выход устройства, цифрой20 - второй выход устройства и циф 20 рой 21 - второй вход устройства.Центральный процессор 1 управляет работой системы в,режиме разделения времени. Блок 2 моделей и констант предназначен для хранения описаний моделей и констант апробированных решений задач проектирования.Блок 3 проверяет работоспособностьспроектированных функциональныхсхем. Блок 4 проектирования топологиирешает задачи размещения элементовБИС, трассировки межсоединенийа также готовит управляющую информацию для терминальных устройств 9.Блок 5 осуществляет проверку работоспособности спроектированных системой схем и их топологических аналогов. Устройство б синтезирует логические, топологические и схемныемодели разрабатываемого узла ЭВМ.Преобразователь 7 вырабатывает4 О управляющие сигналы перестройки цифровой структуры блока 2 моделейи констант. Устройство 8 вводавывода обеспечивает обмен информациемежду центральным процессором 1 и4 терминальными устройствами с осуществлением параллельной работы переменного набора абонентского оборудования. Терминальные устройства9 предназначены для индивидуальнойработы разработчиков с системой. Всоставе любого иэ устройств 9 обязательно наличие исполнительного процессора,Блок 10 управляет работой устройства синтеза моделей. Блок 11 памяти предназначен для хранения задания на проектируемую схему храненияпромежуточных данных синтеза моделей. Блок 12 предназначен для оперативного хранения расшифровываемых5 805322 бО14 Блок 15 формирования конь-соответствующего разработчика. После блокаюнкции и блок 16 формирования дизь- этого центральный процессор, у юнкции фиксируют размерности конь- кает блок 4 проектирования топологии юнкции и дизъюнкции соответственно, передает ему исходные данные на прополучаемых в результате расшифровки ектирование топологии разрабатываемой описания проектируемой схемы, осу,БИС.ществляют анализ на наличие в блоке Одновременно с этим центральный 2 моделей и констант элементов, ре-. процессор 1 запускает блок 3 логиализующих тубуемые конъюнкции и ческого моделирования и передает ему диэъюнкции, а также синтез многовхо- иходные данные следующей по приориых конъюнкций и дизъюнкций из тету задачи проектирования.16В случае отсутствия в блок е 2 мо моделей и констант. Блок 17 дели какого-либо элемента проектиоптимизации комбинационных схем руемой схемы блок 3 логического мо-,ля синтеза схем делирования формирует сигнал запрон п о ессор 1. Послед- приемлемого порядка на имеющихся йли са центральному процессору . оследвозможных физических элементах. 35 ний запускает устройство б синтезаСистема работает следующимобра- моделей и передает ему всю иходнуюинформацию о проектируемой БИС.П мма содержащая в себе опирограмма, По исходным данным на проектируесание функционально схен й схемы БИС важ- мую БИС поступившим с центральногоВ Рм нных соотношений сис- Щ процессора 1, а также информации темы тестовых параметров, электричес- блоков 2,моделей и конста , у рк н таит ст ойких требований к отдельным узлам ство 6 синтезирует отсутствующие в и элементам, некоторых тых технологичес- блоке 2 логические, топологическиеб нностей и топологических и схемные модели. ких осо ено елей стограничени , данй данных о геометрических . По окончании синтеза м д у размерах кристаллсталла,а также указа- ройство б передает информацию ою 7. ния о наи олее специб фических схемно- новых моделях преобразователю конструкторских характерактеристиках БИС, Последний вырабатывает систему упв ля пе ест ойки может ыть рассб рассчитана как на осуще- равляющих сигналов для перестро киой ствление полного ц икла ироектирова- определенных массивов цифрово ние-изготовление, так и н а выполнение ЗО структуры блока 2, После Фиксации частичного цикла, чточто бывает необхо- синтезированных моделей в структуре димо для оперативного ввного выбора опти- блока 2 преобразователь 7 передает мальных вариантов итов проектируемой схемы. управление центральному процессоруцентральны й процессор 1 инициирует 1, который и момент освобожденияования командой операцию ввода, к . 3а ию ввода, которая З блока 3 логического моделир вс ио итетом, вососуществляет от обращение к устройству в соответствии с приоритетом, во -юз ач 8 ввода-вывода. оследнийП ний передает станавливает первоначальную ад у9 нфо мацию на проекти- и в соответствии с вновь синтезироиз устройств инфорос ествляет оконБИС в ентральный процессор ваннычи моделями осуще 1 использующий систему приоритетов 40 чательное логическое д рмо ели ование для определения последовательностист пивших задач. Затем При передаче центральным процеск 4 и оектиисходные данные задач проектирования сором 1 управления блоку ироекти- БИС транслируются в рабочие данные рования топологии последний запраблоков системы.45 шивает из центрального процессора 1По завершении этой операции цент- информацию, необходимую для проекй и о ессо 1 передает управля- тирования топологии (описание схекие азме ы кристалющ ю информацию и транслированные ис- мы, геометрические размеры ющую ин ормла казание технологии схемы). Расходные данные первой задачи в блок ла у3 логического моделирования. Послед- о шифровав и Ф рн о мацию, блок 4 отмений выбирает в блоке. 2 модели логи- чает в блокеблоке 2 моделей и константемые по описанию схемы тополок х элементов и составляет из них требуемые ост кты и с учетом схем- логическую модель, соответствующуюных и конструктивно-технологичес-, проектируемой схеме, после чего блокк х ог аничений, накладываемых осо существляет.моделирование, заклю- ких о ро55ект емых схем н чающееся в о рп еделении выходных сос- бенностями про ируской базой производсттояний элементов в зависимости от технологическо входных сигналов с учетом специаль- ва, осущ ествляет их размещение и ных требований временных соотноше- трассир уси овк межсоединеннй на кристалле заданных геометрических размеи и оектировании топологии,По окончании логического модели ров. При р рае необходимости, разработрования полученные результаты автома- в случае нео дчикимеет возможность корректиротически приводятся к.стандартному виалоговых средствя че. ез центральный вать ее с помощью диало/ ду и направляются черестав терминальных устст ойство 8 ввода-вы- входящих в сос процессор 1, устройств 9, добиваясь при этом оптивода на терминальное устройство 9 я ройств , домального размещения компонентов ч межсоединений на кристалле.Сигнал об окончании проектирования топологических слоев совме-. щенных фотошаблонов БИС передается из блока 4 в центральный процессор 1, который запускает блок 5 анализа и моделирования схем и передает ему исходные данные программы (,ограничения на основные функциональные параметры схемы: статическая помехоустойчивость, потребляемая мощ- . ность, времена задержек, нагрузочная способность, диапазоны питаю щих напряжений рабочих температур, специальные электрические требования, процент выхода годных, тип технологии).Блок 5 в соответствии с логической структурой БИС и реальным топо- логическим размещением ее элементов моделирует принципиальную электрическую схему без ее физической реализации, Анализ этой модели дает статические и динамические характеристики спроектированной БИС.Полученные в результате расчета функциональные характеристики БИС блок 5 сравнивает с характеристиками, требуемыми разработчиками в исходной программе. В случае неудовле творительных результатов сравнения блок 5 анализа и моделирования схем осуществляет детерминированную оптимизацию схемы, результатом которой является электрическая принципиальная схема БИС с скорректированными номиналами ее компонентов.По окончании детерминированной оптимизации блок 5 анализа и моделирования схем проводит расчет схемы с целью обеспечения требуемого выхода годных, Решение этой задачи осуществляется методом статистического моделирования. Если определенный процент выхода годных удовлетворяет требуемому, блок 5 передает управление на центральный процессор 1, .который в свою очередь выводит результаты работы блока 5 (графики выходных характеристик, таблицы качественных показателей, тестовые таблицы для оценок выхода годных и др). через устройство 8 ввода-вывода на терминальный комплект потребителя и передает управление блоку 4 проектирования топологии, В противном случае блок 5 анализа и моделирования схем осуществляет статистическую оптимизацию электрической принципиальной схемы БИС с целью получения такой совокупности оптимальных значений номиналов компонентов, которая обеспечила бы требуемый процент выхода годных схем.По сигналу управления, поступив- . шему из центрального пройессора 1, блок 4 проектирования топологии совместно с блоком 2 корректирует спроектированную топологию в соответствии с результатами работы блока 5анализа и моделирования схем, вносяизменения в модель топологии БИС.Работа системы повторяется с эта- .па проектирования топологииТакой итерационный цикл "проектирование топологии - анализ и моделирование электрических принципиальных схем" осуществляется до тех пор,пока не будет получена схема, удовлетворяющая разработчика по требуемым функциональным параметрам БИСи проценту выхода годных изделий.После получения положительных результатов центральный процессор 15 выдает сигналы блокам 4 и 5, по которым последние редактируют результаты проектирования топологиии электрической принципиальной схемы (совмещенный топологический чер- Я теж, чертежи шаблонов, описаниеэлектрической принципиальной схемы,режимы ее работы, характеристикии др.) к виду, требуемому ГОСТомна документацию. Одновременно блок4 проектирования топологии готовитуправляющую информацию на изготовление фотошаблонов БИС, после чегоцентральный процессор 1 выводит описание документации и управляющейинформации на изготовление комплекта фотошаблонов через устройство 8ввода-вывода на терминальные устройства 9.При построении устройства синтезамоделей были учтены некоторыеособенности, возникающие приавтоматизации проектирования больших интегральных схем, а именно; возможность изменений способа представления и хранения моде лей БИС; необходимость реализациив блоке синтеза моделей алгоритмасинтеза моделей БИС; потребность вспециальных средставх внесения изме-нений в представления моделей.45 Модель БИС появляется в связи снеобходимостью автоматизированногопроектирования и технологическогопроизводства БИС. Поскольку технологии совершенствуются,в них происходят изменения, приводящие к соответствующему изменению моделей.Пусть в некоторый момент проектировшик работает с моделями М ,М .., И, В предлагаемой системе представления этих моделей должны быть реализованы, При этом могут быть два способа реализации моделей. Первый заключается в хранении описаний всех конкретных моделей М 4 И, МК. Иными слова ми, в блоке 2 Моделей и константсистемы имеются К записей, приэтом каждой записи соответствуетописание определенной модели. Прииспользовании любой модели проекти ровщик обращается к соответствующет. После этого блок 10 управленияпосредством центрального процессора ф 1 проводит анализ в блоке 2 моделейи констант на наличие в его библиотеке элемента, реализующего логичесяую дизъюнкцию, размерность которой,полученная. на предццущих:этапах рабо-ты устройства б, зафиксирована в блоке 16 формирования дизъюнкции.Для этого.в блок Формирования дизъьнкции 1 б из блока 2 моделей и констант считываются все возможные ко эффициенты входа логических элементов ИЛИ и для диэъюнкции вычисляютсяпорядки реализуемой схемы. Если ка:- кое-либо значение.равно единице, тов блоке 2 моделей и констант имеется 45 логический элемент ИЛИ, необходимый му описанию, При другом способе представления моделей в системе хранятся некоторые заготовки (Фрагменты описаний) и алгоритм их компонов-. ки. При использовании моделей проектировщик должен описывать схему компоновки моделей иэ Фрагментов, затем запустить алгоритм синтеза, в резуЛьтате которого будет построе на соответствующая модель.По сигналу запуска, поступившему с центрального процессора 1, блок 10 управления переписывает в блок 11 памяти из массива описаний схемы в массив расшифрованных кодов код первого знака и придает ему признак логического отрицания. После этого по сигналам с блока 10 управления код второго знака из описания схемы считывается в блок 12.Считанный код сравнивается в блоке 13 сравнения с кодом скобки, откры вающей логическое выражение, поступившем с блока 14, Если коды совпадают, то в массив расшифрованных кодов заносится признак логической переменной. После эвого из описания схемы в блок 12 считывается код очередного знака описания и, в случае предыдущего знака "скобка", под действием сигналов с блока управления, с блока 14 хранения признаков в блок 13 сравнения подается код логического отрицания. Если коды в блоке 13 сравнения совпадают, блок 10 управ ления фиксирует в массиве расшифро- ванных кодов признак логического отрицания,. после чего работа устройства повторяется. Если в блоке 13 коды не совпадают, в массиве расшифрованных кодов фиксируется признак логической переменой. В случае фиксации логической переменной следующим шагом работы устройства является считывание из блока 11 памяти в блок 12 очередного знака описания и поочередный анализ его в блоке 13 сравнения на совпадение с признаками логического отрицания, логической дизъюнкции, скобки, закрывающей логическое выражение, признаком конца описания проектируемой схемы. Это анализ осуществляется под действием сигналов управления с блока управления, поступающих на блоки 12, 13, 14Если блок сравнения Фиксирует сов падение анализируемого знака с признаком отрицания, то блок управления фиксирует в блоке 11 памяти признак логического отрицания, переписываети ЙЗ т и схемы в массив расшифрованных кодов с признаком логической переменной я фиксирует в блоке 15 Формирования конъюнкции размерность полученной конъюнкции. После этого в блок 12 из блока 11 считывается очередной знак описания проектируемой схемы и осуществляется анализ, следую-,щий в случае фиксации логической переменной;При Фиксировании блоком 13 сравнения совпадения анализируемого знака с признаком логической дизъвнкцияблок управления Фиксирует в блоке 1 бформирования дизъюнкции размерностьполученной дизъюнкции, а также посредством центрального процессора 1осуществляет анализ в блоке 2 моде- Е лей и констант на наличие в его библиотеке элемента, реализующего логическую конъюнкцию, размерности, полученной на предыдущих этапах работыустройства б и зафиксированной и блоке 15 формирования конъюнкции. Дляэтого в блок Формирования конъвнкцйи15 из блока 2 моделей и констант считываются все возможные коэффициентывхода логических элементов И и длякаждой конъюнкции полученной размер ности вычисляется порядок реализуемойсхемы.Если какое-либо вычисленное значение равно единице, это свидетельствует о наличии в блоке 2 моделей Я и констант логического элемента И,позволяющего реализовать логическуюконъюнкцию требуемой размерности.Вычисленная информация Фиксируетсяв блоке 11. Работа устройства пов- ЗО торяется со считывания на анализочередного знака ойисания схемы.Если блок 13 сравнения фиксируетсовпадение анализируемого знака спризнаком скобки, закрывающей логическое Йыражение, то блок 10 управ.ления посредством центрального процессора 1 осуществляет анализ в блоке 2 моделей н констант на наличиев его библиотеке элемента, реализующего логическую конъюнкцию, размер ности, полученной на предыцущих эта:пах работы устройства б и зафиксированной в блоке 15 формирования коньюнкции. Для этого вычисляется и анализируется множество значений поряд ка реализуемой схемы для полученияконъюнкции, а вычисленная информация фиксируется в блоке 11.для реализации дизъюнкции требуемой размерности.Вычисленные значения, описывающие возможные варианты построения ИЛИ на несколько входов, фиксируются в блоке.11.5После этого блок управления запускает блок 17 оптимизации комбинационных схем. Блок 17 оптимизации комбинационных схем вычисляет перерасход аппаратуры при построении ком бинационной схемы из реальных элеменО тов И,ИЛИ,коэффициенты входа которых дали значения порядка схемы, равнйе единице. При многообразии таких пар схема строится из той пары, перерасход аппаратуры при которой ми нимальный. Информация, описывающая синтезированныи логический элемент, фиксируется в массиве расшифрованных кодов блока 11 памяти.Блок 17 определяет также минималь- О ную общую каскадность схемы, реализующей заданную дизъюнктивную нормальную форму (ДНФ) логической Функции при произвольном конечном количестве конъюнкций различных рангов, На следующем этапе работы блок 17 осу ществляет определение минимального количества логических элементов И и минимального количества логических элементов ИЛИ, необходимых для построения схемы, реализующей заданную ДНФ логической Функции. Вычисленные значения заносятся в таблицы решений блока 11 памяти. Последовательно просматривая эти таблицы решений, блок 17 по значению допустимого 535 порядка схемы определяет требуемые элементы И, ИЛИ. После этого блок 10 управления устанавливает блок 15 Формирования конъюнкции и блок 16 формирования дизъюнкции в исходное сос О тояние, считывает из блока 11 в блок 12 очередной знак и проводит его ана лиэ на совпадение с признаками логической диэъюнкции и конца логического выражения. Если код знака совпадает с признаком-дизъюнкции, блок 10 управления фиксирует в блоке 16 Формирования диэъюнкции размерность полученной дизъюнкции, считывает из описания схемы в блок 1250 .очередной знак и осуществляет анализ на совпадение этого знака с признаками логического отрицания и логической переменной, Работа устройства синтеза моделей повторяется.Если анализируемый знак совпадает с признаком конца описания проектируемой схемы, блок 10 управления передает знак конца синтеза модели логического выражения центральному процессору бОЕсли при анализе знака, следующего эа знаком логической переменной, его код не совпадает с признаками логического отрицания, логической диэЪюнкции, скобки, закрывающей.логическое выражение, признаком конца описанця проектируемой схемы, блок 10 управления Фиксирует этот код в массиве расшифрованных кодов с признаком логической переменной, Фи-. ксирует в блоке 15 формирования коньюнкции размерность полученной в результате анализа конъюнкции, считывает из описания схемы в блок 12, очередной анализируемый знак, и работа устройства синтеза моделей повторяется.Концом работы устройства 6 синтеза моделей присинтезе логических моделей является совпадение анализируемого знака с признаком койцаописания проектируемой схемы. В этом случае управление с устройства 6 синтеза моделей передается центральному процессору 1.ФФормула изобретения1. Система для автоматизированного проектирования и управлениятехнологическими процессами в микроэлектронике, содержащая центральный процессор, соединенный двухсторонними связями с блоками логического моделирования, проектированиятопологии, анализа и моделированиясхем, устройством ввода-вывода иблоком моделей и констант, которыйсоединен двухсторонними связямис блоками логического моделирования,проектирования топологии, анализа имоделирования схем, устройство вводавывода соединено двухсторонними связями с терминальными устройствами,о т л и ч а ю щ а я с я тем, что,сцелью повышения эффективности и расширения функциональных возможностейза счет осуществления режима Формирования модели из фрагментов и фиксации этой модели в структуре, в неевведены преобразователь кодов настройки, цифровой структуры, соединенный двухсторонней связью с центральным процессором и подключенныйвыходом к управляющему входу блокамоделей и констант, и устройствосинтеза модслей, первые вход и выход которого соединены с соответствующими выходом и входом центрального процессора, второй вход устройства синтеза моделей соединен свыходом блока моделей и константа второй выход подключен ко входупреобразователя кодов настройки цифровой структуры,2. Система по п. 1, о т л ич а ю щ а я С я тем, что Устройство синтеза моделей содержит блокуправления, соединенный двухсторонними связями с блоками сравнения,хранения признаков, хранения мнемонических знаков, формирования дизъюнкции, Формирования конъюнкции, опти805322 13 14 Заказ 10904 6 Подписное НИИПИ Тираж миэации комбинационных схем и с блоком памяти, который соединен двухсторонними связями с блоками формирования дизъюнкции,. формирования конъюнкции, хранение мнемонических знаков и с блоком оптимизации комбинационных схем, выходы которого подключены соответственно к первым ,входам блока формирования дизъюнкции и блока формирования конъюнкции, вторые входы которых подключены ко второму входу устройства, первый вход которого соединен с первыми входами блоков управления и памяти, первые входы которых соединены с первым выходом устройства, второй вьисодй.а. блока памяти соединен со вторым выходом устройства, выходы блоков хра нения признаков и хранения мнемонических знаков подключены ко входам блока сравнения. Источники инФормации, принятые во внимание при экспертизе1. Табарный В.Г. Автоматизированная система проектирования интеграль ных схем. Известия вузов СССР, сер. "Радиоэлектроника", т. ХУ 1, 1973.9 6.2 Авторское свидетельство СССР по заявке Р 1993565/18-24,кл. 6 06 Р 15/20, 1974. Филиал ППП Патент",г.ужгород,ул.Проектная,4

СмотретьЗаявка

2324152, 09.02.1976

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИАН УКРАИНСКОЙ CCP

ГЛУШКОВ ВИКТОР МИХАЙЛОВИЧ, ДЕРКАЧ ВИТАЛИЙ ПАВЛОВИЧ, ЗГУРОВЕЦ ЛЕОНИД ЯКОВЛЕВИЧ, ЗУБКО ЛЕОНИД МИХАЙЛОВИЧ, КАПИТОНОВА ЮЛИЯ ВЛАДИМИРОВНА, КИЯШКО ГАЛИНА ФЕДОРОВНА, РАКИТСКИЙ ВАЛЕРИЙ РОМАНОВИЧ

МПК / Метки

МПК: G05B 17/02

Метки: texho-логическими, автоматизированногопроектирования, микроэлектро-нике, процессами

Опубликовано: 15.02.1981

Код ссылки

<a href="https://patents.su/7-805322-sistema-dlya-avtomatizirovannogoproektirovaniya-i-upravleniya-texho-logicheskimi-processami-b-mikroehlektro-nike.html" target="_blank" rel="follow" title="База патентов СССР">Система для автоматизированногопроектирования и управления texho-логическими процессами b микроэлектро-нике</a>

Предыдущий патент: Устройство для обнаружения неисправ-ностей b блоках коммутации цифровыхинтегрирующих структур

Следующий патент: Устройство для обработки данныхи управления спектрофотометром

Случайный патент: Многодвигательный электропривод