Вычислительная система для решения дифференциальных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 771674

Автор: Фрадкин

Текст

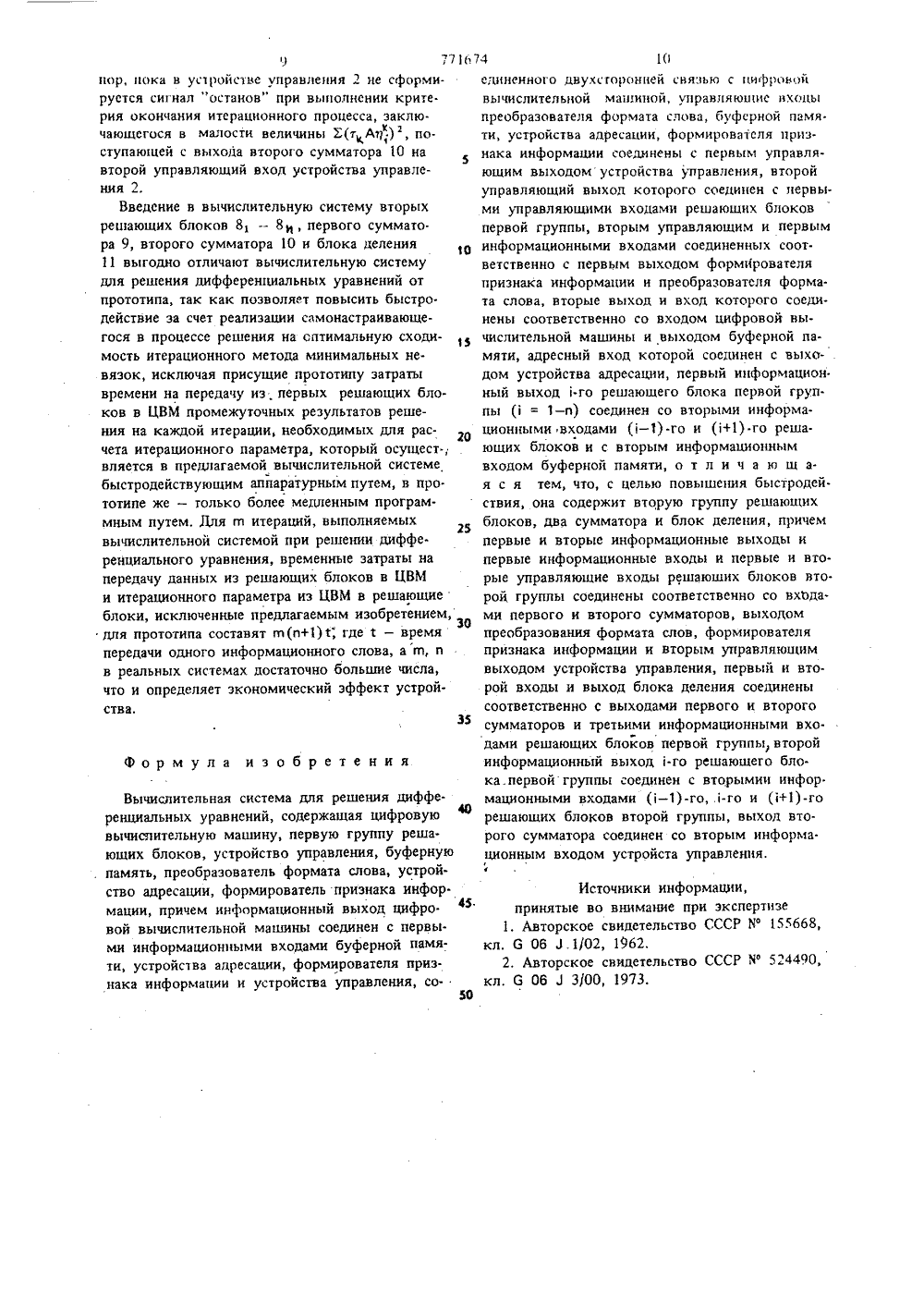

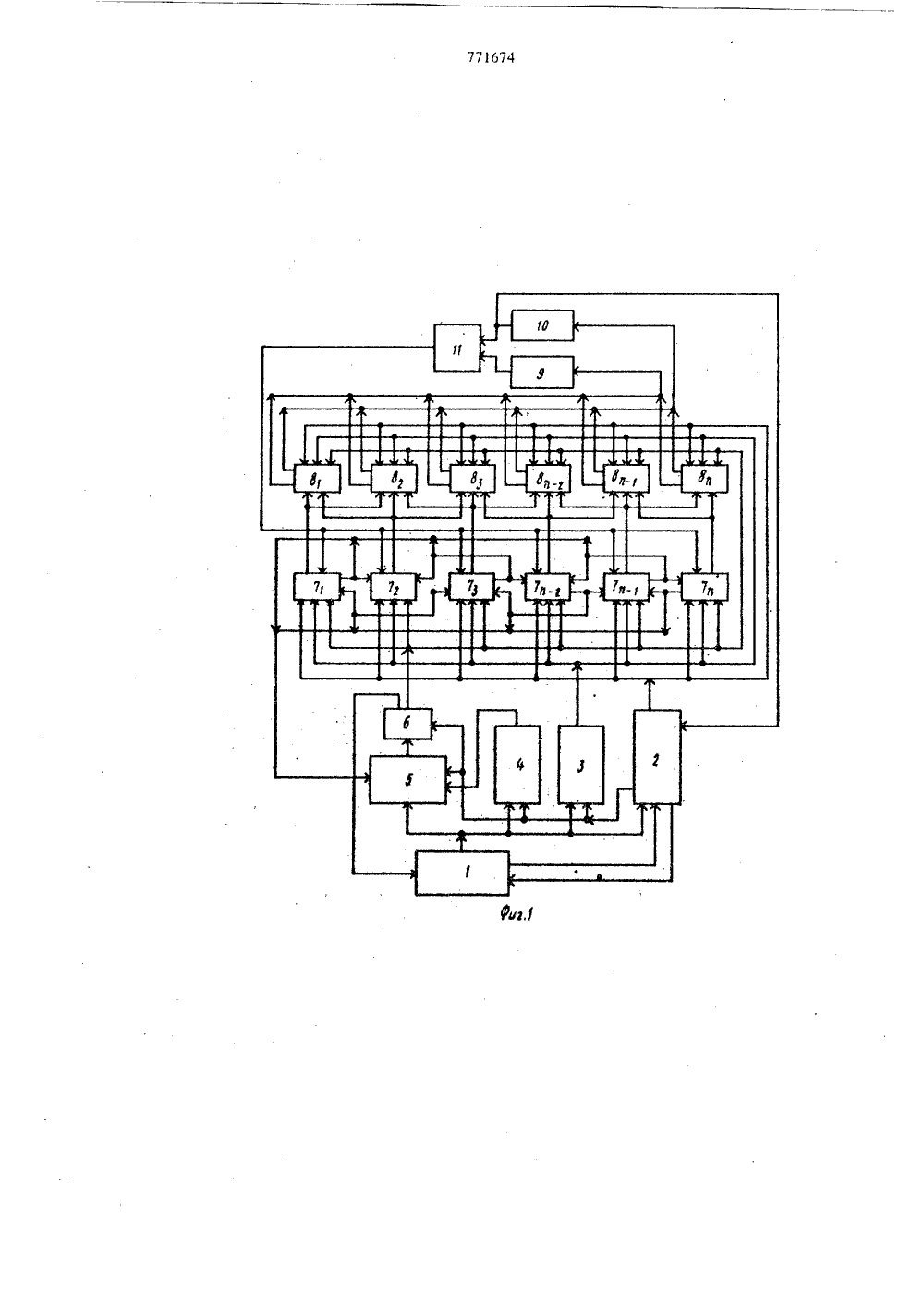

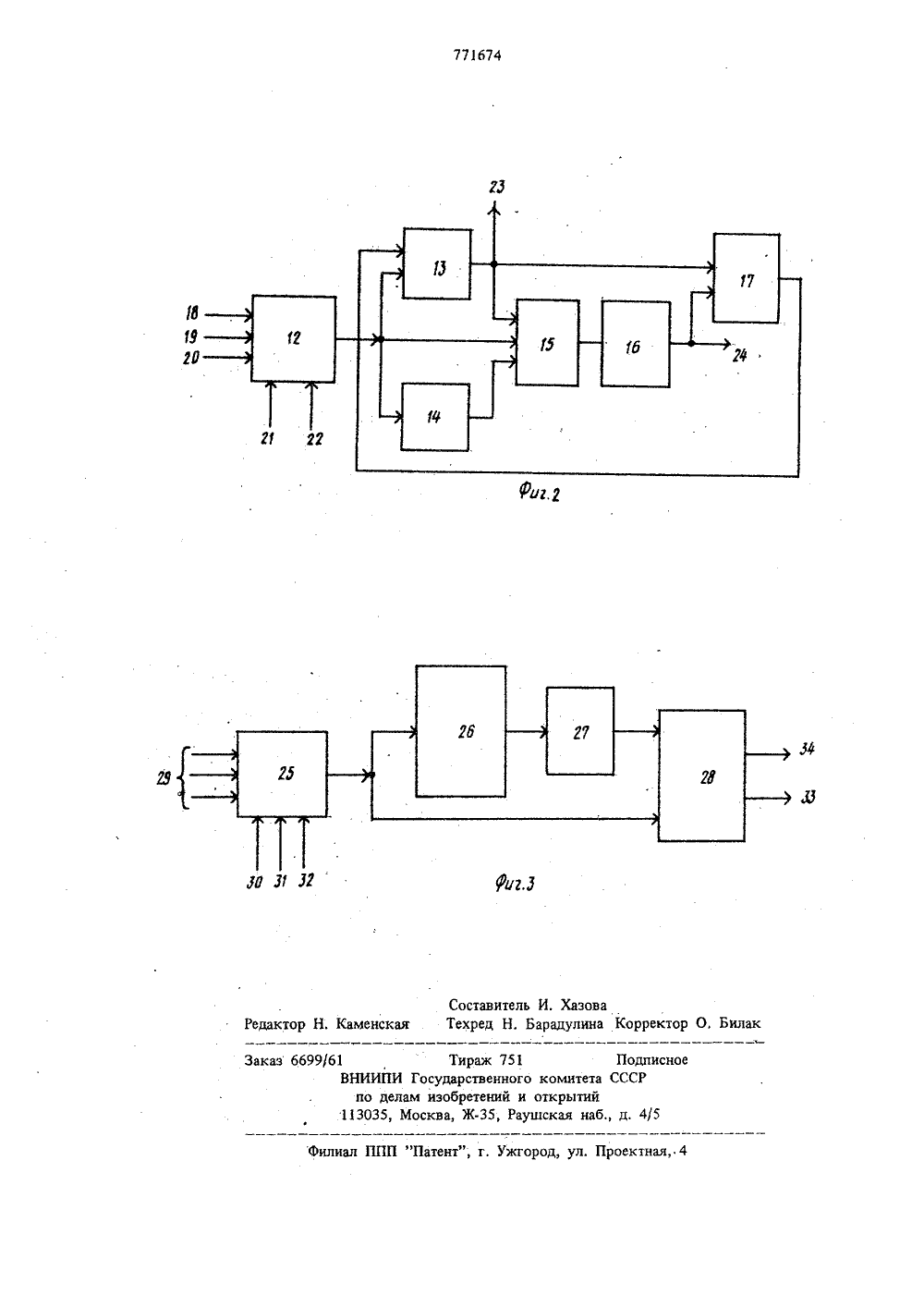

О П И С А Н И Е 1,771674ИЗОБРЕТЕН ИЯ Союз СоветскихСоцналисткческккРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(5 )М. Кл. с присоединением заявки Рй б 06 Р 15/32 Госудорстоонный комитет(28) Рриоритет по делам нзооротеннй н открытий(72) Автор изобретения Б. Г. Фрадкин Таганрогский радиотехнический институт им, В. Д. Калмыкова(71) Заявитель 54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ Йэобретение относится к области вычислитель. ной техники и может быть использовано при решении дифференциальных уравнений в частных производных.Известна комбинированная вычислительная машина, в состав которой входят два арифме 5 тйческих блока, соединенных общим оператив-. ным запоминающим устройством, причем один из блоков выполнен интегрирующим 11.Недостатком такого устройства является от.10 носительно невысокое быстродействие, обуслов. ленное тем, что оба вычислительных блока име. ют последовательную структуру.Из известных устройств наиболее близким по техническому решению является комбиниро 15 ванная вычислительная система 21, содержащая ЦВМ общего назначения, информационный выход которой через блок буферной памяти, первый преобразователь, блок коммутаторов со.единен со входами первых решающих блоков, подключенных информационными входами и выходами между собой, управляющими входами и выходами к устройству управления, информационными выходами через блокбуферной памяти и второй преобразователь - ко вхо. ду ЦВМ, информационный выход которой со. единен также со счетчиком адреса буферной йамяти, регистром адреса граничных решающих блоков, регистром признака инфбрмации и бло. ком местного управления, имеющего двухсто. роннюю связь с ЦВМ и устройством управления и подключенного выходом к управляющему входу регистра, признака информации, соединенного с дешифратором признака информации, подключенным ко входу блока коммутаторов, к управляющему входу регистра адреса граничных решающих блоков, соединенного с дешифратором адреса граничных решаюших блоков, подключенным к адресным входам решающих блоков, к управляющему входу счетчика адреса буферной памяти, соединенйому с дешифратором адреса буферной памяти, подключенным ко вхо. ду блока буферной памяти, к управляющему входу блока коммутаторов и к управляющему входу блока буферной памяти.Известное устройство предназначено для решения дифференциальнь 1 х уравнений в частных производных, представленных с помошью мето.4) 3 771 б 7дв сеток в виде системы конечно разностныхуравнений вида,ц,Ч,О Ч а,Ч =М, (1) которая в матричной записи имеет видА =9, (2) 5 где А - матрица коэффициентов с компонен. тами а1) у - вектор решений с компонентами угг у - вектор свободных членов с компо.нентами у,Решающйе блоки известного устройства реализуют решение (2) итерационным методом,1( К где г 1; - А+ чг невязка решения на к-ой 15 итерации,.;- итерационный параметр, В ка честве недостатка следует указать относительно невысокое быстродействие вычислительной си. стемы, имеющее место как для стационарных итерационных методов (т= сопят не зависит от к) за счет медленной сходимости итераций, так и для нестационарных, самонастраивающих. ся в процессе решения на оптимальную сходимость, итерационных методовв частности ме. тода минимальных невязок, при которомЕ УА 1 за счет затрат времени на передачу промежуточ- ЗОных результатов из решающих блоков в ЦВМдля расчета относительно медленным программным путем параметра т обеспечивающегооптимально быструю сходимость итерации. Указанный недостаток связан с отсутствием в из- З 5вестном устройстве блоков и связей, позволяющих осуществить в процессе решения ускорение сходимости итераций соответствующим вы.бором (4) итерационного параметра тбез су.щественного увеличения промежутка времени 40мелинду двумя соседними итерациями работы вычислительной системы,Целью изобретения является повышенйебыстродействия.Поставленная цель достигается тем, что в вы.числительную систему для решения дифферен.циальных уравнений, содержащую цифровую вы.числительную машину, первую группу решающих. блоков, устройство управления, буферную память, преобразователь формата слова, устройство адресации формирователь признака инфор.мации, причем информационный выход цифровой вычислительной машины соединен с первыми ийформационнымивходами буферной памяти,устройства адресации, формирователя признакаинформации и устройства управления, соединенного двухсторонней связью с цифровой вычис.лительной машиной; управлявшие входы преобразователя формата слова, буферной памяти,4 4 устройства адресации, формирователя признака информации соединены с первым управляющим выходом устройства управления, второй управ. ляющий выход которого соединен с первыми управляющими входами решающих блоков пер. вой группы, вторым управляющим и первым информационными входами соединенных соответственно с первым выходом формирователя признака информации и преобразователя форма. та слова, вторые выход и вход которого соеди. иены соответственно со входом цифровой вы числительной машины и выходом буферной па. мяти, адресный вход которой соединен с выхо. дом устройства адресации, первый информационный выход г-го решающего блока первой группы (1 = 1 - и) соединен со вторыми информа. ционными входами (г - 1).го и (1+1).го реша. ющих блоков и с вторым информационным входом буферной памяти, введены вторая груп. па решающих блоков, два сумматора и блок деления, причем первые и вторые информацион.Гные выходы и первые информационные входы и первые и вторые управляющие входы решающих блоков второй группы соединены соответственно со входами первого и второго сумматоров, выходом преобразователя формата слов, формирователя признака информации и вторым управляющим выходом устройства управления, первый и второй входы и выход блока деления соединены соответст. венно с выходами первого и второго сумматоров и третьими информационными входами решающих блоков первой группы; второй информационный выход г-го решающего блока первой груп. пы соединен со вторыми информационными входами (1-1) го, .го и (г+1)-го решающих блоков второй группы, выход второго сумматора соединен со вторым информационным входом устройства управления.Наличие в вычислительной систЕме вторых решающих блоков, первого и второго сумматоров, блока деления позволяет увеличить быст. родействие устройства (снизить время решения задачи) за счет настройки итерационного процес. са, реализуемого решающими блоками, на опти. малько быструю сходимость без передачи про. межуточных данных, необходимых для расчета т, из решающих блоков в ЦВМ и осуществле. ния расчета итерационного параметра т быстродействующим аппаратурным путем.На фиг. 1 показана структурная схема вычлс. лительной системы для решений дифференциальных уравнений; на фиг. 2 и фиг. 3 представлены схемы решающих блоков первой и.вто. рой групп.Система содержит цифровую вычислительную машину 1, соединенную информационным вы. ходом со входами, устройства управления 2, формирователя признака информации 3, устрой. ства адресации 4, с первым информационным5 77 входом буферной памяти 5, адресный вход ко. торой подключен к выходу устройства адресации 4, а управляющий вход, а также управля. юсцие входы преобразователя формата слова 6, устройства адресации 4 и формирователя признака информации 3 подключены к выходу уст. ройства управления , соединенного первыми управляющими входом и выходом с ЦВМ 1, вторыми управляющими входом и выходом - с первыми управляюшими входом и выходом устройства управления 2, подключенного вторым управляюшим выходом к первым управляющим входам решающих блоков 7, - 7 с, пер. вой группы и решающих бков 8, - 8 п второй группы, соединенных вторыми управляюшк. ми входами с выходом формирователя признака информации 3 и подключенных первыми (блоки 7, - 7 и и блоки 8, - 8 и) информа. ционными вхоцами,ко второму выходу преоб. разователя 6, соединенного первым выходом с ЦВМ 1, и информационным входом - с выходом буферной памяти 5. Решающие блоки 7, - 7 сс подключены между собой вторыми информационными входами и первыми информационными выходами, соединенными также со вторым информационным входом буферной памяти 5, Каждый с-ый решающий блок 8 соединен первыми информационными входами со вторым информационным выходом каждого -го и подключенных к 1-му решающих блоков 7, 7, 74, и подключен первым и вторым информационным выходом ко входу первого 9 и второго О сумматора, соединенного выходом со вторым управляющим входом устройства управления 2 и с первым входом блока деления 11, подключенного вторым входом к вы. ходу первого сумматора 9, а выходом - к третьим информационным входам первых решаюших блоков 7, - 7 и .оСтруктурная схема первого решающего блока 7 , (фиг. 2) содержит узел ввода 12, подключенный ко входам первого регистра 13, второго регистра 14, узла умножения 15, соединенного остальными входами с выходами первого 13 и второго 14 регистра, а выходомсо входом первого сумматора 16, подключенного выходом ко входу второго сумматора 17, соединенного другим входом и выходом с вы ходом и входом первого регистра 13, Входы 18 - 22 узла умножения являются в порядке перечисления первым, вторым, третьим информа. ционными и первым и вторым управляющим входами решающего блока 7 с Выход 23 пер. вого регистра 13 и выход 24 первого суммато. ра 16 являются соответственно первым и вто. рым информационным выходом решающего бло. ка 7.Структурная схема решавшего блока 8 (фиг. 3 с содержис узел ввода 25, подключен1674 6 Устройство управления 2 синхронизирует иуправляет работой всех блоков, осушсствля"юших связь между ЦВМ 1 к решасешими бло 30ками 7 с - 7 и, 8 с - 8 и . 5 10 15 20 25 ный ко входам первого 6 и врого ", уяа умножения, другой вход которого соединен с выходом сумматора 28, подключсниосо вхо;сом к выходу первого узла умножения 6. Входы 29-32 узда ввода 25 являются в порядке иере числения первыми и вторыми инфорл 1 ационыыми, первым к вторым управляюшкм входами рева. юшего блока 8, Выходы 33, 34 являются соответственно первым и вторым информацион. ным выходами решающего блока 8Буферная память 5 состоит из и регистров и предназначена для приема (выдачи) информации из (в) ЦВМ 1 последовательно по словам параллельно по разрядам и передачи информации в решающие блоки 7, - 7 с 8, - 8 и и из решаюших блоков 7, - 7 и параллел ко по сло вам последовательно по разрядам по сигналам устройства управления 2, причем выбор требуемого регистра осушествляется с полошьн устройства 4.Преобразователь 6 служит для преобраэова. ния формата информационного слова ЦВМ 1 в формат информационного слова решаюсцих блоков 7, - 7 и, 8, - , 8 и (и обратно) при передаче данных между ЦВМ 1 и решающими блоками. Решающий блок 7 предназначен для вычисления компоненты ук вектора решения у" накаждой к-ой итеращси работы вычислительнойсистемы,Решающий блок 8; предназначен для вычисления по величинам, пропорциональным невязКкам с 1 величин, пропорциональных величинамсАс 1(Атг ), входяшим в формулу (4) определения оптимального итерационного парамстра т.Блок деления 11 служит для выработкизначения оптимального итерационного параметра тк как частного от деления суммы, получа.емой на и-входовом сумматоре 9, на сумму,получаемую на п.вхоаоволс сумматоре 10.В процессе вьсчссслешгя решения у. синхро.сснизацию и.управление решающими блоками7, - 7 сс и 8, - 8 и осуществляет устройствоуправления 2, формирующее сигналы "пуск"и "останов".В решающем блоке 7 узел ввода 12 пред.назначен для ввода исходных данных передначалом решения в регистры 13, 14 (нулеваяоитерация у. и свободный член) и в узелумножения 15 (коэффициенты аразностссосоуравнения (1) с помощью формирователя 3признака информации, для подключения сосед.них решающих блоков 7 - 7; , для вво.: Первый регистр 13 служит для хранения ивыдачи на каждой итерации решения у . Второй регистр 14 предназначен для хранения ивыдачи свободного члсна р .Узел умножения 15 служит для вычисленияпроизведений решений у . на коэффициенты аи на значение итерационного параметра т.Первый сумматор 16 предназначен для выкчислениЯ величины тКЧ пУтем сУммиРованиЯпроизведений, получаемых в узле умножения15 /см. формулы (1), (3) /.Второй сумматор 17 служит для вычислен+ния решения у путем суммирования вели.чин уи тЧ, поступающих с выходов перк квого регистра 13 и первого сумматора 16/см, формулу (3)/.Во втором решающем блоке 8 узел ввода25 предназначен для ввода с помощью формирователя 3 признака информации в первыйузел умножения 26 коэффициентов а раэностного уравнения (1) до начала решения задачии подключения выходов 24 решающих блоков7(+, 7, 7, ко входам первого и второгоузлов умножения 26 и 27 в процессе решенияФзадачи,Первый узел умножения 26 служит для вы.числения произведений величин т, Ч., пропоркциональных невязке Ч на коэффициенты а.Сумматор 28 предназначен для вычислениявеличины т, АЧ путем суммирования полученкных в узле умножейия 26 произведений.Второй узел умножения 27 служит для по.лучения произведений на выходах 33, 34 про.порциональных соответственно величинамЧАЧ" и (АЧК) 2.Работа вычислительной системы для решениядифференциальных уравнений происходит следующим образом.Из ЦВМ 1 последовательно по словам и параллельно по разрядам при помощи устройства4 в и регистров блока буферной памяти 5 считывается информация, которая затем параллельно по словам и последовательно по разрядам,изменяя соответствующим образом свой фор.мат на преобразователе 6, поступает на первыеинформационные входы 18 решающих блоков7, - 7 и на вторые информационные входы30 решающих блоков 8, - 81, и в зависимое.ти от признака информации, поступающего изформирователя 3 на вторые управляющие входы 22, 32 решающих блоков 7, - 7, 8, - 8 изаписываетсяв регистры 13, 14 (уо, р з) и вузел умножения 15 (коэффициенты а 1 ) реша.ющих блоков 7, - 7 и и в первый узел умно.жения 26 (коэффициенты а) решающих бло-.ков 8, - 81. После занесения исходной информании в решающие блоки 7, - 7, 8, - 8 И устройство управления 2 формирует си 1 нал"пуск", поступающий по первым управляющимвходам 21, 31 в решающие блоки 7, 7 и,8,Яи, с ломощлю которых осуществляетсярешение дифференциального уравнения, пред.ставленного в виде (1) итерационным методом(3), (4). При этом на каждой к-ой итерацииработы устройства в первом решаюцюм блоке7 на входы узла умножения 15 поступают свыходов первого 13 и второго 14 регистроврешение у найденное на предыдущей итерации, и свободный член д, с выхода узла вво.да 12 значения у , у., поступающие с первых информационных выходов 23 соседних решающих блоков 7+, 7, подключенных ковторому информационному входу 19 данного ре.шающего блока 7, и значение оптимальногоитерационного. параметра т, поступающее с выхода блока деления 11. на третий информационный вход 20 данного решающего блока. В край-ние решающие блоки 7 7 и краевые условия уо,.уи поступают иэ буферной памяти 5 черезпреобразователь б на первый информационныйвход 18 соответствующего узла ввода 12. С выхода узла умножения 15 полученные произведе.к, к кния т,а;у 1 тра у+ тка у., тР поступают на,первый сумматор 16, где суммируются,образуя, согласно формулам (1), (3), величинуткЧ, постУпаюШУю на вход втоРого сУмматоРак17, на другой вход которого приходит значениеу.", с выхода первого регистра/13, ПолученнаякИсумма представляет собой решение у, найденное на к.ой итерации, и записывается в первыйрегистр 13. Значения т Ч",ткЧк ,ткЧ". со второго 35информационного выхода 24 решающих блоков7, 7., 7 поступают на первые информационные входы 29 решающего блока 8 и с выходаузла ввода 25 значения тЧ.", т Ч.", т Ч " пок + кступают на вход первого узла умножения 26,где умножаются на коэффициенты а,;, ааПолученные произведения суммируются на сумматоре 28, образуя согласно (1), (2) величинукт АЧ;, которая поступает на вход второго узлаумножения 27, на другой вход которого с вы.45хода узла ввода 25 приходит величина т Ч и.кВторой узел умножения 27 формирует на первом33 и втором 34 и информационных выходахвторого решающего блока 8 произведениятКЧ;АЧ 1-,(ткАЧ. ), которые с выходов всех2 к н К 2"50вторых решающих блоков 8, - 8 поступаютсоответственно на входы первого 9 и второго10 сумматоров вычислительной системы, с выхода которых получаемые суммы поступают навходы блока: деления, формирующего на выходе в сбответствии с формулой (4) значение оптимального итерационного параметра тк, най.денного на М-ой итерации; которое поступает затемв решающие блокЪ 7, - 7 и. Итерации работывычислительной системы продолжаются до тех9 7716 пор, пока в устройстве управления 2 не сформи. руется сигнал "останов" при выполнении крите. рия окончания итерационного процесса, заклю. чающегося в малости величины Х(т, АЧ"), по. ступающей с выхода второго сумматора 1 О на второй управляющий вход устройства управления 2.Введение в вычислительную систему вторых решающих блоков 8, - 8 и, первого суммато. ра 9, второго сумматора 10 и блока деления 11 выгодно отличают вычислительную систему для решения дифференциальных уравнений от прототипа, так как позволяет повысить быстро. действие эа счет реализации самонастраивающегося в процессе решения на оптимальную сходимость итерационного метода минимальных не. вязок, исключая присущие прототипу затраты времени на передачу из первых решающих блоков в ЦВМ промежуточных результатов решения на каждой итерации, необходимых для расчета итерационного параметра, который осущест, вляется в предлагаемой вычислительной системе быстродействующим аппаратурным путем, в про. тотипе же - только более медленным программным путем, Для гп итераций, выполняемых вычислительной системой при решении диффе ренциального уравнения, временные затраты на передачу данных из решающих блоков в ЦВМ и итерационного параметра из ЦВМ в решающие блоки, исключенные предлагаемым изобретением,30 для прототипа составят гп(п+1)т; где т - время передачи одного информационного слова, а гп, и в реальных системах достаточно большие числа, что и определяет экономический эффект устройства.Формула изобретенияВычислительная система для решения дифференциальных уравнений, содержащая цифровую40 вычислительную машину, первую группу решающих блоков, устройство управления, буферную память, преобразователь формата слова, устройство адресации, формирователь признака инфор. мации, причем информационный выход цифро.вой вычислительной машины соединен с первыми информационными входами буферной памя. ти, устройства адресации, формирователя приз.кака информации и устройства управления, со 50 10елинениого днухсгоронней связью с цифровой вычислительной машиной, управляющие входы преобразователя формата слова. буферной памя. ти, устройства адресации, формироваэеля приз. нака информации соединены с первьгм управляющим выходом устройства управления, второй управляющий выход которого соединен с первыми управляющими входами решающих блоков первой группы, вторым управляющим и первым информационными входами соединенных соот. ветственно с первым выходом формйрователя признака информации и преобразователя форма. та слова, вторые выход и вход которого соединены соответственно со входом цифровой вычислительной машины и выходом буферной памяти, адресный вход которой соединен с выходом устройства адресации, первый информацион. ный выход .го решающего блока первой груп пы ( = 1 - и) соединен со вторыми информа. ционными входами ( - 1)-го и (+1).го решающих блоков и с вторым информационным входом буферной памяти, о т л и ч а ю щ ая с я тем, что, с целью повышения быстродей. ствия, она содержит вторую группу решающих блоков, два сумматора и блок деления, причем первые и вторые информационные выходы и первые информационные входы и первые и вто. рые управляющие входы решаюших блоков вто. рой группы соединены соответственно со вх 1 эдами первого и второго сумматоров, выходом преобразования формата слов, формирователя признака информации и вторым управляющим выходом устройства управления, первый и второй входы и выход блока деления соединены соответственно с выходами первого и второго сумматоров и третьими информационными входами решающих блоков первой группы, второй информационный выход -го решающего блока.первой группы соединен с вторымии инфор. мационными входами ( - 1)-го,.-го и (1+1)-го решающих блоков второй группы, выход второго сумматора соединен со вторым информа. ционным входом устройста управления.ФИсточники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР Ко 155668,кл. 6 06,3.1/02, 1962.2. Авторское свидетельство СССР Хо 524490,кл. 6 06 .3 3/00, 1973., д ППП "Патент", г. Ужгород, ул. Проектная, 4 Фил Тираж 751 ПИ Государственного ком делам изобретений и откр 5, Москва, Ж, Раушская Подписноттета СССРтий

СмотретьЗаявка

2631467, 19.06.1978

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ФРАДКИН БОРИС ГИРШАВИЧ

МПК / Метки

МПК: G06F 17/13

Метки: вычислительная, дифференциальных, решения, уравнений

Опубликовано: 15.10.1980

Код ссылки

<a href="https://patents.su/7-771674-vychislitelnaya-sistema-dlya-resheniya-differencialnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система для решения дифференциальных уравнений</a>

Предыдущий патент: Устройство для классификации сигналов

Следующий патент: Цифро-вероятностное устройство для деления чисел

Случайный патент: Радиоактивный фантом