Параллельный матричный сумматорвычитатель

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

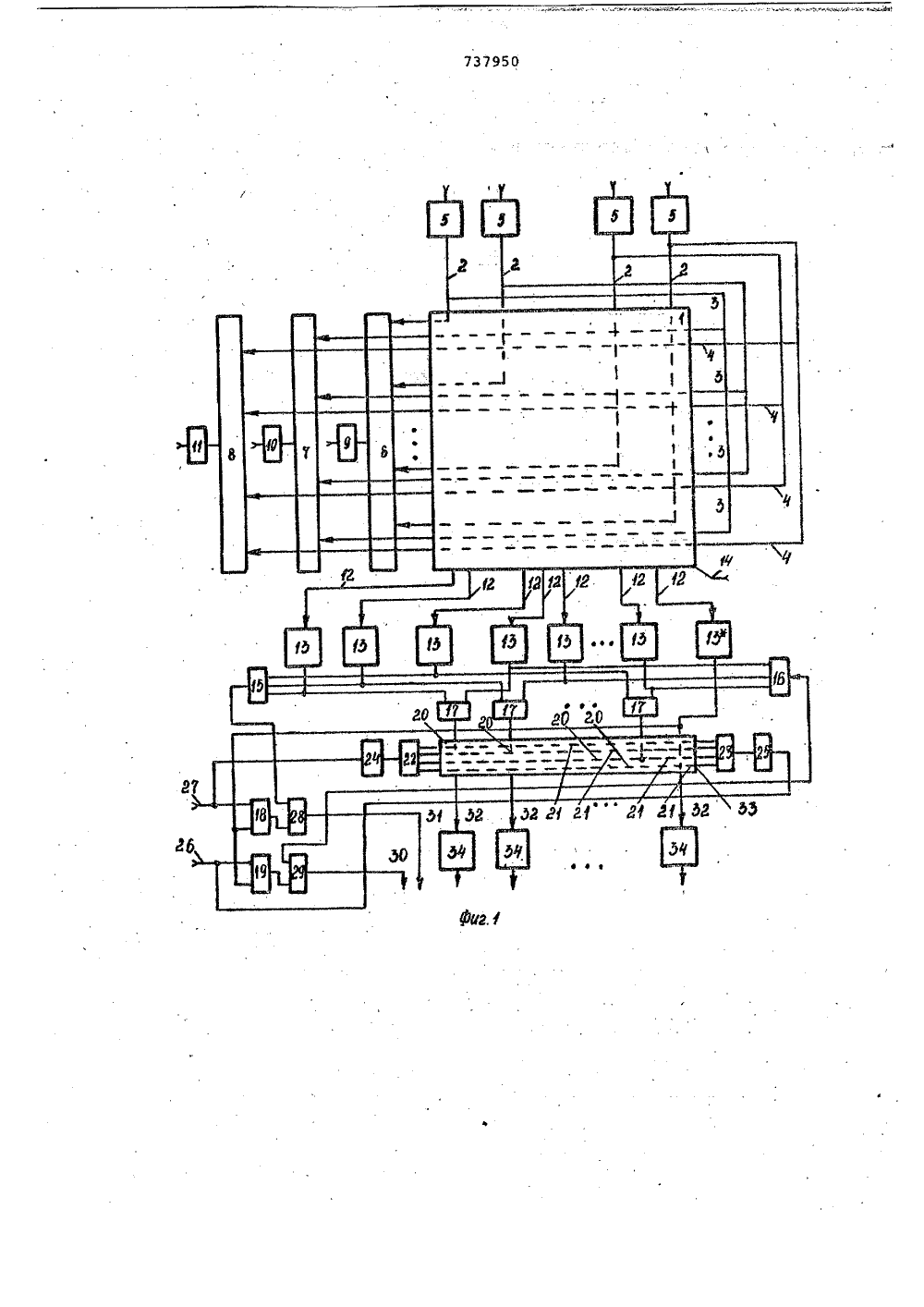

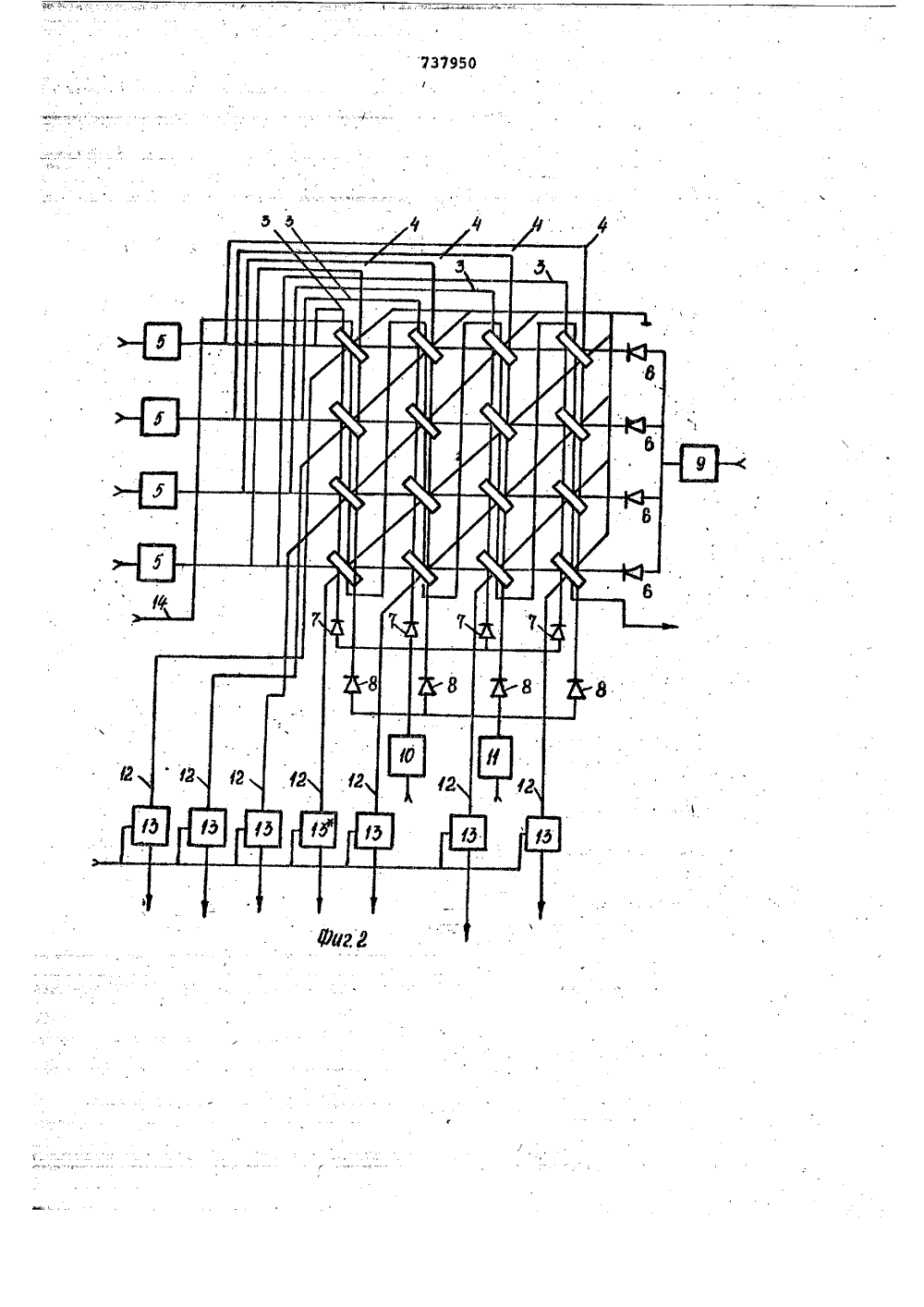

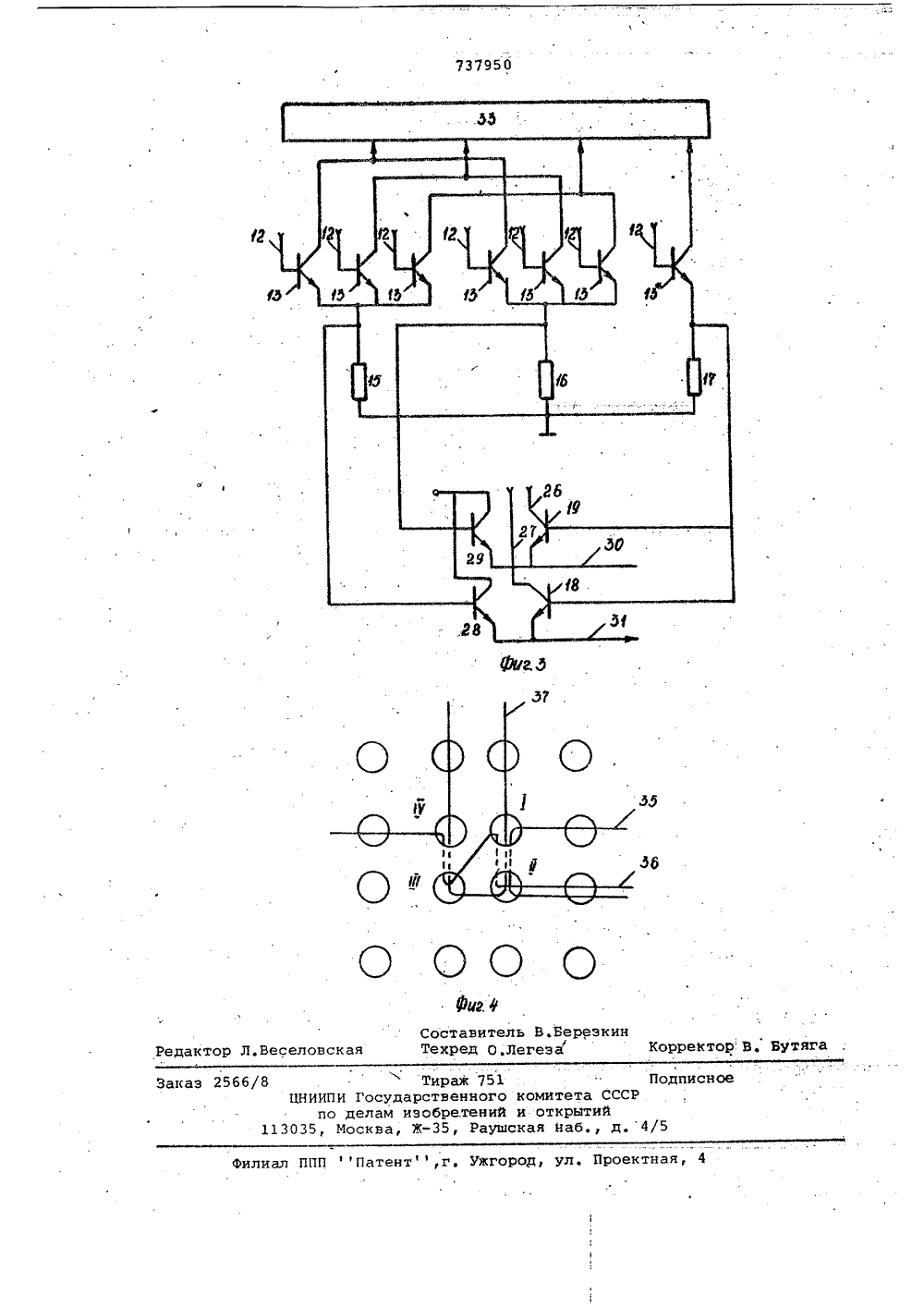

(71) Заявитель ни Московский о инженеПАРАЛЛЕЛЪНЫЙ ИЧНЫЙ СУММАТО ЕЛ 2Изобретение относится к вычисли-дый в-ный разряд, либо введением двух тельной технике и может быть исполь- . групп выходных обмоток, прошитых в зовано в специализированнйх ЦВМ, об- соответствии с таблйцами сложения и. ладающих повышенной надежностью,вычитания, что приводит к усложнению. быстродействием, помехоустойчивостью конструкции устройства. и устойчивостью к дестабилизирующим Наиболее близким к предлагаемому фак торам. является параллельный матричйыйИзвестны одно- и мяогоразрядные сумматор-вычитатель,содержащий матри, сумматоры-вычитатели для систем счисО цу ферритовых сердечников, координат- ,пения с основанием пт, использующие , ные обмотки, две груцпы выходных унитарйые коды 1 из в, и содержащие обмоток, формирователи координатных в каждом в-ном разряде матрицй сло- токов, усилители считывания, обмотки жения и вычитания, как правило, по- .переноса, усилители считывания обмостроенные на магнитных элементах; ток переноса, шины управления, обмотс НПГ, прошитых входными и выходными 1 ку восстановления и формирователь обмотками с использованием электрон- тока восстановления 4. ных ключей и усилителей-формировате- Недостатком данного устройства явлей 13, 21 и 33 . ляется сложность конструкции, аПодобные устройства действуют по именно, наличие двух групп выходных принципу совпадения двух полутоков, о обмоток, обмоток переноса, прошивачто приводит к уменьшению надежности ющих всю матрицу, и усилителей считыи снижению быстродействия из-завания обмоток переноса, а также низжестких требований к величинам полу" кая помехоустойчивость, обусловлен- токов и невозможности форсированного ная присутствием в схеме помех от переключения. Реализация операций полувыбранных в такте считывания сложения и вычитания в аналогичных сердечников, переключающихся но по- устройствах осуществляется либо вве- логой части петли гистерезиса, и дением двух матриц, реализующих взаимным влиянием" соседних элементаблицы сложения и вычитания на каж- тов матрицы друг на друга."ти ее изготовления.Цель достигается тем, что парал лельный матричный сумматор-вычитательсодержащий в какдом о 1-ном разРядематрицу магнитных элементов из материала с прямоугольной петлей гистерезиса в 1 в (где в-основание системысчисления для унитарного кода 1 изаИ, прошитую группами обмоток записипервого .и второго операндов, обмоткой восстановления и группами выходных обмоток поразрядной суммы, формирователи тока записи, диодные.сборки, подключенные к концам обмоток записи операндов, ключи разрешенйя зайиси, подключенные к соот-ветствующим диодным сборкам., содержит в каждом разряде вторую группуобмоток записи второго ойеранда,- усилителЬ считывания, элементы И и 20ИЛИ, щ-разрядный магнитный регистр,имеющий две группы обмотокзаписи,обмотКу считывания и выходные обмот:ки, дополйительныедиодные сборки"й"управлякхйие ключи, причем начало1-ой обмотки записи второго операндапервой групйы соединено с началом(в+1)-ой группы обмотки записивторого операнда второй группы (3.=1,2, , щ), концы обмоток записивторОго операнда второй группы подключены через первую дополнительнуюдиодную сборку к первому дополнительному ключу разрешения записи, первыеВходы первых (т) элементов ИЛИ подКлючены к выходам первого - (ю)- 35го усилителей считывания, входы кото рыхсоединенысоответственно с концами первой - (щ)-ой выяодных обмоток поразрядной суммы первой группы,а вторые входы - к выходам щ-го - 40(2 а)-го усилителей считывания,входы которых соединены соответственно с концами первой - (щ)-ойвыходных ошибок поразрядной суммывторой группы, входы в-го элементаИЛИсоединены с выходами первого -(щ)-го усилителей считывания, входы (в+1)-го элемента ИЛИ с выходамищ-го (2 а)-го усилителей считыванияр первые Входы первОгО и ВТОРОГО 50(2 М)-го усилителя считывания, входкото го соединен с концом в-ой выходи обмотки поразрядной суммыперв "группы,вторые входы первогои второго элементов И подключенысоответственно к шине переноса ийцТне отсутствия переноса из младшего разряда сумматора-вычитателя,входы (в+2)- го элемента ИЛИ подключенЫ к выходу ш- го элемента ИЛИ и к .выходу, первого элемента И, вход(а+3)-го элемента ИЛИ подключены квыходу (в+1)-го элемента ИЛИ и квыходу второго элемента И, выходы(а+2)-го и (а+3)-го элементов ИЛИ подключены соответственно к шинеотсутствия переноса и переноса встарший разряд сумматора-вычитателя,1-я обмотка записи первой и второйгруппы магнитного регистра (1=1щ) соединена с выходом 1-го элемента ИЛИ, а (в)-ая обмотка записипервой и второй группы магнитногорегистра - с выходом (2 щ)-го усилителя считывания, концы обмоток записи первой группымагнитного регистрасоединены со второй дополнительнойдиодной сборкой, а концы обмотокзаписи второй группы магнитного Регистра соединены с третьей дополнительной диодной сборкой, вторая итретья дополнительный диодные сборкичерез соответственно первый и второйуправляющйе ключи соединены соответственно с шиной переноса и шинойотсутствия переноса из младшего раз-.ряда сумматора-вычитателя,Матрица магнитных элементов выполненав виде многоотверстий ферритовой пластины с неравнормерным шагомрасположения отверстий по вертикалии по горизонтали.На фиг.1 представлена схема параллельного матричного сумматора-вычитателя; на фиг.2 - схема прошивки матрицы сумматора-вычитателя для кода 1 из 4, элементы матрицы условно показаны в виде тороидальных сердечников; на фиг.3 - схема выработки переноса на транзисторах дляодного разряда в коде 1 из 4; на фиг4 - один элемент матрицы и схемы анализа результата, выполненной на многоотверстнойферритовой пластине с неравномернымшагом расположения отверстий со всеми необходимыми прошивками.Параллельный матричный сумматорвычитатель содержит матрицу 1 магнит)ных элементов размером щхщ; прошитуюшинами 2 записи первого операнда,шинами 3, 4 записи второго операндавпрямом коде и обратном коде (фиг.1 и 2) . Начала всех шин подключенык общим Формирователям 5 тока записи,Концы всех. обмоток через соответствующие разделительные диодные сборки6, 7 и 8 подключены к ключам 9, 10и 11 разрешения подачи операндов.Имеются также выходные обмотки 12,присоединенные к усилителям-формирователям 13 и обмотки восстановления14, Выходы формирователей 13,соответствукщих значениям суммы О,в, подключены ко входамэлемента ИЛИ 15, а выходы Формирователей 13, соответствующих значениямсуммы в, , 2(в), подключены ковходам элемента ИЛИ 16, Кроме того,выходы данных формирователей подключены ко входам двухвходовых элементов ИЛИ 17, причем на входы )-гоэлемента ИЛИ 17 поданы выходы )-гои +щ)-го Формирователя 13 (=0,в) . Выход формирователя 13,тНа фиг.4 представлено расположе-.ние прошивок для одного элемента.Матрицыили регистра. В многоотвер-местйой ферритовой пластине с неравномерным шагом по вертикали и по горизонтали имеются группы отверстий по4 в каждой, причем расстояния междувцентрами соседних отверстий, принадлежащих одной группе, меньше расстоядсний между центрами соседних отверстий, принадлежащих раэным группам.Элемент, занимает одну группу отверс"Втий и содержит обмотку записи 35,обмотку считывания 36 и выходную щобмотку 37,Устройство работает следующимобразом.В первом такте происходит подачапервого операнда в коде 1 из в (на- Опример 1 из 4) на формирователи 5с одновременной подачей сигнала разрешения на ключ 9. При этом потечетток,записи по обмотке записи однойиз строк матрицы (фиг.2), пвреводя Ывсе сердечники данной строки в+В.(под словом 1 сердечникйподразумевается участок многоотвврстиой. пластины) .Во втором такте подается второй 0операнд нате же формирователи 5,но при этом открывается ключ 10,управляющий сложением, или ключ 11,управляющий вычитанием, в зависимости от выполняемой операции, При этом Я формула изобретения соответбтвующего значению суммя в(на фиг.1 помечен звездочкой) подключен ко вторый входам двухвходовых элементов И 18, 19. Кроме того выход данного формирователя 13 и выходы элементов И 17 подключены каж дый к соответствующей обмотке первой 20 и второй 21 групп обмоток записи магйитного регистра 33. Другие концы данных групп обмоток подключены через соответствующие диоды сборки 22 1 и 23 к ключам 24 и 25 разрешения записи результата с учетом переноса из младшего разряда и без его учета.Входы данных ключей подключены к шинам426 наличия и 27 отсутствия переноса из младшего разряда. Кроме того, шина 26 подключена к первоиу входу элемента И 19, а шина 27 - к первому входу элемента И 18. Выход элемента 18 подключен ко Второму О входу двухвходового элемента ИЛИ 28, а выход элемента 19 - ко второму входу двухвходового элемента 29 ИЛИ К первым входам элементов.28 и 29 подключены выходы соответствующих элементов 15 и 16 ИЛИ. Выход элемента5 29 подключен к шине 30 переноса, а выход элемента 28 - к шине 31 отсутствия. переноса в старшйй разряд. Выходные обмотки магнитного регистра 33 подключены к усилителям 34. потечет ток по одной из вертикальныхобмоток, переводя один из сердечниковвыбранной строки в фф-Вфф.На выходнйх обмотках матрицы появитсясигнал поразрядной суммы.На выходеэлемента 28, либо 29, появится сигнал, соответствующий наличию илиотсутствию переноса в стараий разряд.Результат операции будет записан вмагнитный регистр 33 либо без изменений, либо увеличенный на единицу(при наличии переноса из младшегоразряда) .В третьем такте происходит вос-становление матрицы подачей сигналапо шине 14 и считывание содержимогоМагнитного регистра 33 на усилители 34,1 акимобразом, осуществляетсясуммирование или вычитание двух кодовза три такта с возможностью форсированного переключения сердечника.На фиг.З показан вариант реализации элементов 15, 16, 17, 18, 19,28, 29. Элементы ИЛИ 15, 16 реализованы объединением эмиттеров соответствующих формирователей 13, элементыИЛИ 17 - путем объединения коллекторов соответствующих формирователей13, элементы И 18, 19 реализованы наодном транзисторе каждый, элементыИЛИ 28 и 29 также реализованы объединением эмиттеров соответствующихранзнсторов. При,такой схемной реаизации введение вышеуказанных элентов требует очень мало дополниельного оборудования (три транзисора для кода 1 нз 4),Введение вышеуказанных элементовновые связи, описанные выше, позоляют упростйть конструкцию. Ввеение магнитного регистра и новыевязи позволяют исключить из матрицытолбец элементов и обмотки, учитыающие перенос из младшего разряда.ведение двух групп обмоток дляподачи второго операнда и новые связипозволяют упростить прошивку выходных обмоток, сделав их общими длясуммы и разности.Упрощение конструкции приводит кповышению технологичности изготовления устройства.Принение многоотверстных пластинс неравномерным шагом расположенияотверстий позволяет уменьшить взаимное влияниемежду соседними элементамие 1. Параллельный матричный сумматор вычитатель, содержащий в каждом виом разряде матрицу магнитных элементов из материала с прямоугольной петлей гистерезиса вюп (где в - осно-. вание системы счисления для унитарного хода 1 из в), прошитую группамиобмоток записи первого и второго операндов, обмоткой восстановлении и группами выходных обмоток поразрядной суммы, формирователи тока записи, диодные сборки, подключенные к концам обмоток записи операндов, ключи разрешения записи, подключенные к соответствующим диодным сборкам, о т л ич.а ю.щ и й с я тем, что с целью упрощения конструкции и повьааения технологичности ее изготовления, сум р матор-вычитатель содержит в каждом разряде вторую группу обмоток записи. второго онеранда, усилитель считывания, элементы И и ИЛИ,в-разрядный магнитный регистр, имеющий две группы обмоток записи, обмотку считывания и выходные обмотки, дополнительные диодные сборки и управляющие ключи, причем начало 6-ой обмотки записи второго.операнда первой группы соединено с началом (щ+1)-ой 20 обмотки записи второго операнда второй группы (3.=1,2 в), концы обмоток записи второго операнда второй группы .подключены через первую дополнительную диодную сборку к первому дополни ,тельному ключу разрещения записи, первые входы первых (в) элементов ИЛИ подключены к выходам первого (щ)-го усилителей считывания,входы которых соединены соответственно ЗО с концами первой - (ж)-ой выходных обмоток поразрядной суммы первой группы, а вторые входы - к выходам Й-го - (2 в"2)-го усилителей считывания, входы которых соединены соответ- З 5 ственно с концами первой - (в)-.ой выходных ошибок поразрядной суюсь второй группы, входы щ-.го элемента ИЛИ соединены с выходами первого:., (щ)-го усилителей считывания,4 О входы (в+1)-го элемента ИЛИ - с выходами т го - (2 в)-го усилителей считывания, первые входы первого и второго элементов И соединены с выходом (2 в)-го усилителя считывания, вход которого соединен с концом п-ой выходной обмотки,поразрядной сум- мЫ первой группы, вторые входы первоГо и второгО элементов И подключенысоответственно к шине переноса н шинеотсутствия переноса из младшегоразряда сумматора-вычитателя, входы(в+2)-го элемента ИЛИ подключенык выходу ю-го элемента ИЛИ и к выходу первого элемента И, входы (ю+3)го элемента ИЛИ подключены к выходу(в+1)-го элемента ИЛИ и к выходу второго элемента И, выходы (в+2)-го и(в+3)-го элементов ИЛИ подключенысоответственно к шине отсутствия переноса и переноса в старший разрядсумматора-вычитателя,. 1-я обмотказаписи первой и второй группы магнйтного регистра (1=1,щ) соединенас выходом 1-го элемента И 31 И, а (в)ая обмотка записи первой и второйгруппы магнитного регистра - с выходом (2 ю)-го усилителя считывания,концы обмоток записи первой группымагнитного регистра соединены совторой дополнительной диодной сборкой, а концы обмоток записи второйгруппымагнитного регистра соединеныс третьей дополнительной диодной сборкой, вторая и третья дополнительныедиодные сборки через соответственнопервый и второй управляющие ключисоединены соответственно с шиной переноса и шиной отсутствия переноса измладшего разряда сумматора-вычитателя.2. Сумматор-вычитатель по п.1,о т л и ч а ю щ и й с я тем, чтоматРица магнитных элементов выполнена в виде многоотверстной ферритовойпластины с неравномерным шагом расположени отверстий по вертикали ипо горизонтали,Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРМ 434412, кл. О 06 Г 7/50, 1972.2. Патент США Р 3166669,кл,235-176,1965.3Патент США 93105144,кл.235-176,19634. Патент США 9306 9086,кл.235-176,1962 (прототип),.Веселовская К Тираж 751 Государственного ком елам изобретений и о сква, Ж, Раушская б/8 Зака писное лиал ППП Патент ,г, Ужгород, ул. Проектная,ЦНИИПИ по 113035, МО ета СССР рытийаб д. 4

СмотретьЗаявка

2540076, 03.11.1977

МОСКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНЖЕНЕРНО ФИЗИЧЕСКИЙ ИНСТИТУТ

ПОПОВ ЮРИЙ АЛЕКСЕЕВИЧ, ИЛЬИН ВИКТОР АЛЕКСАНДРОВИЧ, ЕСИПОВ ВЛАДИМИР ВЯЧЕСЛАВОВИЧ, СКВОРЦОВ СЕРГЕЙ ИВАНОВИЧ, ЗАДЕРЕЙ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: матричный, параллельный, сумматорвычитатель

Опубликовано: 30.05.1980

Код ссылки

<a href="https://patents.su/7-737950-parallelnyjj-matrichnyjj-summatorvychitatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельный матричный сумматорвычитатель</a>

Предыдущий патент: Устройство для извлечения корня третьей степени

Следующий патент: Устройство для формирования импульсных последовательностей

Случайный патент: Авторучка