Устройство для управления вводом изображения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

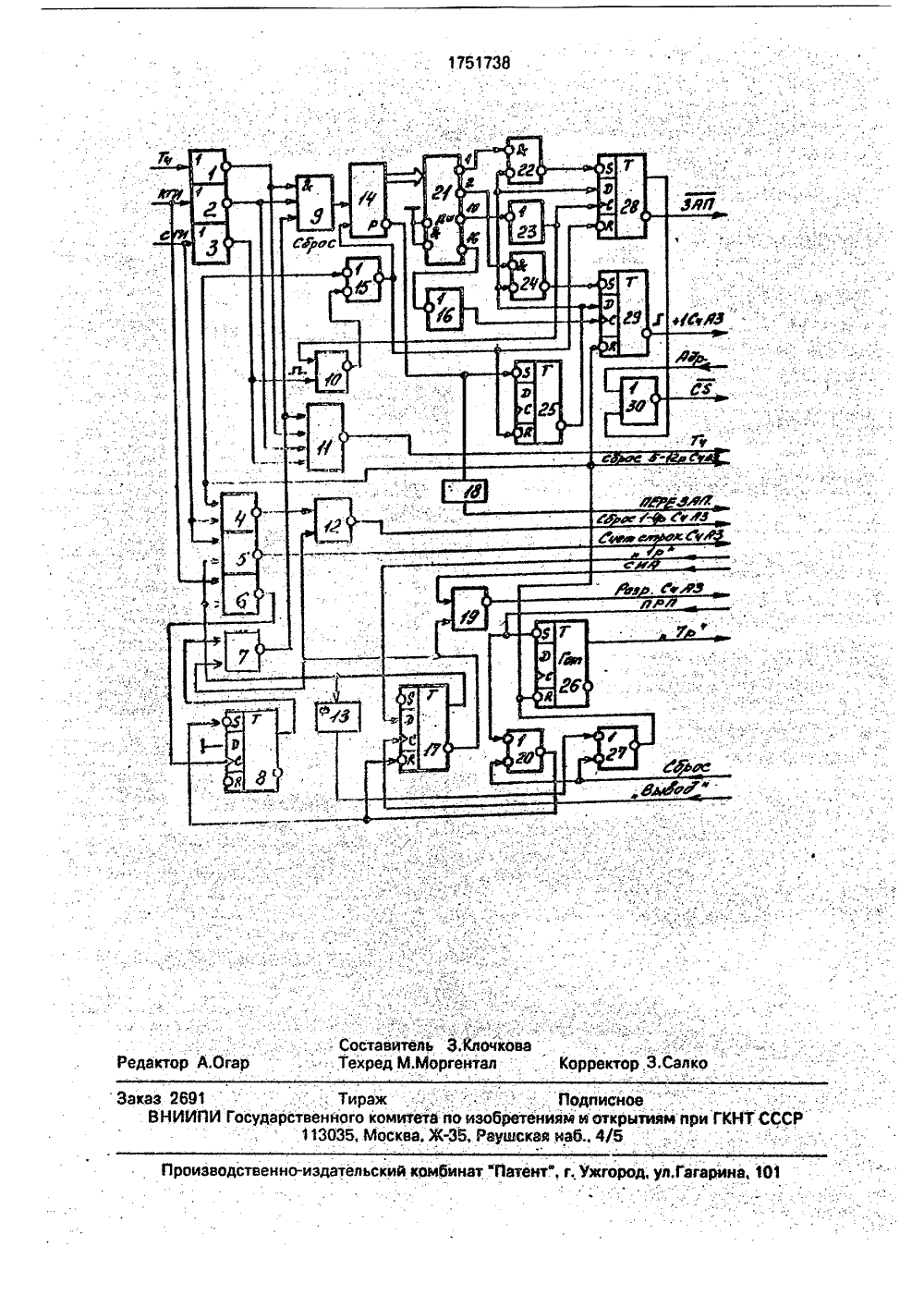

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРеспуБлик 1751738 5 606 ЕЗ/О ИЗОБРТЕЛЬСТВУ ЕН ОПИСА АВТОРСКОМ Н 2(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВВОДОМ ИЗОБРАЖЕНИЯ(57) Изобретение относится к автоматике и ги-вычислительной технике. и предназначенодля использования в устройствах считывания изобретения. Цель изобретения - . повышение помехозащищенности устройства, За счет введения дешифратора; триг.геров и элементов И, И-НЕ,НЕ, ИЛИ-НЕ.ИЛИ появилэсь возможность работы устройства с различными тактовыми" частотами и устранились сбои при записи информации в буферную память, 1 ил.;. Изобретение относится к вычислительной технике и может быть использовано всистемах технического зрения для управле-ния вводом видеоинформации в ЭВМ,Известен блок управления в устройстведля вводаизображения в электройнуювычислительную машину, содержащийблок управления сканированием, интенсив- .ностью и апертурой электронного луча;Формирователи сигналов, управляющихперестройкой апертуры, блок управлениярежимом перестройки апертуры, включающийсхему сравнения и два ключа, формирователь управляющих сигналов, два регулируемых источника тока и двухпозиционныйпереключатель,Недостатки этого устройства - сложно-.сть, невысокая надежность зэ счет низкойпомехозащищенности и возможности сбоевв работе при преобразовании аналоговогосигнала в дискретный код и записи в оперативную память.Известен также блок управления в устройстве для сопряжения цифровой вычислительной машины с устройством вводаиэображений, содержащий два входных реОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТПРИ ГКНТ СССР гистра, блок дешифрации. команд, выполненный нэ программируемой логической матрице, буферную память микрокоманд, выходной регистр, регистр управления, регистрц текущего адреса иследующего адреса, узлы управления"обменом и блок распределения синхроимпульсов,Данное устройство характеризуется сложностью., низкой помехозащищенноСтью, ограниченными "функциональными возможностями.Наиболее близким к: предлагаемому техническим решением является блок управления с формирователем импульсов в устройстве для ввода изображения в ЗВМ, содержащий счетчик бит, три элемента НЕ, четыре элемента И-НЕ, четыре элемента ИЛИ - НЕ, три триггера, формирователь импульсов, включающий узел задержки. ждущий мультивибратор, усилитель, триггер, элемент ИЛИ - НЕ, два формирователя фронта, причем вход узла задержки является входом запуска формирователя, а выход является первым выходом формирователя и подключена к входу ждущего мультивибраторэ, выход которого соединен с входомвыход переполнения которого соединен свходом элемента задержки, выход которогоявляется выходом строба перезаписи устройства, причем первый вход пятого элемента И-НЕ является входом сигнала"Синхронизация активного устройства", С- входы второго триггера являются соответственно входами сигналов "Первый разряд" и "Вывод", а инверсный выход второго триг гера соединен с вторым входом пятого элемента И-НЕ, первым входом третьего элемента ИЛИ-НЕ и первым входом второго элемента ИЛИ-НЕ, второй вход и выход которого соединен соответственно с выходом первого триггера и с первым входомчетвертого элеМента И - НЕ, выход которого является вь 1 ходом тактовой частоты а второй, третий и четвертый входы четвертого элемента И - НЕ соединены соответственно с выходами первого, второго и третьего злемента НЕ, вход которого является входом для подключения сигнала гашения вини телекамеры и соединен с первыми входами первого элемента ИЛИ-НЕ и первого элемента И-НЕ, выход которого является выходом сигнала "Счет строк", а второй вход 354050 усилителя, первого формирователя фронта фи синхровходов трйггера, установочныйвход которого соединен с единичным выходом триггера и четвертым выходом формирователя, выход усилителя является вторйм 5выходом формирователя, выход первого. Формирователя фронта соединен с первымвходом элемента ИЛИ - НЕ, второй вход ко-.торого являетСя разрешающим входом формирователя, а выход является третьим 10выходом формирователя,Недостатками известного устройстваявляются сложность, невысокая надеж-ность из-за низкой помехозащищенности,обусловленной возможными сбоями в работе устройства, и ограниченные функциональные возможности. Сбои в работеустройства мьгут возйикнуть при разбросе.параметров ЯС-цепей, на базе которых организованы сйгналы записи информации, 20выборки, смены адреса. Устройство такжедает сбои в работе, если-увеличиваетсятактовая частота от телекамеры, например 10 мГц вместо 5,Цель изобретения - повышение помехозащищенности.Поставленная цель достигаетсятем, чтоустройство, содержащее первый, второй,"третий элементы НЕ, первый, второй, чет-вертый и пятый элементы И-НЕ, йервый, 30второй и третий элементы ИЛИ-НЕ, второй и третий элементы ИЛИ, первый, второй,третий. и четвертый триггеры, формирователь импульсов, элемент задержки, счетчйк,первого элемейта И-НЕ соединен с выхо- . дом второго триггера, входом формирователя импульсов, первым входом второго элемента И-НЕ, второй вход которого соединен с входом второго элемента НЕ и яв-: ляется входом для подкл очения сигналов кадровых импульсов шины телекамеры, а выход второго. элемента И-НЕ соединен с С-входом первого триггера, О-вход которого соединен с "Общим", а 8-вход - с В-входом второго триггера и выходом второго элемента ИЛИ, первый вход которого соединен с 3-входом четвертого триггера и является входом сигнала "Переполнение счетчика ад-реса", а второй вход второго элемента ИЛИ соединен с первым входом третьего элемента ИЛИ и является входом "Сброс", выход четвертого триггера является выходом Сиг- .нала "Седьмой разряд", вход первого эле- мента НЕ является входом для подключения сигналов тактовой частоты. шины телекамеры, выходпервого элемента ИЛИ-НЕ сое-динен с вторым входом третьего элемента ИЛИ-НЕ, выход которого является выходом сигнала "Сброс 1-4 разрядов счетчика адреса", выход формирователя соединен с вторым входом третьего элемента ИЛИ, выход которого соедийен с Я-входом четвертого триггера, вторым входом первого элемента ИЛИ-НЕ и является выходом сигнала "Сброс 5-12 разрядов счетчика адреса", выход пятого элемента И-НЕ является выходом сигнала "Разрешение на счетчик адреса", в него введены четвертый и пятый элементы НЕ, третий элемент И-НЕ, второй и третий элементы И, первый элемент ИЛИ, четвертый элемент ИЛИ-НЕ; пятый и шестой триггеры, дешифратор, первый элемент И, первый, второй. третий входы и выходкоторого соединены соответственно с выходом первого элемента НЕ, выходом второго элемента НЕ, выходом второго элемента ИЛИ-НЕ и счетным входом счетчика, выход переполнения и группа информационных выходов счетчика соединены соответственно с 3-входом третьего триггера и группой информационных входов дешифратора, управляющие входы которого соединены с. "Общим", а выходы первого, второго, десятого и шестнадцатого импульсов соединены соответственно с первым входом второго элемента И. первым входом третьего элемента И, входом пятого элемента НЕ и входом четвертого элемента НЕ, выход которого соединен с С-входом шестого триггера, О-вход которого соединен с инверсным выходом третьего триггера, вторым входом третьего элемента И, О-входом пятого триггера и вторым входом второго элемента И, выход которого соединен сЯ-входом пятого триггера, С-вход которогоПредлагаемое устройство работает в сосоединен с выходом пятого элемента НЕ и ставе известного устройства ввода изобрапервым входом третьего элемента И - НЕ, жения в ЗВМ, в которое входят известные второй вход и выход которого соединены блоки - регистр сдвига, регистр приема, соответственно с выходом третьего злемен блок буферной памяти, счетчик адреса, блок та НЕ и с первым входом первого элемента канальных приемопередатчиков, блок связи ИЛИ, второй вход которого соединен с вы- с ЭВМ. Устройство предназначено для уп ходом третьего элемента ИЛИ, а выход пер- равления указанными блоками в режимах вога элемента ИЛИ соединен с В-входом записи иэображения в блок буферной памятретьего триггера, входом сброса счетчика, 10 ти и считывания его йз блока буферной пай-входом пятого триггера, выход которого мяти в ЭВМ для обработки.соединен с первым входом четвертого зле- В устройстве с первого по третий элемента ИЛИ - НЕ, второй вход и выход кото- менты НЕ 1-3, первый элемент ИЛИ - НЕ 4, рого являются соответственно входом первый 5 и второй 6 элементы И-НЕ, второй сигнала "Адрес" и выходом сигнала "Вы элемент ИЛИ - НЕ 7, первый триггер 8, пер, борка"Я-вход шестого триггера соединен вый элемент 9 И, третий 10 и четвертый 11 с выходом третьего элемента И, а йнверс- элементы И - НЕ, третий элемент ИЛИ-НЕ ные выходы пятого и шестого триггеровяв, формирователь 13, счетчик 14 бит, перляются соответственно выходом сигнала вый элемент ИЛИ 15, четвертый элемент НЕ "Запись в буферное запоминающее устрой-. 20 16, второй триггер 17, элемент 18 задержки, ство" и выходом сигнала "Прибавление еди- пятйй элемент И - НЕ 19, второй элемент ницы всчетчик адреса". ИЛИ 20, четвертый триггер 26 и третий злеСущественными отличиями устройства мент ИЛИ 27 образуют узел управления, являются наличие дешифратора, пятого и. предназначенный для управления приемом шестого триггеров, первого элемента ИЛИ, 25 одногокадрателевизйонногоизображения, третьего элемента И - НЕ, первого, второго Элементы выполнены на микросхемах сеи третьего элементов И, четвертого и пятого рии 155, в частности эпементы 15, 20, 27, 22 элементов НЕ, четвертого элемента ИЛИ - и 24 выполнены на микросхеме К 155 ЛИ 1, НЕ, а также связей этих элементов между К 155 ЛЛ 1, Получив команду от ЭВМ на ввод собой и с известными блоками и элемента изображения (сигнал "Первый разряд" на ми, что позволяет организовать сигналы "О"-вход второго триггера 17), узел управлезаписи, выборки, смены адресов во времен- ния по началу следующего кадра выдает ном цикле записи информации в,блок бу-разрешение на ввод изображения в блок ферной памяти, причем для формирования буферной памяти, открывает четвертый элесигналов записи, выборки, смены адреса 35 ментИ-,НЕ 11, а по окончании ввода выиспользуются импульсы тактовой частоты, ставляет сигнал готовности в Э ВМ с выхода получаемой с выхода телекамеры, что дает триггера 26 по 7 разряду шины данных возможность исключить сбои в работе уст- ЗВУ.ройства, а также позволяет работать с теле- . Дешифратор 21, счетчик 14 бит, четвер- камерами, имеющими различные тактовые 40 тый элемент НЕ 16, второй элемент И 22, частоты, . пятый элемент НЕ 23, третий элемент И 24,третий 25, пятый 28 и шестой 29 триггеры,На чертеже приведена структурная схе- четвертый элемент ИЛИ - НЕ 30 и связи межма устройства, ду ними образуют формирователь цикла за.- Устройство содержит первый 1, второй 45 писи, выборки, смены адреса в циклах 2 и третий 3 элементы НЕ, первый элемент записи 16-разрядных слов в блок буферной ИЛИ - НЕ 4, первый 5 и второй 6 элементы . памяти, При этом в формировании сигналов И - НЕ, второй элемент ИЛИ - НЕ 7, первый записи "ЗАП" и выборки "СЯ" для блока триггер 8, первый элемент И 9, третий 10 и буферной памяти участвуют четвертый элечетвертый 11 элементы И - НЕ, третий эле мент ИЛИ - НЕ 30, третий 25 и пятый 28 мент ИЛИ НЕ 12, формирователь 13 импуль- триггеры, второй элемент И 22, пятый элесов, счетчик 14, первый элемент ИЛИ 15, мент НЕ 23, дешифратор 21 выходы 1-го и четвертый элемент НЕ 16, второй триггер 10-го импульсов), счетчик 14 бит, первый 17, элемент 18 задержки, пятый элемент элемент И 9, третий элемент И-НЕ 10, пер- И-НЕ 19, второй элемент ИЛИ 20, дешиф вый элемент ИЛИ 15; а при формировании ратор 21, второй элемент И 22, пятый эле-сигнала смены адреса "+1 Сч АЗ" для счетчимент НЕ 23, третий элемент И 24, третий 25 ка адреса участвуют третий 25 и шестой 29 и четвертый 26 триггеры, третий элемент триггеры, третий элемент И 24, четвертый ИЛИ 27, пятый 28 и шестой 29 триггеры элемент НЕ 16,дешифратор 21(выходы вточетвертый элемент ИЛИ - НЕ 30. рого и шестнадцатого импульсов), счетчик1751738 10 20 блока буферной памяти в ЗВМ, передачи "Тч 14 бит, первый элемент И 9, третий элемент И - НЕ 10, первый элемент ИЛИ 16, импульсы с выхода дешифратора 21 синхронизированы импульсами тактовой частоты "Тч",поступающей с выхода телекамеры на счетный вход счетчика 14 бит через первый элемент НЕ 1 и первый элемент И 9,Счетчик бит предназначен дл я подсчетав блоке числа бит информации, поступающей на вход регистра сдвига ввиде видеосигнала, для выдачи при переполнении счетчика 4 бит сигнала перезаписи 16-разрядного слова из регистра сдвига в регистр приема, для формирования двоичных кодов на информационных выходах счетчика 14 15 бит и на входах дешифратора 21 по мере заполнения счетчика 14 бит тактовой частотой. Регистр сдвига - это регистр последовательно-параллельного действия,предназначенного для преобразования видеосигнала, поступающето на информационный вход регистра сдвига, в параллельный 16-разрядный код при подаче на вход синхронизации регистра сдвига 16 импульсовтактовой частотьь Регистр приема предназйачен"дляприема информационного 16-разрядного слова от регистра сдвига в момент переполнения счетчика 14 бит и для хранения этого слова 30 в течение каждого последующего,начиная с второго,цикла заполнения счетчика 14 бит шеСтнадцатью битами, в течение этого времени из 2-го, 1-го, 10-го и 16-го битов формируются импульсы записи "ЗАП", выборки"СЯ" и смены адреса "+1 Сч АЗ", предназначенного для записи 16-разрядного слова из регистра приема в блок буфернойпамяти По окончании цикла записи слова в блок буферной памяти по выбранному адресу ад рес увеличивается на единицу по импульсу,сформированному с переднего фронта импульса смены адреса "+1 Сч АЗ". Блок буферной памяти предназначен для заполнения и хранения введенного кадра телевизионного изображения, Блок выполнен на 16-статических запоминающихэлементах.Счетчик адреса предназначен для формирования адреса, по которому происходит запись очередного информационного слова в блок буферной памяти в режиме ввода изображения в блок буферной памяти, и для записи адреса от ЭВМ, по которому производится считывание информации из блока 55 буферной памяти в канал ЭВМ в режимеввода информации в ЭВМ.Блок канальных приемопередатчиковпредназначен для приема информации из 8данных и адреса из ЭВМ в блок управления.Блок канальных приемопередатчиков состоит из 4 магистральных приемопередатчиков, которые находятся в режиме приемаинформации от ЭВМ. В режим выдачи информации в ЭВМ приемопередатчики переводятся сигналом "ПРД" от блока связи сЭВМ,Блок связис ЭВМ, предназначен дляорганизации обмена информацией с ЭВМ, вего функции входитдешифрация адреса, выполнение канальных операций "В,вод-вывод".Устройство работает следующим образом.Устройство обеспечивает работу в двухрежимах - в режиме ввода информации вблок буферной памяти от телекамеры и.обмена с ЭВМРежим ввода информации от телекаме.ры.В этом режиме видеоинформация, принимаемая от телекамеры регистром сдвига, поступаетпословно в регистр приема, изнего в блок буферной памяти и запоминается в последнем.Порядок выполнения операций следующий. Для перевода устройства в режим приема информации от телекамеры, ЭВМформирует команду сброса устройства, поступающую на элементы 20 и 27, а затемзаписывает единицу (по 1-му разряду канала данных ЭВМ) в регистр управления исостояния (включающий первый триггер 8разрешения приема, второй триггер 17 йуска, четвертый трйггер 26 готовности); дляэтого в цикле работы "Вывод" ЭВМ подает .импульс "Первый разряд" на О-вход триггера 17, в результате чего триггер 17 пускапереводится в единичное состояние, формирователь 13 формирует положительныйимпульс по переднему фронту сигнала"Пуск", который переводит устройство в исходное состОяние, организуя сигнал сбросаустройства навыходе третьего элементаИЛи 27,Сигнал "Пуск" поступает на вход второго элемента И-НЕ, на выходе которого фор-.мируетСя положительный перепад позаднему фронту кадрового импульса "КГИ";поступающему на второй вход второго элемента И - НЕ, т, е, по началу телевизионногокадра, устанавливающий первый триггер 8"Разр. пр," в "0" сигналом с выхода второгоэлемента И - НЕ, поступающего на С-входпервого триггера 8,На выходе второго элемента ИЛИ-НЕ 7формируется сигнал высокого уровня, разрешающий прохождение тактовой частоты" через четвертый элемент И - НЕ 11 навход синхронизации регистра сдвига и через первый элемент И 9 на счетный входсчетчика 14 бит. Счетчик 14 бит по мерезаполнения его импульсами тактовой частоты формирует на информационных выходах 5коды, поступающие на входы дешифратора21, формирующего на выходах первом, втором, десятом и шестнадцатом) импульсы,служащие для формирования на элементах16,22,23,24,25,28,29 и 30 сигналов записи, 10выборки для блока буферной памяти и сигнала смены адреса для счетчика адреса.На выходе переполнения счетчика 14бит по каждому 16-му импульсу тактовой. частотыформируется импульс перейолнения, который через элемент 18 задержки,воздействуя на синхровход регистра приема, перезаписывает информационное слово из регистра сдвига в регистр приема,кроме того, импульс переполнения с выхода 20счетчика бит переводит третий триггер 25 всостояние 1", сигнал с инверсного выходатриггера 25 разрешает формирование сигналовзаписи "ЗАП" на выходе пятого 28триггера и сигнала выборки "СЯ" на выходе 25четвертогоэлемента ИЛИ-НЕ 30 для блокабуферной памяти и для счетчика адреса сигнала смены адреса "+1 Сч АЗ", на вь 1 ходешестого трйггера, который увеличивает содержимое счетчика адреса на единицу.:- 30После заполнения информацией блокабуферной памяти счетчик адреса вырабатывает сигнал переполнения "ПРП", которыйустанавливает четвертый триггер 26 готовности в единичное состояние и сбрасывает 35первый триггер 8 "Разр, пр. и второй триггер17 "Пуск". На этом процесс ввода изобра,. жения в блок буферной памяти прекращается,Режим обмена с ЭВМ. :., 40В этом режиме информация, записанная в блок буферной памяти, может быть- считана ЭВМ при выполнении канальнойоперации "Ввод", Порядок выполнения операций следующий. ЗВМ в адресной частй 45передает адрес ячейки памяти блока буферной памяти по шинам адреса и данных КДАСО)Н в блок канальных приемопередатчиков и по шинам адреса, данных и-управления в блок связи с Э В М. Блок связи с ЭВ М 50дешифрирует адрес данного блока уйравления.Через 150 нс после выдачи адреса вканал ЭВМ вырабатывается сигнал "КСИАН", поступающий на один вход второго 55элемента И - НЕ 19, на второй вход которогопоступает открывающий сигнал в виде высокого потенциала с инверсного выхода второго триггера 17, С выхода второтоэлемента И - НЕ 19 передний франт сигнала"СИАН" записывает в счетчик (регистр) адреса адрес выбранной ячейки блока буферной памяти, адрес запоминается в регистре адреса, Далее ЭВМ снимает информацию с линии КДА(00 - 15)Н, выставляет в блок связи сигнал "КВВЛДН", сигнализируя о готовности ЗВМ принять информацию, Блок связи с ЭВМ, приняв сигналы "КСИАН" и "КВВДН", формирует сигнал "ПРД", кото-рый переводит блок канальных приемопередатчиков в режим чтения информации в ЭВМ, Сигнал выборки "СЯ" для блока буферной памяти при чтении из него информация в канал ЭВМ при выполнейии ЭВМ цикла "Ввод" формируется в блоке связи с ЭВМ из дешифрированного вблокесвязи с ЗВМ адреса и сигнала "СИАН", этот сигнал поступает на один вход "Адр." четвертого элемента ИЛИ-НЕ 30, с выхода которого, он поступает на вход "СГ блока буферной памяти и разрешаетего работу, В результате информация из нужной ячейки памяти блока буферной памяти поступает вЗВМ для дальнейшей обработки.Блок связи с ЭВМ формирует с задержкой относительно сигйала "К Ввод Н" сигнал "К СИП Н", который извещает ЗВМ, что информация выставлена в канал ЭВМ, ЭВМ принимает сигнал "К СИП Н", данные из канала и снимает Сигнал "К Ввод". Блок связи с ЭВМ снимает сигнал "К СИП Н",завершая передачу данных к ЭВМ, по за- днему фронту сигнала "К СИП Н" снимает сигнал "К СИП А", завершая канальный цикл "Ввод",Устройство может быть использовано при создании гибких производственных модулей для очувствления роботов и т. д. в случаях, когда применяется обработка двумерных изображений бинарным методом. Устройство позволяет вести ввод видеоинформации в ЭВМ со скоростью телевизирннай развертки, при этом устройство может работать благодаря введению блока управления, с различной тактовой частотой, принимаемой с интерфейса телекамеры, Введение дешифратора 21, триггеров 28 и 29, элементов 9, 10, 15, 16, 23, 22, 24 и 27 со связями позволяет увеличить помехозащищенность устройства, исключая сбои в работе за счет формирования фронтов и спадов импульсов записи, выборки, смены адреса от тактовой частоты,Предлагаемое устройство по сравнению с известным позволяет повысить помехозащищенность и расширить функциональные возможности устройства для ввода изображения в ЭВМ за счет обеспечения возможности работы с различными тактовыми частотами и устранения сбоев при запи- выход первого элемента ИЛИ-НЕ соединен си информации в буферную память, с вторым входом третьего элемента ИЛИ -НЕ, выход которого является пятым выхоФ о р м у л а и з о б р е т е н и я дом устройства, выход формирователя Устройство для управления вводом изо импульсов соединен с вторым входом пербражения, содержащее три элемента НЕ, вого элемента ИЛИ, выход которого соедичетыреэлемента И - НЕ,триэлемента ИЛИ- нен с входом обнуления четверто о Н Е. два элемента ИЛИ, четыре триггера, триггера, вторым входом первого элемента формирователь импульсов, элемент задер- ИЛИ - НЕ и.является шестым выходом устжки и счетчик, выход переполнения которо ройства; выход третьего элемента И - НЕ явго соединен с входом элемента задержки,ляется седьмым выходом устройства, о т л и- выход которого является первым выходом ч а ю щ е е с я тем, что, с целью повышения блока управления, первый вход третьего помехозащищенности устройства, оно созлемента И-НЕ являетсяпервымвходом держит четвертый ипятый элементы НЕ, блока управления, первый вход"третьего 15 пятый элемент И-НЕ, три элемента И, треэлемента И-НЕ является первым"входом ус- тийэлемент ИЛИ, четвертый элемент ИЛИ - тройства, О и С-входы второго триггера яв- НЕ, пятый и Шестой триггеры, дешифратор, ляются соответственно вторым и третьим . первый-третий входыивыходпервогоэлевходами устройства, второй выход второго мента И соединены соответственно с выхотриггера соединен с вторым входом третье дами первого и второго элементов НЕ, го элемента И-НЕ, первыми входами:треть- выходом второго элемента ИЛИ-НЕ и счетего и второго элемента ИЛИ-НЕ, второй ным входом счетчика, выход переполнения вход и выход последнего соединены соот- и группа информационных выходов счетчиветственно с выходом первоготриггераи с ка соединены соотве 1 ственно с 5-входом первым входом четвертого элемента И - НЕ, 25 третьего триггера и группой информационвыход которого является вторым выходом ных входов дешифратора, первый - четвер- устройства, второй - четвертый:входы чет-тый выходы которого соединены вертого элемента И-НЕ соединены соответ- соответственно с первыми входами второго ственно с выходами йервого -" третьего и третьего элементов И, входами пятого и элементов НЕ, вход третьето элемента ЙЕ 30 четвертогоэлементов НЕ, выход последне- является четвертым входом устройства и го соединен с входом синхронизации шессоединен с первыми входами первого эле- того триггера, О-вход которого соединен с мента ИЛИ-НЕ и пеРвого элемента И - НЕ, - выходомтретьего триггера, вторым входом выход которого является третьим выходом третьего элемента И, О-входом пятого тригустройства, второй вход первого элемента 35 гера и вторым входомвторого элемента И, И-НЕ соединен с первым выходом второго выход которого соединен с 3-входом пятого триггера, входом формирователя импуль- триггера, вход синхронизации которого сосов, первым входом второго элемента И - единен с,выходом пятого элемента НЕ и НЕ, второй вход которого соединен с первым входом пятого элемента И - НЕ, втовходом второго элемента НЕ иявляе 1 ся пя рой вход и выход которого соединены соот- . тым входом устройства, выход второго эле- ветственнос выходомтретьегоэлемента НЕ мента И-НЕ соединен с входом ис первым входомтретьегоэлемента ИЛИ, синхронизации первого триггера, О-вход второй вход которого соединенс: выходом которого соединен с шиной нулевого потек- первого элемента ИЛИ, выход третьего элециала устройства, а Я-вход - с входом обну мента ИЛИ - с входами обнуления третьего ления второго триггера и вйходом второго триггера, счетчика и пятого триггера, выход элемента ИЛИ, первый вход которого сое- которого соединен с первым, входом четвердинен с Я-входом четвертого триггера и яв- того элемейта ИЛИ-НЕ, второй вход и выляется шестым входом устройства, второй ход которого являются соответственно вход второго элемента ИЛИ соединен с пер девятым входом и восьмым выходом устройвым входом первого элемента ИЛИ и явля- ства, Я-вход шестого триггера соединен с ется седьмым входом устройства, выход выходом третьего элемента И, выходы пяточетвертого триггера является четвертым вы- го и шестого триггеров являются соответстходом устройства, вход первого элемента венно девятым и десятым выходами НЕ является восьмым входом устройства. 55 устройства. Тиражсударственного комитета по 113035, Москва. ЖПроизводственно-издательский коиб Подписноезобретениям и открытиям при ГКНТ СССРРауаская наб 4/Бт "Патент", г Ужгород, ул.Гагарина, Ю 1В

СмотретьЗаявка

4748449, 11.10.1989

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ ПРИБОРОСТРОЕНИЯ

КЛОЧКОВА ЗИНАИДА ПРОКОФЬЕВНА, СИРЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, СУББОТИН ВЛАДИМИР АНАТОЛЬЕВИЧ, ПАРФЕНОВ ВАЛЕНТИН ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 3/00

Метки: вводом, изображения

Опубликовано: 30.07.1992

Код ссылки

<a href="https://patents.su/7-1751738-ustrojjstvo-dlya-upravleniya-vvodom-izobrazheniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для управления вводом изображения</a>

Предыдущий патент: Устройство для синхронизации вычислительной системы

Следующий патент: Устройство для ввода информации

Случайный патент: Машина для контактной многоточечной сварки