Программируемый генератор циклов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1644119

Автор: Окороков

Текст

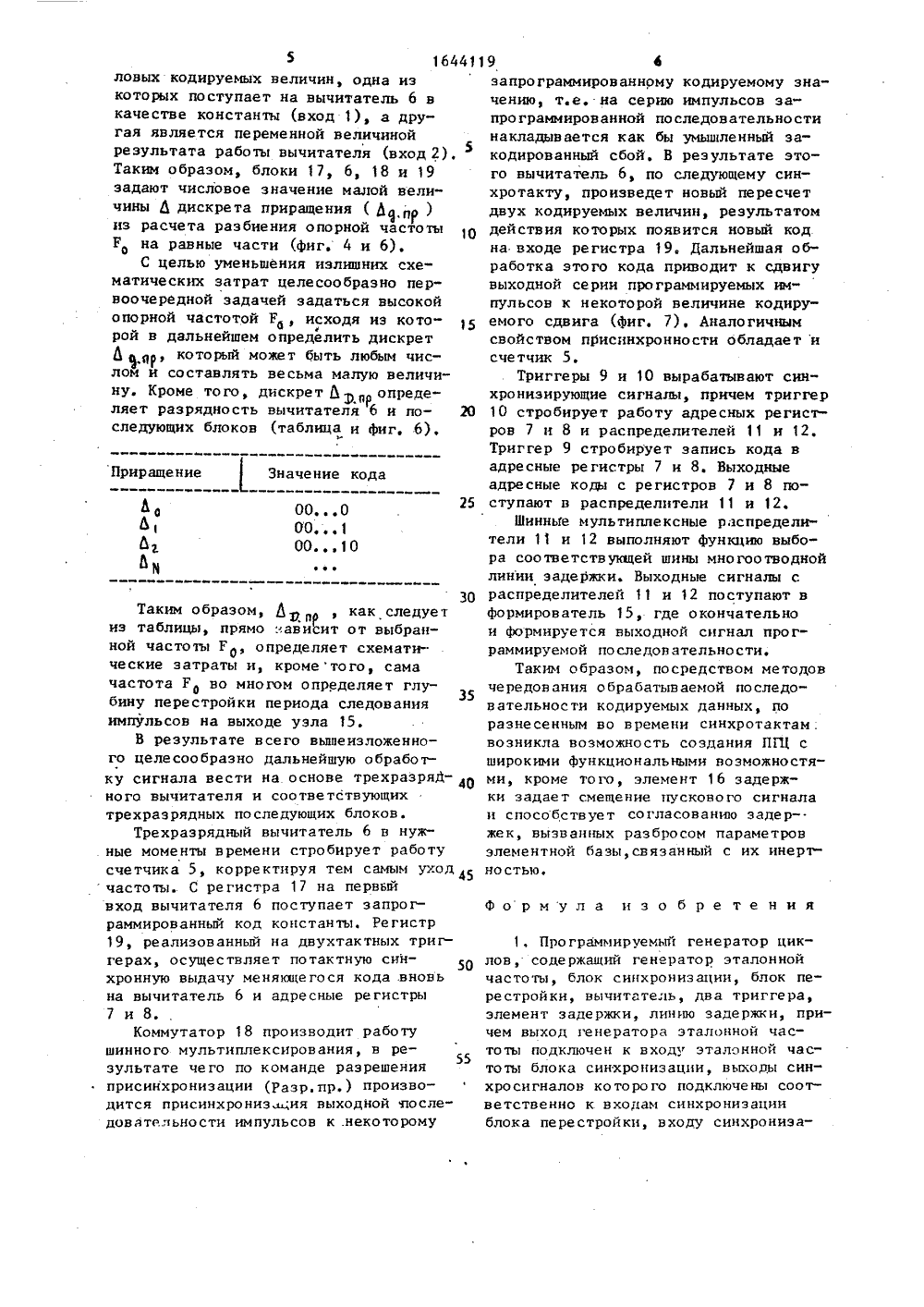

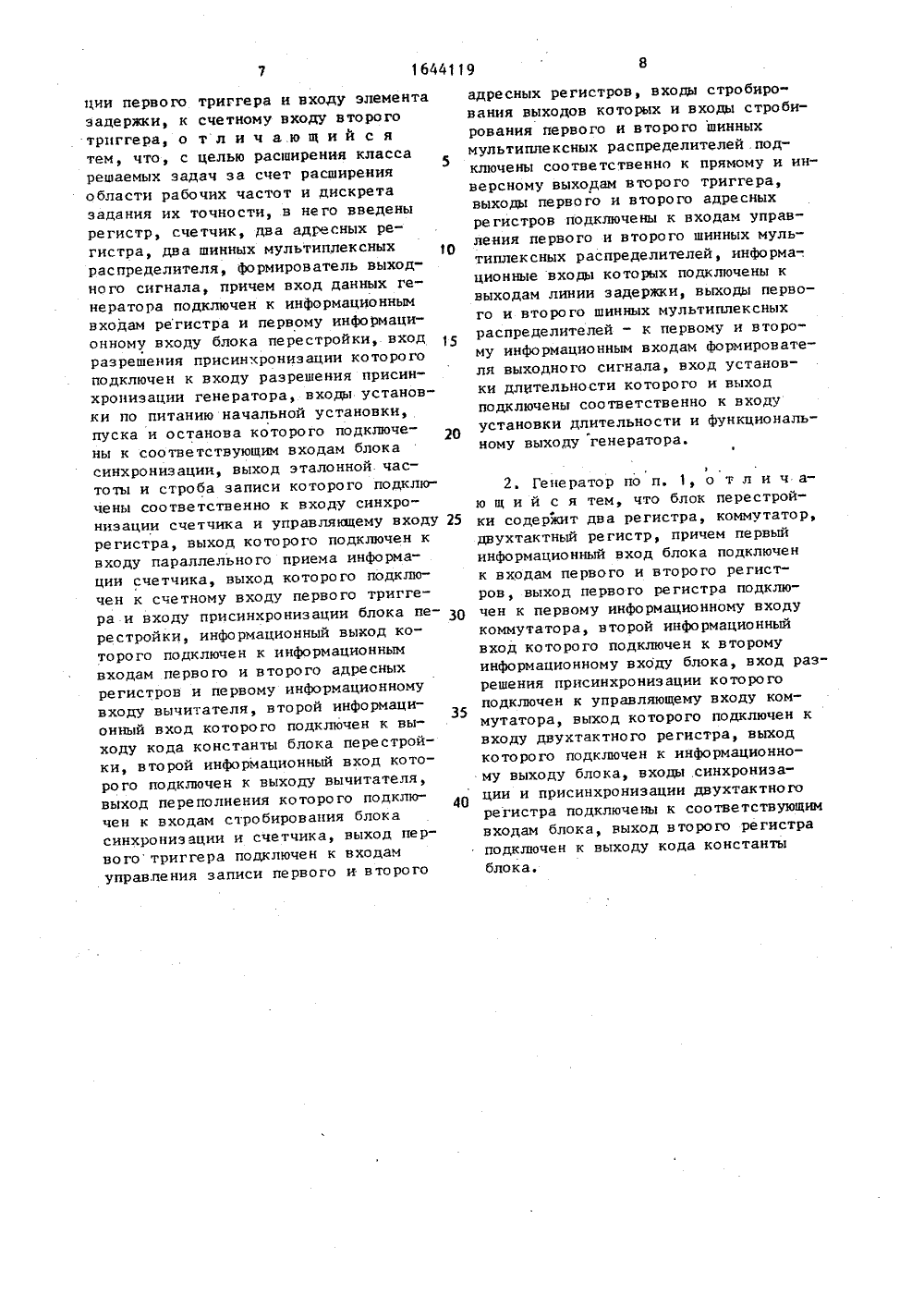

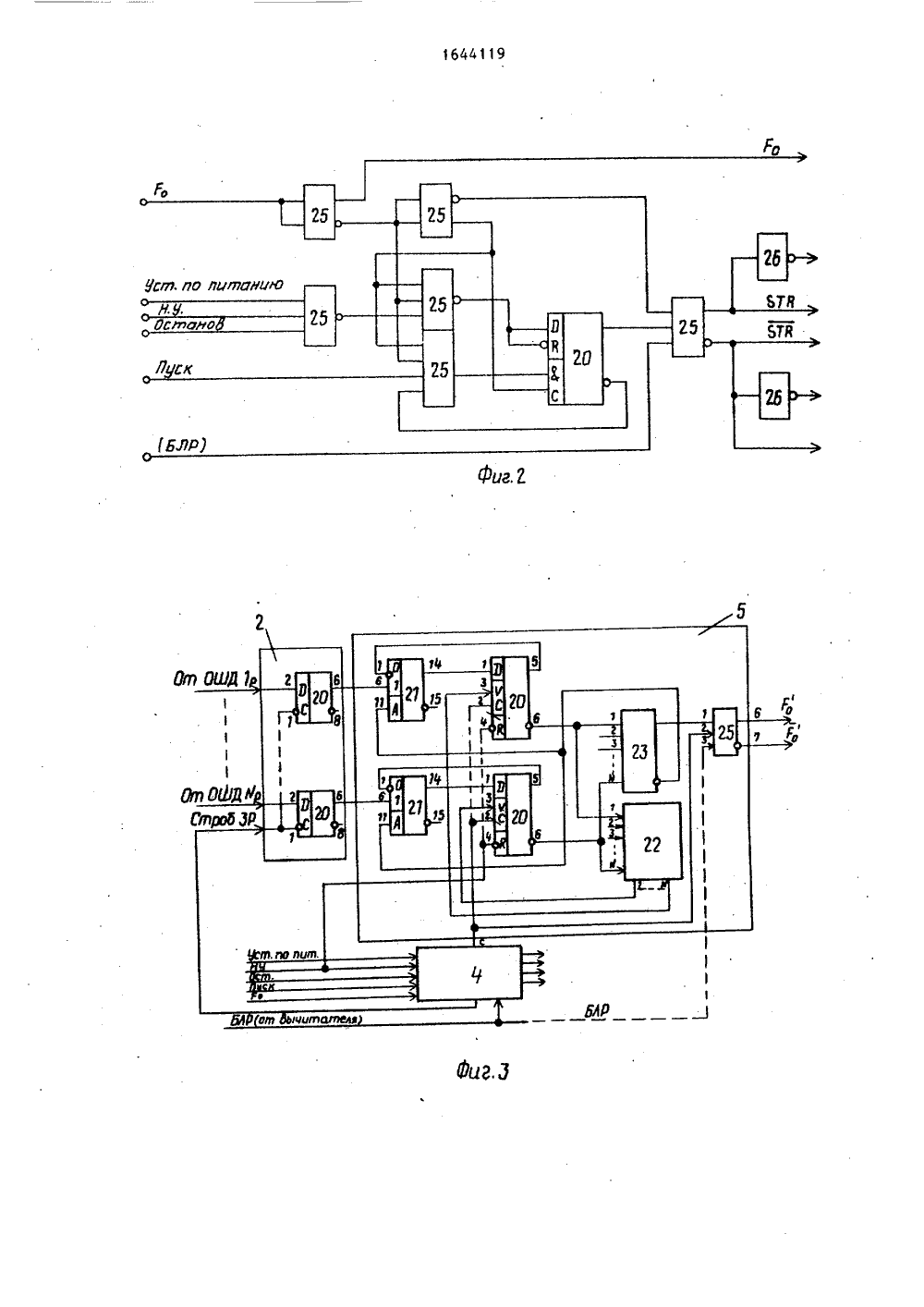

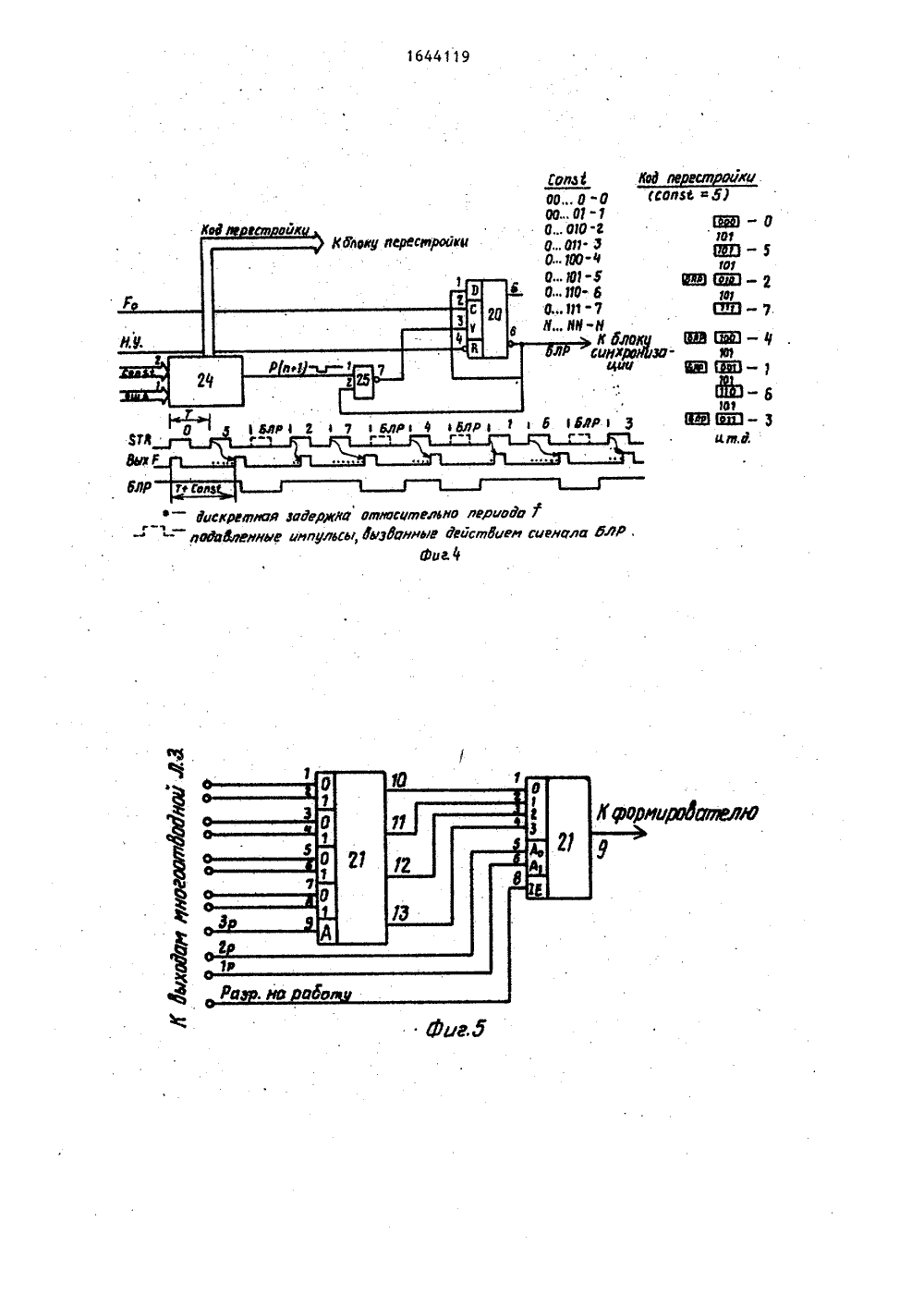

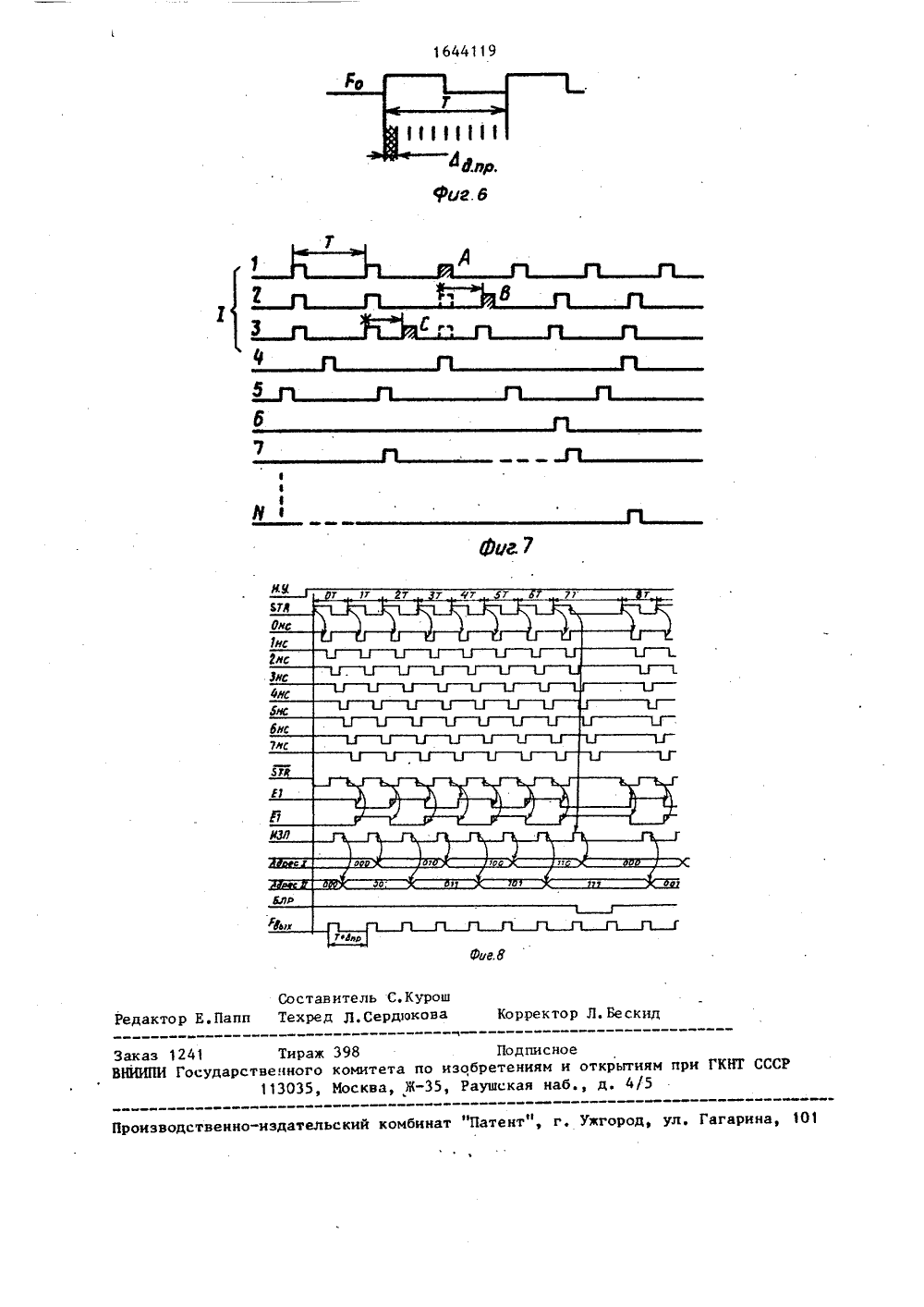

ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОЗНРЫТИЯМПРИ ГКНТ ССОР 51)5 С 06 Р 1/02(56) Авторское свидетельство СССР В 877511, кл. С 06 Р 1/02, 1980.Авторское свидетельство СССР В 564616, кл. С 06 Р 1/02, 1981. (54) ПРОГРАММИРУЕМЫЙ ГЕНЕРАТОР ЦИКЛОВ(57) Изобретение относится к автоматике, выЧислительной технике, предназначено для генерирования импульсных сигналов с заданными периодами следования и может быть использовано в контрольно-измерительном оборудовании параметрического контроля 2БИС и СВИС. Цель изобретения - расширение класса решаемых задач за счет расширения области рабочих частот и дискрета задания их точности. Устройство содержит регистр 2, блок 4 синхронизации, блок 3 перестройки, счетчик 5, вычитатель 6, адресные регистры 7,8, триггеры 9,10, генератор 1 эталонной частоты, шинные мультиплексные распределители 11,12, линию 13 задержки, элемент 14 задержки, формирователь 15 выходного сигнала. Поставленная цель достигается за счет введения регистра 2, счетчика 5, адресных регистров 7,8, шинных мультиплексных распределителей 11,12, формирователя 15 выходных сигналов.1 з.п. ф-лы, 8 ил 1 табл.Изобретение относится к автоматике и вычислительной технике и предназначено для генерирования импульсных сигналов с заданными периодамиследования и, кроме того, может бытьиспользовано в контрольно-измерительном оборудовании параметрического контроля БИС и СВИС в качествеперестраиваемого генератора, таймера, Формирователей синхронизирующих,стробирующих и управлякщих сигналовобъекта контроля, где точное высокочастотное генерирование импульсныхсигналов с заданными параметрами расширяет саму методику параметричес"кого контроля и способствует классусоздания более прогрессивной цифровой вычислительной техники.Цель изобретения " расширение 20класса решаемых задач за счет расширения области рабочих частот и дискрета задания их точности.На Фиг. 1 представлена функци,ональная блок-схема генератора; на 25фиг, 2 - блок синхронизации; нафиг. 3 - схема приемного буферногорегистра и универсального программируемого счетчика; на фиг. 4 - функциональная схема вычитателя и диаграмма его работы; на фиг. 5схемашинного мультиплексного распределителя; на фиг. 6 - диаграмма, поясняюрая расчетную величину дискретана Фиг. 7 - временные диагФ 35раммы выходных импульсов; на фиг. 8 -диаграмма взаимодействия основных сигналов.Устройство содержит генератор 1эталонной частоты, регистр 2, блок 340пере стройки, блок 4 синхро ниэ ации,счетчик 5, вычитатель 6, адресные регистры 7 и 8, два триггера 9 и 10,два шинных мультиплексных распределителя 11 и 12, линию 13 задержки, элемент 14 задержки и формирователь 15выходного сигнала.Блок 3 перестройки содержит регист ры 16 и 17, коммутатор 18, двухтактный регистр 19. На фиг. 2-5 обозначены триггеры 20, мультиплексоры 21,дешифратор 22, схема 23 сравнения,сумматор 24, элементы И 25, элементы ИЛИ 26,Генератор работает следующим об 55разом.С момента подачи питающего напряжения генератор автоматически приводится в исходное рабочее состояние по команде "Установка по питанию" (Уст. по пит.). Работа генератора осуществляется по команде "Пуск" ипрекращается по команде "Останов", причем результат невыполненной операции сохраняется и может быть продолжен по команде "Пуск". Приведение системы в исходное рабочее состояние в процессе работы осуществляется покоманде начальной установки (Н.У.).На вход блока синхронизации поступаетвысокочастотная опорная частота (Г )кварцованного эталонного генератора, которая, минуя блок синхронизации, в последующем синхронизирует работу блоков 2,5,19,9,10 и 14. Таким образом, блок 4 является важным звеном в работе, поскольку обеспечивает синхронность .выполнения внешних и внутренних команд. Числовое значение кода, обрабаты" ваемое блоком 5, определяет длительность следования импульсов на выходе генератора. Чем больше числовое значение этбго кода, тем более значительное время отводится на перекодирование периода следования выходных импульсов, однако следует отметить, что максимальная частота Функционирования блоков 2 и 5 в части перезаписи информации из одного блока в другой соответствует опорной частоте Р, сдвинутой во времени на величину Т/2, где Т - период эталонной частоты Ро, а значение Р, ограничено функциональным быстродействием счетных схем.Таким образом, достигнута возможность получения на выходе блока 5 высокочастотных серий перепрограммируемых импульсов в соответствии с заданным кодом поступлекия. В ряде случаев такой способ грубого задания периода импульсной последовательности является достаточным и широко используется в вычислительной технике при создании программируемых таймеров, синхронизирующих импульсов и ряда других функциональных узлов цифровой техники.Регистры 2, 16 и 17 производят запись исходных кодируемых данных по внешнему импульсному сигналу записи (ИЗ) и обеспечивают по программе информацией блоки 5,6 и 18.Регистр 19 по синхронизирующим импульсам с блока 4 производит хранение результата пересчета двух чис5 164411 ловых кодируемых величин, одна из которых поступает на вычитатель 6 в качестве константы (вход 1), а другая является переменной величиной результата работы вычитателя (вход 2), Таким образом, блоки 17, 6, 18 и 19 задают числовое значение малой вели" чиныдискрета приращения ( Ь,п ) из расчета разбиения опорной частоты 10 Р на равные части (фиг. 4 и 6).С целью уменьшения излишних схематических затрат целесообразно первоочередной задачей задаться высокой опорной частотой Р , исходя иэ кото 4рой в дальнейшем определить дискрет Ь 1, который может быть любым числом и составлять весьма малую величину. Кроме того, дискрет Ь определяет разрядность вычитателя 6 и по следующих блоков (таблица и фиг. 6). 000 0 О 100 10 Приращение Значение кода ЗОТаким образом, Ьи, как следуетиз таблицы, прямо:;ависит от выбранной частоты Р, определяет схематиче ские э атраты и, кромето го, самачастота Рп во многом определяет глу 35бину перестройки периода следованияимпульсов на выходе узла 15,В результате всего вьппеизложенного целесообразно дальнейшую обработку сигнала вести на основе трехразряйнога вычитателя и соответствующихтрехразрядных последующих блоков,Трехразрядный вычитатель 6 в нужные моменты времени стробирует работусчетчика 5, корректируя тем самым уходчастоты. С регистра 17 на первыйвход вычитателя 6 поступает запрограммированный код константы, Регистр19, реализованный на двухтактных тригерах, осуществляет потактную синхронную выдачу менякщегася кода .вновьна вычитатель 6 и адресные регистры7 и 8.Коммутатор 18 производит работушинного мультиплексирования, в результате чего по команде разрешенияприсинхранизации (Разр,пр,) производится присинхрониз;ия выходной последовательности импульсов к .некоторому запрограммированному кодируемому значению, т.е. на серию импульсов запрограммированной последовательностинакладывается как бы умышленный закодированный сбой. В результате этого вычитатель 6, по следующему синхротакту, произведет новый пересчетдвух кодируемых величин, результатомдействия которых появится новый кодна входе регистра 19. Дальнейшая обработка этого кода приводит к сдвигувыходной серии программируемых импульсов к некоторой величине кодируемого сдвига (фиг. 7), Аналогичнымсвойством присинхронности обладает исчетчик 5.Триггеры 9 и 1 О вырабатывают син"хрониэирующие сигналы, причем триггер10 стробирует работу адресных регис 1 ров 7 и 8 и распределителей 11 и 12,Триггер 9 стробирует запись кода вадресные регистры 7 и 8. Выходныеадресные коды с регистров 7 и 8 поступают в распределители 1 и 12.Шинные мультиплексные распределители 11 и 12 выполняют функцию выбора соответствукщей шины многоотводнойлинии задержки. Выходные сигналы сраспределителей 11 и 12 поступают вформирователь 15, где окончательнои формируется выходной сигнал программируемой последовательности.Таким образом, посредством методовчередования обрабатываемой последовательности кодируемых данных, поразнесенным во времени синхротактам .возникла возможность создания ПЩ сширокими функциональными воэможностями, кроме того, элемент 16 задержки задает смещение пускового сигналаи способствует согласованию задержек, вызванных разбросом параметровэлементной базы, связанный с их инерт"ностью,Формула изобретения 1, Праграммируемьп генератор циклов, содержащий генератор эталонной частоты, блок синхронизации, блок перестройки, вычитатель, два триггера, элемент задержки, линию задержки, причем выход генератора эталонной частоты подключен к входу эталонной частоты блока синхронизации, выходы синхроснгналов которого подключены соответственно к входам синхронизации блока перестройки, входу синхрониэа 1644119ции первого триггера и входу элементазадержки, к счетному входу второготриггера, о тлича.ющий с ятем, что, с целью расширения классарешаемых задач за счет расширенияобласти рабочих частот и дискретазадания их точности, в него введенырегистр, счетчик, два адресных регистра, два шинных мультиплексных 1 Ораспределителя, формирователь выходного сигнала, причем вход данных генератора подключен к информационнымвходам регистра и первому информационному входу блока перестройки, входразрешения присинхронизации которогоподключен к входу разрешения присинхронизации генератора, входы установки по питанию начальной установки,пуска и останова которого подключены к соответствующим входам блокасинхронизации, выход эталонной. частоты и строба записи которого подключены соответственно к входу синхронизации счетчика и управляющему входу 25регистра, выход которого подключен квходу параллельного приема информации счетчика, выход которого подключен к счетному входу первого триггера и входу присинхронизации блока пе- ЗОрестройки, информационный выход которого подключен к информационнымвходам первого и второго адресныхрегистров и первому информационномувходу вычитателя, второй информационный вход которого подключен к выходу кода константы блока перестройки, второй информационный вход кото"рого подключен к выходу вычитателя,выход переполнения которого подключен к входам стробирования блокасинхронизации и счетчика, выход первого триггера подключен к входамуправ. пения записи первого и второго адресных регистров, входы стробиро" вания выходов которых и входы стробирования первого и второго шинных мультипле ксных распределителей . подключены соответственно к прямому и инверсному выходам второго триггера, выходы первого и второго адресных регистров подключены к входам управления первого и второго шинных мультиплексных распределителей, информа-. ционные входы которых подключены к выходам линии задержки, выходы первого и второго шинных мультиплексных распределителей - к первому и второму информационным входам формирователя выходного сигнала, вход установки длительности которого и выход подключены соответственно к входу установки длительности и функциональному выходу генератора.Ф32. Генератор по п. 1, о т л и ч аю щ и й с я тем, что блок перестройки содержит два регистра, коммутатор, двухтактный регистр, причем первый информационный вход блока подключен к входам первого и второго регистров, выход первого регистра подключен к первому информационному входу коммутатора, второй информационный вход которого подключен к второму информационному входу блока, вход разрешения присинхронизации которого подключен к управляющему входу коммутатора, выход которого подключен к входу двухтактного регистра, выход которого подключен к информационному выходу блока, входы синхронизации и присинхронизации двухтактного регистра подключены к соответствующим входам блока, выход второго регистра подключен к выходу кода константы блока.-идискреапая 3 адвржна оапосцтедьио лериодд Р иодайянные импульсы, 5 ыубонные дейстВивн сиенцла4 и8,1644119 Фиг 7 77 ис Составитель С. КурошРедактор Е.Папп Техред Д.Сердюкова Корректор Л, Беск Заказ 1241 Тираж 398ВНИИПИ Государственного комитета113035, Москва, Ж оизводственно-издатепьский комб Подписноео изобретениям и открьггиям при ГКНТ СССР35, Раушская наб., д. 4/5 ат "Патент", г, Ужгород, ул. Гагарина, 1 Ъ

СмотретьЗаявка

4436805, 07.06.1988

ОРГАНИЗАЦИЯ ПЯ В-8466

ОКОРОКОВ ВЛАДИМИР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: генератор, программируемый, циклов

Опубликовано: 23.04.1991

Код ссылки

<a href="https://patents.su/7-1644119-programmiruemyjj-generator-ciklov.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый генератор циклов</a>

Предыдущий патент: Исполнительный прямоходный механизм

Следующий патент: Устройство для ввода информации

Случайный патент: 382018