Устройство для суммирования двух чисел с плавающей запятой

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

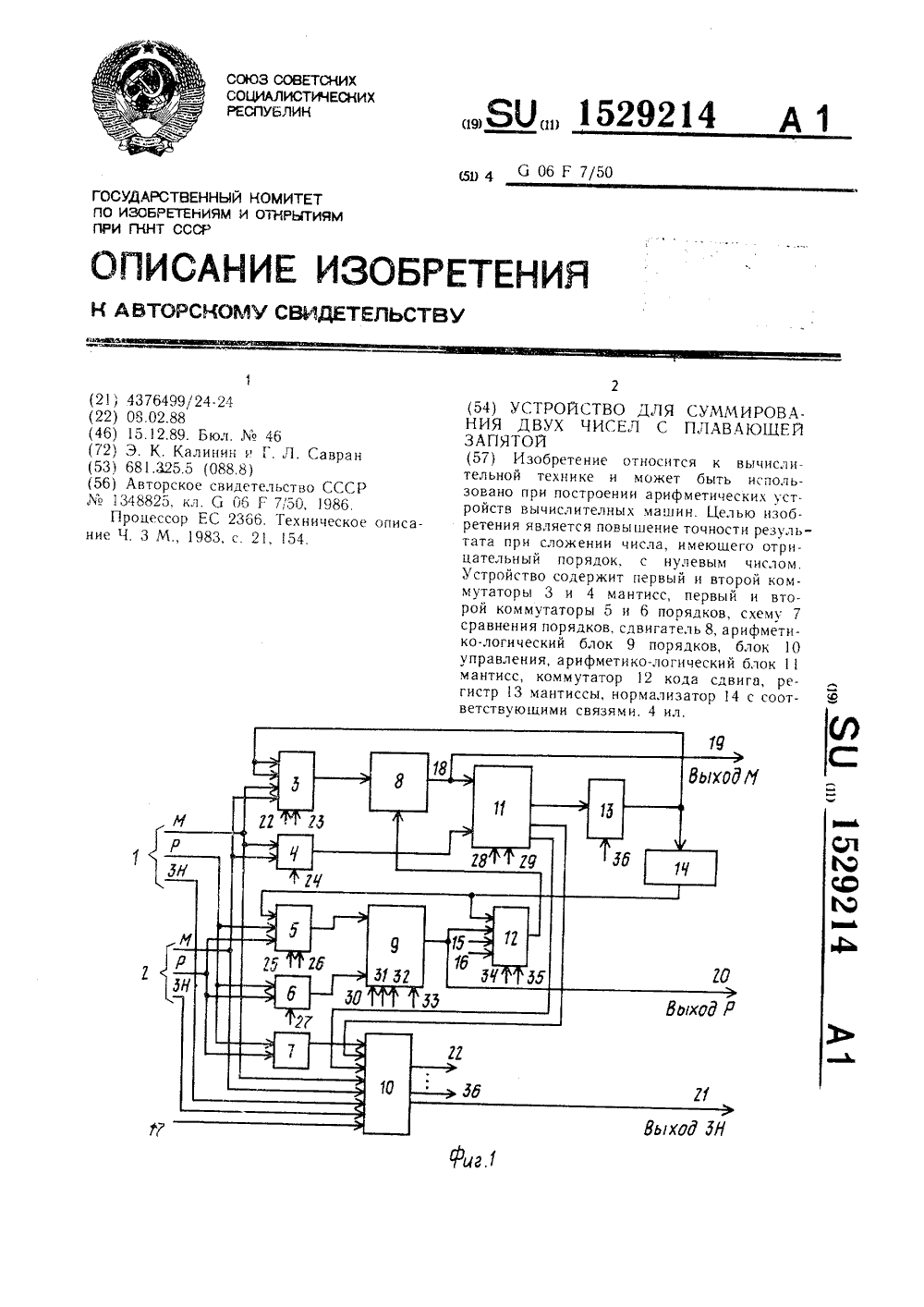

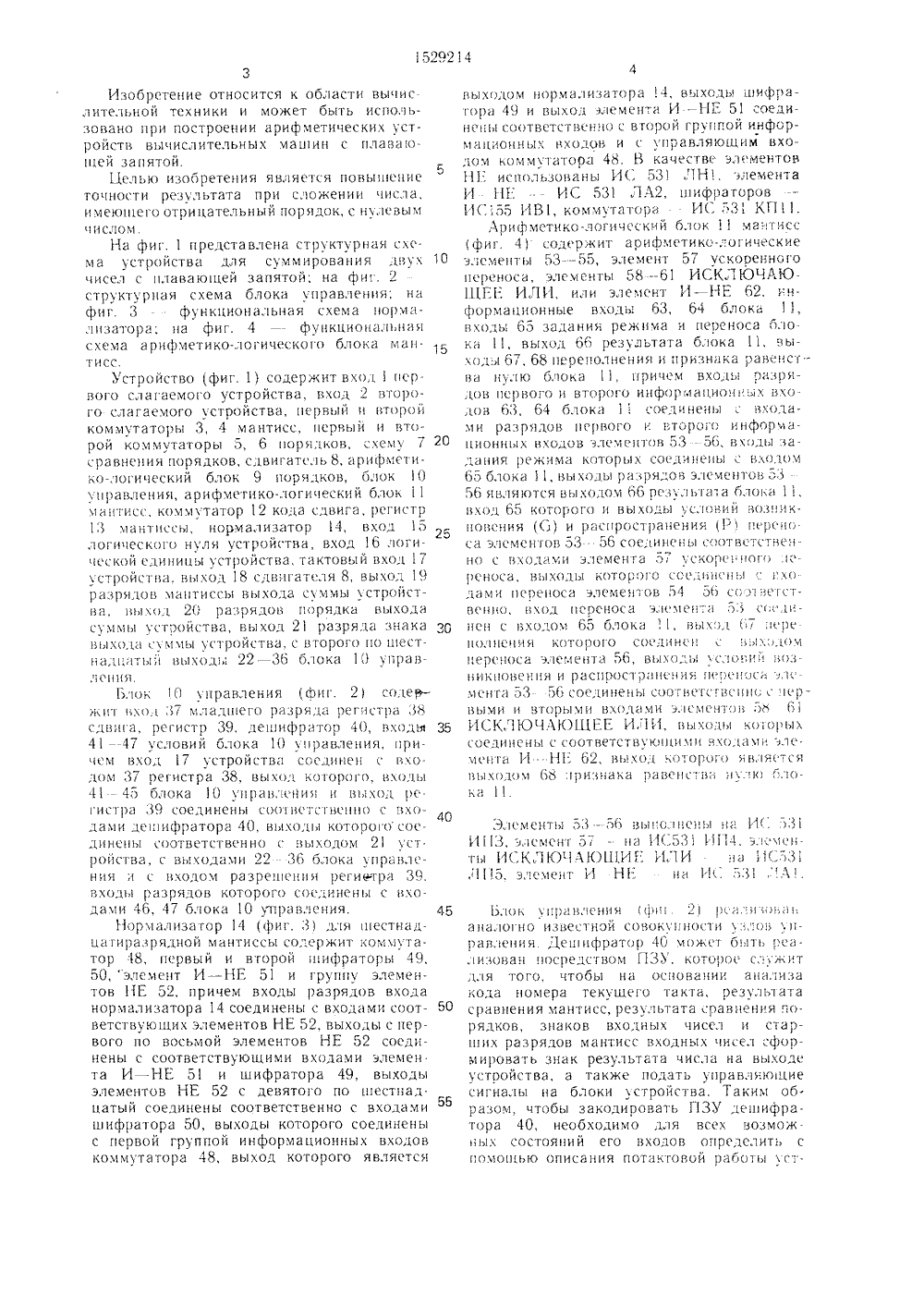

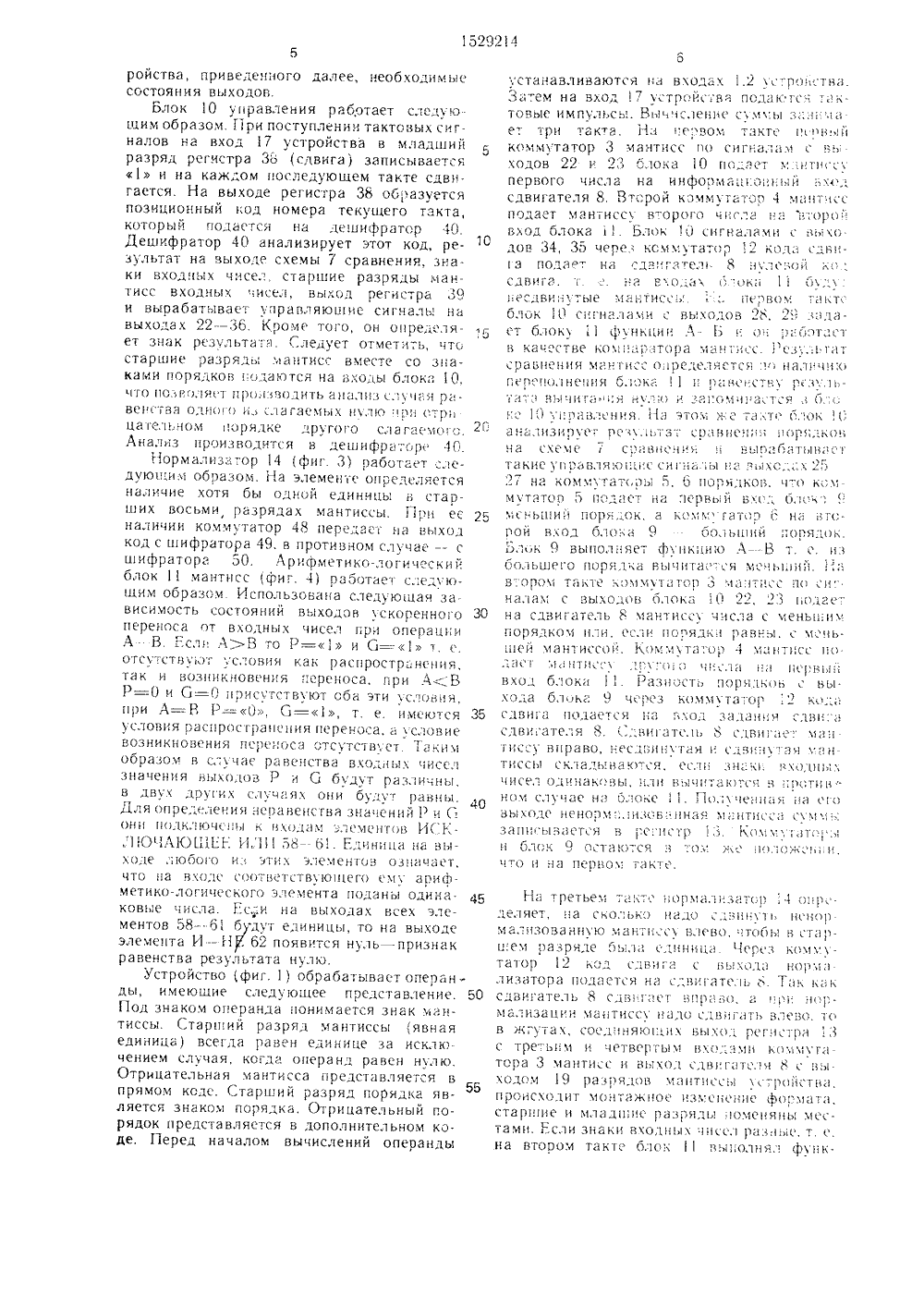

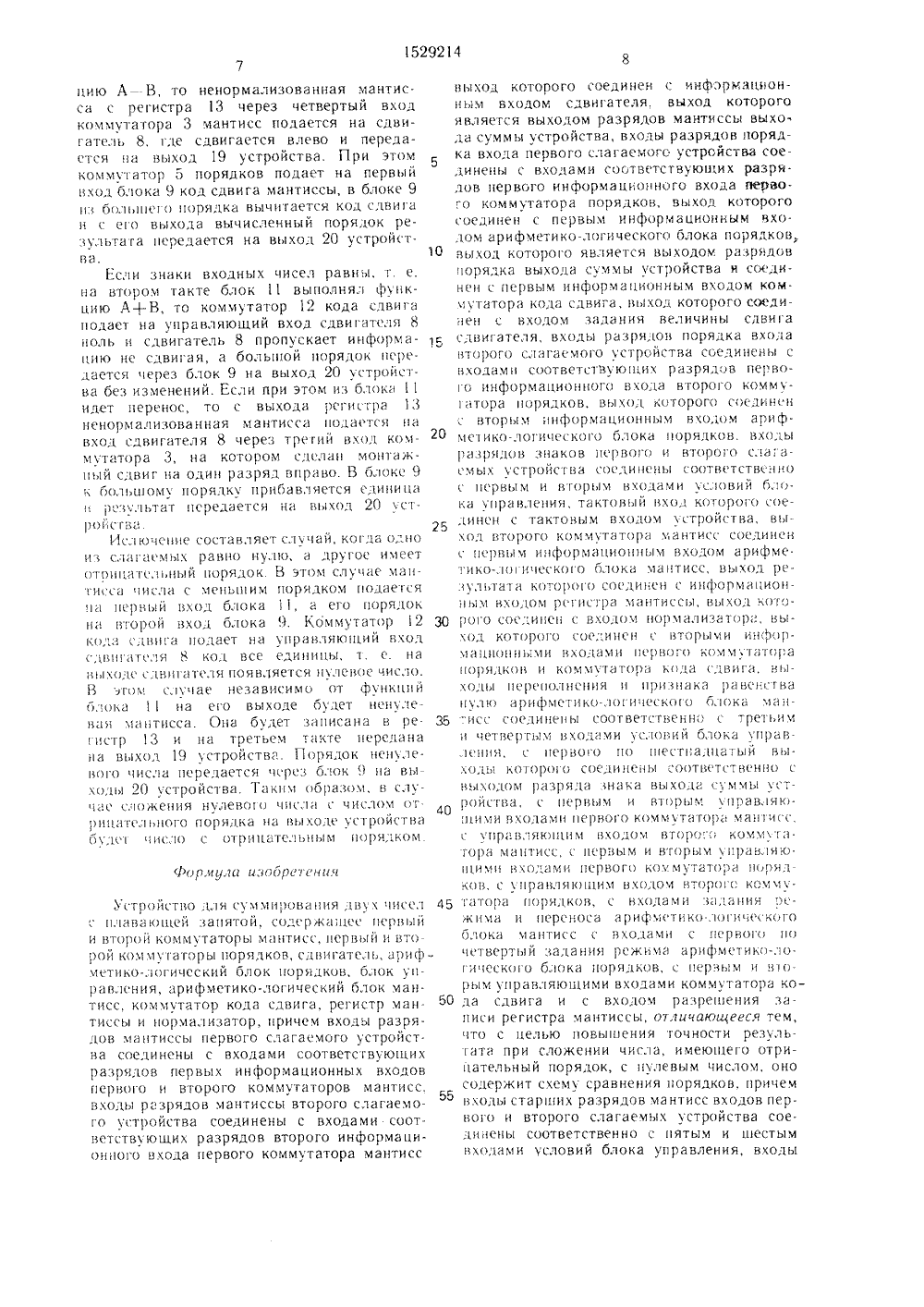

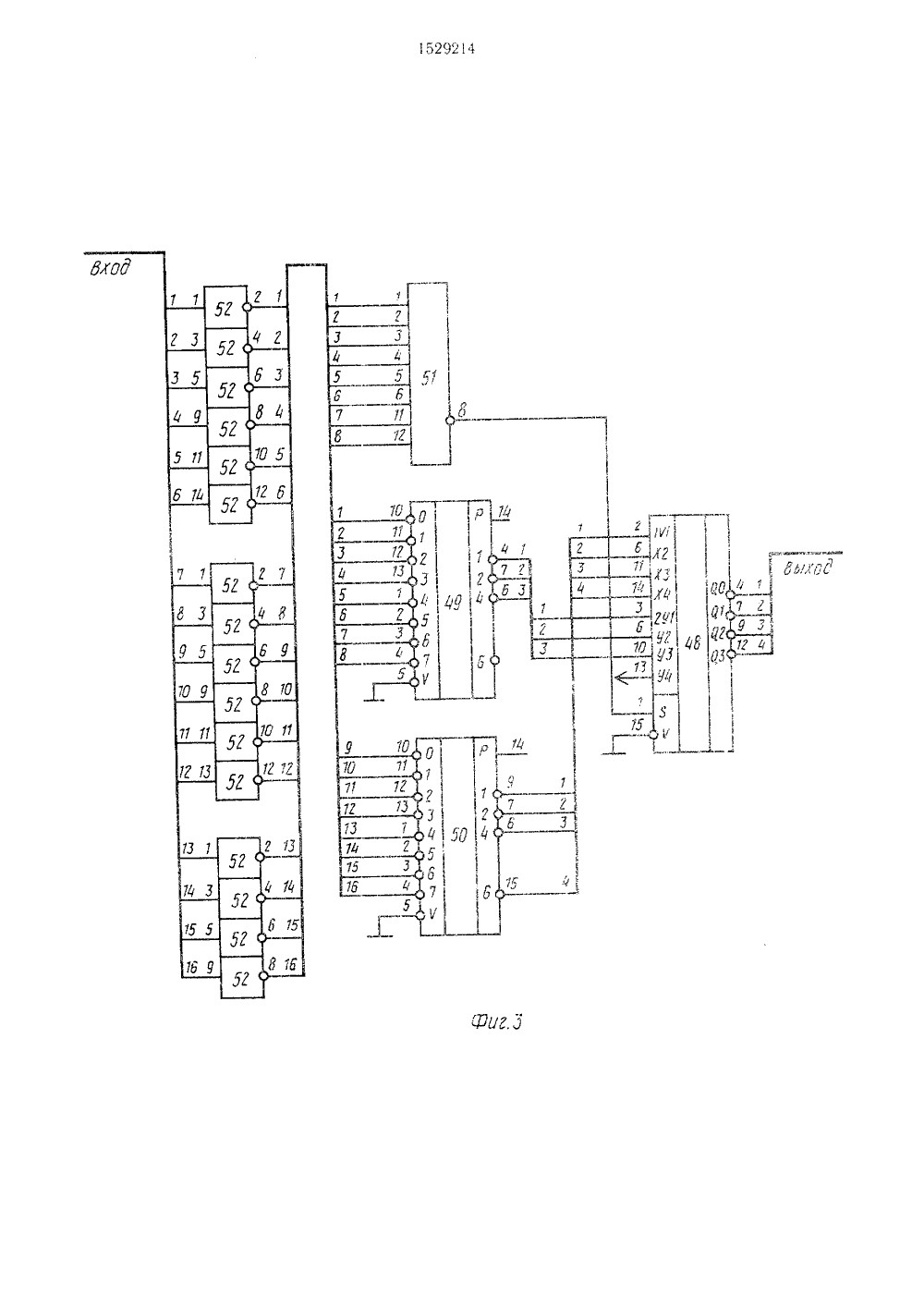

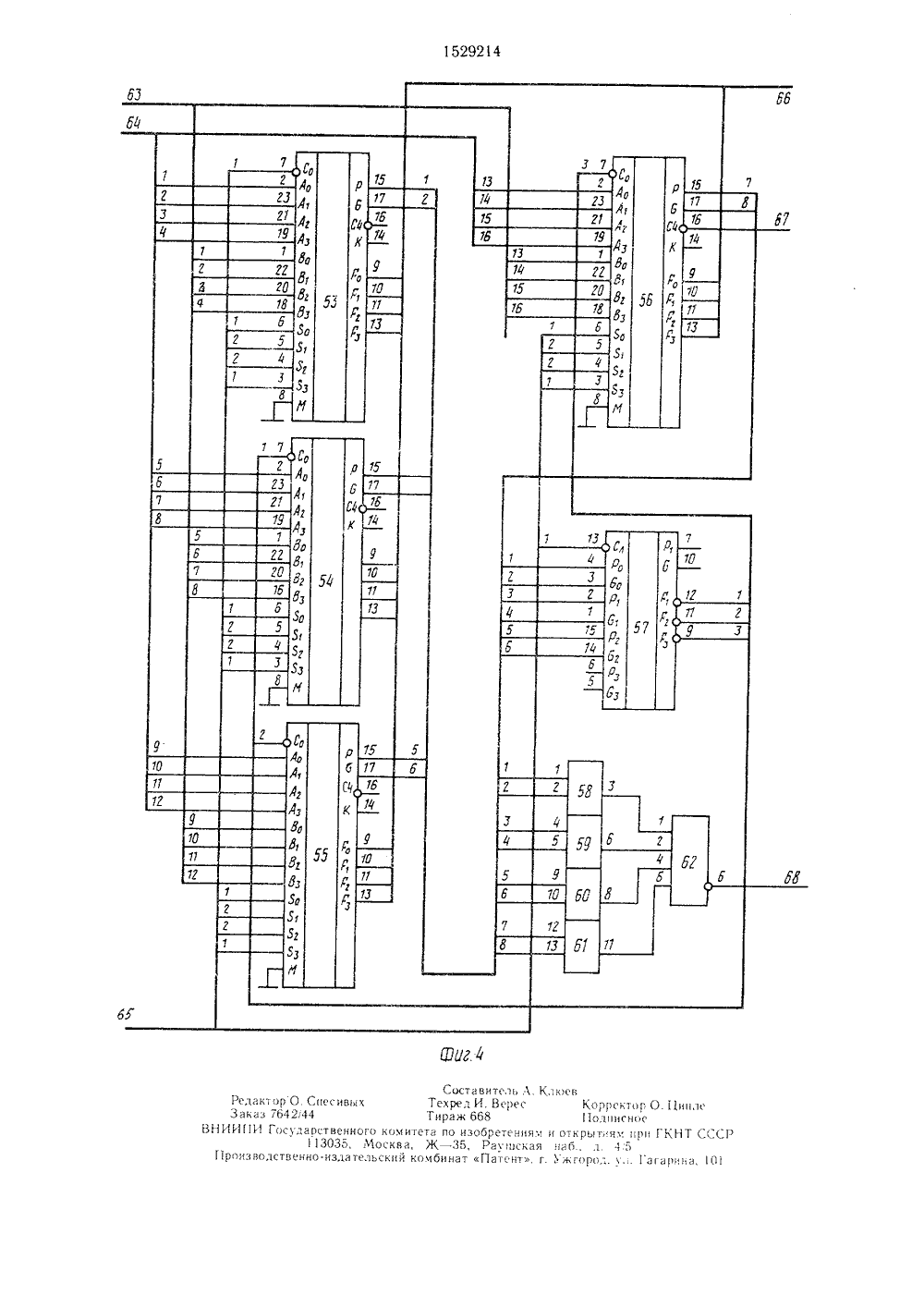

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНРЕСПУБЛИК 4 С 06 Е 7 описаюг,1 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОЩРЬГИПРИ ПЮТ СССР(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ДВУХ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ(57) Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств вычислителных машин. Целью изобретения является повышение точности результата при сложении числа, имеюшего отрицательный порядок, с нулевым числом. Устройство содержит первый и второй коммутаторы 3 и 4 мантисс, первый и второй коммутаторы 5 и 6 порядков, схему 7 сравнения порядков, сдвигатель 8, арифметико-логический блок 9 порядков, блок 10 управления, арифметико-логический блок 1 мантисс, коммутатор 12 кода сдвига, регистр 13 мантиссы, нормализатор 14 с соответствующими связями. 4 ил.1529214 51015 Изобретение относится к области вычислительной техники и может быть использовано при построении арифметических устройств вычислительных машин с плавающей запятой.Целыю изобретения является повышение точности результата при сложении числя, име 1 оцего отрицательный порядок, с н) левым числомНа фиг. 1 представлена структурная сям а устройства для сумм ирован и я двух чисел с плаваюцей запятой; на фиг. 2 структурная схема блока управления; на фиг. 3 - функциональная схема нормялизатора; на фиг. 4 функциональная схема арифметико-логического блока мантисе.Устройство (фиг. 1) содержит вход 1 первого слагаемого устройства, вход 2 Второго слагаемого устройства, первый и второйкоммутаторы 3, 4 мантисс, первый и второй коммутаторы 5, 6 юрялков, схсмх 7 20сравнения порядков, слвигатсль 8, арифметико-логический блок 9 порядков, блок 10управления, арифметико-логический блок 11мя 1 ггисс, коммутатор 12 кода сдвига, регистр13 мантиссы, нормализатор 4, вход 15логического нуля устройтва, вход 16 логической единицы устройства, тактовый вход 17устройств. выход 18 сдвигатсля 8, выход 19разрялов мантиссы выхода лммы устройства, Вы,ол 20 разрядов порядка выходасуммы усгройства, выход 21 разряда знакаВыяхя суммы устройства, с второго по шестнал 1 гятый выход,1 22- - 36 блока 1) управЛ .11151,3 л о к 1 0 управления ( ф и г . 2 ) соле )жнт Вяи 37 млалпего разряла регистра 38сдвига, регистр 39, дешифратор 40, Вхолв 3541- 47 условий блока 10 управления, причем Вход 17 устройства соединен с г 1 хлом 37 регистра 38, выхол которого, Входы41- 45 блока 10 управления и Выход регистра 39 соединены сопнстсгвепно с Входами лен 1 ифратора 40, выхл 11 котооол 1 соединены соответственно с Выходом 21 устрОЙствя, с вьхолями 22 36 блока управления и с Входом разрепцння регистра 39,входы разрядов которого соединены с Входами 46, 47 блока 10 управления. 45Нормализатор 14 фиг. 3) лля шестнадцатиразрядной мантиссы содержит коммутатор 18, первый и второй 1 нифраторы 49,50, элемент И - НЕ 51 и группу элементов НЕ 52, причем входы разрядов входанормялизатора 14 соединены с входами соответствующих элементов НЕ 52, выходы с первого по восьмой элементов НЕ 52 соединены с соответствующими входами элемента И - НЕ 51 и шифратора 49, выходыэлементов НЕ 52 с девятого по шесталцатый соединены соответственно с входамишифратора 50, выходы которого соединеныс первой группой информационных входовкоммутатора 48, выход которого является Выходом нормализятора 4, выходы шифратора 49 и выход элемента И- - НЕ 51 соедин.Ны сООтветствснно с второи Грхппои инфорМ 1 ЦИОННЫХ ВХОЛОВ ИМГ 1 РЯВЛЯЮЩИМ ВХО- лом коммутатора 48. Б качестве элементов Н 1, использованы ИС 53) .11 Н , элемента И НЕ -- ИС 531 СЛА 2, шифраторов ИГ,55 ИБ 1, коммутатора - ИС 53 КП 11.Арифметика-логичский блок 11 магтисе ( фиг. 4) содержит а он фметико-логические элементы 5355, элемент 57 мскоренного переноса, элеменгы 58 61 ИСКЛЮЧАЮ 1 ЦЕ. И.7 И, или элемент И - НЕ 62. Информационные входы 63, 64 блока 11, Вхоль 65 задания режима и переноса Оло кя 11, выход 66 результата блока 11, Выхолы 67, 68 переполнения и признака равенс -Вя нулю блока 11, причем входы разрядов первого и второго инфор 1 яцион ых вхолов 63, 64 блока 1 соединены, вхолами разрядов первого и Второго информяционньх Входов элемегОВ 53 - 06, входы зяляния режима которь 1 х соединены ." Входом65 блока 11, выходы разрядов элементов 5356 являкггся Выхлом 66 рсзхльтя;я блока 11,Вход 65 которо 0 и Выходы0.10 ВИИ Возникновения 6) и распространения (э) перси,са элементов 53 - 56 сое;инены ск 1 твстственно с Входами элемента 57 ускоре 1 ного .реноса, Выходы которого соединен ы . и ядами переноса элементов 54 56 соя:1 етстВенно, Вход перенося элмен.я 53 с 1 линсн с Входом 65 блока1, выход 67 ппеполнения которого соединенььхяломпереноса элемеггя 56, выходы )слов 11 й Возн икновсн 1 я и распростр 1 нен и 51 иренося элемента 53 56 соединены соотнетсгвс",10 с:1 ерВыми и вторыми входами элементов 58 61 ИСК,7 ЮЧАК)ШЕЕ ИЛИ, Выхол, Кпорых соединены с соответствмОшихи Вхолями элемента И - Н 1 62, выхо, которо;0 являтся Выхо;1 ОХ 1 68;1 ризнака рявенсВН 11 хлк 1 блока 1. Элемент 1 53 - 56 ВЫИ 01 нсны на ИС 131 ИПЗ, элемент 57 - ня ИС 531 ИП 4 э,1 смснты ИСК ЮЧАК)ШИЕ И 1 И:1 я 11 С 531 ,115. элемент И Н. Ня ИС 531,.А Ь,10 к х нря В.ения1111 2) рс 1 л 1 И 11,11: а на;1 Огн 0 известнОЙ сОВОг",1. иост и х ялов , правления. Дешифратор 40 може быть рса.изован посредством ПЗУ, которое сл жит лля того, чтобы на основании анализа кола номера текущего такта, результ ата сравнения мантисс, результата сравнения порялков, знаков входных чисел и старших разрядов мантисс входных чисел сформировать знак результата числа на выходе устройства, а также подать управл 5 НОцие сигналы на блоки устройства. Таким образом, чтобы закодировать ПЗУ лешифратора 40, необходимо лля всех возможных состояний его входов определить с помопью описания потяктовой работы ) гт 1529214ройства, приведенного далее, необходимые СОСТОЯНИЯ ВЫХОДОВ.Блок 10 управления работает следующим Обрззсм. При поступлении тактовых сигналов нз вход 17 устройства в младший разряд регистра 38 (сдвига) ззписывается 1 и на каж "ом последующем такте сдвигается. На выходе регистра 38 обргзуется позиционный код номера текущего тякта, который пода(тся на дешифратор 40.Дешифратор 40 анализирует этот код, результат на Выходе схемы 7 сравнения, знаки входных чисел старшие разряды мантисс входных Бисе 1, выход регистра 39 и вырабатывает упрапляюше сигналь Нз Выхолах 22- 36. Кроме того, он определяет знак резмльта гя. Следует отметит)ь что старшие разрядыяцтисс вместе со з аками порядков )сдаются на холы блокя 10, ЧТО ПО.)во;151( Т ПРО;1:)ВОЛИТЬ 3 Ц с 1 Л Из СЛЗя ) с- ВЕЦСТБЯ ОЛГВО и, СЛаГаЕМЫХ НУЛЮ 1 РЦ (ТРЦ ца гельном порялке другого слагаемо: с. Анализ производится в дешифрзт(,ре 40.51 ормалГЗятор 14 (фиг. 3) работзет ледуюц.им образом. На элеменге определяется наличие хотя бы одной единицы старших восьми разрядах мантиссы. Прц ес 25 наличии коммутатор 48 перелае; ца Выход код с шифратора 49, в противном случаес шифраторз 50. Арифметикс-логическй блок 11 мантисс (фиг. 4) работает слелхющим образом. Использоваа следующая заВисимость состояний Выходов ускоренного 30 переноса ст входных чисел гри операции А В. Есл) А)Б тс Р=1 и С)=-1 т. с. отсутствук)п условия как распростр: нецця, так и возникновения переноса, при А= Б Р=О и С)=0 присутствуют сбя эти хслвия, при А=-Р Р=-.0. С)=, т. е. имсются 35 условия распространения перенося, з ус(Овце возникновения псрепссз отсутствует. )Яким образом в слхчае равенства входных иссл значения Быхолоз Р и С) будут различны, в двух других случзях они буду( равны. ,Для Оп релсе(1 ен и 51 нера Бецс Гвя знзБн ий Р иони цолключ(цы к )сн)лм элс )енто 5 ИС);- : Ю 1 АЮ 1)1 ЕЕ И.111 58 61. Елцнццз ца выходе лобого из этих элементов оз)гзчает, ЧтО Ца БХОЛ( (ч)ОТБЕтстВХЮЦГЕГО СМУ аРИфметико-логического элемента поданы одинаковые числа. Ес.и на выходах ьсех элементов 5861 будут единицы, то на выходе элемента И - Н. 62 появится нуль - -признак равенства результата нулю.Устройство (фиг. 1) обрабатывает операнды, имеющие следующее представление. 50 Под знаком операнда понимается знак мантиссы. Стари ий разряд мантиссы (явнзя единица) всегда равен единице за исключением случая, ксглз операнд равен нулю. Отрицательная мантисса представляется в прямом коле. Старший разряд порядка является знаком порядка. Отрицательный порядок представляется В дополнительном коде. Перед началом вычислений операнды",стацавливзются цз ВХОД 2 х 1,2 хе. рсйстцз. Зятем нз ВхОд7 мстрсЙствя пол 1)стсч . к- ТОБЫЕ ИМЛУЛЬСЬ. ВЬЧ)СЛЕН 5( СХ ММЫ ЗЯНс Е тРИ тЯКтв Г 12 )Ес)ОМ ТЗКТС Ч БкОмммтятор 3 мянтисс по сигнал;5) с ь ХОЛОВ 22 и 23 б.10 КЗ 1 О Г 10 ЯЕТ МЗИТсгс П Е Р БОГО Ч И СЛ 2 Н Я И Н фс с) М сп (11. Си 1:. Ы й Ь Х( Л слвигателя 8. Второй коммутзтср 4 мзц с псдаег мантиссу Б.орсго числя нз коро ВхОд блока1. Блок . 0 сиГИЗ 1 ямц 5. Бь ХО. дов 34, 35 через коммутатор 12 кслз сльцгз подя, ня Лвцгзтел 8 цлеои слвигг. : Ня Бхо,.зх б ск; 11 хл 5, Ьссдвиц.ЫЕ ."ЯНТИССЬ. с Ь ПЕРВОМ ТЯКТС блок 10 сцгнзлами с Бьхолов 2 Г), 29 ззля- (.Т б.СКХ1 фН КПИ И:; - Б . ОЧ;) с". ОТ,)СТ Б КЯЧЕСТВЕ КОПЗ)ТОРЯ М а)1 ТЦСС.ЕЛ, 21 Тс 1 Т СРЗБ)Е 1)ИЯ МЯНТЦСС 0.1 РЕ,сЕ.)ЯСТ(5 ,) ЦЯЛЦ 11)О переполнения б.и)кз 11 ц рзненсту р з,;ья"з Бы)и Гс ) я н лк) и зз)с с)И 1 сз( т .я б с ке 10 ,).Г)явления. (я этом сьс тзлте блок,0 2 Н сГ (1 И 3 И с) М ЕП Е 5 Х .Ь Т 3 Т С П 3 Б Ц (. Ц с Ц11 С Р 5 Л К 0 Б на схеме 7 срявнсци); ц Бырзбзты;( Тс 1 КИС ) ц ПЗВЛЯСПИС ( И152 )Ы ця БьХС,.Х .) 7 н 2 кОМ",тат(,пы 5,пс)Я,1 кс. что ксм - мутатор 5 пс-яет на (1 срвый ьхсд Омс ьшцц поря,.ск, я комм Гятсп 6 ня гсПсй БХОЛ бпскс) 9 00.1 ЬЦЦЙ ПОПЯЛОК Блок 9 Выполняет фуцкцию А- В т. е. Из б 0.1 ьшеГО по)ялка Быс) итаРтся мс ь 1 с) ий. 11) В. Ором тя кте к)м мут 3 топ 3 1(1:тисе лс си" на(ям с Выходов слскз 10 2, ) 3 болз(т на слвигзтель 8 мантиссу числя с 5 еньпИх порядком цли, если попялки рав)-:ы, с хСньшей мантиссой. 1 хоммутзтс 1) 4 мантисс цо Дзс. ) с 1 цтисс .1) (гО )цс(1 с Н)1 п(1)ББхс.), О(10 к1. Разцйст)з порядков с Выхода блскз 9 через комм утао 1 .2 ксдз СЛВИЗ ПСЛЗЕТСЯ Цз Б "ОЛ ЗЯЛЗЦИЯ СЛБЦГЗ слВ 1. ЯтелЯ 8. (.,ДБ 15 Ятсхь 8 с:)БИИ 5 ст м)1 ц ) цсс) Вправо, цеслвцнутзя ". Слвц)х тая, зц-Ц(СЬ СКЛЗ 1 БзтТСЯ Е( 5 )ц 1;,БХ,) (ЦЫХ с)ИСЕ 0 (ИЦЯКОБЫ Ц 1 Ц Е)Ь 1 ЧЦ; 2 К)Т( 5: Б П)01 Ц Б:. НМ С 1 Х ЧЗЕ Ня б(СКС1. Пс) Ч(сц(с)я ця (С БЬХОЛС ЦЕНО)М З.ИЗСВ: ЦН)1 Я МЦТЦссс) ( М,: Зсц Ы 12(ТСЯ Б с с. Ц(1 Р1). 1 ХОХ М,с С и б -н к с ;с". 1 к) - с я 1 -0; )с с) ,с)0; 1 ч то ц и а пер Б о м тз кт е . Нз третьем тз-., Нормал)ззтср .4 с.р,- леляет, ца сколько нзло слцнль ц(цор М 2 ЛЦЗОВЗ)НМЮ 1 с 1 НТЦССХ В.1(ВО, Тобы Б СТс 11)- и:ем разряде былз е,1 цниця. 1(ер(з ком )- тятср 12 кл слв)1 Гя с )ыхсл;1 цсрм, ЛИЗятОра ПОЛЗЕтся Ня СЛБИГятЕЛЬ с(. Т;)К КЗК слсзиЗтель 8 слв Гает Бпрс)вс, 3 и Ис)1, - МЗ(1 И 32 ЦИ ": Х 21 ТИССТС и с)ЛС (,) БЦс)ТЬ Б(1 Е 150. Тс В жг тах, 5:Оелц н Яюццх Выход рс Г) стоя 1 3 с третьим и четвертым Бхслх 5 кс, мут- тора 3 мантисс ц Выход слвцгзтс,Я 8 с Бы холом 19 разрялов мцтцссы( тройстз, цроисхолит мсцтажцоизме Сцце ф 01 матя, старПие и млалц и( рззрялы:)омецяць мсс- таМИ. ЕСЛИ ЗНаКИ БХОЛЦЫХ:ЦС(Л РЗЗсЫС, т. Е. на втором такте блок 11 Выполнял фуцк 1529214цию ЛВ, то ненормализованная мантисса с регистра 13 через четвертый вход коммутатора 3 мантисс подается на сдвигатель 8, гле сдвигается влево и передается ца выход 19 устройства. При этом коммутгатор 5 порядков подает на первыи Вя)л блока 9 код сдвига мантиссы, в блоке 9 из большего порядка вычитается код сдвига и с его выхола вычисленный порядок результата передается на выхол 20 устройстВа.10Если знаки входных чисел равны, т. е.на втором акте блок 11 выполнял функцию А+В, то коммутатор 12 кода сдвига полает на управляющий вход сдвигателя 8 ноль и слвигатель 8 пропускает информацию не сдвигая, а большой порядок цредается через блок 9 на выход 20 устройства без изменений. Если при этом из блока 11 идет перенос, то с выхода регистра 13 ненормализованная мантисса податся ца вход сдвигателя 8 через третий вход коммутатора 3, на котором сделан монтажный сдвиг на один разряд вправо. Б Олоке 9 к гк)лысому порядку прибавляется слицица3)е)ультат пс релается на выход 20 устроьс гна ргИс 330 чец 3 е составляет случай, когда олцо из слагаемых равно нулю, а другое ихеет Отриательцый порялок. В этом случе мантисса игла с меньшим порядком подаеся 3 а первый Вход блока 11, а его порядок ца Второй Вя)Л блока 9. Коммутатор 12 30 кола;1 Б 1 га пола т на у 3 равляк)1 циЙ Вход слвигателя 8 кол все единицы, т. е. на Выя)ЛС с ЛВИГатЕЛя ПОяВ;ЕяЕтСя цуЛЕВОЕ ЧИСЛО.В агом ,1) ае независимо от фу 3 кцц Й ;)лона 11 ца его выходе будет ненулевая х 133 тисса. Она будет записана в ре гистр 13 и на третьем такте передана ца в 1 хол 19 устройства. Порядок 33 енйгеьч)го числа передается через олок 9 ца выходы 20 устройства. Т)к 3)3 Ооразом, в слуС 30 гКЕИИЯ НуЛЕВ 010 33311 С ЧИС.10 М ОТ 40 рццательцого порялка на ьчхоле устройства булл ч исло с отрицательным поря,комФор,гу)а изог)ре) енгг)гУстройство Лля суммироваци 5) Лвм; чисел 45плаВа к) щгЙ за ято Й, солг. р ж 1 цес 11)вь 1 Й и второй коммутаторы мантисс, первый и второй комму)аторы порядков, сдвигатель, арифметико.логический блок юрялков, блок управлсния, арифметико-логический блок мантисс, коммутатор кода слвига, регистр ман.тиссы и цормализатор, причем Входы разрядов мантиссы первого слагаемого устройсгва соединены с входами соответствующих разрядов первых информационных входов первого и второго коммутаторов мантисс.Входы разрядов мантиссы второго слагаемо 55 го устройства соединены с входами соответствующих разрядов второго информационного входа первого коммутатора мантисс Вьход которого соединен с информационным входом слвигателя, выход которого является выходом разрядов мантиссы выхо. ла суммы устройства, входы разрядов порядКа ВХОЛа ПЕРВОГО СЛаГаЕМОСС УСтРОйетаа СОЕ- динены с входами соответствующих разрядов первого информац 303 с 1 го входа первого коммутатора порядков, Выход которого соединен с первым информационным Входом арифметико-логического блока порядков. выход которого является выходом разрядов цорялка выхода суммы устройства н соединен с первым информационным входом коммутатора кола сдвига, Выход которого сс)елицен с входом задания величины сдвига слвигателя, входы разря,ов порядка входа Второго слагаемого устройства соединены с Входами соответствую цих разрядов первого информационного вхола второго коммугатора порядков, выход которого соединенвторым информационным Входом ариф е) ико-логи ес кого блока порядков. входы разрялов знаков первого и второго сла:а- СМЫХ УСТРОЙСТВа СОСЛ 3131111 Ы СООТВСТСТВС 1 НО с первым и в горм Входами условий 6.3)- ка управления, тактовый Вход которого соединен с тактовым входом устройства, выкал второго коммутатора мантисс соединен с первым информационным Входом арифмет)ко-гн)3 ц еского блока мацтисс, Выход резултата которого сослицен с ицф)орг)а 1 ио 3- :Ым входом рсгистра мантиссы, Выход коО- рого сослицец с входом цормализатора, ВыХОЛ КОТОРОГО СОЕЛИЦс Н С ВТОРЫМИ ИпфоР- ма:1 цоц ными Входами первогс) комм;тагора 310 р 5 лков и ком хх та тора к)ла с;1 В и г 1, В 1. х Ол ы и с 1) с и Ол ц е ц и я и ц р и 3 ц а к а ,) а Ве 3. с т В а 33 улк) ар 3 фметико-,О ичсск 010 блока х)а 3- гисс соединены соответственно с третьим и Ест вертым Вхо,1 ами )с.оеий ОлОКВ ,Г)рав - ,ения, с 3 ерзого цо иестпалцатый Выхо;1 ы кот)роо соедице: ы сс)е)твстствен 30 с Вья)лом разряда знака выхоа суммы хстройст)а, с первьм и Вторым х прав.як)- 3 Ех)и входами первого комл хтатс)р 3 мацисс, с, п 1)а 1 151 к)п 113 м Вхоло, ВТОРОком) а. тора мантисс, с цсрвым и вторым х црав.яюци м и В хо;1 ам и перво го ко) м утато;) а поря Л- ко в, с х цра Вля к) щим входом Второп кох 1 м мтатора порядков, с Входами зедания )- жима и переноса арифметико-логического блока мантисс с Вхолами с первс)го цо четвертый задания режима арифметикгг-лог;еского блока цорялков, с пер:)ым и В)орым управляю)ними вхолами коммутатора кола слвига и с входом разрешения записи регистра мантиссы, отличающееся тем, что с целью повышения точности результата при сложении числа, имеющего отрицательный порядок, с нулевым числом, оно содержит схему сравнения порядков, причем Вя)ды старших разрядов мантисс входов перВого и второго слагаемых устройства соелинены соответственно с пятым и шестым Входами условий блока управления, входыразрядов мантиссы входа второго слагаемого устройства соединены с входами соответствующих разрядов второго информационного входа второго коммутатора мантисс, входы разрядов порядка входа первого слагаемого устройства соединены с входами соответствующих разрядов второго информационного входа второго коммутатора порядков и первого входа схемы сравнения по рядков, выход которой соединен с седьмым входом условий блока управления, входы разрядов порядка входа второго слагаемого устройства соединены с входами соответствующих разрядов третьего информационного входа первого коммутатора порядков и второго входа схемы сравнения порядков,выход сдвигателя соединен с вторым информационным в.,одом рифмегко-логического блока мантсс. выход (К) -го разряда регтра мантиссы соеди нен с входом 1 и - К+ ) -го разряда третьего нформационного входа первого коммутатора мантиссс, выход К-го разряда (К=1 п,п разрядность слагаемого) регистра мантиссы соединен с входом (иК+ )-го разряда четвертого информационного входа первого коммутатора мантисс, третий и четвертый информационные входы коммутатора кода сдвига соединены соответствено с входами логического нуля и огической единицы устройства.О Б А Вр Вз 6, р КакснКорр11 од ии открытяя на 6., иг. х жгород. оставитель Лред И, Всресж бб 8о изобретени35, Рауиискнат Патг нт сктор 0.11 ипаеснос и при ГКНТ ССС Сие ного комитета иМосква, Ж - тедьский комби Со Ар А 4 ,4 з Во Вг А 4 4 з Ва Редактор О сиЗаказ 7542;44ВН ИИ 11 И Государстве1130311 роизнодственно.изд

СмотретьЗаявка

4376499, 08.02.1988

ПРЕДПРИЯТИЕ ПЯ А-1081

КАЛИНИН ЭДУАРД КАЗИМИРОВИЧ, САВРАН ГЕОРГИЙ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/50

Метки: двух, запятой, плавающей, суммирования, чисел

Опубликовано: 15.12.1989

Код ссылки

<a href="https://patents.su/7-1529214-ustrojjstvo-dlya-summirovaniya-dvukh-chisel-s-plavayushhejj-zapyatojj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для суммирования двух чисел с плавающей запятой</a>

Предыдущий патент: Устройство для арифметической обработки элементов конечного поля

Следующий патент: Устройство для умножения

Случайный патент: Устройство для контроля случайных дефектов рисунка фотошаблона