Устройство интерполяции для отображения графической информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

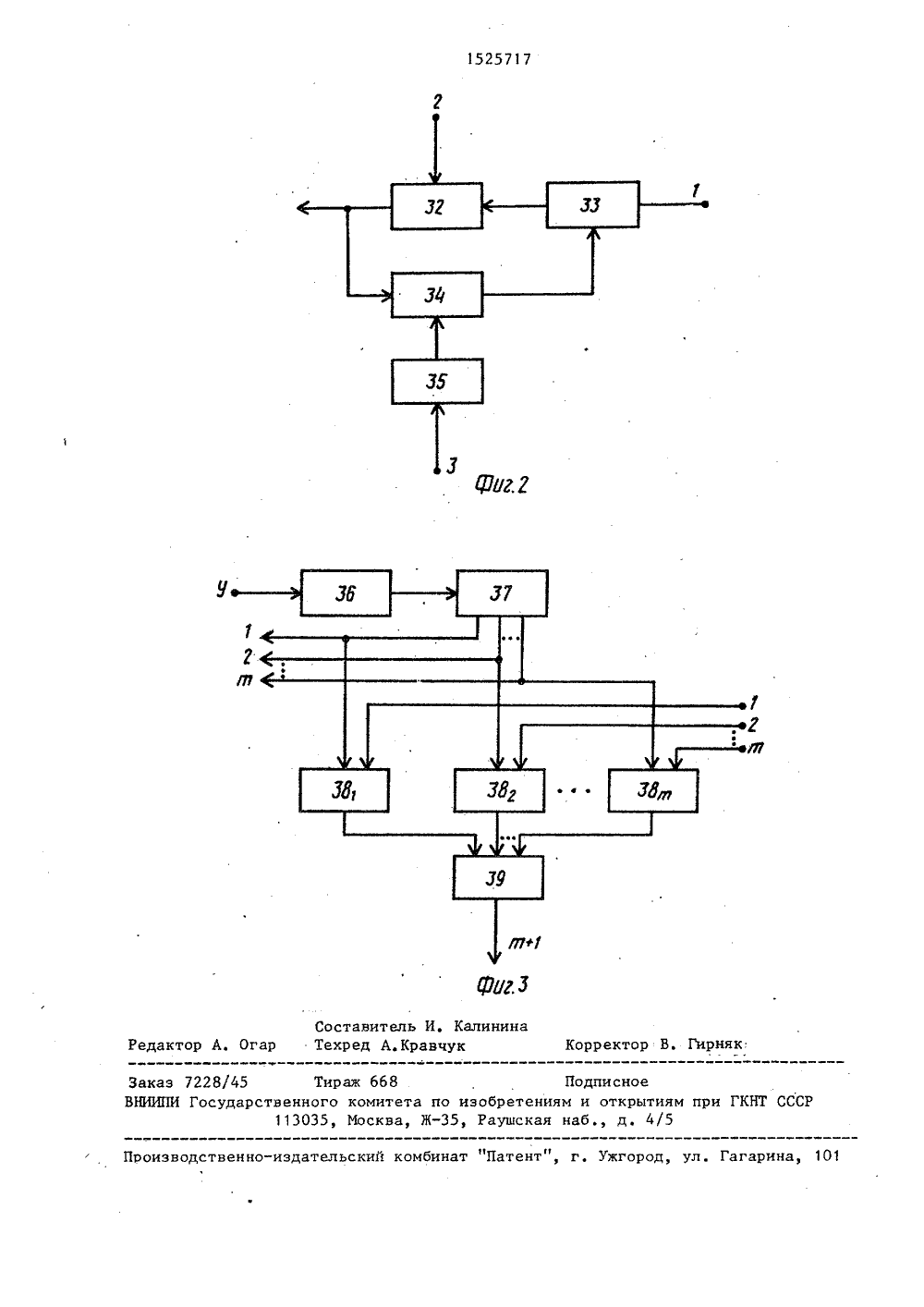

1525717 ния за счет устранения геометрических и яркостных искажений при егопреобразовании Устройство содержитчетыре элемента 1, 6, 19, 22 задержки, пять блоков 2, 15, 21, 25, 27памяти, два коммутатора 3, 26, блок.4 коммутаторов, два блока 5, 16 вы,читания, генератор 7 тактовых имИзобретение относится к вычислительной технике и может быть использовано для геометрических преобразований циФровых иэображений, получаемых с помощью оптико-электронных приборов с конической разверткой пространства предметов.Цель изобретения - повьппение качества изображения за счет устранения геометрических и яркостных искажений при его преобразовании. 25На Лиг.1 приведена Функциональная схема устройства; на фиг.2 - схема кольцевого регистра; на Ьиг,З - схема второго коммутатора.Устройство содержит (Лиг.1) первый элемент 1 задержки, первый блок .2 памяти, первый коммутатор 3, блок 4 коммутаторов, первый блок 5 вычитания, второй элемент 6 задержки, генератор 7 тактовых импульсов, счет,чик 8, схему 9 сравнения, первый умножитель 10, первый сумматор 11, эле,мент ИЛИ 12, первый 13 и второй 14 сдвиговые регистры, второй блок 15; памяти, второй блок 16 вычитания, 40 параллельный регистр 17, второй умно- житель 18, третий элемент 19 задержки, второй сумматор 20, третий блок 21 памяти, четвертый элемент 22 задержки, триггер 23, элемент И 24, четвертый блок 25 памяти, второй коммутатор 26, пятый блок 27 памяти, кольцевой счетчик 28, дешифратор 29, кольцевые регистры 30 и ключи 31,Кольцевой резистор (Фиг.2) обра.зуют сдвиговый регистр 32, элемент ИЛИ 33, элемент И 34 и элемент НЕ 35.Коммутатор 26 (иг.З) включает счетчик 36, дешифратор 37, элементы И 38 и элемент ИЛИ 39.Элемент 1 задержки имеет время за 55 держки, равное периоду следования видеосигналов Ь 1. Элемент 6 задержки имеет время задержки, равное врепульсов, счетчик 8, схему 9 сравнения два умножителя 10, 18, два сумматора 11, 20, элемент ИЛИ 12, двасдвиговых регистра 13, 14, регистр17, триггер 23, элемент И 24, кольцевой счетчик 28, дешифратор 29,кольцевые регистры 30, ключи -31,3 ил,мени обработки видеосигналов в блоках 5 и 10. Элемент 22 задержки имеет время задержки, кратное периоду следования строчных синхроимпульсов Т,; - (ш -1)Т элемент 19 задержки имеет время задержки, равное времени обработки видеосигналов в блоках 16 и 18. Блоки 15, 21 и 27 памяти выполнены циклическими, что обеспечивает многократное последовательное считывание записанных в них предварительно массивов Б;, К 6соответст 1венно. Дпя предварительной записи указанных массивов блоки 15, 21 и 27 имеют специальный вход (на Лиг.1 не показан). Сдвиговый регистр 13 содержит два связанных последовательных регистра. При этом первый выход сдвигового регистра 13 соединен с разрядами целой части чисЛа, записанного в первый регистр. Второй выход сдвигового регистра 13 связан с разрядами дробной части числа, записанного во второй регистр. Сдвиговый регистр 14 состоит из (и+1) регистров. Первым входом сдвигового регистра 14 является вход его первого регистра. Выходом сдвигового регистра 14 является выход его последнего регистра, Сдвиговый регистр 32 содержит и регистров. Емкость счетчика 36 равна ш. Элемент ИЛИ 39 имеет ш входов. Кольцевые регистры 30 имеют емкость равную И , причем выходы блока 30 соединены с соответствующими входами второго коммутатора 26. Значение ш определяется на единицу большим, чем число строк выходного изображения, которые содержат информацию одного скана оптико-электронного прибора. Максимальное значение счетчика 28 равно (ш), Признак соответствия текущего преобразованного по строке и по кадру отсчета номеру строки выходного изображения, выставленно,где Е- расстояние от центра проектарования до плоскости предметов;- картинное расстояние; - коэффициент использованияразвертки;а, аа 22 ааэ =а з 2 аЗ а 1 а 21 А 1 - матрица повоРотов ОЭП получим значение преобразованноговидеосигнала Вк , оторегистрацияткоторого значительно проще, чем исходного. Поэтому преобразованное попредлагаемому алгоритму и зарегистрированное иэображение свободно отгеометрических и яркостных искажений,присущих исходному изображению.Устройство работает следующим образом.В исходном состоянии в блоке 2поочередно записан исходный фрагментизображения, Счетчики 8 и 28 обнулены. Коммутаторы 3 и 26 и блок 4 закрыты. Генератор 7 тактовых импульсовотключен, сдвиговые регистры 13 и 14,регистр 17 и кольцевые регистры 30обнулены. В блоке 15 записан массивиз и значений Ч . В блоке 21 записан35массив из п значений К . В блоке 271записан массив из и значений Ь;,При включении блока 2 на воспроизведение с его выхода построчно последовательно поэлементно на входкоммутатора 3 поступают цифровые видеосигналы с частотой Г з = 1 41 аС второго выхода блока 2 строчныесинхроимпульсы поступают через элемент 22 задержки на вход триггера 4523, на второй вход элемента И 24, навход генератора 7 тактовых импульсов, который запускается для Формирования и импульсов с частотойблагодаря чему обеспечивается переза 50пись строки обработанного изображения,из коммутатора 2 б в блок 25,на первыйвход элементаИЛИ 12,с выходакоторогоони поступают на управляющий входблока 15 обеспечивая этим считываФ55ние из блока 15 и запись через пер -вый вход сдвигового регистра 13 в егопервый регистр значения И;, Выходные импульсы генератора 7 тактовых импульсов поступают на вход счетчика 8, который подсчитывает количество поступивших импульсовна вторые входы кольцевых регистров 30, обеспечивая сдвиг записанных там значений обработанного видеосигнала, на второй вход сдвигового регистра 14, обес= печивая задержку видеосигнала на период следования строки, и на вход блока 27 памяти, благодаря чему осуществляется синхронизация поступления отсчета на входы ключей 31 и считывания признаков соответствия Ь; из блока 27. С выхода счетчика 8 текущее значение числа импульсов постоянно гоступает на первый вход схемы 9 сравнения, на второй вход которой поступает значение целой части хп 1(И;) числа, записанного в первый регистр сдвигового регистра 13 с первого выхода этого регистра. При равенстве значений на обоих входах схемы 9 сравнения на первом и втором выходах последней формируются управляющие импульсы различной длительности. При этом на первом выходе формируется управляющий импульс, равный по длительности 2/Г ,т.е. равЬф а и ный периоду следования двух видеосигналов. На втором выходе Формируется импульс половинной длительности, т.е,равный длительности периода следования одного видеосигнала. С первого выхода схемы 9 сравнения импульс поступает на управляющий вход коммутатора 3 и открывает его на время длительности управляющего импульса, т.е. на время периода следования двух видеосигналов (-го и (х+1)-го), С выхода открытого ключа 31 видеосигналы Ви В; 1 последовательно поступают на первый вход блока 4, С второго выхода схемы 9 сравнения импульс поступает на вторые входы блока 4 и элемента ИЛИ 12 и на управляющие входы сдвигового регистра 13 и блока 21, обеспечивая считывание и запись очередного -го значения коэ 3 ициента К в регистр 17. Управляющий импульс также обеспечивает сдвиг на один элемент содержимого сдвигового регистра 13, т.е. перезапись числа 11, с его первого регистра во второй. С выхода элемента ИЛИ 12 импульс поступает .на управляющий вход блока 15, благодаря чему очередное значение - число И; 1 - считывается из блока 15 и записывается9 15в первый регистр сдвигового регистра13. Происходит поступление управляющего импульса на второй вход блока 4,а второго видеосигнала Вна втой + 3рой выход блока 4. С.первого выходаблока 4 Б;-й видеосигнал через элементзадержки, задерживающий напериод следования видеосигнала 5 Ф,поступает через элемент б задержки,в котором задерживается на времяобработки видеосигналов в блоках 5и 10, на первый вход сумматора 11 ина первый вход блока 5 вычитания одновременно с поступлением на еговторой вход М-го видеосигнала,+вычитания поступает на первый входумножителя 10, на второй вход которого поступает дробная часть числаИ ,т.е. коэФициент К , с второговыхода сдвигового регистра 13. Выходной сигнал (В , , -В ) К у УмН , 1ножителя 10 поступает на второй входсумматора 11, где суммируется с соответствующим значением В 1 С выхо 1да сумматора 11 частично Ьбработанный видеосигнал В , поступает неУ,посредственно на первый вход блока16 вычитания и через регистр 14, вкотором задерживается на время периода следования строчных синхроим-пульсов, т.е. на период следованиястрок изображения, на второй входблока 16 вычитания, в котором вычисляется значение (В, . - В у , )1+1и через элемент 19 задержки, где задерживается на время обработки видеосигналов в блоках "16 и 18, и навторой вход сумматора 20, С выходаблока 16 вычитания видеосигнал(В ,. - . В , , ) поступает на первый вход умножителя 18, на второйвход которого с выхода регистра 17.поступает -е значение коэАЬициентаК . Выходной сигнал (В. .1 фВ) К, умножителя 18 поступает1на второй вход сумматора 20, где суммируется с соответствующим значениемВ,1,. С выхода сумматора 20 обрабо 1танный видеосигнал В 1; поступает)на входы ключей 31. Код номера строки выходного изображения, соответствующий текущему значению обработанного видеосигнала, формируется всчетчике 28 на основе поступающегона его вход значения Ь, и текущего.,значения счетчика 28 и поступает навход дешиФратора 29, где преобразу 25717 10 10 15 20 25 30 35 40 45 50 55 ется в позиционный код, Значение "1"на )-м выходе, который соответствует номеру строки выходного изображения, деширатора 29 открывает соответствующий ключ 31 и обеспечиваетпрохождение и запись преобразованного видеосигнала в 1-й кольцевой регистр 30. Поступивший видеосигналзаписывается в первую ячейку регистра 30и перемещается по регистру30 со скоростью поступления импуль-сов из генератора 7 тактовых импульсов, Последняя ячейка регистра 30соединена с 1-м входом коммутатора26, поэтому видеосигнал, поступившийв 1-й регистр 30 задерживается на(-К) периодов сканирования, где К -номер текущей обработанной дуговойстроки исходного изображения, Такимобразом, регистры 30 обеспечиваютАормирование строки выходного изображения максимум за (ш).периодовсканирования, После записи первойдуговой строки в регистры 30.-30производится считывание первой строки выходного линейно-строчного изображения из регистра ЗО,. Считываниеначинается после прихода синхроимпульса очередной строки, который пос-.тупает на второй вход элемента И 24.Синхроимпульс первой строки, пройдя элемент 22 задержки, опрокидывает триггер 23, значение "1" на выхо-де которого после этого постояннопоступает на первый вход элементаИ 24, Поэтому очередной синхроимпульс, поступивший на второй входэлемента И 24, проходит через него ипоступает.на управляющий вход комму"татора 26, который в этом случае соединяет свой первый вход со своим выходом и подает на третий вход первого кольцевого регистра 30 сигнал"1", Благодаря этому обеспечиваетсясчитывание содержимого именно с выхода первого кольцевого регистра 301.Во время считывания первой строки выходного изображения происходит распределение видеосигналов ш-й дуговойстроки в регистры ЗО -30 , Послезаписи ш-й дуговой строки с приходомочередного синхроимпульса строкина выходе элемента И 24 образуется"1" и коммутатор 26 соединяет второйвход со своим выходом, а также обес,печивает аналогично ранее описанному режиму работы считывание обработанных видеосигналов из второго5717 12 11 152кольцевого регистра (с его выхода),Во время считывания второй строкиобработанного иэображения происходитраспределение (ш+1)-й дуговой строки входного изображения по регистрам305-30 э 30 4 и т,д,Формула из обр етения 510 динен с первым входом второго блока вычитания, выход которого соединен спервым входом второго блока умножения и с информационным входом треть-его элемента задержки, выход которого соединен с первым входом второгосумматора, информационный выход чет-,вертого блока памяти соединен с входом регистра, выход которого соединенУстройство интерполяции для отобр аж ения гр афической информации, со, держащее первый блок памяти, вход которого является информационным , входом устройства, первый выход сое,.динен с информационным входом первого коммутатора, выход запускающих : импульсов устройства соединен с входом запуска генератора тактовых им пульсов, с первым входом элемента ИЛИ , и входом второго блока памяти, выход генератора тактовых импульсов соеди, нен со счетным входом счетчика, выход счетчика соединен с первым входом схемы сравнения, выход третьего блока памяти соединен с.входом первого сдвигового регистра, первый выход которого соединен с вторым входом схемы сравнения, второй выход которой соединен с первым входом первого умножителя, первый выход схемы сравнения соединен с управляющим входом первого коммутатора, второй выход схемы сравнения соединен с управляющим входом. блока коммутаторов, вторым входом элемента ИЛИ, с управляющим входом первого. сдвигового регистра и с управляющим входом четвертого блока памяти, выход элемента ИЛИ соединен с входам третьего блока памяти, выход первого коммутатора соединен с инФормационным входом блока коммутаторов, первый выход блока коммутаторов соединен с входом первого элемента задержки, второй выход блока коммутаторов соединен с первым входом первого блока вычитания, выход первого элемента задержки соединен с вторым входом первого блока вычитания и с входом второго элемента задержки, выход перво - го блока вычитания соединен с вторым входом первого блока умножения, выход первого блока умножения соединен с первым входом первого сумматора, выход второго элемента задержки соединен с вторым входом первого сумматора, выход первого сумматора сае 25 30 35 40 45 50 55 с вторым входом второго умножителя,выход которого соединен с вторымвходом второго сумматора, о т л и -ч а ю щ е е с я тем, что, с цельюповышения качества изображения засчет устранения геометрических и яркостных искажений, в него введенывторой сдвиговый регистр, четвертыйэлемент задержки, триггер, элементИ, второй коммутатор, пятый блок па-.мяти, кольцевой счетчик, дешифратор,ш-ключей, ш-кольцевых регистров, где ш = а+1, а - число строк выходногоизображения, причем выход генератора тактовых импульсов соединен с тактовым входом второго сдвигового регистра, с управляющим входом пятогоблока памяти и тактовыми входами школьцевых регистров, выход запускающих импульсов первого блока памятисоединен с входом четвертого. элемента задержки и первым входом элемента И, выход четвертого элемента задержки соединен с входом триггера,выход которого соединен с вторым входом элемента И, выход элемента Исоединен с входом второго коммутатора, выход которого соединен с входомвторого блоха памяти, выходы группы второго коммутатора соединены с управляющими входами ш кольцевых регистров,информационные выходы которых соединены с входами второго коммутатора,выход пятого блока памяти соединенс входом кольцевого счетчика, выходкоторого соединен с входом дешифратора, выходы дешифратора соединеныс управляющими входами ш ключей, информационный выход второго сумматора соединен с информационными входамиш ключей, выходы ш ключей соединеныс входами ш кольцевых регистров, выход первого сумматора соединен синформационным входом второго сдвиговаго регистра, выход второго сдвиговага регистра соединен с входомвторого блока вычитания и вторымвходом третьего элемента задержки./4 6 судар Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарин ЗаказВНИИПИ Составитель И, Калинин Техред А.Кравчук енного комитета по изо 13035, Москва, Ж, Р Подписноеениям и открытиям при ГКНТ СССРкая наб., д, 4/5

СмотретьЗаявка

4402128, 25.01.1988

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

ИВАНЧЕНКО ВАДИМ ИВАНОВИЧ, БАТРАКОВ АНАТОЛИЙ СЕМЕНОВИЧ, ГАВЕНКО ВИКТОР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06T 3/00

Метки: графической, интерполяции, информации, отображения

Опубликовано: 30.11.1989

Код ссылки

<a href="https://patents.su/7-1525717-ustrojjstvo-interpolyacii-dlya-otobrazheniya-graficheskojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство интерполяции для отображения графической информации</a>

Предыдущий патент: Многоканальный цифровой интерполирующий фильтр для частотного уплотнения каналов

Следующий патент: Устройство для селекции изображений объектов

Случайный патент: Устройство для определения амплитудных характеристик случайных процессов