Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 693377

Авторы: Калмыков, Кириченко, Левков, Линчевский, Сычев

Текст

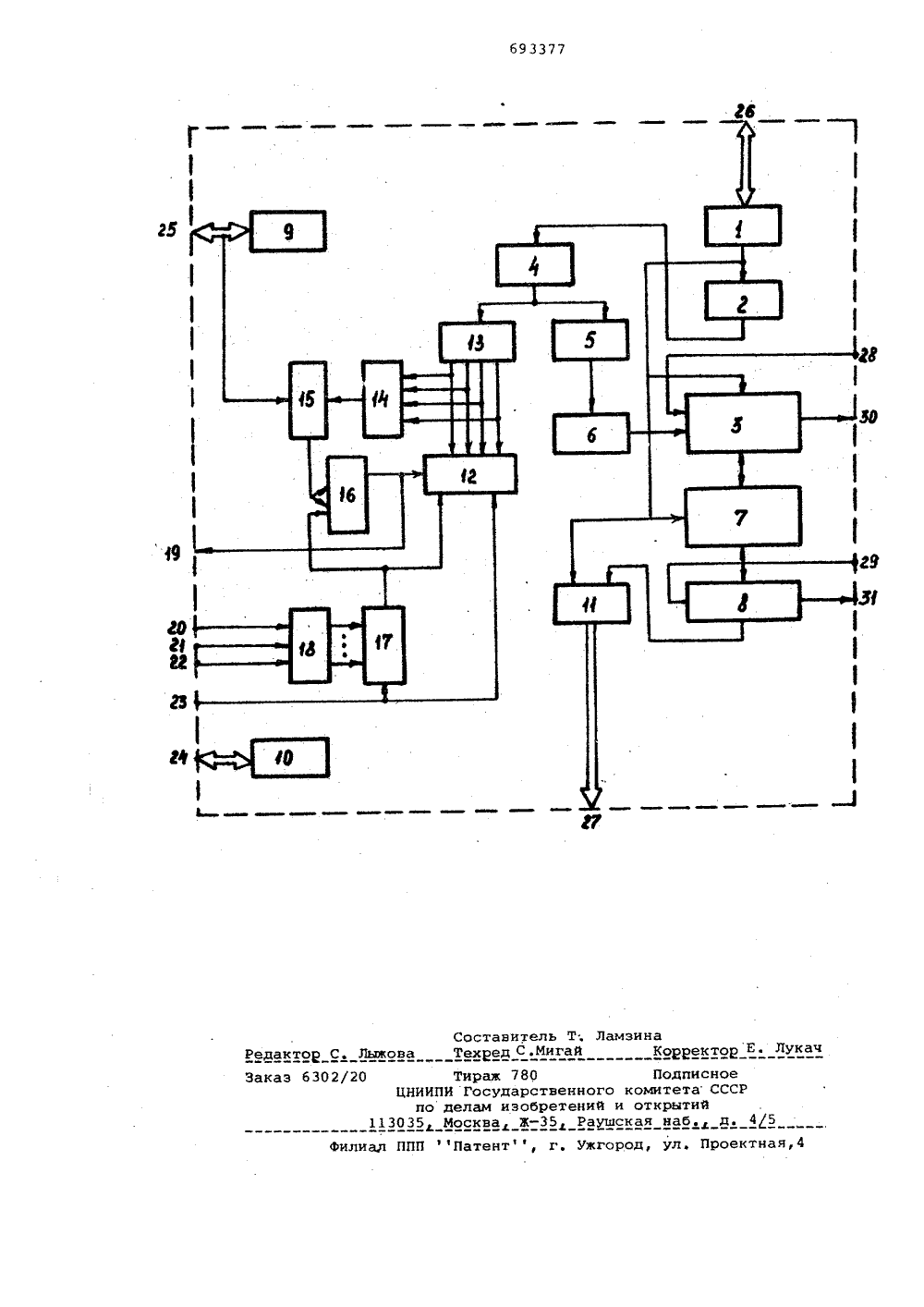

(22) Зайвлено 0,404.77 (21) 2472550/18-"24с присоединением заявки Йо(51)М. Кл.2 С Об Р 15/00 Государственный комитет СССР по делам изобретений. и открытий(54) МИКРОПРОЦЕССОР Изобретение относится к области вычислительной техники и может быть использовано при создании больших интегральных схем (БИС), предназначенных для построения вычислительных и управляющих систем.Известны микропроцессоры, содержащие арифметическо-логическое устройство, блок регистров, устройство управления, соединенные между собой, а также входные и выходные шины переноса, и предназначенные для построе- ния многоразрядных вычислительных систем 1) .Недостаток подобного микропроцес сора - имеющаяся избыточность при построении вычислительных систем, возникающая из-за Функциональной незаконченности микропроцессора, а именно: устройство управления вычис лительной системой на основе такого микропроцессора реализуется или на основе специальных БИС, или на основе малых интегральных схем.Наиболее близким к изобретению по технической сущности и достигаемым результатам является микропроцессор, содержащий блок управления вводом-выводом данных,-регистр команд, арифметическо-логическое уст- ЗО ройство, дешифратор и шифратор команд, регистр управления, блок регис ров, Формирователь приращений,устройство синхронизации и устройство управления циклом памяти, адресный регистр, выход которого является выходной шиной адреса, а первыйвход адресного регистра соединен спервым выходом Формирователя приращений, причем ввод-вывод блока управления вводом-выводом данных соединен с шиной данных, а его выходсоединен со вторым входом адресногорегистра, первым входом арифметико-логнческого устройства, входомблока регистров и входом регистракоманд, выход которого соединен через дешифратор и шифратор командсо входом регистра управления, соединенным своим выходом со вторымвходом арифметическо-логическогоустройства, вход-выход которого соединен с входом-выходом блока регистров, вход-выход которого соединенс входом-выходом Формирователя приращений, третий вход арифметическологического устройства является первым входом переносов микропроцессора, вход Формирователя приращенийявляется вторым входом гереносовмикропроцессора, выход арифметическологического устройства является пе:;. -вым вьгходом переносов микропроцесс.ара, а второй выход Формирователя приращений является вторым Выходом переносов микропроцессора Выход деееифратора команд соединен со Входом ееифратора групп команд 21,Недостатки этого микрог:роцессорапотеря быстродействия при Обработкеслов больше двойной длины и сложностьсоздания Вычислительных систем г:риаппаратногм наращивании разрядности.,Все это приводит к ограничениюФункциональных Возможностей микропроцессора и снижению его быстродействияЦелью изобретеш.я является расши-рение функциональных ВозможностеймикрОЕЕРОцессора за счет Введени 5 е ДОполнительного блока и соотвечствутющгехсВязей В тактирующее устройство атакже повышение быстродействия микропроцессора на этой Основе,Поставленная цепь достигается тем,.что тактирующее устройстВО Выполне-.но в виде распределителя длительноститактов, Введены элементы И и ИЛИ,триггер, кодопреобразсватель, счетчеиесФОРМИРОВанИЯ ЦЛИтЕЛ=,НОСти таКтовгруппа ВхОдОВ котОрого соединена сгруппой Выходов кодопреобразаэателя,дополнительный Вход счетчика соедеененс Внешним Входом управления микро-.процессора и ттервит Входом распределителя длительности тактОВ, а егоВЫход подключен ко Второму Входу распределителя длительности "актОВ иодному из счетных входов триггера,дРугой вход триггера соединен с Выходом элемента И первый вход которого соединен с выходом элемента ИЛИ,а второй вход соединен с Выходом устройства синхрОниэации, группа выходов шифратора групп команд соедитте"на с группой Входов элемента ИЛИи с группой Входов расптэецелителяДЛИТЕЛЬЕЕОСТИ ТаКтов, ДОГЕОЛЕтитс:ЛЬНЫЙВХОД РаСПРЕДЕЛИТЕЛЯ ДЛИТЕЛЬНОС.ТНтактов соединен с Выходом триг 1 ераи выходом микропропессора еевляю.щимся выходом управления синхронизацией, группа Входов кодопреобразователя является группой Входов мтекро-процессора, на которые принимаетсякод длительности такта,На чертеже представлена блок-схема микропроцессора.Микропроцессор содержит блок 1управления Вводом-выводом данных,регистр 2 команд, арифметическо-логическое устройство 3., дешифратор4 и шифратор 5 команд, регистр 6управления, блок 7 регистров, Формирователь 8 прираецений устройство 9 синхронизации, устройство 10управления циклом памяти адресныйрегистр 11, тактирующее устройство 12 Вьвчоеененное В Виде распреде,ееителя длительности тактов, шифратор 13 групп команд, элемент ИЛИ 14,элемент И 15, триггер 16, счетчик17 формирования длительности тактов,кодопреобразователь 18, выход 19управления синхронизацией, группаВходов 20-22 кодопреобразователя,Внешний вход 23 управления микропроцессором, шины 24, 25 управлениямикропроцессором, шину 26 данных, ши,п ну 27 адреса, входы 28,29 и выходы30,31 переьосов арифметическо-логического устройства 3 и Формирователя приращений 8.Мина 26 данных подключена к блокууправления вводом-выводом данных,соединенному по выходу с регистром 2команды арифметическо-логическимустройством 3, блоком 7 регистрови адресным регистром 11, другой входкоторого соединен с Формирователем8 приращений, а выход подключен кшине 27 адреса, Регистр 2 командысоединен через дешифратор 4 командыс: шифратором 13 групп команд и шифратором 5 команды, выход которогочерез регистр 6 управления соединенс арифметическо-логическим устройством 3, Группа выходов шифратора 13групп команд соединена с группойВходов тактирующего устройства 12и со входами элемента ИЛИ 14, выход3,которого соединен с первым входомэлемента И 15, второй вход которогосоединен с выходом устройства 9синхронизации, выход элемента И 15З 5 соединен со счетным входом триггера.6. Выход которого соединен с выходом 19 микропроцессора, являющимся Выходом управления синхронизацией, и дополнительным управляющим4 О Входом тактирующего устройства 12,Второй Вход которого соединен с установочным Входом триггера 16 и с выходом счетчика 17 Формирования длительности тактов. К установочнымвходам счетчика 17 подключены выходыкодопреобразователя 18, группа входов 20-22 которого является входамимикропроцессора. Внешний вход 23 управления микропроцессором соединенсо счетными Входами тактирующегоустрой тва 12 и с дополнительным вхоДОМ СЧЕтЧИка 17 формирования длительности тактов, при этом входы и выходы переносов арифметическо-логического устройства 3 и формирователя8 приращений соединены соответственНО со входами 28, 29 и выходами 30,31 переносов микропроцессора.Устройство работает следующим образом.60 Коды Операций, выполняемых в микропроцессоре, сгруппированы такимОбразом что каждой группе соответСТВУЕт ОДИН таКт, В КОТОРОМ ФОРМИруется сигнал переноса, а команды,65 В которых не формируется сигнал пе 693377реноса, вообще не вырабатывают управляющих сигналов на выходе шйфратора 13 групп команд, Достигается это тем, что соответствующие этим операциям выходы дешифратора 4 не подсоединены ко входам шифратора 13.При наращивании разрядности вычислительного устройства аппаратным способом на основе БИС возникают задержки в формировании сигналов переноса, величина которых зависит от местояа хождения кристалла БИС, от места начала их формирования.В изобретение длительность такта формирующего сигнала переноса изменяется в зависимости от величины15 этих задержек аппаратным способом.Длительность такта зависит от кода, постоянно подаваемого на группу входов 20-22 кодопреобразователя 18, выход которого определяет код допол" нения, вносимого в счетчик 17, при этом цля устройств, обрабатывающих старшие разряды слов, этот код равен 000 (максимальная длительность такта), а для младших разрядов - код 1111 (минималь ная длительность) . Для промежуточных положений микропроцессора величина длительности такта определяется кодами от 000 до 1111 ф,Формирование длительности произ водится следующим образом.При поступлении на вход устройства по шине 26 данных кода команды через блок 1 в цикле команды в регистр 2 команд записывается код 35 команды, подлежащей исполнению, который поступает на вход дешифратора 4 команды, на выходе которого воз- , буждается одна иэ шин.Сигнал по этой шине поступает на вход шифраторов 13 и 5. Выходной код шифратора 5 поступает на регистр 6 управления, выходы которого управляют работой устройства 3, блока 7 и формирователя 8 приращений, а также формируют или принимают сигналы управления памятью и шинами в устройствах 9 и 10, Если же на вход микропроцессора поступает команда, выполнение которой предполагает формирование сигналов переноса в одном иэ тактов, то на соответствующем выходе шифратора 13 вырабатывается сигнал, который поступает на вход тактирующего устройства 12 и через элемент ИЛИ 14 на один из 55 входов элемента И 15, на другой вход которого поступает сигнал признака выборки кода операции команды из шины 25 управления. По заднему фронту сигнала признака цикла триггер 16 Щ устанавливается в единичное состояние, переключая выходным сигналом тактирующее устройство 1.2 в режим формирования удлиненного такта, определяющего перенос в данной операции, 65 При этом выходной сигнал триггера 16сформируется также на выходе 19 управления синхронизацией, Этот сигналможет быть использован микропроцес-.сором (его секциями) при обработкемладших разрядов слов, как сигналЗапрос шиныфф, переводящий адресныешины и шины данных в высокоимпедансноесостояние,а указанные секций микропроцессора в состояние ожидания. Длительность такта переноса определяется выходным сигналом переноса счетчика 17, который по установочному входуустанавливает триггер 16 в нулевоесостояние и переводит тактирующееустройство 12 в режим Формированиятактов номинальной длительности. Нулевой сигнал на выходе 19 переводитмладшие секции микропроцессора в режим синхронного выбора следующегокода операции. При поступлении на входустройства кода команды, выполнениекоторой не предполагает Формированиесигналов переноса, на выходе шифратора 13 не возбуждается ни один изуправляющих сигналов и переключениережима тактирующего устройства 12не происходит.Изменение тактовой сетки не производится также в цикле выбора команды, т.е. в этих случаях производится обработка информации параллельно и одновременно каждой секциеймикропроцессора.Суммарное время выполнения команды в многоразрядном микропроцессоре, синтезированном на известныхустройствах, равноТ + (и - 1)Т,а в изобретении(в)Т+ -- Т 1т,е. быстродействие вычислительнойсистемы, использующей изобретение,повышается в К раз, где равноТ+ (-4 1 1 4.)1 11-4)т+ + т и+згде и - число секций микропроцес"сора, используемых для наращивания разрядности;Т - цикл микропроцессора.Таким образом, предложенное изобретение позволяет повысить быстродействие вычислительной системы, синтезированной на основе данного микропроцессора, за счет возможности аппаратно регулировать длительность тактов, в которых возникают сигналы переноса, а также расширить функциональные возможности за счет аппаратного наращивания разрядности.Формула изобретенияМикропроцессор, содержащий блок управления вводом-выводом данных,регистр команд, арифметическо-логическое устройство, дешифратор и шифратор команд, регистр управления,блок регистров, формирователь приращений, устройство синхронизациии устройство управления циклсм памяти, адресный регистр, выход которсгоявляется выходной шиной адреса, апервый вход адресного регистра соединен с первым выходом формирователяПриращений, причем ввод-вывод блока 10управления вводом-выводом данныхсоединен с шиной данных, а его выход соединен со вторьщ входом адресного регистра, первым входом арифметическо-логического устройства, вхо"дом блока регистров и входом регистракоманд, выход которого соединен через дешифратор и шифратор команд совходом регистра управления, соединеннымсвоим выходом со вторым входом арифме-тйческо-логического устройства, входвыход которго соединен с входом-выходом блока регистров, вход-выход которого соединен с входом-выходомФормирователя приращений, третийвход арифметическо-логического устройства является первым входом переносов микропроцессора, вход формирователя приращеиий является вторымвходом переносов микропроцессора,выход арифметическо-логического устройства является первым выходом переносов микропроцессора, а второй выход формирователя приращений являетсявторым выходом переносов микропроцессора, выход,цешифратора команд сое динен со входом шифратора группкоманд, о т л и ч а ю щ и й с я тем. что, с целью повышения быстродействия,в микропроцессоре тактирующее устройство выполнено в виде распределителя длительности тактов, введены элементы И и ИЛИ, триггер, кодопреобразователь, счетчик формирования длительности тактов, группа входов которого соединена с группой выходов кодопреобразователя, дополнительный входсчетчика соединен с внешним входомуправления микрогроцессора и первымвходом распределителя длительноститактов, а его выход подключен ко второму входу распределителя длительности тактов и к одному из счетных входов триггера, другой вход триггерасоединен с выходом элемента И,первыйвход которого соединен с выходомэлемента ИЛИ, а второй вход соединенс выходом устройства синхронизации,группа выходов шифратора групп командсоединена с группой входов элементаИЛИ и с группой входов распределителядлительности тактов, дополнительныйвход распределителя длительности тактов соединен с выходом триггера и выходом микропроцессора, являющимсявыходом управления синхронизацией,группа входом кодопреобразователя является группой входов микропроцессора,на которые принимается код длительности такта. Источники йнформации,принятые во внимание при экспертизе 1, Электроника, 1975, 9 3,с, 33-35. 2. Электроника, 1976, 9 17,с. 33-40 (прототип).693377 г 5 оставитель Т; Ламехред С.Мигай наКорректор Е. Лука актоо С. Лыж Тираж 780ЦНИИПИ Государственногопо делам изобретений и 13035 Москва, ЖРачдс За Подписноеомитета СССРоткрытийая наб. д. Фили Патент, г. Ужгород, ул. Проектная

СмотретьЗаявка

2472550, 04.04.1977

ПРЕДПРИЯТИЕ ПЯ А-7160

КИРИЧЕНКО НИКОЛАЙ ВАСИЛЬЕВИЧ, КАЛМЫКОВ ВАЛЕНТИН АЛЕКСАНДРОВИЧ, ЛИНЧЕВСКИЙ ВАЛЕНТИН ГЕОРГИЕВИЧ, ЛЕВКОВ ВЛАДИМИР ЕФИМОВИЧ, СЫЧЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 25.10.1979

Код ссылки

<a href="https://patents.su/5-693377-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для контроля электропитания электронной вычислительной машины

Следующий патент: Устройство для вычисления координат вектора на плоскости

Случайный патент: Гидравлическая машина ударного действия