Устройство для кодирования аналоговых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1316091

Авторы: Анисимов, Ванде-Кирков, Матвеев, Устинова, Шепелев

Текст

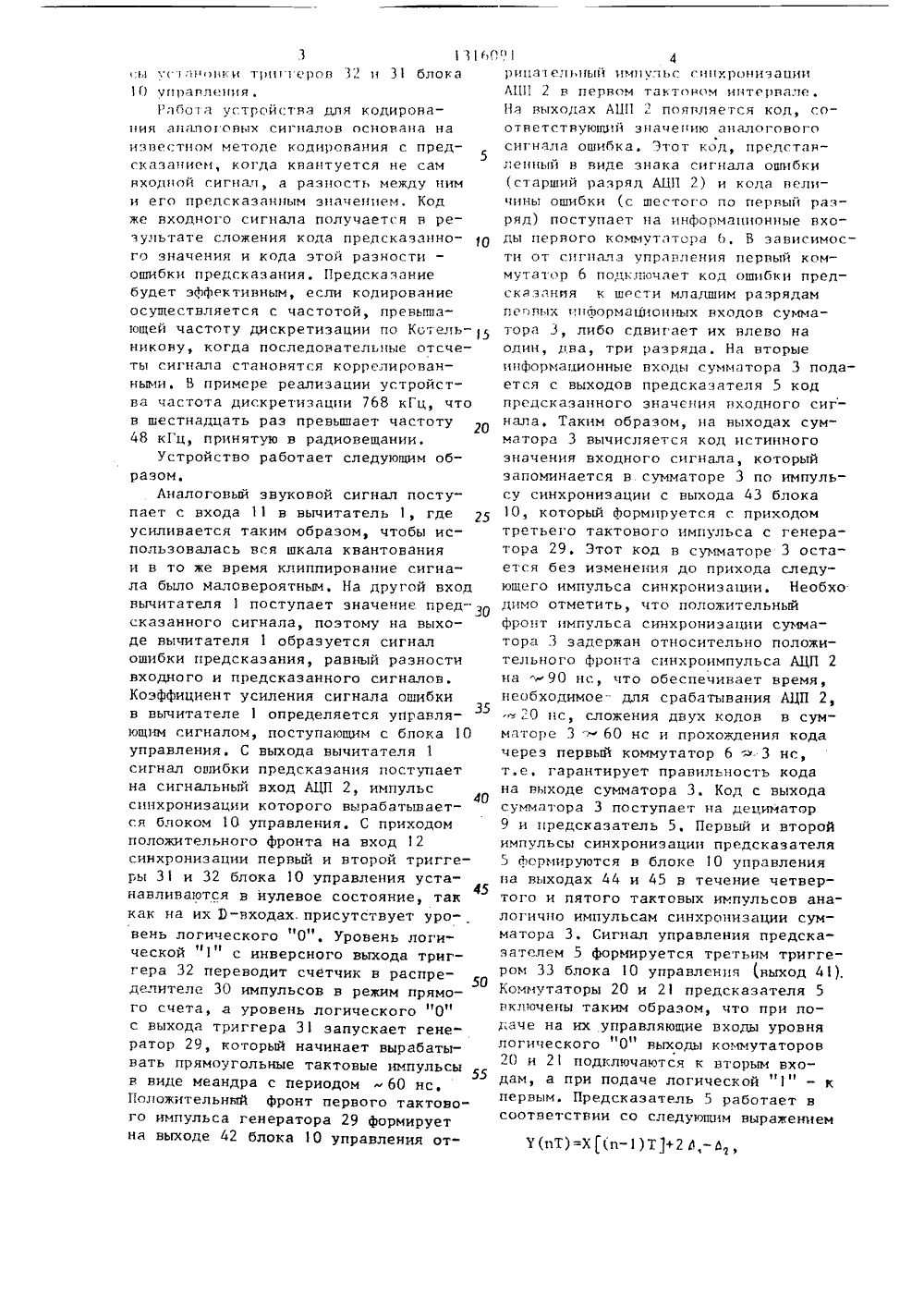

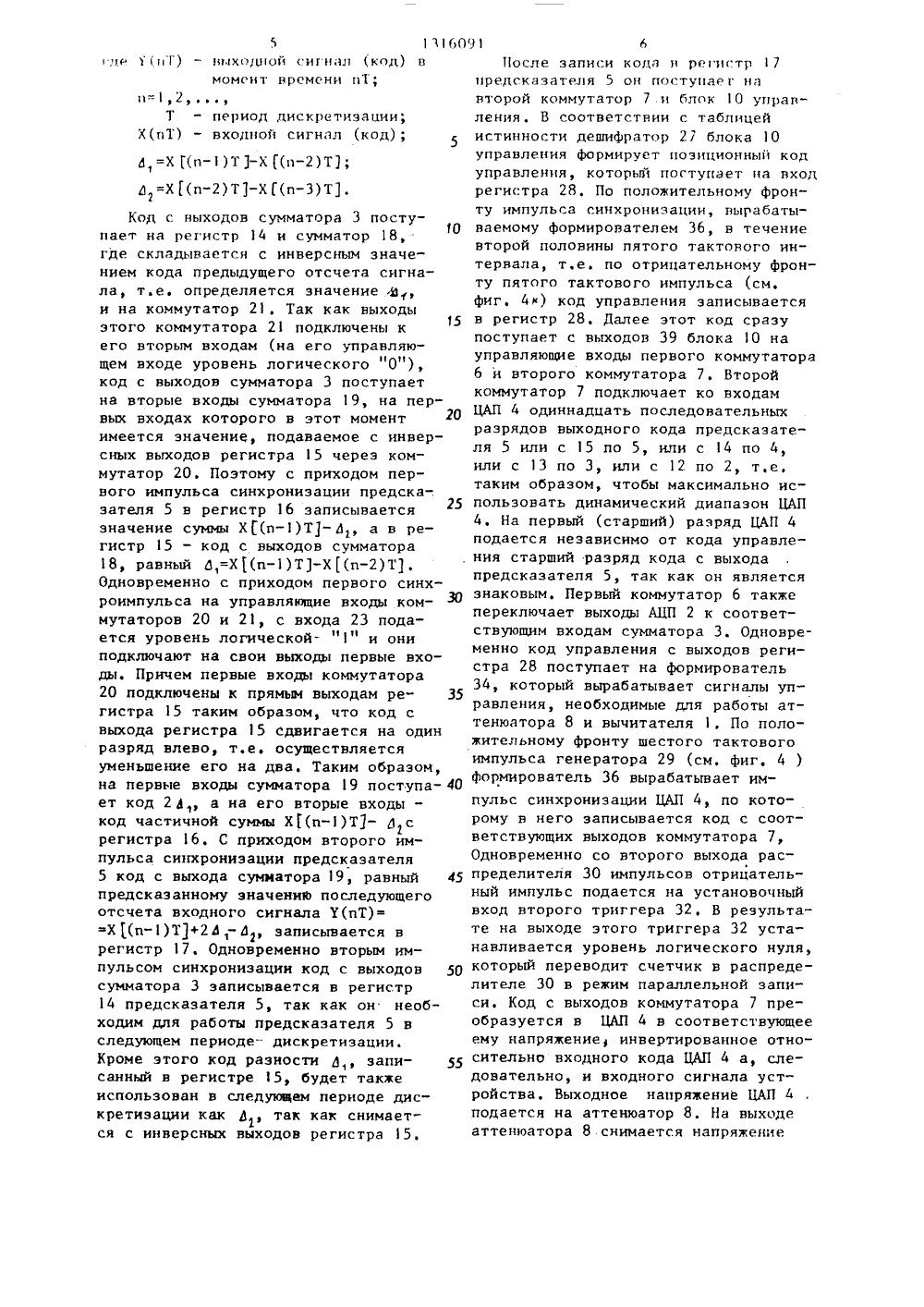

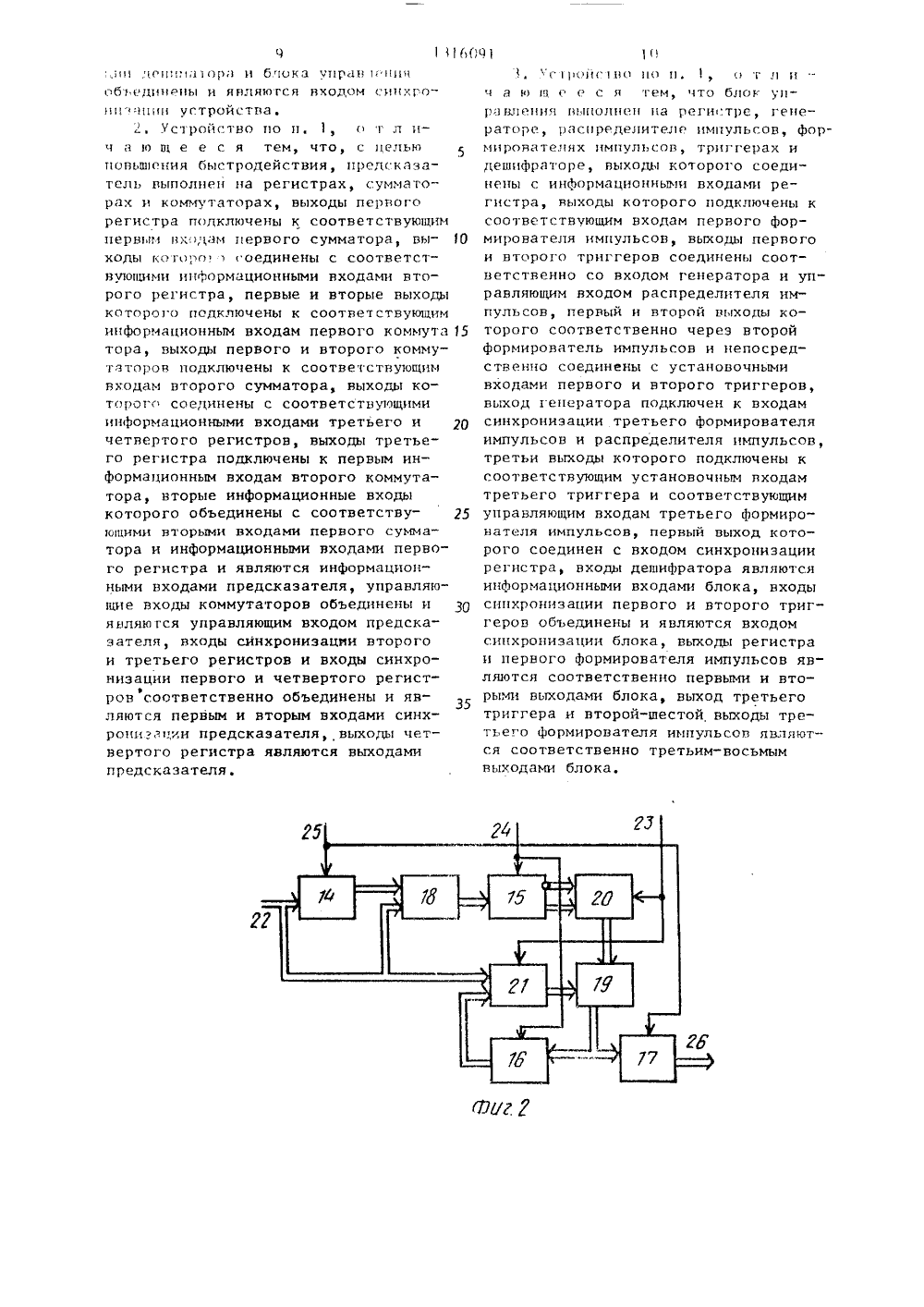

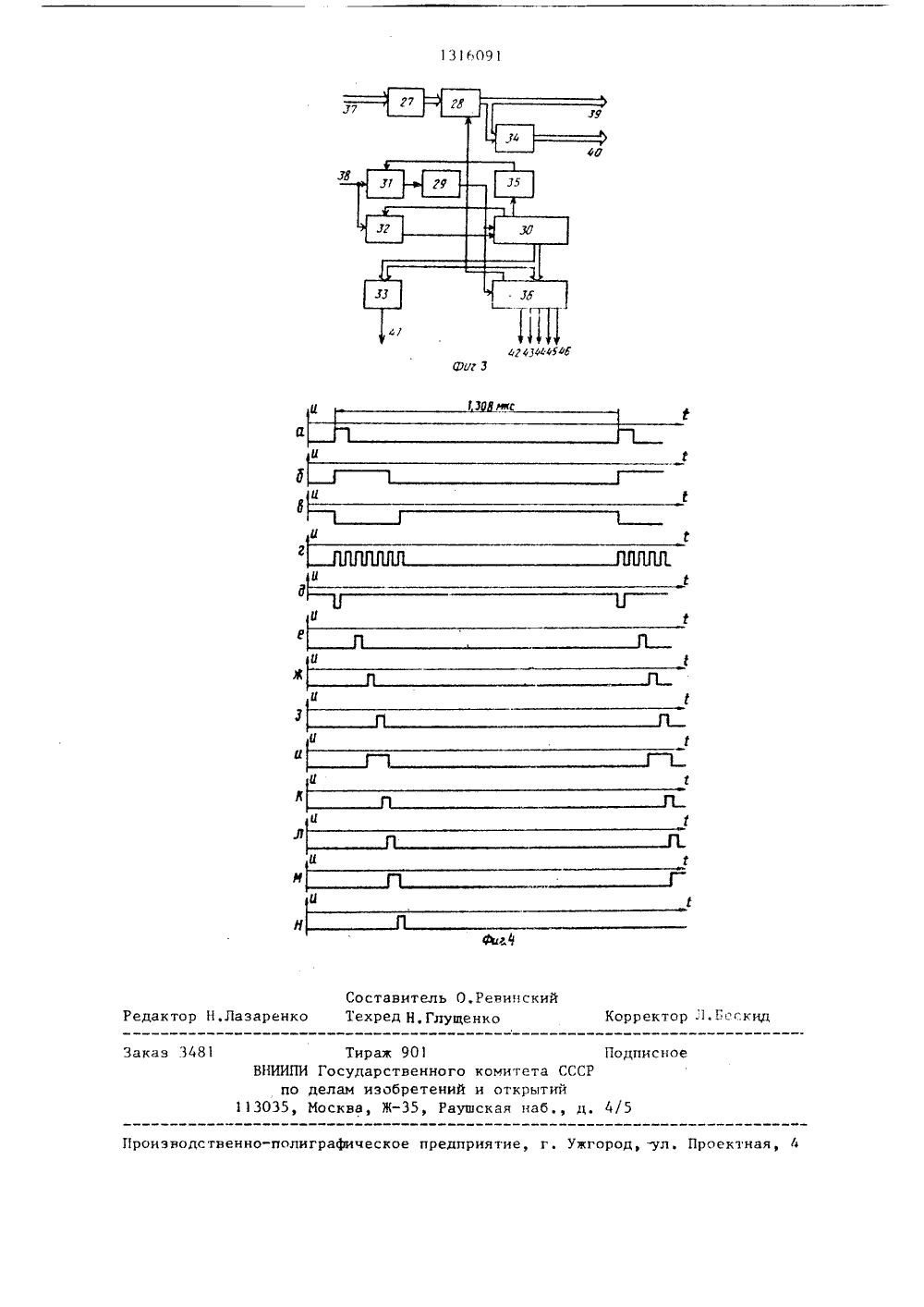

ОЮЗ СОВЕТСКИХ ЦИАЛИСТИЧЕСКИ СПУБЛИК 119) 11 6091 03 М 3/О(5 РСТВЕННЫЙ НОМИТЕТ СССР М ИЗОБРЕТЕНИЙ И ОТКРЫТ ГО 1 СИС ЕНИЯ 1 гЕЕЫ ". СВИДЕТ ТОРСН Ц 020 1 (1.1, 13.12.85 а обрего осит К те вацие в си напрцме оляет повь, 87, Бвл. У градский ин ной 0(,06 1 1 сцицо прибо ) С.В.А .Е.Матвее о -дцскрвых о т ав ть точсодеровойтор 3,гцалов п цо;172 ировация цс е-Кирков, и В.И.111 ежит вычитательпреобразовательцифроаналоговый англо1 АЦтт) елен 53) 62 56) Ап 11970 образовател и дециматор ов б и 7, а у вления 7 сказатель е коммута тво ССС 13,0-Зч 7,тт об 84 праумов вно ых вы ци ическ Сггси 1 гз8-25, 11 7,Тгапзас ещз, 191. РОЙСТВО СИГНАЛО 8 скретиз и более кже пот аз, чт цровац ил сть к цыыае 4-лы,.и т к- . 3 ч 0 Г 1,ЕЕ 1 Вуз ф 9 тостроенияисимов, В,В,ВЛ.Б.Устино РОВАНИЯ АНАч, пре Введсн атора г( чина Щ 2 и лией повиси чем в блокаснижени1 АП 4, апредскачастотч ателя 5 позв1 З ЬОИзобретение относится к автоматике и может быть использовано в системах дискретной передачи, например,звуковых сигналов,Цель изобретения - повышение точ 5ности кодированияНа фиг.изображена блок-схемаустройства для кодирования; на фиг.2и 3 - блок-схемы соответственно предсказателя и блока управления; на Офиг. 4 - вр:менные диаграммы работыустройства,Устройство для кодирования аналогового сигнала содержит вычитатель1, аналого-цифровой преобразователь 52 (АЦП), сумматор 3, цифро-аналоговый преобразователь 4 (ЦАП), предсказатель 5, первый и второй коммутаторы 6 и 7, аттенюатор 8, дециматор 9и блок 10 управления. На фиг. 1 обозначены информационный вход 11, вход12 синхронизации и выходы 13,Предсказатель 5 выполнен (фиг.2)с первого по четвертый регистрах 1417, первом и втором сумматорах 18 и 2519, первом и втором коммутаторах 20и 21, На фиг, 2 обозначены информационные входы 22, управляющий вход23, первый и второй входы 24 и 25синхронизации, выходы 26.Аттенюатор 8 - прецизионный управляемый делитель напряжения.Дециматор 9 представляет собойпоследовательное соединение цифрового фильтра низкой частоты, выполнен 35ного в виде нерекурсивного фильтрас конечной импульсной характеристикой, и компрессора частоты дискретизации (например, регистра), синхровходы которых объединены и являютсявходом синхронизации дециматора. Блок 10 управления выполнен(фиг. 3) на дешифраторе: 27, регистре 28, генераторе 29, распределителе 45 30 импульсов, первом, втором и третьем триггерах 31-33, первом, втором и третьем формирователях 34-36 импульсов, На фиг. 3 обозначены информационные входы 37., вход 38 синх рониэации с первого по восьмой выходы 39-46, Первый формирователь 34 импульсов служит для выработки сигналов управления коммутаторами 6 и 7 и представляет собой преобразователь уровней сигналов, Второй формирователь 35 импульсов обеспечивает дифференцирование отрицательного фронта поступающего на него импульса, Тре Входной код ыходной код 11 11 Зн,р. 1 р, 2 р. 3 1 2 3 4 1 1 1 0 1 1 1 1 1 0 0 1 1 1 1 0 1 0 1 1 1 1 0 0 0 1 1 1 0 01 1- 0 1 1 0 1 0 1 0 10 О 1 1 1 0 1 0 0 0 1 1 1 0 1 1 1 11 О 1 1 0 1 1 0 1 1 0 1 1 0 1 1 1 0 0 1 0 1 1 0 101 1 00 0 1 1 10 0 1 0 1 1 1 0 0 0 О 1 1 1 Распределитель 30 импульсов включает в себя счетчик и дешифраторНа фиг. 4 обозначено: а) импульс внешней синхронизации на входе 12; б) импульс на выходе триггера 32 блока 10 управления; в) импульс на выходе триггера 31 блока 10 управления; г) импульсы на выходе генератора 29 блока 1 О управления; д) импульсы на выходах 42-45 блока 10 управления (на входах синхронизации АЦП 2, сумматора 3 и входах 24 и 25 предсказателя 5 соответственно); и) сигнал на выходе триггера 33 (на входе 23 предсказателя 5); к) импульс на входе синхронизации регистра 28 блока О управления; л) импульс на выходе 46 блока. 10 управления .(на входе синхронизации ЦАП 4); м), н) импуль 91 2тий формирователь ЗЬ импульсов служит для выдачи импульсов синхронизации на блоки 2-5 и может быть выполнен в виде блока ключей, Дешифратор 27 реализует следующую таблицу истинности:3 13 с оы чпцки тцеров 32 и 31 блока 10 управления.Набоа устройства для кодирования аналоговых сигналов основана на о4 рипазельцыи импульс синхронизации АЦП 2 в первом тактоном интервале, На выходах АШ 2 появляется код, соответствующий значению ацалогоногоЪсигнала ошибка, Этот код, представленный в виде знака сигнала ошибки (старший разряд АЦП 2) и кода величины ошибки (с шестого по первый разряд) поступает ца информационные нхоизвестном методе кодирования с предсказанием, когда кнацтуется не самвходной сигнал, а разность между цим и его предсказанным значением, Кодже входного сигнала получается н результате сложения кода предсказанного значения и кода этой разностиошибки предсказания. Предсказаниебудет эффективным, если кодированиеосущестнляется с частотой, преньппады первого коммутатора б, В занисимос 1 О ти от сигнала управления первый коммутатор 6 подк.пючает код ошибки предсказания к шести младшим разрядампегвых информационных входов сумматора 3, либо сдвигает их влево наодин, дна, три разряда. На вторые ющей частоту дискретизации по Котельникону, когда последовательные отсчеты сигнала станонятся коррелиронацными. В примере реализации устройстна частота дискретизации 768 кГц, что в шестнадцать раэ превышает частоту 48 кГц, принятую в радиовещании.Устройство работает следующим образом,Аналоговый звуковой сигнал поступает с входа 11 в вычитатель 1, где усиливается таким образом, чтобы использовалась нся шкала квантования 20 25 и в то же время клиппирование сигнала было маловероятным, На другой входнычитателя 1 поступает значение пред-,0сказанного сигнала, поэтому на выходе вычитателя 1 образуется сигнал ошибки предсказания, равный разности входного и предсказанного сигналов. Коэффициент усиления сигнала ошибки в вычитателе 1 определяется упранляющим сигналом, поступающим с блока 1 Оуправления. С выхода вычитателя 1 сигнал ошибки предсказания поступает на сигнальный вход АЦП 2, импульс синхронизации которого ньрабатынает 40 ся блоком 10 управления. С приходом положительного фронта на вход 12 синхронизации первый и второй триггеры 31 и 32 блока 10 управления устанавливаются в нулевое состояние, так45 как на их З-входах. присутствует уровень логического цО. Уровень логиче ской 1 с инверсного выхода т риггера 3 2 переводит сч е тчик в распре 50 делителе 30 импульсов в режим прямого счета, а уровень логического Оцс выхода триггера 31 запускает генератор 29, который начинает вырабатывать прямоугольные тактовые импульсы55н виде меандра с периодом60 нс,Положительний фронт первого тактового импульса генератора 29 формируетна выходе 42 блока 10 управления от" информационные входы сумматора 3 подается с выходов предсказателя 5 код предсказанного значения входного сигнала, Таким образом, ца выходах сумматора 3 вычисляется код истинного значения входного сигнала, который запоминается в сумматоре 3 по импульсу синхронизации с выхода 43 блока 10, который формируется с приходом третьего тактового импульса с генератора 29, Этот код в сумматоре 3 остается беэ изменения до прихода следующего импульса синхронизации. Необхо димо отметить, что положительный фронт импульса синхронизации сумматора 3 задержан относительно положительного фронта синхроимпульса АЦП 2 на90 цс, что обеспечивает время, необходимое- для срабатывания АЦП 2,"0 цс, сложения двух кодов в сумматоре 360 нс и прохождения кода через первый коммутатор 6 . 3 нс, т.е, гарантирует правильность кода на выходе сумматора 3, Код с выхода сумматора 3 поступает ца дециматор 9 и предсказатель 5. Первый и второй импульсы синхронизации предсказателя 5 формируются в блоке 10 управления ца выходах 44 и 45 в течение четвертого и пятого тактовых импульсов аналогично импульсам синхронизации сумматора 3. Сигнал управления предсказателем 5 формируется третьим триггером 33 блока 10 управления 1,ныход 41), Коммутаторы 20 и 21 предсказателя 5 включены таким образом, что при подаче на их управляющие входы уровня логического "0 выходы коммутаторовО и 21 подключаются к вторым нходам, а при подаче логической "1" - к первым. Предсказатель 5 работает в соответствии со следующим выражениемУ (цТ) =Х п) Т +2 д - Ь,сф 1Г) ьх)цОи сигнал 1 КОд) Вмомент времени пТ;ю 2 ьффТ - период дискретизации;Х(пТ) - входной сигнал (код);Д, =Х (п) Т 3-Х (и) ТЗ;с =Х Г(п) Т -Х (п) Т.2Код с выходов сумматора 3 поступает на регистр 14 и сумматор 18, где складывается с инверсным значением кода предыдущего отсчета сигнала, т.е. определяется значение .2, и на коммутатор 21, Так как ныходы этого коммутатора 21 подключены к его вторым входам (на его управляющем входе уровень логического "0"), код с выходов сумматора 3 поступает на вторые входы сумматора 19, на первых входах которого в этот момент имеется значениЕ, подаваемое с инверсных выходон регистра 15 через коммутатор 20, Поэтому с приходом первого импульса синхронизации предска-. зателя 5 н регистр 16 записывается значение суммы Х(.(п)Т- Л, а в Регистр 5 - код с выходов сумматора 18, равный о=Х (и) Т-Х (и)Т. Одновременно с приходом первого синхроимпульса на управляющие входы коммутаторов 20 и 21, с входа 23 подается уровень логической и они подключают на свои выходь первые входы. Причем первые входы коммутатора 20 подключены к прямым выходам регистра 15 таким образом, что код с выхода регистра 15 сдвигается на один разряд влево, т.е. осуществляется уменьшение его на два. Таким образом, на первые входы сумматора 19 поступает код 2 М а на его вторые входы - код частичной суммы Х 1(п)Т 1- Д с2 регистра 16. С приходом второго импульса синхронизации предсказателя 5 код с выхода сумматора 19, равный предсказанному значению последующего отсчета входного сигнала У(пТ)= Х (п- ) Т +2 Л; д, записывается в регистр 17. Одновременно нторым импульсом синхронизации код с выходов сумматора 3 записывается в регистр 14 предсказателя 5, так как он. необходим для работы предсказателя 5 в следующем периоде- дискретизации.Кроме этого код разности д записанный в регистре 15, будет также использован в следующем периоде дискретизации как Д 1, так как снимается с инверсных вйходов регистра 5.6096После записи кода н реистр 17 предсказателя 5 он поступая г на второй коммутатор 7 и блок 10 управления. В соответствии с таблицей истинности дешифратор 27 блока 10 управления формирует позициотный кодуправления, который поступает на вход 10 15 20 25 30 35 40 45 50 55 регистра 28, По положительному фронту импульса синхронизации, вырабатываемому формирователем 36, в течение второй половины пятого тактового интервала, т.е. по отрицательному фронту пятого тактового импульса (см.фиг. 4 н) код управления записываетсяв регистр 28, Далее этот код сразупоступает с выходов 39 блока 1 О науправляющие входы первого коммутатора6 и второго коммутатора 7. Второй коммутатор 7 подключает ко входам ЦАП 4 одиннадцать последовательных разрядов выходного кода предсказателя 5 или с 15 по 5, или с 14 по 4, или с 13 по 3, или с 12 по 2, т.е. таким образом, чтобы максимально использонать динамический диапазон ЦАП4. На первый (старший) разряд ЦАП 4 подается независимо от кода управления старший разряд кода с выхода предсказателя 5, так как он является знаковым, Перный коммутатор 6 также переключает выходы АЦП 2 к соответствующим входам сумматора 3. Одновременно код управления с выходов регистра 28 поступает на формирователь 34, который вырабатывает сигналы управления, необходимые для работы аттенюатора 8 и вычитателя 1. По положительному фронту шестого тактового импульса генератора 29 (см. фиг, 4 ) формирователь 36 вырабатывает импульс синхронизации ЦАП 4, по которому в него записывается код с соответствующих выходов коммутатора 7, Одновременно со второго выхода распределителя 30 импульсов отрицательный импульс подается на установочныйвход второго триггера 32. В реэультате на выходе этого триггера 32 устанавливается уровень логического нуля,который переводит счетчик в распределителе 30 в режим параллельной записи. Код с выходов коммутатора 7 преобразуется в ЦАП 4 в соответствующее ему напряжение, инвертированное относительно входного кода ЦАП 4 а, следовательно, и входного сигнала устройства, Выходное напряжение ЦАП 4 подается на аттенюатор 8. На выходе аттенюатора 8 снимается напряжениетакое, чтобы нссстдцонить амплитудуН Р Р Д Г К Д З Д Н 11 ОО 3 и Д Ч Р ЦИ Я В Х О Д 110 ГО 1. И Гцдлд, искаженную н результате коммутации сигнала ца входе ЦАП 4, Пеобходимо отметить, что умецьп 1 аетг.я цавыходе аттецюаторд 8 не только самсигнал, цо и ошибка, вносимая неточностью уровней ЦАП 4, Сигнал с выхода аттецюдтора 8 поступает цд второйвход нычитателя 1, н котором ныраба- Отывается сигнал ошибки предсказанияС приходом седьмого тактового импульса с генератора 29 блока 10 управления формирователь 35 вырабатывает короткий положительный импульс, который устанавливает на выходе первоготриггера 31 уровень логической единицы и ог.тананливает генератор 29.С приходом очередного импульса синхронизации в блок 10 управления работа всего устройства повторится, какбыло описано вьппе,С выходов сумматора 3 коды отсчетов входного сигнала с частотой768 кГц поступают на информационный 25вход дециматора 9, а на его входсинхронизации поступает сИгнал внешней синхронизации с частотой 768 кГц.Цифровой фильтр, включенный в составдециматора 9, подавляет частотные 30составляющие, лежащие вне полось 1 полезного звукового сигнала (аналогично аналоговому фильтру нижних частотс полосой пропускания 0-20 кГц), дкомпрессор частоты дискретизации понижает частоту дискретизации до г.тацдартной 48 кГц, пропуская на выходыдециматора 9 только каждый шестнадцатый код с выхода цифрового фильтра.Таким образом на выходах дециматора 409 формируются коды отсчетов входного аналогового звукового сигнала счастотой 48 кГц, соответствующихшестнадцатиразрядному линейному кодированию, 45Устройство для кодирования аналоговых сигналов, благодаря дополнительной обработке предсказанного значения входного сигнала с помощью второго коммутатора 7 и аттеиюатора 8,упранляемьгс блоком 10 управления,позволяет уменьшить шум, вносимый неточностью ЦАП 4, более чем на 1014 дБ, А дополнительная обработкасигнала ошибки предсказания нычитателеми первым коммутатором 6позволяет сохранить условие незцачительногти шумов, вносимых АЦП 2 Кроме этого, использование н петле обР ДТЦОИ С В Я ЗИ 11 РРДС КД 1;11 Г 11 Я 1 НЫЦОЦ ИЕЦЦО 1 О ИО ОРИ 1 ИЦД 1 ЬЦОИ ГХ 1 МС, ДДЕТ возможность унеличит 1, чд 1 г 1 ту дискрети 1 д 1 Ц 1 и болРР че 1 н 16 рдз НО Грдн - ЦРЦИН 1 С ЦРИЦЯТОй 1 Ы 1 Я КС 11 ИР 11 НДЦИЯ ЗНУКОЦЫХ СИГ 51 ДЛОН1 ТО ПОЗ ВОЛ 51 РТ ЦРИ использовании цд ныход 1 устройства дгцимдторд 9 поныгить т 1 чцость кодирования еще цд 12 дБ,Формула и з о б р Р т е н и я, Устройство д 51 я кодирования аналоговых сигцдлон, содержащее нычитатель, выход которого соединен с ин - формационным входом дцд:1 ого-цифрового прес бразонателя, цифродцдлогоный преобразователь, сумматор, выходы которого подключены к соотнетствук 1 щим ицформациоццым входам дециматора и предсказателя, выходы которого соедицецы с соответствующими первыми входами сумматора, первый информационный вход вычитателя является информационным входом устройства, выходы дециматора являются нь 1 ходами устройства, о т л и ч а ю щ е е с я тем, что, с целью цовьппеция точности кодирования, в устройство введены коммутаторы, аттенюатор и блок уцрднлг 1;я, первые выходь 1 которого подключены к соответствующим управляющим входам первого и второго коммутаторов, выходы которых подключены соответственно к вторым входам сумматора и информационным входам цифроаналогового преобразователя, выход которого соединен с ицформациоццым входом аттецюатора, вторые выходы блока упранлепия подключены к управляющим входам нычитателя и дттгцюдторд, вь 1- ход которого соединен с вторым информационным входом вычитдтеля, выходы аналого-цифрового цреобрдзондтеля подключены к информационным входам перного коммутатора, соответствующие информационные входы второго коммутатс рд и блока управления объе 55 ицены и подключены к соответствующим выходам предсказателя, третий, четнертый и пятый выходы блока управления соедицецы соответственно с управляющим входом и первым и вторым входами синхронизации предсказателя, шестой, седьмой и носьмой выходы блока управления соединены с входами синхронизации соответственно цифроаналогового и аналого-цифрового преобразона телей и сумматора, входы с.ицхроццза,. .инаор и блока упр гв с с объединены и являются входом ихроц;:пни устройства, Устройство по и, 1, с т л ич а ю щ е е с я тем, что, с целью повьшения бьстродействия, предсказатель выполнен на регистрах, сумматорах и коммутаторах, выходы первого регистра подклнчены к соответствующим первым н;дам первого сумматора, вы ходы которо.оединены с соответствуюцнии информационными входами второго регистра, первые и вторые выходы которого подключены к соответствующим информационным входам первого коммута 15 тора, выходы первого и второго коммутаторов подключены к соответствующим входам второго сумматора, выходы котспото соединены с соответствующими информационными входами третьего и р четвертого регистров, выходы третьего регистра подключены к первым информационным входам второго коммутатора, вторые информационные входы которого объединены с соответствующими вторыми входами первого сумматора и информационными входами первого регистра и являются информационными входами предсказателя, управляющие входы коммутаторов объединены и являются управляющим входом предсказателя, входы синхронизации второго и третьего регистров и входы синхронизации первого и четвертого регистров соответственно объединены и являются первым и вторым входами синхронизации предсказателя, выходь четвертого регистра являются выходами предсказателя.с)ус сйгвссо и. 1, с т и и и ащ е е с я тем, что блок упр влснис вьнсолнен на реги.тре, генераторе, аснределителе импульсов, формирователях импульсов, триггерах и дешифраторе, выходы которого соединены с информационными входами регистра, вьходы которого подключены к соответствующим входам первого формирователя импульсов, выходы первого и второго триггеров соединены соответственно со входом генератора и управляющим входом распределителя импульсов, первый и второй выходы которого соответственно через второй формирователь импульсов и непосредственно соединены с установочными входами первого и второго триггеров, выход генератора подключен к входам синхронизации третьего формирователя импульсов н распределителя импульсов, третьи выходы которого подключены к соответствующим установочным входам третьего триггера и соответствующим управляющим входам третьего формирователя импульсов, первый выход которого соединен с входом синхронизации регистра, входы дешифратора являются информационными входами блока, входы синхронизации первого и второго триггеров объединены и являются входом синхронизации блока, выходы регистра и первого формирователя импульсов являются соответственно первыми и вторыми выходами блока, выход третьего триггера и второй-шестой выходы третьего формирователя импульсов являются соответственно третьим-восьмым выходами блока.

СмотретьЗаявка

4020140, 13.12.1985

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

АНИСИМОВ СЕРГЕЙ ВАСИЛЬЕВИЧ, ВАНДЕ-КИРКОВ ВЛАДИМИР ВАДИМОВИЧ, МАТВЕЕВ НИКОЛАЙ ЕВГЕНЬЕВИЧ, УСТИНОВА ЛИДИЯ БОРИСОВНА, ШЕПЕЛЕВ ВАДИМ ИВАНОВИЧ

МПК / Метки

МПК: H03M 3/04

Метки: аналоговых, кодирования, сигналов

Опубликовано: 07.06.1987

Код ссылки

<a href="https://patents.su/7-1316091-ustrojjstvo-dlya-kodirovaniya-analogovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования аналоговых сигналов</a>

Предыдущий патент: Преобразователь угла поворота вала в код

Следующий патент: Устройство для формирования квазитроичных кодов

Случайный патент: Устройство для регистрации сигналов неисправности