Программируемый процессор спектральной обработки сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1092517

Авторы: Каневский, Краснощеков, Куц, Сергиенко

Текст

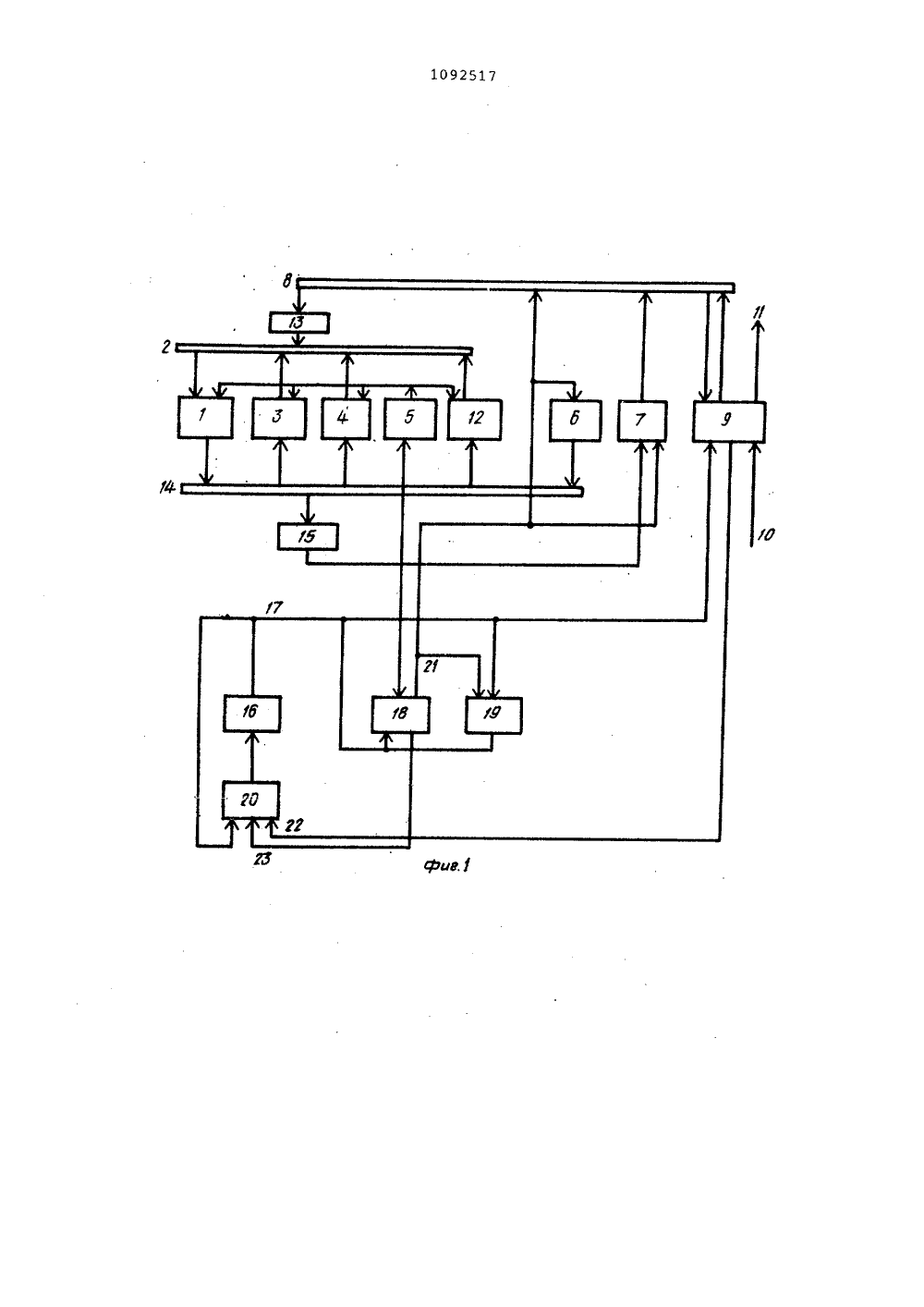

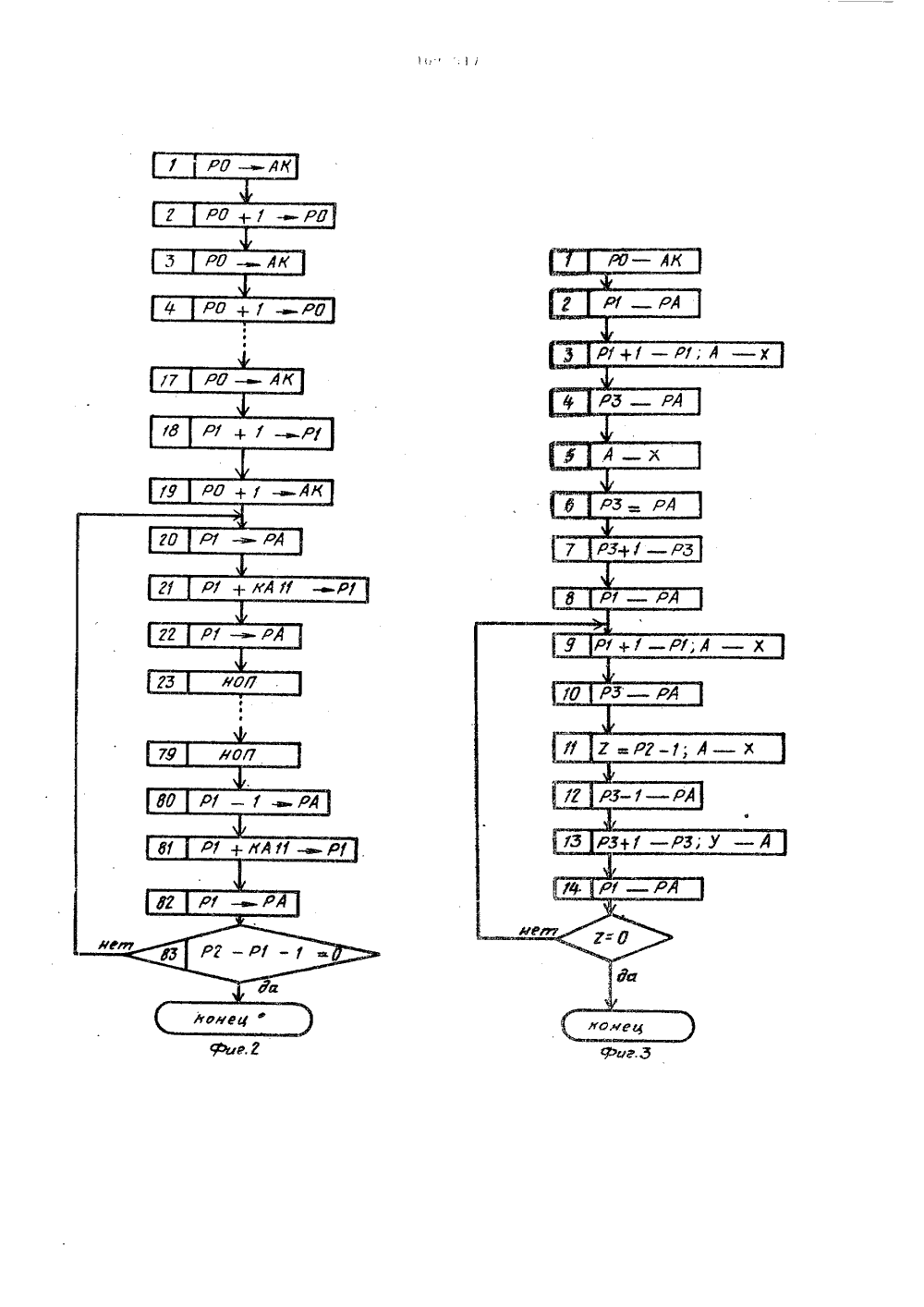

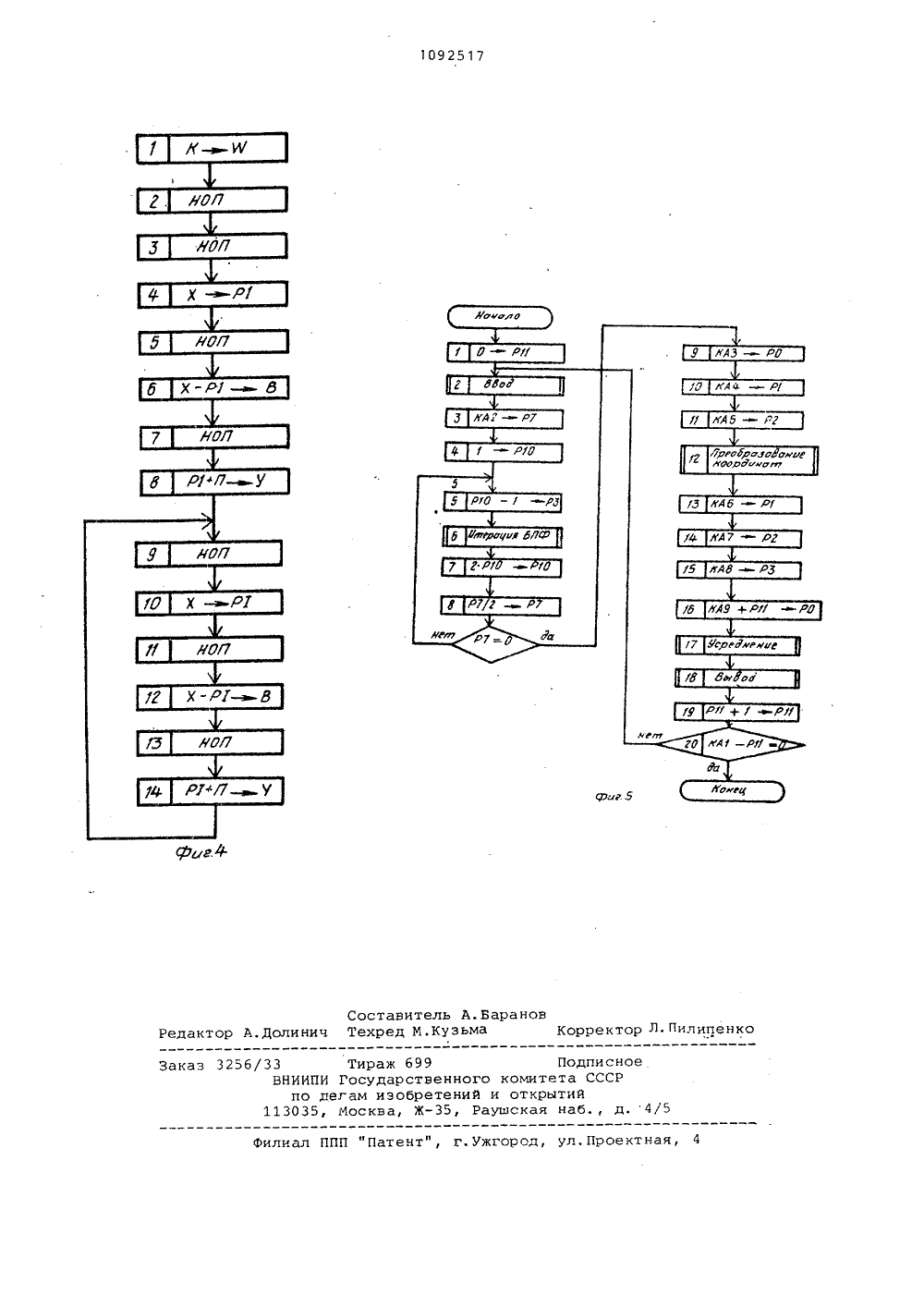

(71) Киевский орденанический институт имВеликой Октябрьской среволюции(прототип). 18П.КраснощековкоЛенина политех50-летияоциалистическо й госеееп 8,ельство СССР5/332, 1977 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ ОМУ СВИДЕТЕЛЬСТВ(54)(57) ПРОГРАММИРУЕМЫЙ ПРОЦЕССОРСПЕКТРАЛЬНОЙ ОБРАБОТКИ СИГНАЛОВ,содержащий первый арифметическийблок, информационный выход которогоподключен к информационным входам регистров первой группы и первому информационному входу блока умножения,информационный выход которого соединен с информационными выходами регистров первой группы и подключен кинформационному входу первого арифметического блока, коммутатор связис интерфейсом, первый вход которогосоединен с информационным выходомблока памяти, второй вход и первыйвыход коммутатора связи с интерфейсом являются соответственно информационным входом и информационным выходом процессора, блок постояннойпамяти, информационный выход которого соединен с вторым информационнымвходом блока умножения, блок управления,состоящий из узла адресации иузла памяти микропрограмм, информационный выход которого соединен с входом следующего адреса узла адресации, вход признака которого являетсявходом признака блока управления,выход узла адресации соединен с адресным входом узла памяти микропрограмм, выходы группы разрядов которого соединены с управляющими входами соответственно первого арифметического блока, регистров первой группы и блока умножения, о т л ич а ю щ и й с я тем, что, с целью повышения быстродействия процессора, он содержит сдвигатель, первый и второй буферные регистры, второй арифметический блок, вторую группу регистров, блок памяти программ и блок адресации, выход которого соединен с адресным входом блока памяти программ, информационный выход которого подключен ко входу следующего адреса блока адресации, управляющему входу второго арифметическо- Ж го блока, информационному входу второго арифметического блока, входу установки начального адреса узла адресации блока управления, тактовым входам регистров второй группы и управляющему входу коммутатора связи с интерфейсом, второй выход которого подключен к входу установки4 начального адреса блока адресации, вход признака условного перехода которого соединен с выходом окончания вычислений второго арифметическо го блока, информационный выход которого соединен с информационными входами регистров второй группы, адресными входами блока памяти и блока по стоянкой памяти, первым входом коммутатора связи с интерфейсом и информационным входом первого буферного регистра, информационный выход которого объединен с информационными выходами сдвигателя и подключен к информационному входу первого арифметического блока, информационный выход которого соединен с информационными входами сдвигателя и информационным входом второго буферного регистра, информационный выход которого подключен к информационному входу блока1092517 памяти, информационный вход первогобуферного регистра подключен к третьему выходу коммутатора связи с интерфейсом, информационные выходы регистров второй группы соединены с инфор 1Изобретение относится к вычислительной технике и может использоваться в вычислительных системах и устройствах цифровой обработки сигналов.Известен программируемый процессор 5 спектральной обработки сигналов, кото рый содержит блок регистров, арифметико-логический блок, блок умножения, блок оперативной памяти, блок снязи с интерфейсом, соединенные между собой магистралью, блок управления Г 1 1.Недостатком этого процессора явля- ется низкая производительность, обусловленная тем, что обмен данными между всеми блоками осуществляется по одной двунаправленной магистрали, т.е. эффективность загрузки отдельных блоков является сравнительно низкой.Наиболее близким по технической сущности к изобретению является прог- О раммируемый процессор спектральной обработки сигналов, который содержит первый арифметико-логический блок первый вход которого через первую магистраль соединен с выходами первого блока регистров и блока умножения, блок управления выходом соединен с первыми входами первого блока регистров и блока умножения и со вто. рым входом первого арифметико-логического блока, блок памяти констант,Г 3 блок оперативной памяти, выходом соединенный через вторую магистраль с первыми входом и выходом блока связи и с интерфейсом, вторые вход и выход которого являются входом и выходом 35 процессора соответственно.для возможности выполнения алгоритм мов спектральной обработки сигналон Данный процессор дополнительно содержит индексный блок адресации, блок 4 О преобразования координат, накопитель, блок синхронизации. Обмен данными и микрокомандами осущестнляется через три магистрали Г 23.При выполнении базовой операции алгоритма, быстрого преобразования Фурье ),БПФ ) используется первый арифметико-логический блок, первый блок регистров, блок умножения, блок оперативной памяти, блок памяти констант, первая, вторая и третья магистрали. При выполнении алгоритма усреднения используется накопитель,мационным входом второго арифметического блока, упранляющие входы сдвигателя соединены с соотнетстнующимиуправляющими выходами группы узла памяти микропрограмм блока управления. блок оперативной памяти, вторая итретья магистрали. При выполненииалгоритма преобразования координатиспользуется блок преобразования координат, а также вторая и третья магистрали. Таким образом ввиду того,что все три магистрали во времяполнения указанных алгоритмов почтивсегда загружены, невозможно совмещение во нремени реализации этих алгоритмон блоками процессора, т.е.загрузка этих блоков характеризуетсянизкой эффективностью. Программы обработки, константы и данные н процессоре находятся в одной области памяти, образонанной блоком памяти констант и блоком оперативной памяти,выходами соединенных с одной второймагистралью. Эта область памяти адресуется одним и тем же индекснымблоком адресации отсюда следует невозможность совмещения во временивыборки и дешифрации микрокоманд, выборки констант и выборки данных.Кроме того,. сигнал выборки микрокоманд проходит длинный путь иэ блокауправления через первую и третью магистраль в индексный блок адресации,т.е, загружает две магистрали сразу.Пересылки между первым арнфметико-логическим блоком, первым блоком регистров и блоком умножения осуществляются по одной (первой )магистрали,поэтому невозможно распараллеливание выполнения операций в блоке умножения и в первом арифметико-логическом блоке, Следовательно, недостатком данного процессора является низкая производительность при сравнительно больших аппаратурных затратах,Цель изобретения - повышение быстродействия процессора.Поставленная цель достигается тем, что программируемый процессор спектральной обработки сигналов, содержащий первый арифметический блок, информационный выход которого подключен к информационным входам регистров первой группы и первому информационному входу блока умножения, информационный выход которого соединен с информационными выходами регистров первой группы и подключен к информационному входу первого арифметического блока, 1092517коммутатор связи с интерфейсом, первый вход которого соединен с информационным выходом блока памяти, второй вход и первый выход коммутатора связи с интерфейсом являются соответственно информационным входом и инфор- мационныМ выходом процессора, блок постоянной памяти, информационный выход которого соединен с вторым информационным входом блока умножения, блок управления, состоящий 1 О из узла адресации и узла памяти микропрограмм, информационный выход которого соединен со входом следующего адреса узла адресации, вход признака которого является входом признака 15 блока управления, выход узла адресации соединен с адресным входом узла памяти микропрограмм, выходы группы разрядов. которого соединены с управляющими входами соответственно перво-о го арифметического блока, регистров первой группы и блока умножения, содержит сдвигатель, первый и второй буферные регистры, второй арифметический блок, вторую группу регистРов, 5 блок памяти программ и блок адресации, выход которого соединен с адресным входом блока памяти программ, информационный выход которого подключен к входу следующего адреса блока адресации, управляющему входу второго арифметического блока, информационному входу второго арифметического блока, входу установки начального адреса узла адресации блока управления, тактовым входам регистров второй группы и управляющему входу коммутатора связи с интерфейсом, второй выход которого подключен к входу установки начального адреса блока адресации, вход признака условного 40 перехода которого соединен с выходом окончания вычислений второго арифметического блока, информационный выход которого соединен с информационными входами регистров второй группы, 45 адресными входами блока памяти и блока постоянной памяти, первым входом коммутатора связи с интерфейсом и информационным входом первого буферного регистра, информационный выход которого объединен с информационными выходами сдвигателя и подключен к информационному входу первого арифметического блока, информационный выход которого соединен с информационными входами сдвигателя и информационным входом второго буферного регистра, информационный выход которого подключен к информационному входу блока памяти, информационный вход первого буферного регистра подключен к третьему выходу коммутатора связи с интерфейсом, инФормационные выходы регистров второй группы соединены с информационным входом второго арифметическога блока, управляющие входы сдвиъ 5 гателя соединены с соатвст твующв 1 я управляющими выходами группы у зл па. .мяти микропрограмм блока управления,На фиг, 1 представлена блок-схема процессора; на фиг. 2 - блок-схема алгоритма вычисления адресной после - давательности для преобразования координат; на Фиг. 3 - блок-схема алгоритма вычисления адресной последова.тельности усреднения; на Фиг, 4 блок-схема алгоритма вычисления усреднения; на Фиг. 5 в ,блок-схема алгоритма циФровой обработки сигналов.Программируемый процессор спектральной обработки сигналов содержит арифметический блок 1, магистраль 2, группу регистров 3, блок умножения 4, блок управления 5, блок постоянной памяти ( констант ) б, блок (оперативной ) памяти 7, магистраль 8, коммутатор связи с интерфейсом 9, вход 10 и выход 11 процессора соответственна, сдвигатель 12, буферный регистр 13, магистраль 14, буферный регистр 15, блок 16 памяти программ, выхс 17 блока 16, арифметический блок 18, группу 19 регистров, блок 20 адреса. ции, выход 21 блока 18, вход 22 (вход установки начального адреса программы ) блока 20 адресации, вход 23 (признак условного перехода ).Программируемый процессор спектральной обработки сигналов работает следующим образом.Блок 1, группа регистров 3, блок умножения 4 и сдвигатель 12 под ваэдейстьием управляющих сигналов из блока управления 5, обмениваясь между собой операндами через магистрали 2 и 14, выполняют одну из элементарных операций, таких как базовая операция алгоритма БПФ, операция усреднения, операция преобразования координат и другие. Код этой операции поступает в блок 5 управления с выхода 17 блока 16 памяти программ. Обрабатываемые массивы операндов хранятся в блоке 7 оперативной памяти, считываются иэ него и через магистраль 8 и буферный регистр 13 поступают в магистраль 2 и далее в блоки 1, 3, 4, 12, где обрабатываются согласна алгоритму заданной элементарной операции, Результаты этой операции из магистрали 14 через буферный регистр 15 записываются в блок оперативной памяти 7. Константы, необходимые при выполнении элементарной операции, хранятся в блоке 6 памяти констант, откуда выдаются в магистраль 14. Адреса для блока 6 памяти констант и блока 7 оперативной памяти поступают с выхода 21 блока 18. Исходные данные са входа 10 процессора поступают в коммутатор 9 связи с интерфейсом через его вход и далее с ега выхода через магистраль 8 записываются в блок 7 оперативной памя 1092517ти. Результаты обработки считываются из блока 7 оперативной памяти и через магистраль 8 поступают на вход коммутатора 9 связи с интерфейсом, с выхода которого выдаются на выход 11 процессора. С выхода 17 блока 16 памяти программ на вход коммутатора 9 связи с интерфейсом поступает управляющая информация. С выхода коммутатора 9 связи с интерфейсом на вход 22 блока 21 адресации поступает 10 начальный адрес программы спектральной обработки сигналов.В блоке 16 памяти программ хранятся програмж спектральной обработки сигналов, Каждая такая программа со держит последовательность команд обработки согласно тому или иному алгоритму спектральной обработки сигналов. В поле команды указывается код элементарной операции, который рО через выход 17 блока 16 поступает в блок управления 5, а также код адреса подпрограммы вычисления адресных последовательностей, который поступает на первый вход блока 20 адресации.25 Подпрограммы вычисления адресных последовательностей хранятся в том же блоке 16 памяти программ. По микро- командам подпрограмм в блоке 18 и группе 19 регистров вычисляются адре-ЗО са операндов, результатов и коэффициентов, которые поступают на шину 21, при этом с блока 16 на вход блока 18 поступают константы, необходимзе при вычислении адресной последовательно- З 5 сти.По одной команде процессор выполняет один цикл вычислений, например одну итерацию алгоритма БПФ, цикл усреднения или Цикл преобразования координат операндов массива, хранящегося в блоке 7 оперативной памя ти. При этом количество элементарных операций в цикле равно количеству й операндов в массиве. Блок управления 5, получив код элементарной операции 4 с шины 17, выдает. управляющие сигна- лы в блоки 1, 3, 4 и 12, по которым происходит в этих блоках неоднократ-ное выполнение заданной элементарнойоперации до тех пор, пока из блока 16не поступает новый код элементарнойоперации. В это же время блок 18 игруппа 19 регистров согласно подпрограмме производят вычисления последовательности адресов операндов, результатов и констант, участвующих ввычислении элементарной операции,причем время вычисления одной элементарной операции равно времени вычисления адресов для следующей элементарной операции Кроме того, дляопределения конца подпрограммы в одном из регистров группы 19 регистров ведется счет количества элементарных операций. По достижении заданного числа элементарных операцийблок 18 с выхода выдает сигнал навход 23 блока 20 адресации,по которомупроисходит возврат из подпрограммы ииз блока 16 памяти программ выбирается следующая команда. В то время,когда в блоках 1, 3, 4 и 12 вычисляется 1-я элементарная операция, изблока 7 оперативной памяти считываются в буферный регистр 13 исходныеданные для 1+1-й элементарной операции и из буферного регистра 15 вблок 7 оперативной памяти записываются результаты 1-1-й элементарнойоперации. Таким образом, в процессоре осуществляется совмещение во времени определения адресов операндов, результатов и констант, обращение к блоку 7 оперативной памяти, обращение к блоку 6 памяти констант и непосредственно вычисление элементарной операции блоками 1,3, 4, 5 и 12, что позволяет загрузить все блоки процессора и получить высокую производительность. Выполнение различных элементарных операций одним и тем же набором блоков 1, 3, 4, 5, 7 и 12 поз, воляетотказаться от применения блока преобразования координат и блока накопления, что упрощает процессор и уменьшает аппаратурные затраты.Заказ 325 отск Филиал ППП "Патент", г. Ужгород, ул, Проектная 3 Тираж 699ВНИИПИ Государственногопо дегам изобретений и13035, Москва, Ж, Рауш Подписноетета СССРрытийя наб., д. 4

СмотретьЗаявка

3511980, 17.11.1982

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50-ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

КАНЕВСКИЙ ЮРИЙ СТАНИСЛАВОВИЧ, КРАСНОЩЕКОВ ИВАН ПЕТРОВИЧ, КУЦ НАТАЛИЯ ЕВГЕНЬЕВНА, СЕРГИЕНКО АНАТОЛИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 17/14

Метки: программируемый, процессор, сигналов, спектральной

Опубликовано: 15.05.1984

Код ссылки

<a href="https://patents.su/7-1092517-programmiruemyjj-processor-spektralnojj-obrabotki-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый процессор спектральной обработки сигналов</a>

Предыдущий патент: Цифровой генератор синуса

Следующий патент: Цифровой спектроанализатор

Случайный патент: Устройство для ошиновки катодных стержней электролитической ванны для получения алюминия