Конвейерное устройство для вычисления функции y=е

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

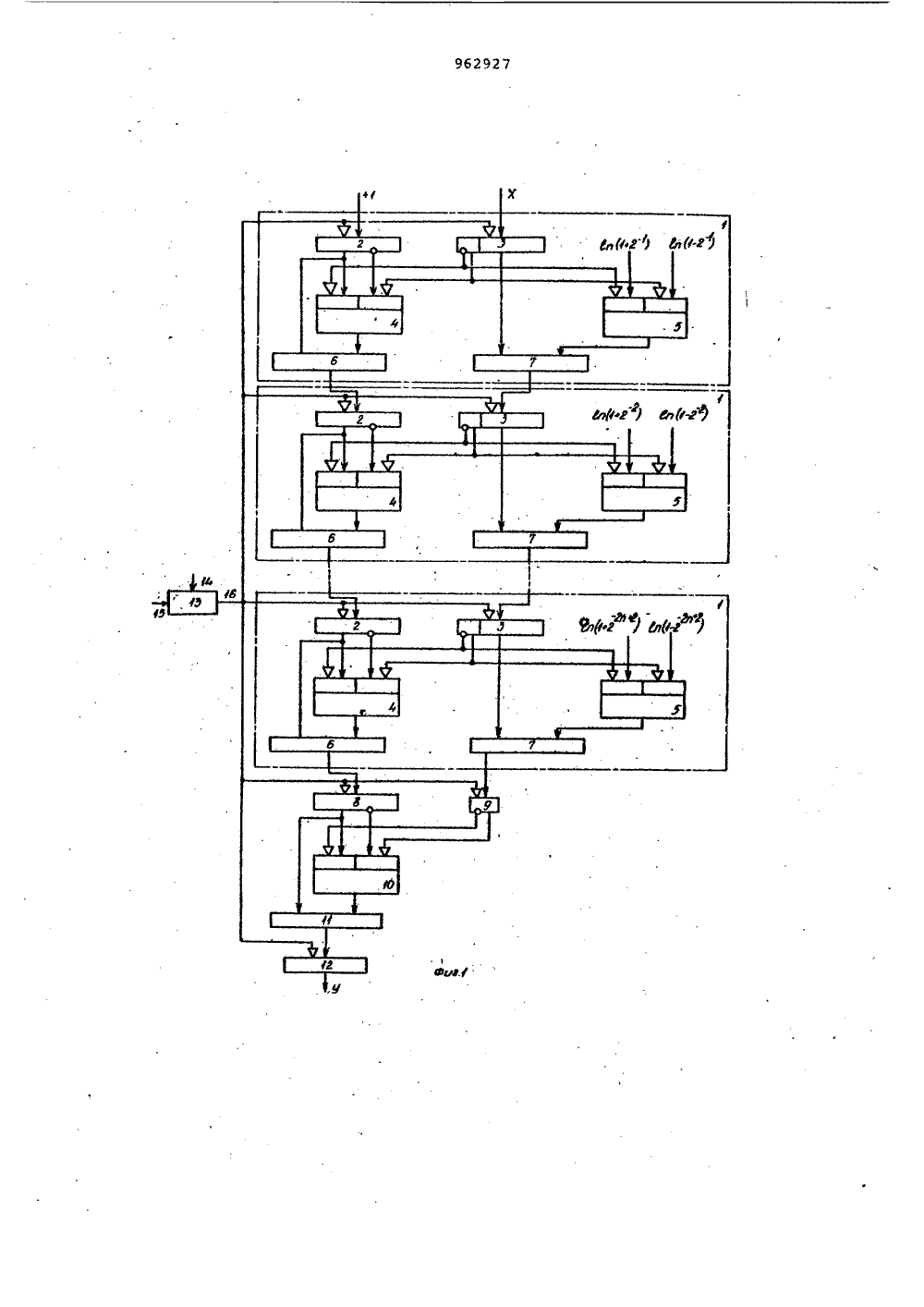

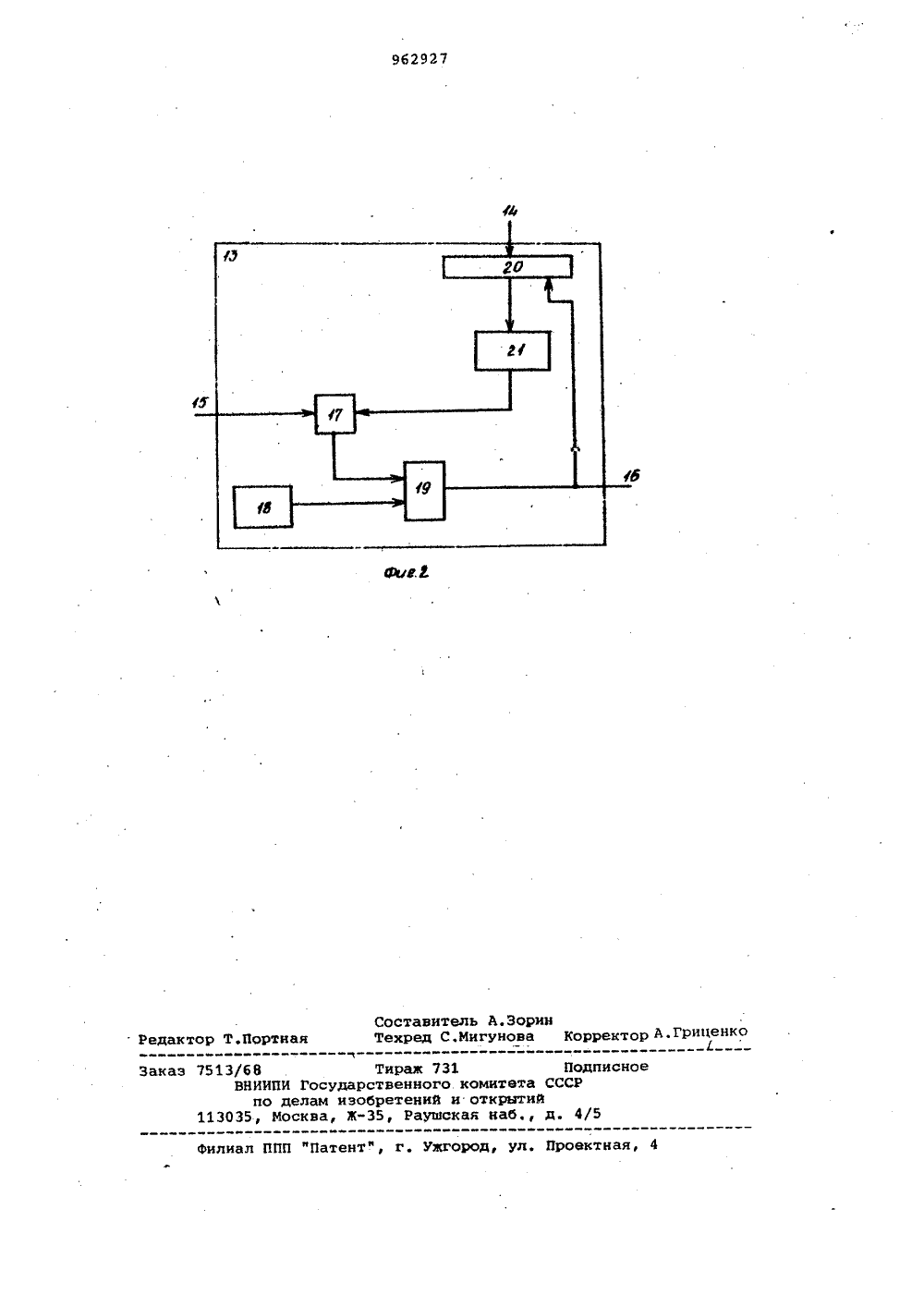

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(23) Приоритет Государственный комитет СССР по дедам изобретений и открытийОпубликовано 30.09.82. Бюллетень Йо 36 Дата опубликования описания 30.09,82. с 3;Львовский ордена Ленина политехнический институт" - -им. Ленинского комсомола(54) КОНВЕЙЕРНОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ х = ех Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного процессора вычислительной системы высокой производительности,построенной на основе больших интегральных схем, для вычисления функции у = е",При цифровой обработке сигналов,например в задачах, связанных с обработкой физической информации, требуется выполнять операции вычисления зкспоненциальной Функции надмассивами чисел, Причем в системахреального времени при исследованиибыстропротекающих.процессов требования к быстродействию выполнения данной операции очень высокиИзвестно устройство для вычисления функции вида у е", содержащеерегистр аргумента, блок маскирования аргумента, блок постоянной памяти, блок оперативной памяти, блоквыделения младшей эоны аргумента,.блок управления, блок определениянулевых значений аргумента, блокумножения 1),Недостатком известного устройстваявляется низкое быстродействие,поскольку экспоненциальная Функция здесь. вычисляется по итерационнойФормуле, причем в кажцой итерациииспользуется времяемкая операцияумножения.Наиболее близким по техническойсущности к изобретению является устройство, содержащее первый и второйрегистры, первый и второй сумматоры,блок сдвига, промежуточный регистрдля кратковременного хранения констант, блок памяти для хранения.констант, счетчик адреса, блок микропрограммного управления.Данное устройство аппаратно реали 15 .зует операцию вычисления Функцииу = е". Быстродействие данного устаройства при вычис.-ении Функции увне превышает времени Т. " 2,5 пти,где и в . разрядность обрабатываеьысоперандов, т, - время суммирования.двух чисел на сумматоре. При реализации данного устройства необходимблок памяти для хранения 2 п констанТ,.а также микропрограмм блока микро"программнбго управления 21.Недостатком известного устройст"ва является низкое быстродействиеи большие объемы дорогостоящих блоков памяти для храненияконстант иЗО микропрограмм,+1 "Х,.=Х,. - Еи(+;1 ")9 Р .:з 1 Р х,где К(1) Цель изобретения - повышение быстродейств:;я и сокращение объема памяти,Поставленная цель достигаетсятем, что в устройство, содержащееблок управления, промежуточный регистр и выходной сумматор, первыйвход которого соединен с прямым вы"ходом промежуточного регистра, дополнительно введены (2 п) блоковвычисления итераций (где и - раз- Орядность аргумента), триггер, выходной коммутатор и выходной регистр,выход которого является выходомустройства, управляющий и информа"ционный нходы выходного регистра соединены соответственно с выходом блока управления и выходом выходногосумматора, второй вход которого соединен с выходом выходного коммутатора, первый и второй управляющие входы которого соединены соответственнос иннерсным и прямым выходами триггера, первый и второй информационныевходы нь.ходного коммутатора соединены соответственно с прямым и инверсным выходами промежуточного регистра,первый и второй входы блока управления соединены соответственно с нходом задания длины массива и пускаустройства, каждый блок вычисленияитерациисодержит два входных ре- ЗОгйстра, дна промежуточных коммутатора и два промежуточных сумматора,причем первый и второй входы каждогопромежуточного сумматора соединенысоответственно с прямым выходом соответствующего входного регистра ивыходом соответствующего промежуточного коммутатора, перный и второйуправляющие входы промежуточных коммутаторов соединены соответственно с 40инверсным и прямым выходами второговходного регистра, первый и второйинформационные входы первого промежуточного коммутатора соединены соот. ветственно с прямым и инверсным выходами первого входного регистра, управляющие входы первого и второго входных регистров соединены с выходомблока управления, информационныевходы первого и второго входных регистров первого блока вычисленияитерации соединены соответственно свходом начального значения функциии входом аргумента устройства, выходы первого и второго промежуточныхсумматоров К-го блока вычисления 55итерации (К 1,22 п) соединены синформационными входами соответственно первого и второго входных регистров (К+1)-го блока вычисления итерации, выходы первого и второго промежуточных сумматоров (2 п)-го блокавычисления итерации соединены с информационными входами соответственно промежуточного регистра и триггера, управляющие нходы которых соеди иены с выходом блока управления,первый и нторой информационные входывторого промежуточного коммутатораК-го блока вычисления итерации соединены с входами задания констант соответственно 1 п (1+2 ") и 2 п (1-2 " )устройства.Блок управленик содержит счетчик,элемент ИЛИ-НЕ, триггер, генераторимпульсов и элемент И, выход которого соединен с выходом блока упранления и счетным входом счетчика, информационный вход и выход которогосоединены соответственно с первымвходом блока управления и входом элемента ИЛИ-НЕ, ныход которого соединен с первым входом триггера, второй вход и выход которого соединенысоответственно с вторым входом блокауправления и первым входом элементаИ, второй вход которого соединен свыходом генератора импульсов,На фиг. 1 дана блок-схема конвейерного устройстваф на фиг. 2 - схема блока управления,Конвейерное устройство для вычисления функции уе" содержит блок1 вычисления итерации, регистры 2 и3 входные, коммутаторы 4 и 5 промежуточные, сумматоры 6 и 7 промежуточные, регистр 8, промежуточный триггер 9, коммутатор 10 выходной, сумматор 11 выходной, регистр 12 выходной, блок 13 упрайления, входы 14 и15 блока управления и выход 16 бло-.ка управления,Блок 13 управления содержит триггер 17, генератор 18 импульсе элемент И 19, счетчик 20 и элементИЛИ-НЕ 21.Алгоритм вычисления ех описывается следующими итерационными формулами ф- + 1 при 1 четном;г1+116( - ,и 1в .- при 1 нечетном; которые при начальных значениях уо1, хо = х дают после 2 п итераций у и ехпУстройство работает следующим образом.В первом также в регистр 2 первого блока 1 записывается константа +1, а в регистр 3 поступает значение операнда х в обратном коде в форме с фиксированной запятой, Если х ( 1, то= -1, то есть знаковый разряд регнстра 3 равен единице. Управляющий сигнал, поступающий с прямого выходазнакового разряда регистра 3, пропускает через коммутатор 4 обратноезначение содержимого регистра 2,сдвинутое на один разряд вправо, насумматор б и через схему коммутатора5 обратное значение кода Зп 1-2 ")на сумматор 7. На сумматоре б производится сложение числа +1, хранимогов регистре 2, с числом, поступающимс коммутатора 4. Поскольку зто,число равно -0,1, и поступает в обратномкоде, то на выходе сумматора б полу чается число 0,9. На сумматоре 7производится сложение обратных кодовоперанда х, поступающего из регистра 3, и значения Уп (1"2- ), то естьпроизводится вычитание из значениях значения Хп 1-2).Если же хО, то= +1, тоесть знаковый разряд регистра 3 равеннулю. управляющий сигнал, поступаю-щий с инверсного выхода знаковогоразряда регистра 3, пропускает черезкоммутатор 4 прямое значение содержимого регистра 2, сдвинутое наодин разряд вправо, на сумматор б,и через коммутатор 5 обратное значение кода Хп 1+2 ) на сумматор 7.На сумматоре б число +1, хранимоев регистре 2, суммируется с числом,поступающим с коммутатора 4, равным0,1, то есть формируется число 1,1.На сумматоре 7 производится сложение обратных кодов операнда х, поступающего из регистра 3, и значения1 п (1+2 "),Во втором такте производится запись результатов вычислений первогоблока 1 во второй запись полученного на сумматоре б числа р регистр2 второго блока 1 и запись полученного на сумматоре 7 числа в регистр3 второго блока 1. Одновременно врегистр 3 первого блока 1 поступаетзначение второго операнда.В первом блоке 1 производитсявыполнение первой итерации над вторым операндом, аналогичное выполненной в первом такте над первым операндом, а во втором блоке 1 выполняется вторая итерация над первым операндом. В третьем такте результатывычислений, полученные во втором блоке 1, записываются в третий блок 1.,а результаты первого блока 1 - вовторой. В регистр 3 первого блока 1поступает третий операнд, В первомблоке 1 выполняется первая итерациянад третьим операндом, во втором -вторая итерация над вторым операндом,в третьем - третья итерация над первым операндом, причем в третьемблоке 1 промежуточный результат скоммутатора 5 поступает на сумматорб со сдвиговым на два разряда вправо,а на сумматор 7 через коммутатор 5поступают значения 1 п 1+2 ) или1 п (1-2 ), см кем где 1 см - время суммирования на сум-,маторе,задержка информации коммутатором.Видно, что по быстродействию,предлагаемое устройство значительнопревосходят прототип при обработкемассивов чисел. Быстродействие повы-шено в 2,5 и раэ,Кроме того, в предлагаемом устройстве нет необходимости хранитьконстанты, количество которых равно 2 п, в блоках памяти, посколькуони подаются на коммутаторы устрой 55 В дальнейшем результаты предыдущих блоков поступают в последующиеблоки, а в первый блок поступаетновый операнд и т,д причем в каждом нечетном и следующем за ним бло 5 ке промежуточные результаты с коммутатора 4 поступают на сумматор б сосдвигом на один разряд вправо большим, чем в предыдущих двух блоках,а в выражениях логарифмов, которые1 О подаются монтажным способом.на коммутатор 5, степень двойки возрастаетна единицу,В 2 п-м такте сформированное насумматоре б (2 п)-го блока 1 выра 15 жение записывается в регистр 8, асодержимое знакового разряда сумматора 7 (2 п)-го блока 1 переписы.вается в триггер 9, сигналы с прямого и инверсного выходов которогоуправляют прохождением прямого или .инверсного значения регистра 8 черезкоммутатор 10 на сумматор 11 сосдвигом на (и) разряд., На сумматоре 11 формируется значение искомой5 Функции от первого операнда. Одновременно результаты обработки всехРпоследующих операндов сдвигаютсяна одну ступень вниз и производитсяих обработка".В (2 п+1)-м такте на выходном регистре 12 получается первый результат, и в дальнейшем в каждом тактена выход будет появляться новыйрезультат, то есть результат вычисления функции от первого операнда масЗ 5 сива чисел будет получен через 2 птактов, а от каждого последующегооперанда массива - через один такт.Тактовые импульсы, управляющие1работой устройства, генерирует блок46 13 управления. устройство работаетпо конвейерному принципу, поэтомув каждом такте в него можно вводитьновый операнд, а на выходе получатьновый результат вычисления. При обработке массивов чисел быстродействие устройства определяется длительностью такта обработки данных, которая равна задержке в одном блоке1 устройства и определяется выраже5 нием5 10 15 20 25 ЗО 35 ства монтажным способом, а также ненужен блок памяти для хранения микропрограмм сложного блока микропрограммного управления, так как управление устройством осуществляетсяот простого блока управления. Формула изобретения 1. Конвейерное устройство для вычисления функции у д е", содержащее блок управления, промежуточный регистр и выходной сумматор, первый вход которого соединен с прямым выходом промежуточного регистра, о тл и ч а ю щ е ес я тем, что, с целью повышения быстродейстния, в него введены (2 п) блоков вычисления итераций (где и - разрядность аргумента), триггер, выходной коммутатор и выходной регистр, выход кото" рого является выходом устройства, управляющий и информационный входы выходного регистра соединены соответственно с выходом блока управления и выходом выходного сумматора, второй вход которого соединен с выходом выходного коммутатора, первый и второй управляющие входы которого соединены соответственно с иннерсным и прямым выходами триггера, первый и второй информационные входы выходного коммутатора соединены соответственно с прямым и инверсным выходами промежуточного регистра, первый и второй входы блока управления соединены соответственно с входом задания длины массива и пуска устройства, каждый блок вычисления итерации содержит два входных регистра, два ромежуточных коммутатора и два промежуточных сумматора, причем первый и второй входы каждого промежуточного сумматора соецинены соответственно с прямым выходом соответствующего входного регистра и выходом соответствующего промежуточного коммутатора, первый и второй управляющие входы промежуточных коммутаторов соединены соответственно с инверсными прямым выходами второго входного регистра, первый и второй информационныв входы первого промеяюточного коммутатора соединены соответственно с прямым и инверсным выходами первого входного регистра,управляющнв нходы первого и второговходных регистров соединены с выходом блока управленияр информационные входы первого и второго входныхрегистров первого блока вычисленияитерации совдинены соответственнос входом начального значения функциии входом аргумента устройства, ныходыпервого и второго промежуточных сумматоров К-го блока вычисления итерации (К=1,22 п) соединены с информационными входами соответственнопервого и второго входных регистров(К+1)-го блока вычисления итерации,выходы первого и второго промежуточных сумматоров (2 п) -го блока вычиаления итерации соединены с информационными входами соответственно промежуточного регистра и триггера, управляющие входы которых соединены с выходом блока управления, первый и второй информационные входы второ" го промежуточного коммутатора К-го блока вычисления итерации соединены с входами задания констант соответственно Хп (1+2-" ) и 2 п (1-2 " ) устройства.2. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что блок управ-,ления содержит счетчик, элементИЛИ-НЕ, триггер генератор импульсови элемент И, выход которого соединен с выходом блока управления исчетным входом счетчика, информационный вход и выход которого соединены соответстненно с первым входом блокауправления и входом элемента ИЛИ-НЕ,выход которого соединен с первым входом триггера, второй вход и выходкоторого соединены соответственно свторым входом блока управления и первым входом элемента И, второй входкоторого соединен с выходом генератора импульсов,Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРРб 31924, кл, С Об Р 7/556, 1978.2. Байков В.Д Смолов В,Б. Агпаратурная реализация элементарныхфункций в УВМ. Из-во Ленинградскогоуниверситета, 1975,962927 Составитель А.ЗориТехред С,Мигунова Корректор А,ГРиден Редактор Т,Портная Подписное СР акаэ 7513/6 ВН/5 Филиал ППП "Патентф, г. Ужгород, ул. Проектная Тираж ПИ Государственн делам изобретен Москва, Ж, Ра

СмотретьЗаявка

3247823, 12.02.1981

ЛЬВОВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

МЕЛЬНИК АНАТОЛИЙ АЛЕКСЕЕВИЧ, ОСИПИШИН ИВАН САВВОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, конвейерное, функции

Опубликовано: 30.09.1982

Код ссылки

<a href="https://patents.su/6-962927-konvejjernoe-ustrojjstvo-dlya-vychisleniya-funkcii-ye.html" target="_blank" rel="follow" title="База патентов СССР">Конвейерное устройство для вычисления функции y=е</a>

Предыдущий патент: Устройство для логарифмирования

Следующий патент: Устройство для вычисления показательных функций

Случайный патент: Способ подготовки природного газа к дальнему транспорту