Устройство для обнаружения и исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 938415

Авторы: Бобин, Свенцицкий

Текст

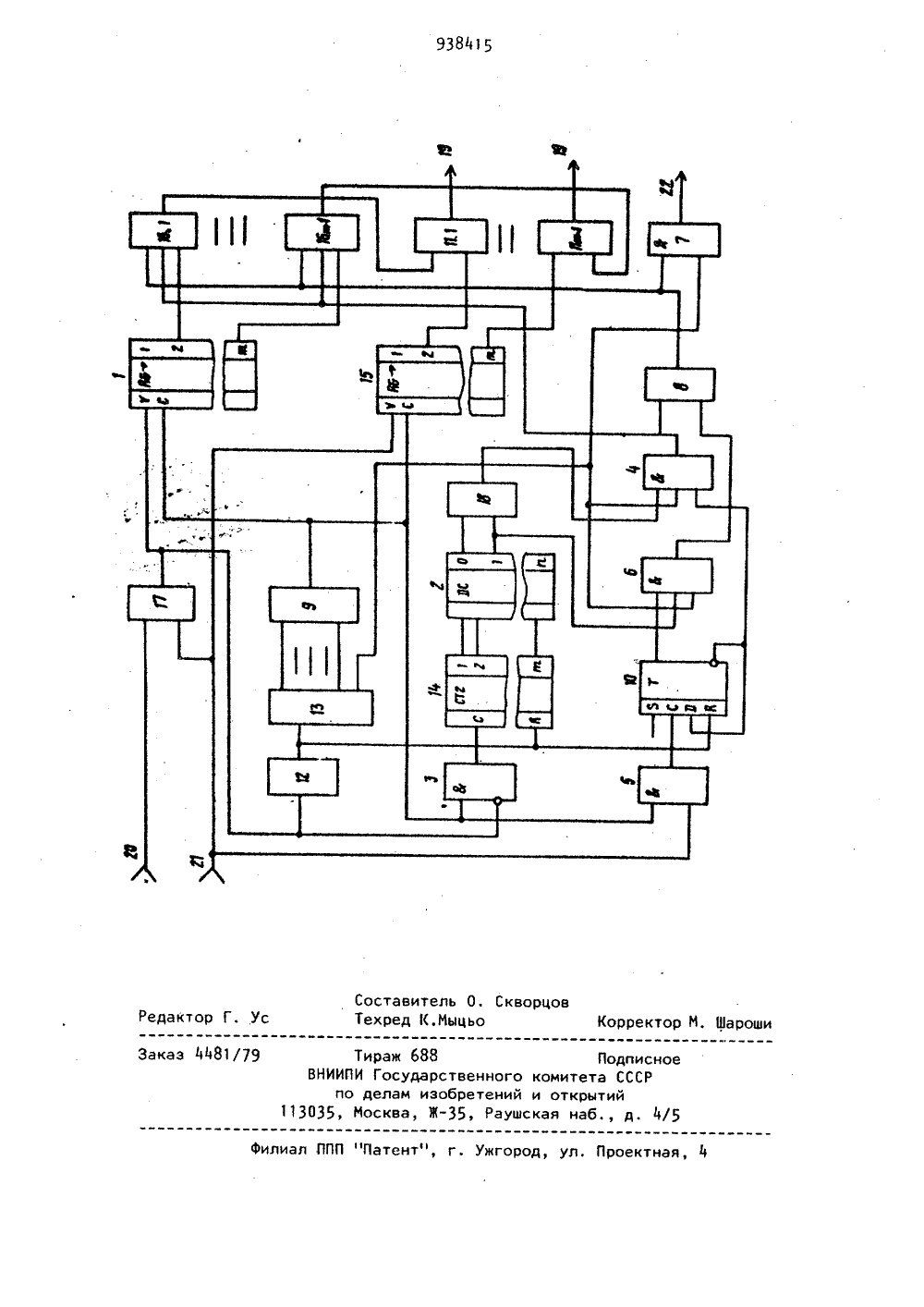

Союэ СоввтсиикСоциаяистичесиинРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 11 938415(51)М. Кл. Н 04 В 1/10 фкударстеаеий комитет ССЕР в леаам зобретеннй и етнрытнй(72) Авторы изобретения дТБйТ 40.ПЧЙВЧЗСКИС" ИЮ 1 Р 1 д П. Г. Бобин и Р. А. Свейф(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОВИБОК 1Изобретение относится к приему дискретной информации и может быть использовано в телемеханических системах, автоматизированных системах управления, в системах связи.Известно устройство для обнаружения и исправления ошибок, содержащее приемник, канальные фильтры, амплитудные селекторы, селектор синхронизирующего импульса, распределитель тактовых импульсов, схему ИЛИ, промежуточный и выходной регистры 111;Недостатками этого устройства являются низкое быстродействие и малая достоверность приема информации.Кроме того, в устройстве для обнаружения и исправления систематических кодов время приема и обработки кодового слова возрастает вдвое из-за приема дополнительных контроль-щ ных символов после приема информационных.Устройство для обнаружения и исправления циклических кодов должно 2работать от двух последовательностей тактовых импульсов. При этом частота первой последовательности равна скорости передачи информации по каналу связи, а частота второй последовательности В К раз выше (К - число информационных импульсов в кодовой комбинации).Наиболее близким к изобретению по технической сущности является устройство для обнаружения и исправления ошибок, состоящее из четырех счетчиков, дешифратора на четыре входа и шесть выходов и схемы исправления, выходы которой соединены с информационными выходами устройства, а входы соединены соответственно с выходами дешифратора и выходами группы элементов И, первые входы которых соединены с управляющим выходом распределителя, а вторые входы с выхо дами соответствующих триггеров наборного устройства, установочные входы которых соединены соответственно с3 93841 выходами первых двенадцати элементов И наборного устройства, первые входы которых соединены соответственно с первым и вторым выходом триггера входного устройства, а вторые входы 5 соединены с первыми шестью выходами распределителя, последние четыре выхода которых соединены соответственно с вторыми входами последних четырех элементов И наборного устройства, 10 первые входы которых соединены с первым выходом триггера входного устройства, а выходы соединены соответственно с первыми входами группы элементов ИЛИ, остальные входы которых 15 . соединены с установочными входами соответствующих триггеров наборного устройства, а выходы соединены с входами соответствующих счетчиков, выходы которых соединены с входами де шифратора 1,2 .Недостатком известного устройства является значительное увеличение длины кодовой комбинации за счет контрольных символов, количество которых зависит от длины слова,. что значительно усложняет устройство для обнаружения и исправления ошибок и увеличивает время обработки кодовой комбинации.Все это, приводит к снижению эффективности использования каналов связи и достоверности выявления ошибок. Цель изобретения - повышение достоверности выявления ошибок. 35Поставленная цель достигается тем, что в устройство, содержащее регистр, дешифратор, первый, второй, третий, четвертый и пятый элементы И, первый и второй элементы ИЛИ счетный триггер 10 и группу элементов ИСКЛОЧМОЩЕЕ ИЛИ, выходы которых соединены с информационными выходами устройства, введены формирователь, распределитель, счетчик, дополнительный регистр, до полнительная группа элементов ИСКЛОЧАЮЩЕЕ ИЛИ, а также первый и второй вспомогательные элементы ИСКЛОЧАЮЩЕЕ ИЛИ, первый вход устройства соединен с первым входом первого вспомогатель ного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом регистра, входом формирователя и запрещающим входом первого элемента И, выход которого соединен со счет ным входом счетчика, выходы которого соединены с входами дешифратора, нулевой и единичный выходы которого 5 фсоединены с первым и вторым входами второго вспомогательного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ и первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых сое-: динены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с выходами дополнительного регистра, информационный вход которого соединен с вторым входом первого вспомогательного элемента ИСКЛОЧАЮЩЕЕ ИЛИ, вторым входом устройства и первым входом третьего элемента И, второй вход которого соединен с вторым входом первого элемента И, тактовыми входами регистра и дополнительного регистра и выходом второго элемента ИЛИ, входы которого соединены с выходами распределителя, вход которого соединен с выходом формирователя и входами сброса счетцика и счет" ного триггера, счетный вход и выход которого соединены соответственно с выходом третьего элемента И и первым входом четвертого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом пятого элементаИ, выход и второй вход которого соединены соответственно с управляющим выходом устройства и дополнительным выходом распределителя, который соединен с вторыми входами второго и четвертого элементов И, третьи входы которых соединены соответственно с инверсным выходом счетного триггера и единичным выходом дешифратора, а третьи входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛОЧАЮЩЕЕ ИЛИ соединены с выходами регистра.На чертеже представлена схема устройства для обнаружения и исправления ошибокУстройство включает регистр 1, дешифратор 2, первый 3, второй 4, третий 5, четвертый 6 и пятый 7 элементы И, первый элемент ИЛИ 8 и второй элемент ИЛИ 9, счетный триггер 10, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11, формирователь 12, распределитель 13, счетчик 14, дополнительный регистр 15, дополнительную группу элеСигналами, сформированными вторым элементом ИЛИ 9, происходит запись результатов проверки на идентичность четных и нечетных элементов ко" да в регистр .1, запись нечетных эле" ментов кода в дополнительный регистр 15, подсчет элементов кода, подвер,женных однократному искажению, счет" чиком 14, проверка на четность нечетных элементов кода счетным триггером 10. 9384 ментов ИСКЛЮЧАЮЩЕЕ ИЛИ 16, а также первый 17 и второй 18 вспомогательные элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 соединеныс информационными выходами 19 устройства, первый вход 20 устройства соединен с первым входом первого вспомогательного элемента ИСКЛЮЧАЮЩЕЕИЛИ, выход которого соединен с информационным входом регистра 1, входом 1 Зформирователя 12 и запрещающим входом первого элемента И 3, выход которого соединен со счетным входом счетчика 14, выходы которого соединены свходами девифратора 2, нулевой и.единичный выходы которого соединены спервым и вторым входами второго вспомогательного элемента ИСКЛЮЧАЮЩЕЕИЛИ 18, выход которого соединен с первым входом второго элемента И 4, 26выход которого соединен с первымвходом первого элемента ИЛИ 8 и первым входами элементсв ИСКЛЮЧАЮЩЕЕИЛИ 16, дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с выходами дополнительного регистра 15, информацион- Эв ный вход которого соединен с вторым входом первого вспомогательного элемента ИЛИ 17, вторым входом 21 устройства и первым входом третьего элемента И 5, второй вход которого соеди 1 э нен с вторым входом первого элемента И 3, тактовыми входами регистра 1 идополнительного регистра 15 и выходом второго элемента ИЛИ 9, входы которого соединены с выходами распределителя 13, вход которого соединен с выходом формирователя 12 и входамисброса счетчика 14 и счетного триггера 10, счетный вход и выход которогосоединены соответственно с выходом третьего элемента И 5 и первым входом четвертого элемента И 6, выход которого соединен с вторым входом первогоэлемента ИЛИ 9, выход которого соединен с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и с первым входом пятого элементов И 7, выход и второй вход которого соединеныИ соответственно с управляющим выходом 22 устройства и дополнительным выходом распределителя 13, который соединен со вторыми входами второго 4 и 156четвертого 6 элементов И, третьи вхо ды которых соединены соответственно с инверсным выходом счетного триггера 10 и единичным выходом дещифратора 2, а третьи входы элементов ИСКЛО" ЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 соединены с выходами регистра 1.Устройство для обнаружения и исправления оеибок работает следующим образом.По приходу синхронизирующего сиг" нала, отличающегося от информацион" ного .больаей длительностью, срабатывает формирователь 12, сигналом с выхода которого запускается распреде" литель 13, обнуляется счетчик Й и счетный триггер 10, тем самым подго" тавливая устройство к приему кодового слова.Принимаемая кодовая последовательность, образованная из четных и нечетных элементов кода, поступает соответственно на первый и второй вход устройства, проверяется на идентичекть первым вспомогательным элементом ИСКЛОЧМЮЕЕ ИЛИ 17, сигналы с выхода которого поступают на вход формирователя 12, информационный вход регистра 1, служащего для регистрации разрядов кода, в которых произовло искажение и.запрещающий вход первого элемента И 3, служащего для формирования сигналов записи количества элементов кода, подверженных искажение. Кроме того, сигналы нечетныхэлементов кода, приходящих на второй вход устройства, поступают также на информационный вход дополнительного регистра 15, служащего для промежуточного хранения принимаемой информации, и на первый вход третьего элемента М 5, служащего для формирования сигналов, поступающих на вход счетного триггера. 10.По окончанию приема кодового слова на последнем такте распределителя 13 происходит анализ принятого сообщения на достоверность, выявление и исправление ошибки. 5Анализ сообщения о наличии искажения кодового слова происходит по сопоставлению состояний выходных сигналов дешифратора 2 и счетного триггера 10.10Возможны следующие случаи искажений в зависимости от этих состояний.Наличие сигнала на нулевом и единичном выходе дешифратора 2 и нулевое состояние счетного триггера 10 показывает, что искажений в кодовом слове нет при наличии сигнала на нулевом выходе дешифратора 2 и имеет место искажение одного четного элемента кода при наличии сигнала на 20 единичном выходе дешифратора 2,При наличии сигнала на единичном выходе дешифратора 2 и единичного состояния счетного триггера 10 говорит о том, что произошло искажение одного нечетного элемента кода.Наличие сигнала на нулевом выходе дешифратора 2 и единичного состояния счетного триггера 10 показывает наличие искажения четных и нечетных эле ментах кода в одинаковых разрядах кодовой комбинации нечетной кратности.Отсутствие сигналов на нулевом и единичном выходе дешифратора 2 незави- З 5 симо от состояния счетного триггера 10 говорит о искажении четных и нечетных элементов кода не в одинаковых разрядах кодовой комбинации четной или нечетной кратностй, 30 Сигнал о наличии искажения одного четного элемента кода или отсутствия искажения формируется вторым вспомогательным элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 1845 и вторым элементом И 4. Четвертым, элементом И 6 Формируется сигнал наличия искажения одного нечетного элемента кода.Если имеется наличие искажения од 50 ного четного элемента кода или отсутствие искажения кода, то на два входа каждого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 поступают единичные сигналы, сформированные вторым элемен-5 том И 4 и первым элементом ИЛИ 8, поэтому на выходе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы эле 15 8ментов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 будут нуле" .вые сигналы, которые поступают на первые входы элементов ИСКЛОЧАЮЩЕЕ ИЛИ 11, На вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы элементов ИСКЛОЧАЮЩЕЕ ИЛИ 11 поступают сигналы с выхода дополнительного регистра 15. Поэтому на информационные выходы на последнем такте распределителя 13 информация поступает без исправления.Если имеется наличие искажения одного нечетного элемента кода, говорящее о том, что принятая и записанная в дополнительный регистр 15 информация недостоверна, то на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11 поступают следующие сигналы: нулевой сигнал на первые входы с выхода второго элемента И 4; единичный сигнал на вторые входы с выхода первого элемента ИЛИ 8, на третьи выходы поступают сигналы с выхода регистра 1.1Так как нулевой. сигнал с выхода регистра 1 говорит о наличии искажения в данном разряде кода, а единичный сигнал - об отсутствии искажения в данном разряде, то на выходах тех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 будут нулевые сигналы, на третьи входы которых поступают единичные сигналы с выходов регистра 1, и единичные сигналы у тех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, на третьи входы которых поступают нулевые сигналы с выхода дешифратора 2, говорящие о том, что в этом разряде кодового слова произошло искажение. Поэтому на последнем такте распределителя при наличии искажения одного нецетного элемента кода произойдет исправление единичной ошибки. Исправит ошибку тот элемент ИСКЛЮЧАЮЩЕЕ ИЛИ группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11, на вход которого поступает единичный сигнал с соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 16.Сигнал считывания информации, который поступает на управляющий выход устройства, формируется пятым элементом Ина последнем такте распределителя при наличии единичных сигна9384лов на выходе второго 4 или четвертого элементов И 6.Если имеет место искажение четных и нечетных элементов кода в одинаковых разрядах кодовой комбинации не четной кратности или искажение нескольких четных и нечетных элементов кода не в одинаковых разрядах кодовой комбинации четной или нечетной кратности, то формирование сигнала считывания информации не происходит и сообщение бракуется.Таким образом, устройство позволяет обнаруживать все ошибки нечетной кратности, часть ошибок четной кратности, а также исправлять однократные ошибки при увеличении времени передачи сообщения только на величину длительности одного единичного символа, При этом достоверность 20 учетной и управляющей информации повышается на порядок в относительных единицах,25Формула изобретенияУстройство для обнаружения и исправления ошибок, содержащее регистр, дешифратор, первый, второй, третий, зо четвертый и пятый элементы И, первый и второй элементы ИЛИ, счетный триггер и группу элементов ИСКЛОЧАЮЩЕЕ ИЛИ, выходы которых соединены с инФормационными выхОдами устрОЙствдр 35 о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности выявления ошибок, в него введены формирователь, распределитель, счетчик, дополнительный регистр, дополнитель в ная группа элементов ИСКЛЮЧАОЦЕЕ ИЛИ, а также первый и второй вспомогательные элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход устройства соединен с первым входом первого вспомогательного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ выход которого соединен с информационным входом регистра, входом формирователя и запрещающим входом первого элемента И, выход которого соединен со счетныМ 5 В входом счетчика, выходы которого соединены с входами дешифратора, нулевой и единичный выходы которого соединены 110с первым и вторым входами второго вспомогательного элемента ИСКЛЮЧАОЦЕЕ ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ и первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй входы которых соединены с выходами дополнительного регистра, информационный вход которого соединен с вторым входом первого вспомогательногоэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторым входом устройства и первым входом третьего элемента И, второй вход которого соединен с вторым входом первого элемента И, тактовыми входами регистра и дополнительного регистра и выходом второго элемента ИЛИ, входы которого соединены с выходами распределителя, вход которого соединен с выходом Формирователя и входами сброса счетчика и счетного триггера, счетный вход и выход которого соединены соответственно с выходом третьего. элемента И и первым входом четвертого элемента И, выход которого соединенс вто" рым входом второго элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, выход и второй вход которого соединены соответственно с управляющим выходом устройства и дополнительным выходом распределителя, который соединен с вторыми входами второго и четвертого элементов И, третьи входы которых соединены соответственно с инверсным выходом счетного триггера и единичным выходом дешифратора, а третьи входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ дополнительной группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами регистра. Источники информации,принятые во внимание при экспертизе1. Тутевич В. Н. Телемеханика. И., "Энергия"., 1973.2. Шляпоберский В. И. Основы техники передачи дискретных сообщений. И., "Связь, 1973 (прототип).938415 оставитель О. Скворцовехред К,Иыцьо Кор рек Шароши едактор Г, Ус Заказ 4 наб д. илиал ППП "Патент", г. Ужгород, ул. Прае Тираж 688 ВНИИПИ Государственного ко по делам изобретений и 13035, Москва, И, Раушска

СмотретьЗаявка

2972431, 13.08.1980

УРАЛЬСКОЕ ПРОИЗВОДСТВЕННО-ТЕХНИЧЕСКОЕ ПРЕДПРИЯТИЕ "УРАЛЭНЕРГОЧЕРМЕТ"

БОБИН ПЕТР ГРИГОРЬЕВИЧ, СВЕНЦИЦКИЙ РУДОЛЬФ АДОЛЬФОВИЧ

МПК / Метки

МПК: H04B 1/10

Метки: исправления, обнаружения, ошибок

Опубликовано: 23.06.1982

Код ссылки

<a href="https://patents.su/6-938415-ustrojjstvo-dlya-obnaruzheniya-i-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и исправления ошибок</a>

Предыдущий патент: Устройство для формирования импульсной последовательности

Следующий патент: Устройство контроля качества дискретных каналов связи с переменными параметрами

Случайный патент: Патронный фильтр