Преобразователь перемещения в код

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1777240

Автор: Авакян

Текст

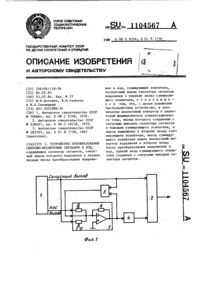

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУбЛИК 1777240 3)5 Н 03 М 1/24, 1/ ЕТЕН ОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОбРЕТЕНИЯМ И ОТКРЫТИЯМРИ ГКНТ СССР(56) Авторское свидетельство СССР М 1424123, кл. Н 03 М 1/24, 1986.Авторское свидетельство СССР М 1711328, кл, Н 03 М 124, Н 03 М 1 П 8, 1988.(57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах программного управления станками и радиотелескопами. Целью изобретения является повышение точности преобразователя, Для этого в Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах программного управления станками и радиотелескопами.Целью изобретения является повышение точности преобразователя,На фиг.1 представлена структурная схема преобразователя; на фиг,2 - функциональная схема формирователя напряжений смещения; на фиг.3 - диаграммы, поясняющие работу преобразователя перемещения в код; на фиг, 4 - функциональная схема формирователя корректирующего сигнала; на фиг, 5 - формирователь амплитуды; на фиг. 6 - формирователь кода адреса,Преобразователь перемещения в код содеркит первичный преобразователь 1 перемещения в аналоговые сигналы, содержащий блок 1 перемещения в аналоговые преобразователь перемещения в код, содержащий первичный преобразовательперемещения в аналоговые сигналы, фотоприемники, суммирующие усилители, инверторы, компараторы, формирователь напряжения смещения, первый формирователь корректирующего сигнала, формирователи амплитуд, элемент ИСКЛЮЧАЮЩЕГО ИЛИ, селектор сигналов октантов и аналогоцифровой преобразователь, дополнительно, введены второй формирователь корректирующего сигнала, формирователь кода адреса, постоянное запоминающее устройство и распределитель импульсов, Введение новых блоков и соответствующих связей позволяет разбить весь диапазон преобразования на отдельные области, в которых осуществляется коррекция сигнала. 3 э.п. ф-л ы, 6 ил. сигналы, содержащий блок 2 излучателей, измерительный 3 и индикаторный 4 диски, фотоприемники 5 и 6 и усилители 7 и 8, суммирующие усилители 9 и 10, инверторы 11 и 12, компараторы 13 и 14, формирователь 15 напрякений смещения, формирователи 16 и 17 корректирующих сигналов, формирователи 18-21 амплитуд, элемент 22 И СКЛ ЮЧАЮЩЕ Е ИЛ И, селектор 23 сигналов октантов, содержащий аналоговые коммутаторы 24 и 25, компаратор 26, элемент 27 ИСКЛЮЧАЮЩЕЕ ИЛИ, аналого-цифрой преобразователь (АЦП) 28, формирователь 29 кода адреса, постоянное запоминающее устройство 30 и распределитель 31 импульсов,Формирования содержит рлоговые пре тель 15 напряжений смещеегистры 32 и 33, цифроанаобразователи 34 и 35, 177724055 источники 36 и 37 опорного напряжения, блок 38 делителей напряжения, суммирующие усилители 39 и 40.Каждый иэ формирователей 16 и 17 корректирующих сигналов содержит регистр 41, цифроаналоговый преобразователь 42, делитель 43 и суммирующий усилитель 44.Каждый из формирователей амплитуд 18-21 содержит регистр 45 и цифроаналоговый преобразователь 46.Формирователь 29 кода адреса содержит формирователи 47 и 48 прямых и инвертированных .прямоугольных импульсов, формирователи 49 и 50 импульсов переднего и заднего фронта, блок 51 формирования счетных импульсов, реверсивный счетчик 52, генератор 53 и счетчик 54,Преобразователь работает следующим образом.Световой поток от блока 2 излучателей через щели. измерительного 3 и индикаторного 4 дисков попадает на чувствительные площадки фотоприемников 5 и 6, на которых выделяются электрические сигналы, пропорциональные падающему на них световому потоку. Эти сигналы усиливаются усилителями 7 и 8 и поступают на выходы первичного преобразователя 1. При вращении вала преобразователя излучение модулируется растровым сопряжением и на выходах первичного преобразователя 1 образуются сигналы 01 и 02, по форме близкие к синусоидальным (фиг.3 а, б). Сигналы 01 и 02 поступают на входы суммирующих усилителей 9,10, на вторые входы которых поступают напряжения смещения Оо 1 и Оо 2, вырабатываемые формирователем 15 напряжения смещения. В идеальном случае на выходах усилителей 9, 10 выделяются сигналы Оз и 04, симметричные относительно нуля и по форме повторяющие сигналы 01 и 02 (фиг.Зв,г). Компараторы 13 и 14, работающие в режиме нуль-органа, формируют иэ сигналов Оз и О логические сигналы, первый иэ которых является сигналом первого разряда выходного кода, а второй смещен относительно первого на четверть шага измерения (фиг, 3 д,е). Логические сигналы,суммируясь по модулю два элементом 22 ИСКЛЮЧАЮЩЕЕ ИЛИ, образуют на его выходе сигнал второго разряда выходного кода (фиг.Зж),Прямые и инвертированные инверторами 11 и 12 сигналы Оз и 04 через формирователи ",8-21 амплитуд, а кроме того, сигнал О непосредственно с выхода усилителя 10 поступают на входы аналогового коммутатора 24 селектора 23 сигналов октантов. Коммутатор 24 управляется сигналами пер 5 10 15 20 25 30 35 40 вого и второго разрядов выходного кода таким образом, что на одном из его выходов при низком уровне сигнала первого разряда выделяется прямой сигнал Оз, поступающий с выхода формирователя 18, а при высоком уровне - инвертированный сигнал Оз с выхода формирователя 19 (фиг.З э).На другом выходе коммутатора 24 при разных уровнях сигналов первого и второго разрядов выходного кода выделяется инвертированный сигналОа с выхода формирователя 20, при низких уровнях сигналов первого и второго разрядов - прямой сигнал 04 с выхода усилителя 10, а при высоких уровнях - прямой сигнал 04 с выхода формирователя 21 (фиг. 3 и). Сигналы 05 и 05, выделяемые на выходах коммутатора 24, сравниваются по величине компаратором 26, на выходе которого формируется логический сигнал, смещенный относительно сигнала второго разряда выходного кода на четверть шага (фиг. 3 к). Эти сигналысуммируются по модулю два элементом 27 ИСКЛЮЧАЮЩЕЕ ИЛИ, на выходе которого образуется третий разряд выходного кода (фиг, 3 л). Сигналы 05 и Оо поступают также на входы аналогового коммутатора 25, который управляется логическим сигналом, формируемым компаратором 26 таким образом, что на его выход поступает сигнал 05 при низком уровне логического сигнала, а при высоком уровне - сигнал Оо (фиг.З м). С выхода коммутатора 25 аналоговый сигнал, по форме близкий к треугольному, поступает на вход АЦП 28, где формируются младшие разряды выходного кода.При линейно возрастающей ветви аналогового сигнала на выходе АЦП 28 вырабатывается прямой код, а при линейно убывающей ветви код на выходе АЦП 28 инвертируется сигналом третьего разряда выходного кода,Младшие разряды кода могут быть также сформированы АЦП 28, как отношение аналогового сигнала на выходе коммутатора 25 и другого аналогового сигнала, полученного преобразованием сигналов 05 и Оо при помощи аналогового коммутатора, управляемого таким образом, что при низком уровне сигнала на выходе компаратора 26 выделяется сигнал Ов, а при высоком - сигнал 05. В обоих случаях остаточная погрешность преобразования в пределах октантов при необходимости может быть устранена с помощью ПЗУ,В реальных преобразователях перемещения в код имеет место отклонение фазового сдвига между сигналами 01 и 02 от номинального значения (л/2) и его изменение в диапазоне измерений, что обусловле 17772405 10 15 30 40 45 50 но погрешностями, возникающими при нанесении штрихов на оригиналы индикаторного 4 и измерительного 3 дисков, процессом фотолитографии и наличием остаточного эксцентриситета дисков 3 и 4. Кроме того, изменение соотношения площадей прозрачных и непрозрачных штрихов на разных участках дорожки измерительного диска 3 приводит к изменению формы и среднего уровня Оср полного размаха сигналов в пределах диапазона измерения. Поэтому при формировании прямоугольных сигналов по уровню, обеспечивающему точное угловое положение фронтов этих сигналов в одной области измерения, в других областях возникают погрешности, приводящие также к погрешностям и внутри шага измерения.В устройстве для каждой области измерений, где погрешность формирования прямоугольных сигналов иэ сигналов 01 и 02 превышает заданную, формирователем 15 напряжений смещения вырабатываются постоянные напряжения 001 и 002, поступающие на вторые входы суммирующих усилителей 9 и 10. Напряжения 001 м 002 выбираются равными по величине значениям сигналов 0 1 и О 2 соответственно при углах, отстоящих на величину л, и обратными по знаку, В результате на выходах суммирующих усилителей 9 и 10 формируются сигналы 01 и 02, принимающие нулевые значения при углах с периодом л, но в общем случае смещенные один относительно другого на величину, не равную л/2.Формирование напряжений смещения осуществляется следующим образом, От источника 37 опорного напряжения через делители 38 на входы суммирующихусилителей 39 и 40 поступает постоянное напряжение, величина которого соответствует нижней границе требуемого напряжения смещения во всем диапазоне измерения.На вторые входы суммирующих усилителей 39 и 40 поступают постоянные напряжения, сформированные перемножающими ЦАП 34 и 35, аналоговые входы которых подключены к источнику 36 опорного напряжения. Величина опорного напряжения выбирается таким образом, чтобы при максимальном значении кода (111,11) на входах ЦАП 34 и 35 напряжения на выходах суммирующих усилителей 39 и 40 соответствовали верхней границе требуемого напряжения смещения во всем диапазоне измерения. Таким образом, при изменении кода, поступающего на входы ЦАП 34 и 35 с выходов регистров 32 и 33, от минимального значения (00.00) до максимального значения (1111) величины напряжений смещения 001 и 002 на выходах формирователя 15 изменяются в диапазоне ЬО 01 и Л 002 (фиг,З а). Значения кодовых комбинаций, при которых сигналы 01 и 02 в определенной области измерения принимают нулевые значения при углах с периодом д(с допустимой погрешностью), фиксируются регистрами 32 и ЗЗ и остаются неизменными в данной области. Значения угла, при которых сигналы 01 м 02 принимают нулевые значения, могут отличаться от теоретических на величину, превышающую допустимую погрешность преобразования, причем в различных областях диапазона измерения на различную величину. Эти погрешности устраняются суммированием сигналов 01 и 02 с сигналами, вырабатываемыми формирователями 16 и 17 корректирующих сигналов и поступающими на входы суммирующих усилителей 9 и 10 соответственно.Формирователи 16 и 17 корректирующих сигналов работают следующим образом. С выхода суммирующего усилителя 10 на аналоговый вход перемножающего ЦАП 42 подается сигнал 04, который с выхода ЦАП 42 поступает на один из входов суммирующего усилителя 44, На второй вход суммирующего усилителя 44 через делитель 43 напряжения поступает инвертированный сигнал 04 с выхода 12. При коэффициенте деления делителя 43, равном двум, и изменении кода на входах ЦАП 42, поступающего с выходов регистра 41, от значения 00.00до 1111 на выходе формирователя 16вырабатывается корректирующий сигнал, соответствующий прямому или инвертированному сигналу 04, меняющийся по величине от 04/2 до О, Таким образом, сигнал 01 суммируется в усилителе 9 с частьюсигнала 04, сдвинутого относительно сигнала 01 на величину, близкую л/2, что приводит к смещению значений углов, при которых сигнал Оз принимает нулевые значения, Кодовые комбинации, при которых сигнал Оз в определенных областях измерения принимает нулевое значение при углах, отличающихся от теоретических на допустимую величину, фиксируются регистром 41 и остаются неизменными в этих областях.Аналогичным образом формирователем 17 вырабатывается корректирующий сигнал, представляющий собой часть прямого или инвертированного сигнала Оз, который суммируется с сигналом 02 усилителем 10. Код, фиксируемый регистром 41 формиро 177724010 15 20 30 40 вателя 17, выбирается таким, чтобы сигнал О 4 принимал нулевые значения с допустимой погрешностью при углах, смещенных на к/2 относительно аналогичных значений сигнала Оз.Для устранения влияния асимметрии сигналов Оз и 04 относительно оси абсцисс, а также каждой из полуволн этих сигналов относительно экстремумов на точность формирования фронтов логического сигнала на выходе компаратора 26 прямые и инвертированные сигналы Оз и О 4 поступают на входы аналогового коммутатора 24 через формирователи амплитуд 18-21,Величина сигналов на выходах Формирователей 18-21 амплитуд, поступающих на аналоговые входы перемнокающих ЦАП 46, определяется значением кода на цифровых входах ЦАП 46, соединенных с выходами регистров 45.Значение кода выбирается таким, чтобы в пределах определенной области измерений (с требуемой точностью) при угле к/4 величина прямого сигнала Оз была равной величине прямого сигнала Од на выходе суммирующего усилителя 10; при угле 3/4 Л величина инвертированного сигнала О 4 - равной величине прямого сигнала Оз на выходе формирователя 18; при угле 5/4 л величина инвертированного сигнала Оз- равной величине прямого сигнала О 4 на выходе формирователя 21, при угле 7/4 л величина прямого сигнала Од - равной величине инвертированного сигнала Оз на выходе формирователя 19. Эти значения кодов фиксируются регистрами 45 формирователей 18-21 и в пределах данной области измерения остаются неизменными.Вся совокупность значений кода, поступающих на входы регистров 45 формирователей 18-21, для всех областей измерения, где осуществляется коррекция сигналов, записывается в ПЗУ 30. Выбор соответствующего значения кода осуществляется кодом адреса, который вырабатывается формирователем 29 кода адреса, имеющим две группы выходов. Ка выходах одной группы при помощи генератора 53 и счетчика 54 Формируется трехразрядный двоичный код, поступающий, помимо входов ПЗУ 30, на входы распределителя 31 импульсов.На каждом из восьми выходов распределителя 31, подключенных к тактовым входам соответствующих регистров, выделяется импульс записи в регистр, соответствующий одной из восьми кодовых комбинаций кода адреса. Распределитель 31 работает таким образом, что импульс записи поступает на регистр Формирователя 15-21, для которого предназначена информация, записанная в ПЗУ 30 по адресу, код которого соответствует импульсу записи. На выходах другой группы формирователя 29 вырабатывается код адреса, определяющий область измерений, к которой относится совокупность из восьми кодовых комбинаций, записанных в ПЗУ 30 по этому адресу.Кодадреса этой группы выходо формирователя 29 формируется следующим образом, Аналоговые сигналы О и О 2 с выходов преобразователя 1 поступают на входы формирователей 47 и 48, где выделяются прямые и инвертированные прямоугольные сигналы, сформированные по среднему,уровню сигналов О 1 и О 2. Прямоугольныесигналы с выходов формирователей 47 и 48 поступают на формирователи 49 и 50 импульсов переднего и заднего Фронта, из которых образуются последовательности счетных импульсов блоком 51. Блок 51, на входы которого поступают, помимо импульсов переднего и заднего фронтов, еще прямые и инвертированные прямоугольные импульсы с выходов формирователей 47 и 48, работает таким образом, что при перемещении измерительного диска в одном направлении счетные импульсы выделяются на выходе, подключенном к суммирующему входу реверсивного счетчика 52, а при перемещении измерительного диска в обратномнаправлении счетные импульсы выделяются на выходе блока 51, подключенном к вычитающему входу счетчика 52. На выходах счетчика 52, которые являются группой выходов формирователя 29, вырабатывается код, представляющий собой цифровой эквивалент величины перемещения, Угловой эквивалент импульса старшего разряда счетчика 52 соответствует половине диапазона измерений. Число сгарших разрядов счетчика 52, используемых в качестве кода адреса, определяет число областей коррекции, равное числу возможных комбинаций этого кода. Число областей коррекции определяется параметрами сигналов 01 и О 2 во всем диапазоне измерений, а также величиной допустимой погрешности преобразователя перемещения в код. Формула изобретения 1. Преобразователь перемещения в код,содержащий первичный преобразовательперемещения в аналоговые сигналы, первый и второй выходы которого соединены с первыми входами соответственно первого и второго суммирующих усилителей, вторые входы которых подключены соответственно к первому и второму выходам Формировате 1777240 105 10 20 25 30 40 45 50 ля напряжений смещения, выход первого суммирующего усилителя соединен с информационным входом первого формирователя амплитуды, с первым входом первого компэратора, с первым информационным входом первого формирователя корректирующего сигнала и с входом первого инвертора, выход которого соединен с информационным входом второго формирователя амплитуды и с вторым информационным входом первого формирователя корректирующего сигнала, выход которогосоединен с третьим входом второго суммирующего усилителя, выход которого соединен с первым информационным входом селектора сигналов октантов, с информационным входом третьего формирователя амплитуды, с первым входом второго компаратора и с входом второго инвертора, выход которого соединен с информационным входом четвертого формирователя амплитуды, выходы первого, второго, третьего и четвертого формирователей амплитуды соединены соответственно с вторым третьим, четвертым и пятым информационными входами селектора сигналов октантов, вторые входы компаратора соединены с шиной нулевого потенциала, выход первого компаратора является выходом первого разряда преобразователя и соединен с первым управляющим входом селектора сигналов октантов и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу второго компаратора, а выход является выходом. второгоразряда преобразователя и соединен с вторым управляющим входом селектора сигналов октантов, первый выход которого является выходом третьего разряда преобразователя и соединен с управляющим входом аналого-цифрового преобразователя, а второй выход соединен с информационным входом аналого-цифрового преобразователя, выходы которого являются выходами разрядов преобразователя, начиная с четвертого, о т л и ч а ю щ и й с я тем, что, с целью повышения точности преобразователя, в него введены второй формирователь корректирующего сигнала, формирователь кода адреса, постоянное запоминающее устройство и распределитель импульсов, первый и второй выходы которого соединены с одноименными тактовыми входами формирователя напряжений смещения, управляющие входы которого объединены с одноименными управляющими входами каждого из формирователей амплитуды икаждого из формирователей корректирующего сигнала и подключены к одноименным выходам постоянного запоминающего устройства, первый и второй выходы первичного преобразователя перемещений в аналоговые сигналы соединены с одноименными входами формирователя кода адреса, первая группа выходов которого соединена с первой группой входов постоянного запоминающего устройства, а вторая группа выходов соединена с второй группой входов постоянного запоминающего устройства, и с входами распределителя импульсов, третий и четвертый выходы которого соединены с тактовыми входами соответственно первого и второго формирователей корректирующего сигнала, а пятый, шестой, седьмой и восьмой выходы соединены с тактовыми входами соответственно первого, второго, четвертого и третьего формирователей амплитуды, выход второго суммирующего усилителя соединен с первым информационным входом второго формирователя корректирующего сигнала, выход которого соединен с третьим входом первого суммирующего усилителя, а второй информационным вход подключен к выходу второго инвертора. 2, Преобразователь по п. 1, о т л и ч а ющ и й с я тем, что формирователь напряжений смещения содержит два регистра, два цифроаналоговых преобразователя, два источника опорного напряжения, блок делителей напряжения и два суммирующих усилителя, информационные входы регистров обьединены и являются управляющими входами формирователя, тактовые входы первого и второго регистров являются соответственно первым и вторым тактовыми входами формирователя, выходы первого и второго регистров соединены с информационными входами соответственно первого и второго цифроаналоговых преобразователей, управляющие входы которых подключены к выходу первого источника опорного напряжения, а выходы соединены с первыми входами соответственно первого и второго суммирующих усилителей, выходы которых являются соответственно первым и вторым выходами формирователя, выход второго источника опорного напряжения соединен с входом блока делителей напряжения, первый и второй выходы которого соединен с вторыми входами соответственно первого и второго суммирующих усилителей.3. Преобразователь по п. 1, о т л и ч а ющ и й с я тем, что формирователь корректирующего сигнала содержит регистр, циф-. роаналоговый преобразователь, делитель и суммирующий усилитель, выход которого является выходом формирователя, информационные входы регистра являются управ 1777240ляющими входами формирователя, тактовым входом которого является тактовый вход регистра, выходы которого соединены с информационными входами цифроаналогового преобразователя, управляющий Б вход которого является первым информационными входом формирователя, а выход соединен с первым входом суммирующего усилителя, вход делителя является вторым информационным входом формирователя, а 10 выход делителя соединен с вторым входом суммирующего усилителя. 4. Преобразователь по п.1, о т л и ч а ющ и й с я тем, что формирователь амплитуды содержит регистр и цифроаналоговый преобразователь, выход которого является выходом формирователя, а управляющий вход - информационным входом формирователя, информационные входы регистра являются управляющими входами формирователя, а тактовый вход регистра- тактовым входом формирователя, выходы регистра соединены с информационными входами цифроаналогового преобразователя,. Лиси Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 10 каз 412 ВНИИ оставитель Е. Бударинаехред М.Моргентал Корректор Тираж ПодписноеГосударственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4689831, 09.03.1989

ИНСТИТУТ РАДИОФИЗИКИ И ЭЛЕКТРОНИКИ АН АРМССР

АВАКЯН АВАК ГЕОРГИЕВИЧ

МПК / Метки

Метки: код, перемещения

Опубликовано: 23.11.1992

Код ссылки

<a href="https://patents.su/8-1777240-preobrazovatel-peremeshheniya-v-kod.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь перемещения в код</a>

Предыдущий патент: Преобразователь угол-код

Следующий патент: Способ преобразования угла поворота вала в частоту и код угловой скорости и устройство для его осуществления

Случайный патент: Устройство измерения временных интервалов