Устройство для формирования сигнала переноса при суммировании многофазных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

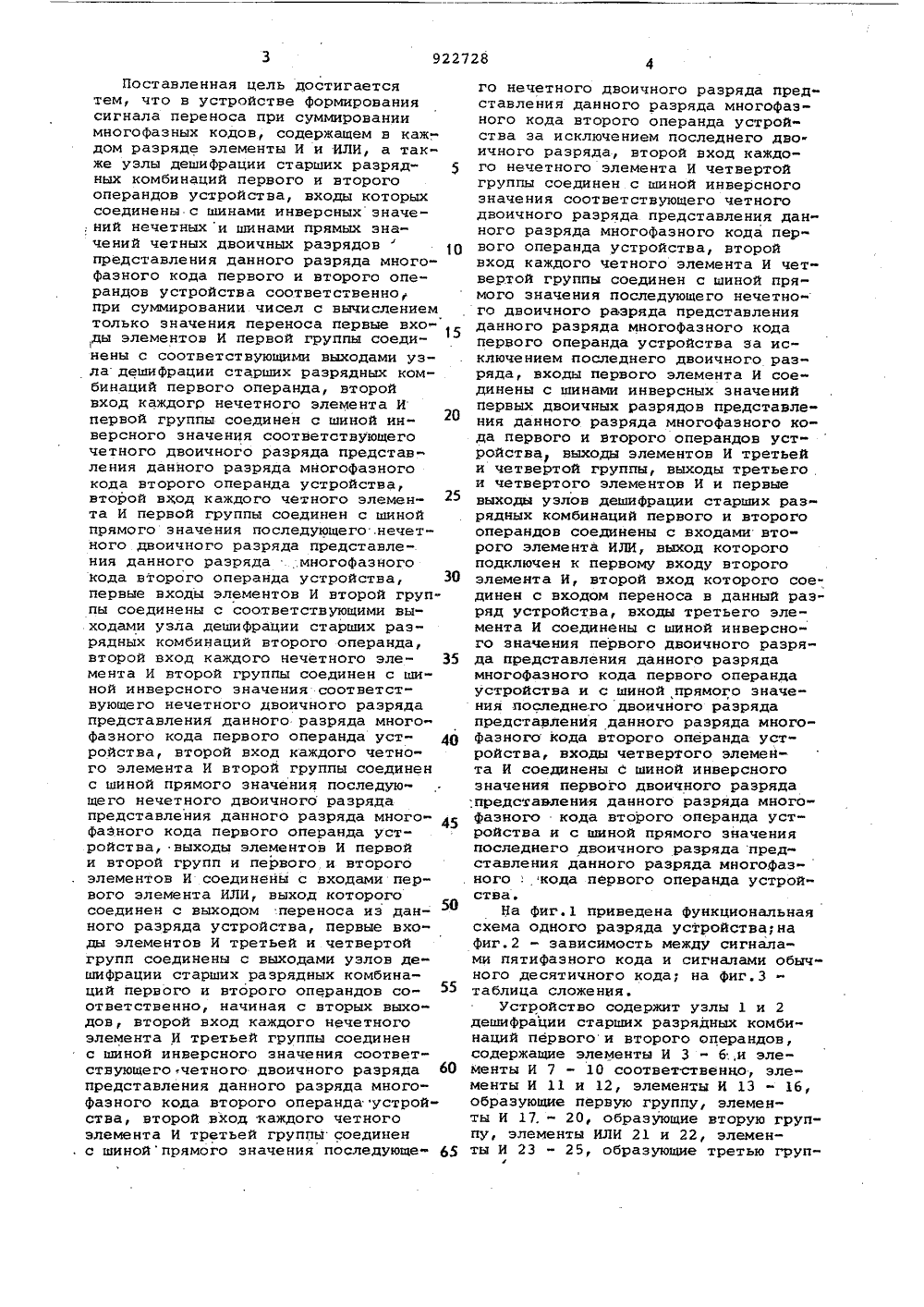

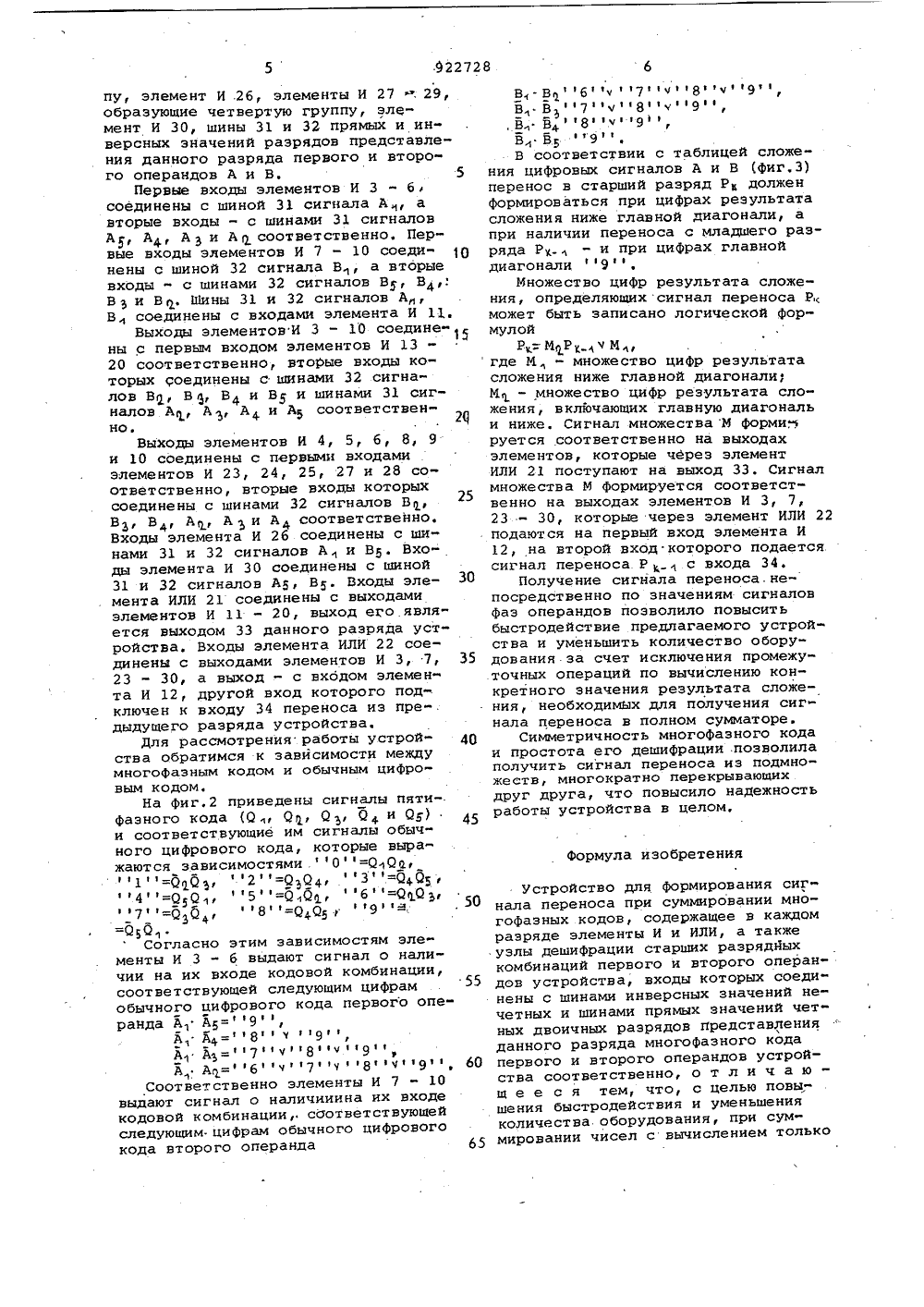

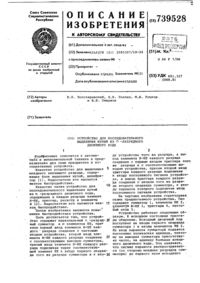

с шинойпрямого значения последующе 65 Поставленная цель достигается тем, что в устройстве формирования сигнала переноса при суммировании многофазных кодов, содержащем в каж-, дом разряде элементы И и ИЛИ, а также узлы дешифрации старших разрядных комбинаций первого и второго операндов устройства, входы которых соединены с шинами инверсных значе, ний нечетных и шинами прямых значений четных двоичных разрядов о представления данного разряда многофазного кода первого и второго операндов устройства соответственно при суммировании чисел с вычислением только значения переноса первые вхо 1ды элементов И первой группы соединены с соответствующими выходами узла дешифрации старших разрядных комбинаций первого операнда, второй вход каждогр нечетного элемента И первой группы соединен с шиной инверсного значения соответствующего четного двоичного разряда представ ления данного разряда многофазного кода второго операнда устройства, второй вХод каждого четного элемента И первой группы соединен с шиной прямого значения последующего .нечетного двоичного разряда представления данного разряда .многофазного кода второго операнда устройства, 30 первые входы элементов И второй группы соединены с соответствующими выходами узла дешифрации старших разрядных комбинаций второго операнда, второй вход каждого нечетного эле мента И второй группы соединен с шиной инверсного значения соответствующего нечетного двоичного разряда представлений данного разряда многофазного кода первого операнда уст 40 ройства, второй вход каждого четного элемента И второй группы соединен с шиной прямого значения последующего нечетного двоичного разряда представления данного разряда много фаЗного кода первого операнда устройства, выходы элементов И первой и второй групп и первого.и второго элементов И соединены с входами первого элемента ИЛИ, выход которого соединен с выходом .переноса из данного разряда устройства, первые входы элементов И третьей и четвертой групп соединены с выходами узлов дешифрации старших разрядных комбинаций первого и второго операндов соответственно, начиная с вторых выходов, второй вход каждого нечетного элемента И третьей группы соединен с шиной инверсного значения соответ 60ствующего четного двоичного разрядапредставления данного разряда многофазного кода второго операнда устройства, второй вход каждого четного элемента И третьей группы соединен го нечетного двоичного разряда представления данного разряда многофазного кода второго операнда устройства за исключением последнего двоичного разряда, второй вход каждого нечетного элемента И четвертойгруппы соединен с шиной инверсногозначения соответствующего четногодвоичного разряда представления данного разряда многофазного кода первого операнда устройства, второйвход каждого четного элемента И четвертой группы соединен с шиной прямого значения последующего нечетно-го двоичного разряда представленияданного разряда многофазного кодапервого операнда устройства за исключением последнего двоичного разряда, входы первого элемента И соединены с шинами инверсных значенийпервых двоичных разрядов представления данного разряда многофазного кода первого и второго операндов устройства выходы элементов И третьейи четвертой группы, выходы третьего .и четвертого элементов И и первыевыходы узлов дешифрации старших разрядных комбинаций первого и второгооперандов соединены с входами второго элемента ИЛИ, выход которогоподключен к первому входу второгоэлемента И, второй вход которого соединен с входом переноса в данный разряд устройства, входы третьего элемента И соединены с шиной инверсного значения первого двоичного разряда представления данного разрядамногофазного кода первого операндаустройства и с шиной прямого значения последнего двоичного разрядапредставления данного разряда многофазногокода второго операнда устройства, входы четвертого элемента И соединены с шиной инверсногозначения первого двоичного разряда;представления данного разряда многофазного кода второго операнда устройства и с шиной прямого значенияпоследнего двоичного разряда представления данного разряда многофазного . кода первого операнда устройства,На фиг.1 приведена функциональнаясхема одного разряда устройства;нафиг.2 - зависимость между сигналами пятифазного кода и сигналами обычного десятичного кода 1 на фиг.3таблица сложения.Устройство содержит узлы 1 и 2дешифрации старших разрядных комбинаций первогои второго операндов,содержащие элементы И 3 - б;,и элементы И 7 - 10 соответственно, элементы И 11 и 12, элементы И 13 - 1 б,образующие первую группу, элементы И 17, - 20, образующие вторую груп"пу, элементы ИЛИ 21 и 22, элементы И 23 - 25, образующие третью груп/формула изобретения пу, элемент И .26, элементы И 27 , 29,образующие четвертую группу, элемент И 30, шины 31 и 32 прямых и инверсных значений разрядов представления данного разряда первого и второго операндов А и В. 5Первые входы элементов И 3 - бсоединены с шиной 31 сигнала А , авторые входы - с шинами 31 сигналовАр А 4, А 3 и А 0 соответственно. Первые входы элементов И 7 - 10 соедииены с шиной 32 сигнала В, а вторыевходы - с шинами 32 сигналов В, В 4,.В 3 и В 1. Шины 31 и 32 сигналов А,Всоединены с входами элемента И 11,Выходы элементов И 3 - 10 соедине 11ны с первым входом элементов И 13 -20 соответственно, вторые входы которых Чоединены с шинами 32 сигналов В, В 4, В 4 и В 5 и шинами 31 сигналов А 1, А 3, А 4 и А 5 соответственно.Выходы элементов И 4, 5, б, 8, 9и 10 соединены с первыми входамиэлементов И 23, 24, 25, 27 и 28 соответственно, вторые входы которыхсоединены с шинами 32 сигналов В,В 3, В 4, А, А 3 и А 4 соответственно,Входы элемента И 26 соединены с шинами 31 и 32 сигналов А и В. Входы элемента И 30 соединены с шиной31 и 32 сигналов А, В. Входы элемента ИЛИ 21 соединены с выходамиэлементов И 11 - 20, выход его является выходом 33 данного разряда устройства. Входы элемента ИЛИ 22 соединены с выходами элементов И 3, 7, 3523 - 30, а выход - с входом элемента И 12, другой вход которого подключен к входу 34 переноса из пре-.дыдущего разряда устройства.Для рассмотрения работы устрой 4 Оства обратимся к зависимости междумногофазным кодом и обычным цифровым кодом.На фиг,2 приведены сигналы пяти-.фазного кода (О, 0, 03, 04 и 0)и соответствующие им сигналы обычного цифрового кода, которые выражаются зависимостями .0=001,11733 - 0 0 118110 0 3 У 9 УЬ ф0501Согласно этим зависимостям элементы И 3 - б выдают сигнал о наличии на их входе кодовой комбинации,соответствующей следующим цифрамобычного цифрового кода первого операнда А А=9,А . А =8 ч 9Ф РА А:7 чф 8 ч 911 = чАА: бф фч ф ф 7 ч8 ф чф 1911 60Соответственно элементы И 7 - 10выдают сигнал о наличииина их входекодовой комбинации,. соответствующейследующим цифрам обычного цифровогокода второго операнда 65 Вч Вб ч7 ч 8 ч 91В 7 ч 8 ч 9. 1 ф РВ,В 19В соответствии с таблицей сложения цифровых сигналов А и В (фиг.3)перенос в старший разряд Р долженформироваться при цифрах результатасложения ниже главной диагонали, апри наличии переноса с младшего разряда Рч- и при цифрах главнойдиагонали 9,Множество цифр результата сложения, определяющихсигнал переноса Рможет быть записано логической формулойР:Мрч М,где М- множество цифр результатасложения ниже главной диагонали;М - множество цифр результата сложения, включающих главную диагональи ниже. Сигнал множества М Формируется .соответственно на выходахэлементов, которые через элементИЛИ 21 поступают на выход 33. Сигналмножества М формируется соответственно на выходах элементов И 3, 7,23 - 30, которые через элемент ИЛИ 22подаются на первый вход элемента И12, на второй вход. которого подаетсясигнал переноса Рс входа 34,Получение сигнала переноса.непосредственно по значениям сигналовфаз операндов позволило повыситьбыстродействие предлагаемого устройства и уменьшить количество оборудования за счет исключения промежуточных операций по вычислению конкретного значения результата сложения, необходимых для получения сигнала переноса в полном сумматоре.Симметричность многофазного кодаи простота его дешифрации .позволилаполучить сигнал переноса из подмножеств, многократно перекрывающихдруг друга, что повысило надежностьработы устройства в целом,Устройство для формирования сигнала переноса при суммировании многофазных кодов, содержащее в каждом разряде элементы И и ИЛИ, а также узлы дешифрации старших разрядных комбинаций первого и второго операндов устройства, входы которых соеди" нены с шинами инверсных значений нечетных и шинами прямых значений четных двоичных разрядов представления данного разряда многофазного кода первого и второго операндов устройства соответственно, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и уменьшения количества. оборудования, при суммировании чисел свычислением толькозначения переноса, первые входы элементов И первьй группы соединены ссоответствующими вьходами узла дешифрации старших разряДных комбинаций первого операнда, второй входкаждого нечетного элемента И первбй группы соединен с шиной инверсногозначения соответствующего четногодвоичного разряда представления дан.ного разряда многофазного кода второго операнда устройства, второйвход каждого четного элемента И первой группы соединен с шиной прямогозначения последующего нечетного двоичного разряда представления данного разряда многофазного кода второго операнда устройства первые вхо-,ды элементов И второй группы соединены с соответствующими выходами узла дешифрации старших разрядных комбинаций второго операнда, второйвход каждого нечетного элемента Ивторой группы соединен с шиной инверсного значения соответствующегочетного двоичного разряда представления данного разряда многофазногокода первого операнда устройства,второй вход каждого четного элемента И второй группы соединен с шиной прямого значения последующегонечетного двоичного разряда представления данного разряда многофазного кода первого операнда устройства, выходы элементов И первой ивторой групп и первого и второгоэлементов И соединены с входами первого элемента ИЛИ, выход которогосоединен с выходом переноса из данного разряда устройства, первые входы элементов И третьей,и четвертойгрупп соединены с выходами узлов дешифрации старших разрядных комбинаций первого и второго операндов соответственно, начиная с вторыхвыходов, второй вход каждого нечетного элемента И третьей группы соединен с шиной инверсного значениясоответствующего четного двоичногоразряда представления данного разряда многофазного кода второгооперанда устройства, второй входкаждого четного элемента И третьейгруппы соединен с шиной прямого значения последующего нечетного двоичного разряда представления данногоразряда многофазного кода второгооперанда устройства, за исключениемпоследнего двоичного разряда, второйвход каждого нечетного элемента И четвертой группы соединен с шинойинверсного значения соответствующего четного двоичного разряда представления данногоразряда многбфазного кода первого операнда устрой 5 ства, второй вход каждого четногоэлемента И четвертой группы соединен с шиной прямого значения последующего нечетного двоичного разрядапредставления данного- разряда много 0 фазного кода первого операнда устройства, за исключением последнегодвоичного разряда, входы первогоэлемента И соединены с шинами инверсных значений первых двоичных разря 15 дов представления данного разрядамногофазного кода первого и второгооперандов устройства, выходы элементов И третьей и четвертой групп, выходы третьего и четвертого элементов И и первые выходы узлов дешифрации старших разрядных комбинацийпервого и второго операндов соединены с входами второго элемента ИЛИ,выход которого подключен к первомувходу второго элемента И, второйвход которого соединен с входом переноса в данный разряд устройства,входы третьего элемента И соединеныс шиной инверсного значения первогодвоичного разряда представления данного разряда многофазного кода первого операнда устройства и с шинойпрямого значения последнего двоичного разряда представления данногоразряда многофазного кода второгооперанда устройства, входы четвертого элемента И соединены с шиной инверсного значения первого двоичногоразряда представления данного разряда многофазного кода второго операн 40 да устройства и с шиной прямого значения последнего двоичного разрядапредставления данного разряда .многофазного кода первого операнда устройства.45 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРпо заявке У 2352761/18-24,кл. С 06 Р 7/385, 1978.50 2, Прангишвили И,В,и др, Микроэлектроника и однородные структурыдля построения логических вычислительных устройств. М Наука,1967, с. 176 рис. 4.22.3. Авторское свидетельство СССРпо заявке Р 2585230/18-24,кл, 6 06 Р 7/385, 1978 (прототип),922728 оставитель В.Березкехред С. Мигунова Корре ор Л.Б заказ 2581/6 исноеССР 4/ Ужгород, ул, Проектная, 4 тфф ППП и Редактор В,Дан ВНИИПИ по д 113035, ИоТираж 732 Государственного елам изобретений сква, Ж, Рауш Под комитета и открыт кая наб,

СмотретьЗаявка

2746881, 31.01.1979

ПРЕДПРИЯТИЕ ПЯ Г-4514

КОЧЕРГИН ВАЛЕРИЙ ИВАНОВИЧ, ЛЕКАРЕВ АНАТОЛИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 7/49

Метки: кодов, многофазных, переноса, сигнала, суммировании, формирования

Опубликовано: 23.04.1982

Код ссылки

<a href="https://patents.su/6-922728-ustrojjstvo-dlya-formirovaniya-signala-perenosa-pri-summirovanii-mnogofaznykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования сигнала переноса при суммировании многофазных кодов</a>

Предыдущий патент: Арифметико-логическое устройство

Следующий патент: Комбинационный двоичный сумматор

Случайный патент: Устройство для контроля амплитудно-частотной характеристики телевизионной аппаратуры