Устройство для последовательного выделения нулей из п разрядного двоичного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 739528

Авторы: Золотаревский, Нэллин, Руцков, Смирнов

Текст

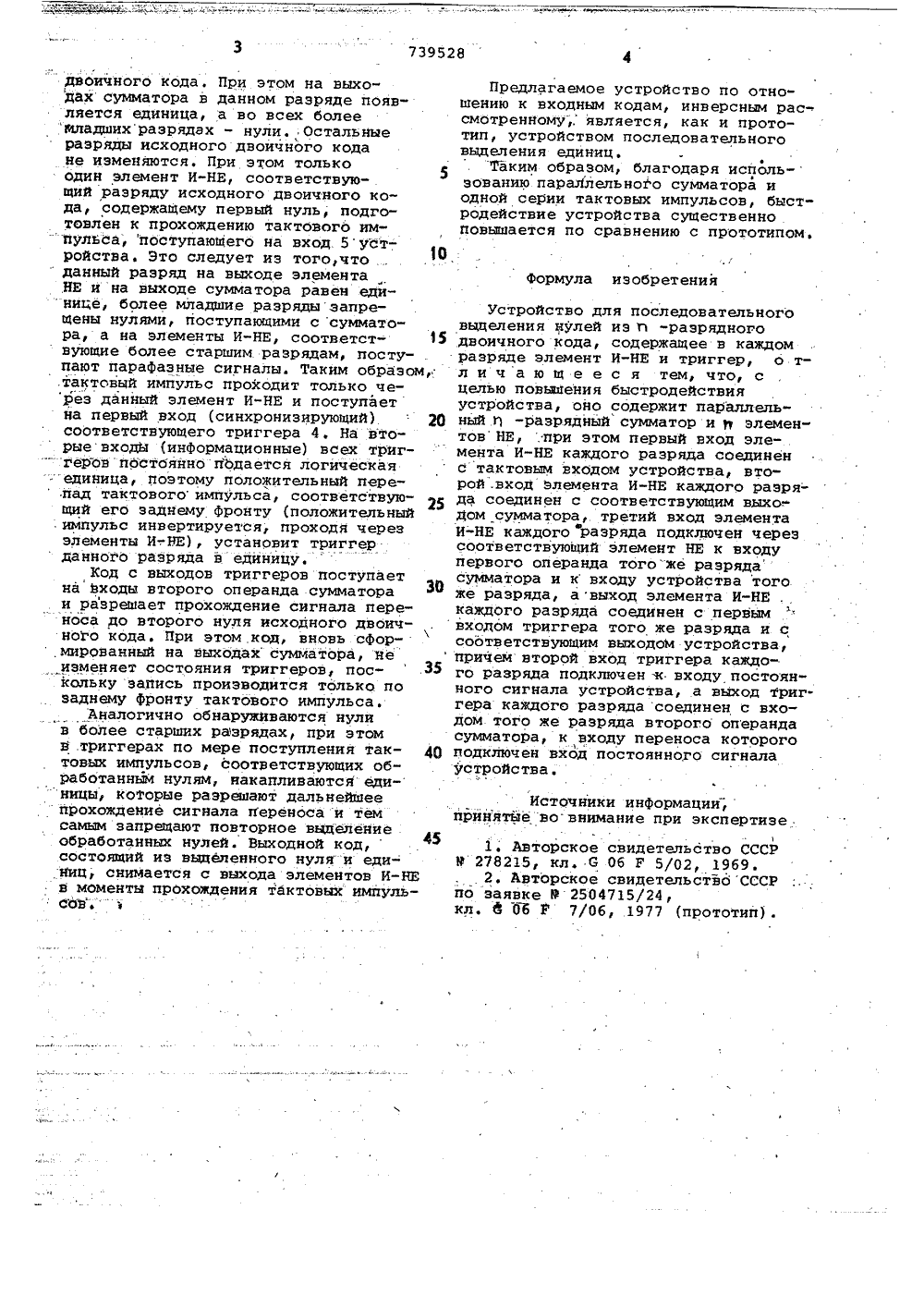

Союз Советских Сощиалистнческик Республикон 739528 б 1 лнительное к авт. свид 2) Заявлено 210278 (21) 2583307/18-24 Р 7 с присоед нием заявки М сударственный комитет СССР по делам изобретений и открытий(72) Авторы изобретени ков,аявитель 4) УСТРОЙСТВО ДЛЯ ПОСЛЕДОВАТЕЛЬНОГО ВЫДЕЛЕНИЯ НУЛЕЙ ИЗ 11 в РАЗРЯДНО ДВОИЧНОГО КОДА Йзобретение относится к автоматике.и вычислительной технике и предназначено для схем приоритета и ассоциативных устройств.Известно устройство для выделения младшего значащего разряда, содержащее блок выделения нулей, дешифратор 1. Недостатком его является низкое быстродействие.Известно также Устройство дпя последовательного выделения нулей из П -разрядного двоичного кода, содержащее в каждом разряде элемент И-НЕ, триггер, регистр и элементы И 2). Недостатком его является низкое быстродействие.Целью изобретения является повышение быстродействия устройства,Цель достигается тем, что устройство содержит параллельный и -разряд ный сумматор и тт элементов НЕ, при 1 этом первый вход элемента И"НЕ каждогоразряда соединен с тактовым входом устройства, второй вход элемента И-НЕ каждого разряда соединен. 2 с соответствуюшим выходом сумматора, третий вход элемента И-НЕ каждого разряда подключен через соответствующий элемент НЕ к входу первого операнда того же,разряда сумматора и к входу устройства того же разряда, а выход элемента И-НЕ каждого разряда соединен с первым входом триггера того же разряда и с соответствующим выходом устройства, причем второй вход триггера каждого разряда подключен к входу постоянного сигнала устройства, а выход триггера каждого разряда соединен с входом того же разряда второго операнда сумматора, к входу переноса которого подключен вход постоянного сигнала устройства,На чертеже изображена структурная схема предлагаемого устройства. Оно содержит сумматор 1, элементы НЕ 2, элементы И-НЕ 3, триггеры 4, тактовый вход 5.Устройство работает следующим об"разом. В исходном состоянии триггеры обнулены. Исходный двоичный кодпоступает на входы первого операндасумматора 1 и входы элементов НЕ 2.На вход переноса сумматора подаетсяпостоянно логическая единица, поэтому на выходах сумматора присутствует число, на единицу большее исход"ного двоичного кода. Это означает,что сигнал переноса распространяется (со стороны младшихразрядов сум-.матора) до первого нуля исходногодвоичного кода. При этом на выходах сумматора в дайном разряде появляется единица, а во всех более йладшихразрядах - нули. Остальныеразряды исходного двоичного кодане изменяются. При этом толькоодин элемент И-НЕ, соответствую- .щий разряду исходного двоичного кода, содержащему первый нуль, подготовлен к прохождению тактового им пульса, поступающего на вход. 5 устройства, Это следует из того,чтоданный разряд на выходе элементаНЕ и на выходе сумматора равен едйнице, более младшие разряды запрещены нулями, поступающими с сумматора, а на элементы И-НЕ, соответствующие более старшим. разрядам, поступают парафазные сигналы. Таким образом,тактовый импульс проходит только через данный элемент И-НЕ и поступаетйа первый вход синхронизирующий)20соответствующего триггера 4. На вторые входй (информационные) всех триг геров постоянно пЬдается логическая . единица, поэтому положительный перепад тактовогоимпульса, соответствующий его заднему фронту (положительный . импульс инвертируется, проходя черезэлементы И-. НЕ), установит триггерданного разряда в единицу.Код с выходов триггеров поступаетна входы второго операнда сумматора . и разрешает прохождение сигнала переноса до второго нуля исходного двоичного кода. При этом код, вновь сфор,мированный на выходах" сумматора, неизменяет состояния триггеров, пос-З 5кольку запись производится только позаднему Фронту тактового импульса.Аналогично обнаруживаются нулив более старших разрядах, при этомв триггерах по мере поступления тактовых импульсов, соответствующих обработанным нулям, накапливаютсяеди-ницы, которые разрешают дальнейшеепрохождение сигнала переноса и темсамым запрещают повторное выделениеобработанных нулей. Выходной код,состоящий из выделенного нуля-и едийиц, снимается с выхода элементов И-НЕв моменты прохождения тактовых импульсов Предлагаемое устройство по отно шению к входным кодам, инверсным рассмотренному, является, как и прототип, устройством последовательного выделения единиц.Таким образом, благодаря использованию параЛлельного сумматора и одной серии тактовых импульсов, быстродействие устройства существенно повышается по сравнению с прототипом.Формула изобретенияУстройство для последовательноговыделения нулей из й -разрядногодвоичного кода, содержащее в каждомразряде элемент И-НЕ и триггер, о тличающееся тем, что, сцелью повыаения быстродействияустройства, оно содержит параллельный О -разрядный сумматор иэлементов НЕ, .при этом первый вход элемента И-НЕ каждого разряда соединенс тактовым входом устройства, второй .вход ълвкента И-НЕ каждого разряда соединен с соответствующим выхо-.дом сумматора, третий вход элементаИ-НЕ каждого разряда подключен черезсоответствующий элемент НЕ к входупервого операнда тогоже разрядасумматора и к входу устройства тогоже разряда, а выход элемента И-НЕ .каждого разряда соединен с первымвходом триггера того же разряда и ссоответствующим выходоМ устройства,причем второй вход триггера каждого разряда подключен .к входу постоянного сигнала устройства, а вйход триггера каждого разряда соединен с входом того же разряда второго операндасумматора, к входу переноса которогоподключен вход постоянного сигналаустройства,Источники инФормации,принятйе во внимание при экспертизе11. Авторское свидетельство СССРВ 278215, кл, 6 Об Г 5/02, 1969.2. Авторское свидетельство СССРпо заявке Р 2504715/24,кл. Ф Об Р 7/Об, 1977 (прототип).739528 Составитель Е. ПупырРедактор Л. Волкова ТехредА.Щепанская ктор Т. Скворцова Подписное илиал ППП Патентф, г. Ужгород, ул. Проектная, .4 Заказ 2926/43.ЦНИИПИ Гос по дел 113035, МоскваТираж. 751дарственного комитета СССРм изобретений и открытийЖ, Раушская наб., д. 4/

СмотретьЗаявка

2583307, 21.02.1978

ПРЕДПРИЯТИЕ ПЯ М-5489

ЗОЛОТАРЕВСКИЙ БОРИС ЛЕОНОВИЧ, НЭЛЛИН ВИКТОР ВАЛЕНТИНОВИЧ, РУЦКОВ МИХАИЛ ВАДИМОВИЧ, СМИРНОВ ВЛАДИМИР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/06

Метки: «нулей», выделения, двоичного, кода, последовательного, разрядного

Опубликовано: 05.06.1980

Код ссылки

<a href="https://patents.su/3-739528-ustrojjstvo-dlya-posledovatelnogo-vydeleniya-nulejj-iz-p-razryadnogo-dvoichnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для последовательного выделения нулей из п разрядного двоичного кода</a>

Предыдущий патент: Устройство для упорядоченной выборки значений параметра

Следующий патент: Цифровое вычислительное устройство

Случайный патент: Кулисно-рычажный механизм