Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

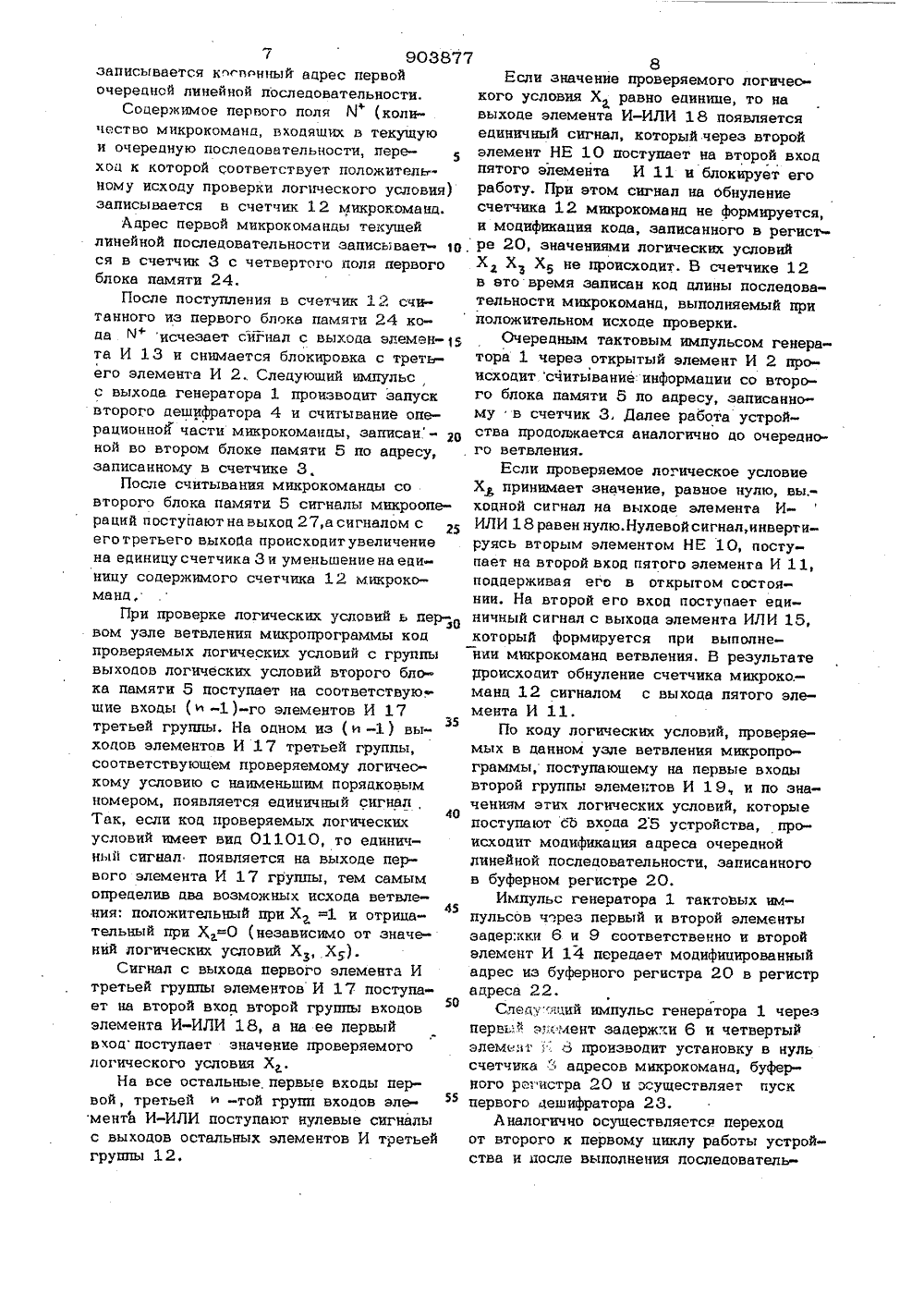

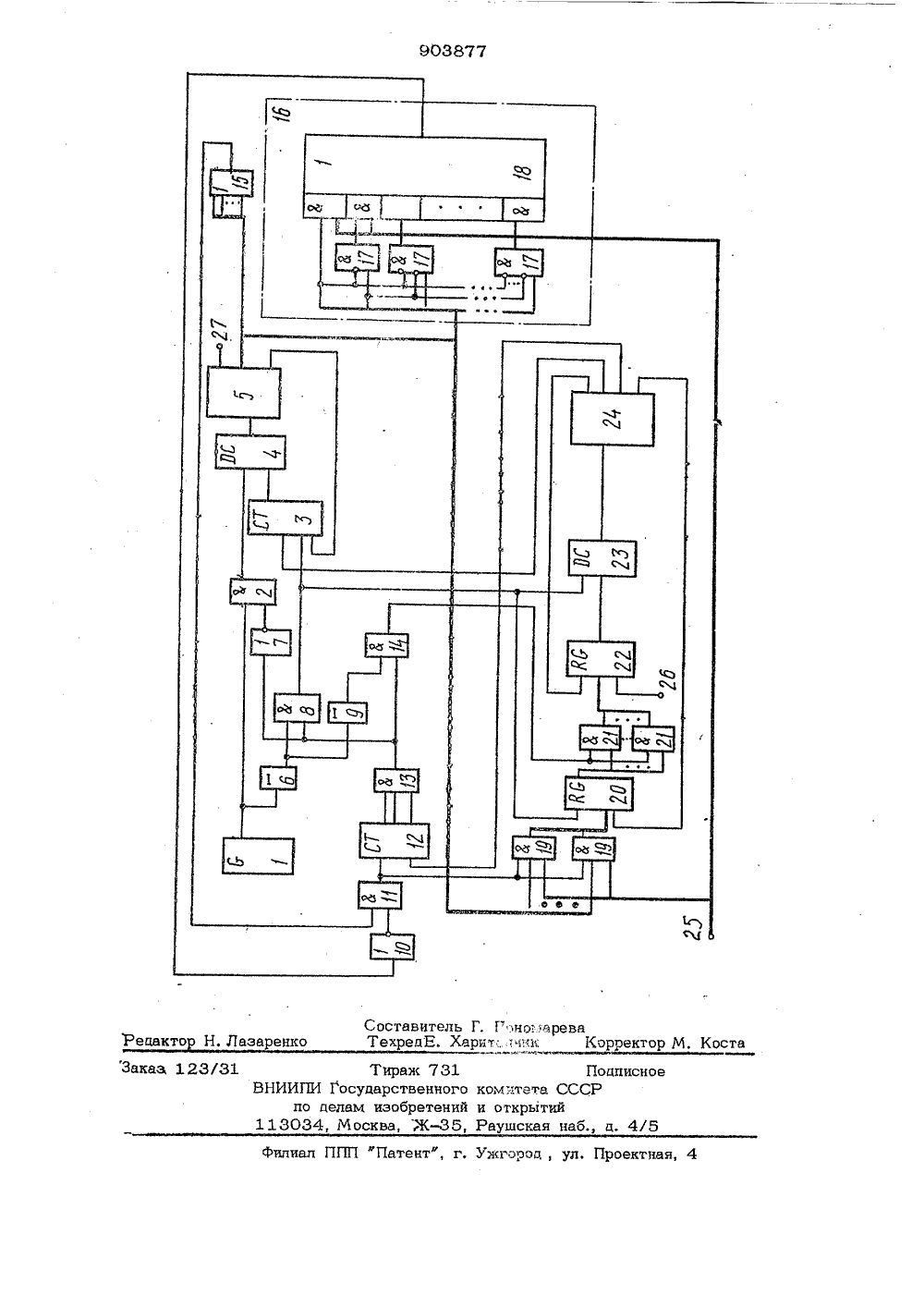

ц 1903877 Союз Совет сникСоциалистическихРеспублик ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(51)М, Кл. 606 Г 9/22 3 Ънударстюаа камнтнт СССР йв двлам нзобретеннй н втнрмтнй(72) Авторы изобретения 71) Заяв 54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕН ыполнения 1 оаной линейнойности к аругой, а такженомичности первого блокауменьшения его избыточзобрете 1 ехоаа ой техник ри проект ослеаовател повышение экпамяти путемности. граммного ельных маш н 5 15 го ие относится к вычиспительф может быть использовано ванин устройств . микропроравления цифровых вычислиИзвестно устройство микропрограммного управпениясоаержащее ава блокапамяти, два дешифратора, регистры, счетчик адреса, генератор, элементы И 113 .Недостатком данного устройства является низкое быстродействие.Наиболее близким к изобретению потехнической сущности является устройство микропрограммного управления, которое содержит ава бпока памяти, двадешифратора, счетчики микрокомана иадреса, буферный и адресный регистры,генератор, элементы И, НЕ 23Неаостатком известного устройстваявляется низкое быстроаействие и большойобъем первого блока памяти.Бель изобретения - повышение быстродействия устройства микропрограммногоуправления за счет уменьшения времени Поставленная цель достигается тем, что в устройство микропрограммного управления, содержащее генератор тактовых импупьсов, выход которого соеаинен через первый и второй элементы задержки с первым вхоаом первого элемента И, второй вход которого соединен с выходом второго элемента И, с первым входом третьего элемента И и через первый элемент НЕ с первым входом четвертого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход третьего элемен. та И соединен с первыми входами первого аешифратора, счетчика адреса и буферного регистра, группа выходов которо соединена с первыми входами элементов И первой группы, вторые входы которых, соединены с выходом первого элемента И.7 4Сущность изобретения состоит в повышении быстродействия, снижении объема блоков памяти путем задания в формате адресной микрокоманцы суммарного числа операционных микрокоманц, входящих в текущую линейную последовательность и последовательность, выполняемую за ней при положительном исхоце проверки логических условий.При этом повышение быстродействия достигается за счет того, что при проверке,логических условий в любом узле ветвления микропрограммы, в случае положительного исхода проверки, происходит формирование адреса первой микрокоманцы соответствующей очередной линейной последовательности путем естественной адресации. При этом переход к считыванию информации из первого блока памяти не происходит. 3 90387 еыхоцы элементов И первой группы соецинены с группой ингормационных входов регистра адреса, вход кода операции которого является входом кода операции устройства, выход регистра ацреса соединен со вторым в одом первого цешифратора, выход которого соединен с вхоцом первого блока памяти, первый и второй выходы которого соединены соответственно с входом сброса регистра адреса, и 10 со вторым входом счетчика адреса, третий вход которого соецинен с первым выходом второго блока памяти, второй выход которого является выхоцом устройства, вхоц второго блока памяти соединен 15 с выходом второго дешифратора, первый и второй входы которого соединены соответственно с выхоцами четвертого элемента И и счетчика адреса, группа входов второго элемента И соединена с группой 20 . выходов счетчика микрокоманц, первый вхоц которого соединен с третьим выхоцом первого блока памяти, четвертый выход которого соединен со вторым входом буферного регистра, группа входов 25 которого соецинена с выходами элементов И второй группы, первые входы которых являются группой вхоцов логичес- ких условий устройства, вторые вхоцы элементов И второй группы соединены с группой выходов второго блока памяти, введены третья группа элементов И, состоящую из (и -1) элемента И, элемент И-ИЛИ, элемент ИЛИ, второй элемент НЕ, пятый элемент И, причем первые входыЭ 5 групп входов элемента И-НЕ соединены с группой входов логических условий устройства, второй вхоц первой группы входов элемента И-ИЛИ соединен с первым выходом группы выходов второго блока40 памяти, вторые входы второй и-ой группы входов элемента И-ИЛИ соецинены с уыхоцами элементов И третьей группы, первые вх оды которы х соединены с соответствующими выходами группы выходов45 второго блока памяти, а второй (1+1) -й инверсные входы каждого -го элемента третьей группы элементов И соединены с первым --тым выходами группывыхоцов второго блока памяти ( =1,и),50 вторая группа выходов второго блока памяти соединена с группой входов элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, второй вход которого через второй элемент НЕ соединен с выходом элемента И-ИЛИ, а выход - со вхоцом установки в нуль счетчика микрокоманц и третьими входами элементов И второй группы. Повышение экономичности устройствамикропрограммного упра впения достигается путем уменьшения числа ячеек .внервом блоке памяти за счет отказа отхранения адресов первых микрокоманцлинейных последовательностей, переход ккоторым осуществляется при положительном исходе проверки логических условий.Первый блок памяти разделен на четыре поля. В первом попе записываетсясуммарное количество микрокоманд, содержащихся в текущей последовательности и очерецной, переход к реализациякоторой возможен в случае положитепьного исхода проверки погических условий.Во втором поле записывается косвенныйадрес очередной последовательности. Втретьем поле записывается сигнал сбросарегистра адреса. В четвертом - адреспервой микрокоманцы текущей поспедовательности.Второй блок памяти разбит на три поля. В первом поле записываются операционные части выполняемых микрокоманц,а во втором - коц проверяемых логических условий, в третьем - метка, обозначающая признаксчитывания микрокоманциз второго блока памяти.Положительному (отрицательному)ходу проверки логических условий соответствует принятие единичного ( нулевого) значенгая логического условия с наименьшим номером,Третья группа элементов И и элементИ-ИЛИ образуют узел идентификации ветви микропрограммы, введение которогопозволяет идентифицировать положительный исход проверки логических условий.5 90387На чертеже представлена функциональная схема устройства микропрограммного управления,На схеме обозначены генератор 1 тактовых импульсов, третий элемент И 2, 5счетчик 3 адресов микрокоманл, второйдешифратор 4, второй блок памяти 5,первый элемент задержки 6, первый элемент НЕ 7, четвертый элемент И 8, второй элемент задержки О, второй элемент 10НЕ 10, пятый элемент И 11, счетчик 12микрокоманц, первый элемент И 13, второй элемент И 14, элемент ИЛИ 15,узел 16 идентификации ветви микропрограммы, состоящей из третьей группы 15элементов И 17, элемента И-ИЛИ 18,вторая группа элементов И 19, буферныйрегистр 20, первая группа элементовИ 21, регистр адреса 22, первый цешифратор 23, первый блок памяти 24, вхоц 2025 логических условий, вход кода операции 26, выход 27 устройства.Выполнение микропрограммы подразделяется на два цикпа:цикл формирования адреса первой микрокоманды очередной последовательностии считывания его из первого блока 24 ицикл считывания операционных частеймикрокоманд из второго блока памяти 5с выхода 27 поля микроопераций. 30В цикле формирования алреса первоймикрокоманцы очередной последовательности и считывания ее из первого блокапамяти 24 информация передается из бу.ферного регистра 20 в регистр адреса 22 З 5и палее через первый дешифратор 23 впервый блок памяти 24. Б первом блокепамяти 24 записывается коц М количество микрокоманц в двух последовательностях, между которыми возможен переход 4 Олишь микрокоманц при положительном исходе проверки логического условия, коцИ передается в счетчик микрокоманц 1 2.Во втором попе записывается косвенныйадрес первой микрокоманцы очередной линейной послецовательности, который перецается в регистр 20. Лдрес первоймикрокоманцы текущей последовательностизаписывается в четвертом поле первогоблока памяти и передается в счетчик. 3,Счетчик микрокоманц 1 2 поцсчитывает количество выполняемых микроко.мана.Счетчик 3 формирует адреса микрокоманд в текущей послецовательности.Генератор 1 тактовы х .импульсов осуществляет тактирование работы устройстваи считывания информации из запоминающих блоков,7 6Узел 16 идентифицирует положительный исход проверки логических условий,Во втором цикле работы устройствамикропрограммного управления происходит считывание операционных частей микрокоманд, входящих в текущую послецоватепьность.Содержимое счетчика микрокоманц 12во втором цикле работы устройства микропрограммного управления отлично отнуля.После того как будут сосчитаны операционные части микрокоманц, образующих текудую последовательность, устройство осуществляет проверку значений логических условий. Узел 16 осуществляетпроверку выбора ветви микропрограммыпо коду и значению логического условия.В зависимости от значения, которое принимает проверяемое логическое условие, вмикропрбграмме возможно формированиедвух ветвей микропрограммы, соответствую.щих положительному и отрицательному исхолам проверки.В случае положительного исхода прсверки логического условия, содержимоесчетчика 3 увеличивается на единицу, формируя при этомадрес очередной микрокоманды,Содержимое счетчика 12 микрокоманцы уменьшается на ециницу, При этомего обнуление не происхоцит, а код, записанный в регистре 20, не модифицируется, Устройство микропрограммного управления процоджает находиться во второмцикле работы.В случае отрицательного исхода проверки логического условия происходитпринудительное обнуление счетчика 12микрокоманц. Устройство микропрограммного управления перехоцнт к циклу формирования адреса первой микрокоманцыочередной линейной последовательностипо адресу, записанному в буферный регистр 20.Устройсто работает следующим образом.Код операции поступает на третийвход регистра адреса 22 и является адресом первой микрокоманды первой линейной последовательности, записанной в блоке памяти 24,Генератор 1 тактовых импульсов через первый элемент задержки 6 и четвертый элемент И 8 производит запуск первого цешифратора 23 и выбирает соответствующую ячейку памяти нз первого блокапамяти 24. Содержимое второго поля первого блока памяти 2 -1 поступает нл первый вход буферного регистра 20, н в нем7 90387записывается ко о нный адрес первойочередной линейной последовательности,Содержимое первого поля Й (количество микрокоманд, входящих в текущуюи очередную последовательности, переход к которой соответствует положительному исходу проверки логического условия)записывается в счетчик 1 2 микрокоманд.Адрес первой микрокоманды текущейлинейной последовательности записывает.ся в счетчик 3 с четвертого поля первогоблока памяти 24.После поступления в счетчик 12 считанного из первого блока памяти 24 кодаисчезает сигнал с выхода элеменета И 1 3 и снимается блокировка с третьего элемента И 2,. Следующий импульсс выхода. генератора 1 производит запусквторого дешифратора 4 и считывание операционной части микрокоманды, записан- щоной во втором блоке памяти 5 по адресу,записанному в счетчике 3.После считывания микрокоманды совторого блока памяти 5 сигналы микроопераций поступают на выход 27,а сигналом сего третьего выхода происходит увеличениена единицу счетчика 3 и уменьшение на единицу содержимого счетчика 12 микрокоманд,При проверке логических условий ь первом узле ветвления микропрограммы кодпроверяемых логических условий с группывыходов логических условий второго блока памяти 5 поступает на соответствующие входы (и -1)-го элементов И 17третьей группы. На одном из (и -1) вы 35ходов элементов И 17 третьей группы,соответствующем проверяемому логическому условию с наименьшим порядковымномером, появляется единичный сигнал,40Так, если код проверяемых логическихусловий имеет вид 011010, то единичный сигнал появляется на выходе первого элемента И 17 группы, тем самымопределив два возможных исхода ветвления: положительный при Х =1 и отрица 45тельный при Х =0 ( независимо от значений логических условий Х, Х).Сигнал с выхода первого элемента Итретьей группы элементов И 17 поступает на второй вход второй группы входовэлемента И-ИЛИ 18, а на ее первыйвход поступает значение проверяемогологического условия Х.На все остальные, первые входы первой, третьей и -той групп входов элемента И-ИЛИ поступают нулевые сигналыс выходов остальных элементов И третьейгруппы 12,7 8Если значение проверяемого логического условия Х равно единице, то навыходе элемента И-ИЛИ 18 появляетсяединичный сигнал, который через второйэлемент НЕ 10 поступает на второй входпятого элемента И 11 и блокирует егоработу. При этом сигнал на обнулениесчетчика 12 микрокоманд не формируется,и модификация кода, записанного в регионре 20, значениями логических условийХд Х, Х не происходит. В счетчике 12в это время записан код длины последовательности микрокоманд, выполняемый приположительном исходе проверки.Очередным тактовым импульсом генератора 1 через открытый элемент И 2 происходит считывание информации со второго блока памяти 5 по адресу, записанному в счетчик 3. Далее работа устройства продолжается аналогично до очередного ветвления.Если проверяемое логическое условиеХ принимает значение, равное нулю, вы.ходной сигнал на выходе элемента ИИЛИ 1 8 равен нулю. Нулевой сигнал,ннвертируясь вторым элементом НЕ 10, поступает на второй вход пятого элемента И 11,поддерживая его в открытом состоянии. На второй его вход поступает единичный сигнал с выхода элемента ИЛИ 15,который формируется при выполнении микрокоманд ветвления, В результатепроисходит обнуление счетчика микроко. -манд 12 сигналом с выхода пятого элемента И 11.По коду логических условий, проверяемых в данном узле ветвления микропрограммы, поступающему на первые входывторой группы элементов И 19, и по значениям этих логических условий, которыепоступают сЪ входа 25 устройства, происходит модификация адреса очереднойлинейной последовательности, записанногов буферном регистре 20,Импульс генератора 1 тактовых импульсов ч.реэ первый и второй элементыэадер:кки 6 и 9 соответственно и второйэлемент И 14 передает модифицированныйадрес из буферного регистра 20 в регистрадреса 22.Следу.:щий импульс генератора 1 черезпервы" элемент задержки 6 и четвертыйэлемент Е. д производит установку в нульсчетчикаадресов микрокоманд, буферного регистра 20 и осуществляет пускпервого дешифратора 23.Аналогично осуществляется переходот второго к первому циклу работы устройства и после выполнения последователь10 9 90 Й 877ности, соответствующей положительномуисходу проверки. В этом случае обнулениесчетчика 12 происходит но сигналам свыхоца блока памяти 24. 5Таким образом, введение третьей груп; аы элементов И, элемента И-ИЛИ, элемента ИЛИ, второго элемента НЕ пятого элемента И и обнуленных ими связей позволяет повысить быстродеиствие устройь1 О ства и увеличить экономичность" устрой.тва в целом. формула изобретения 15 Устройство микропрограммного: управления, соаержашее генератор тактовых импульсов, .выход которого соединен через первый и второй элементы задержки 20 с первым входом первого элемента И, второй вход которого соецинен с выходом второго элемента И, с первым входом третьего элемента И и через первый элемент НЕ с первым входом четвертого элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход третьего элемента И соединен с первыми входами первого цешифратора, счетчика адреса. и буФерного регист;о ра, группа выходов которого соецинена с первыми входами элементов И первой группы, вторые входы которых соецинены с выхоаом первого элемента И, выходы элементов И первой группы соединены с группой информационных входов регистра адреса, вхоа кода операции которого является входом кода операции устройства, выхоц регистра ацреса .соецинен со вторым входом первого цешифратора, выхоц которого 4 О соединен с входом первого блока памяти, первый и второй выходы которого соединены соответственно с вхоаом сброса регистра адреса н со вторым входом счетчика адреса, третий вход которого со ецинен с первым выходом второго блока памяти, второй выход которого является выхоаом устройства, вход второго блока памяти соединен с выходом второго цешифратора, первый и второй входы которого соединены соответственно с выхоаами четвертого элемента И и счетчика адреса,группа входов второго элемента И соединена с группой выходов счетчика микрокоманц, первый вход которого соединенс третьим выходом первого блока памяти,четвертый выход которого соединен со вторым вхоаом буферного регистра, группавходов которого соеаинена с выхоцамиэлементов И второй группы, первые входыкоторых являются группой вхоаов логических условий устройства, вторые входыэлементов И второй группы соеаинены сгруппой выходов второго блока памяти,о т л и ч а ю ш е е с я тем, что, с целью повышения быстродействия устройства,оно содержит третью группу элементов И,состоящую из (и -1) элемента И, элемент И-ИЛИ, элемент ИЛИ, второй элемент НЕ, пятый элемент И, причем первыевходы ру групп входов элемента И-ИЛИсоединены с группой входов логическихусловий устройства, второй вход первойгруппы входов элемента И-ИЛИ соединенс первым выходом группы выходов второго бпока памяти, вторые входы второйру -ой группы входов элемента И-ИЛИсоединены с выходами соответствующих,элементов И третьей группы, первые входы которых соединены с соответствующими выходами группы выходов второго блока памяти, второй - ( +1)-й инверсныевходы каждого-го элемента третьейгруппы элементов И соединены с первым -а -тым выколамв группы выкоаов второго блока памятв ( 1 1,а -11, вторая группа выходов второго блока памяти соединена с группой входов элемента ИЛИ, выход которого соеаинен с первым входомпятого элемента И, второй вход которогочерез второй элемент НЕ соединен с выходом элемента И-ИЛИ, а выход пятогоэлементаИ соединен со входом установки в нуль счетчика микрокоманц и третьими входами элементов И второй группы.Источники информации,принятые во внимание при экспертизе1, Авторское свицетепьство СССРМб 638962, кл. 6 06 Г 9/14, 1976.2. Авторское свицетельство СССР903877 оставите ехред Е. едакто Н. Лазаренко аказ, 123/31 ипиал ППП "Патент", г, Ужгород, ул. Проектная Тираж 73 ИИПИ Государственн по делам изобрете 13034, Москва, ЖГ. Г но:;ареварит:, . нь: Корректор М. Кос 1 Подписноего комитета СССРий и открытий5, Раущская наб., д, 4/5

СмотретьЗаявка

2920161, 28.04.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, САМАРСКИЙ ВИКТОР БОРИСОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 07.02.1982

Код ссылки

<a href="https://patents.su/6-903877-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для распределения заданий

Следующий патент: Устройство для динамического преобразования адресов

Случайный патент: Затирочная машинка