Устройство для определения разностидвух п-разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

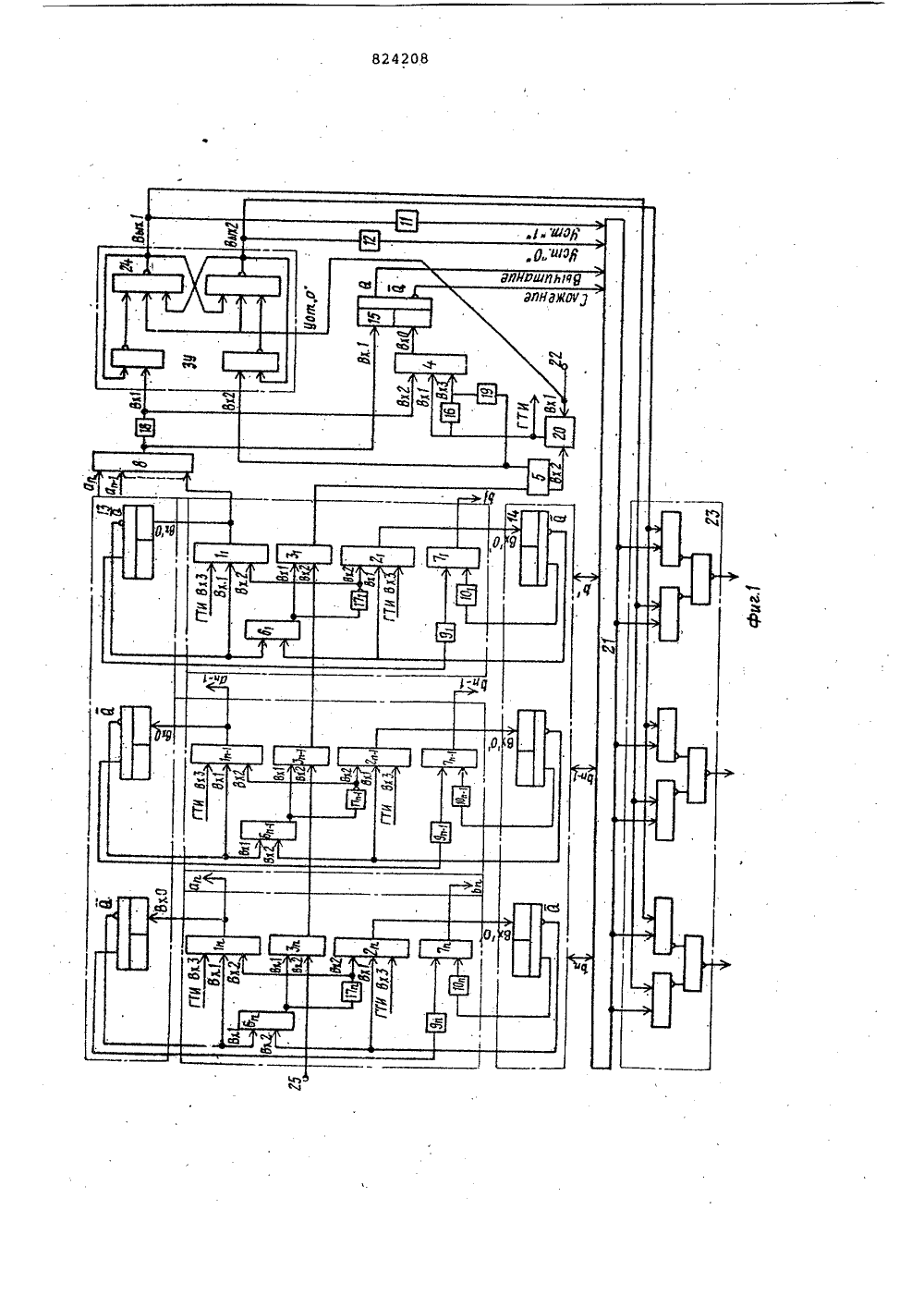

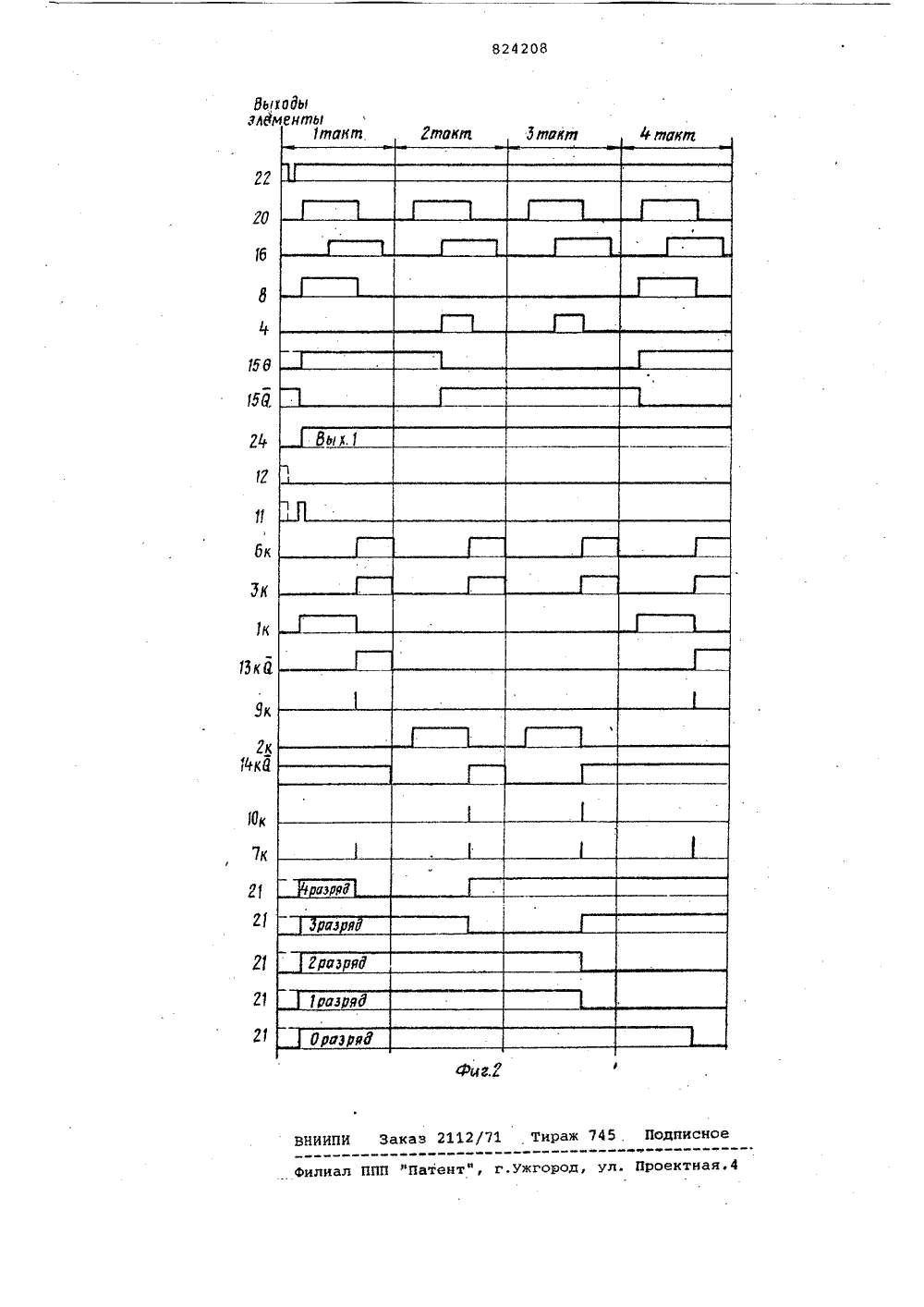

(51)М, К .з С 06 Г 7/62 с присоединением заявки Мо Государственный комитет ССС.Р ло делам. изобретений н открытий/ Дата опубликования описания 230481(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ РАЗНОСТИ ДВУХ И РАЗРЯДНЫХ ЧИСЕЛ Изобретение относится к автоматн ке и вычислительной .технике и может быть использовано в системах автоматического управления и электронных вычислительных машинах.Известно устройство для определения разности двух чисел, содержащее генератор импульсов, выход которого соединен с одними входами пер- вого и второго элементов И, выходы которых подключены ко входам вычитания первого и второго двоичных счетчиков соответственно, выходы которых соединены со. входами блока сравнения, первый ивторой выходы которого подключены и другим входам первого и второго элементов И соответственно, триггеры, элементы ИЛИ, И, НЕ,. счетчик разности 1). Недостатком устрОйства является малое быстродействие, так как количество тактов сравнения равно количеству импульсов, добавленных в счетчик меньшего числа.Наиболее близким к предлагаемому является устройство для определения разности двух чисел, которое .содержит генератор импульсов, выход которого соединен со входами первого,и второго элементов И, выход каждого из которых подключен ко входам сложения и вычитания первого и второго реверсивных счетчиков и первому и второму входам первого элемента ИЛИ, выходы счетчиков соединены со входами блока сравнения, первый и второй выходы которого подключены к другим входам первого и второго элементов И, первому и второму входу второго элемента ИЛИ соответственно, третий выход блока сравнения подключен ко входам первого триггера третьего элемента.ИЛИ, четвертый выход блока срав нения подключен ко входам второго триггера и третьего элемента И, выход которого подключен ко входу треть.его элемента И, выход которого подключен ко входу первого разряда счет О чика разности, вход в."орого разрядакоторого соединен с выходом первого элемента ИЛИ, нулевые входы первого и второго триггера объединены и соединены с шиной установки их в исходное состояние, а их прямые выходы соединены соответственно с другими входами первого и второго элементов И, выход второго элемента ИЛИ через элемент НЕ соединен с другим входом ЗО третьего элемента И 21.Недостатком устройства является малое быстродействие.Цель изобретения - повышение быстродействия.Поставленная цель достигается тем, что устройство для определения разности двух и разрядных чисел, содержацее два элемента И, элемент ИЛИ, первый элемент НЕ, триггер, реверсивный счетчик, генератор тактовых импульсов, выход которого соединен с первым входом первого элемента И, со", держит коммутатор, второй элемент НЕ, блок памяти, элемент задержки, два регистра, два Формирователя импульсов и схему сравнения, каждый 1-й разряд которой (1=1,2и) содержит три элемента И, элемент ИЛИ, элемент НЕ, два Формирователя импульсов и элемент равнозначности, первый и второй входы которого соединены с инверсными выходами 1-х разрядов соответственно 20 второго и первого регистра, а также с первыми входами соответственно первого и второго элементов И 1-х разрядов схемы сравнения, вторые входы которых соединены с выходом элемента 25 НЕ 1-го разряда схемы сравнения, вход которого соединен с выходом элемента равнозначности и с первым входом третьего элемента И 1-го разряда схемы сравнения, третьи входы первого и втОрого элементов И 1-го разряда схемы сравнения соединены с выходом генератора тактовых импульсов, а выхо" ды - соединены с установочными входами разрядов соответственно первого и второго регистров, прямые выходы 1-х разрядов подключены к входам соответственно первого и второго формирователей импульсов 1-х раз.- рядов схемы сравнения, выходы которых соединены соответственно с пер О вым и вторым входами элементов ИЛИ в каждом. 1-ом разряде схемы сравнения, выходы которых подключены к входам соответственно 1-х разрядов реверсивного счетчика импульсов, второй 45 вход третьего элемента И 1-го разря-. да схемы сравнения (3=1,2и) соединен с выходом третьего элемента И (1+1)-го разряда схемы сравне" ния, второй вход третьего элемента О И и-го разряда схемы сравнения соединен с шиной управления устройства, а выход третьего элемента И пер. вого разряда схемы сравнения соеди" нен с первым входом второго элемента И, выходы первого элемента И 1-х разрядов схемы сравнения соединены со входами элемента ИЛИ, выход которого соединен с единичным входом триг. гера и с входом первого элемента НЕ, выход которого соединенс первым 6 О входом блока памяти и вторым входом , первого элемента И, третий вход кото- рого соединен с выходом элемента задержки и с выходом второго элемента НЕ вход которого соединен со вторы мн входами второго элемента И и блока памяти, выход первого элемента И соединен с нулевым входом триггера, инверсный и прямой выходы которого. соединены соответственно со входами "сложения" и "вычитания" реверсивного счетчика импульсов, входы которого "Установка 0" и "Установка 1" соединены с выходами соответственно 1 первого и второго ФорМирователей импульсов, а прямые и инверсные выходы каждого 1-го разряда реверсивного. счетчика соединены соответственно с прямыми и инверсными информационными входами каждого -го разрядакоммутатора, первый и второй входыуправления коммутатора подключены соответственно к входам первого и второго Формирователей импульсов и к первым и вторым выходам блока памяти,. вход "Установка 0" которого соединен с установочной шиной устройства и первым управляющим входом генератора тактактовых импульсов, второй вход которого соединен с выходом второго элемента И, а выход - со входом элемента задержки.На фиг. 1 представлена Функциональная схема устройства, на фиг. 2диаграмма его работы,(ГТИ), реверсивный счетчик 21(импульсов), установочную шину 22, коммутатор 23, блок 24 памяти, шину 25управления.Рассмотрим пример определения разности двух пятиразрядных чисел (01110,записанного в регистр 13 и 10101, записанного в регистр 14). После записичисел в регистры на выходах элементов равнозначности б, 64, о и 61образуется отрицательный потенциал,а на выходе элемента б 3 - положительный. Элементы И 1 , 24, 22 и 14 открыты по первым и вторым входам, элементы И 1 и 2 закрыты по вторымвходам, элементй И 34, 3 и 34 закрыты по первым и вторым входам, элементы И 3 и 3 закрыты по одному извходов.При подаче положительного потенциала па шину 25 управления и отрица"тельного импульса на установочнуюшину 22 производится установка выходов запоминающего устройства в нулевое положение и пуск генератора 20.По первому фронту импульсов генератора 20 на выходе элемента И 1 появляется положительный потенциал, приэтом возбуждается выход элементаИЛИ 8, срабатывает триггер 15 и наего прямом выходе образуется положительный потенциал, подаваемый на вход "вычитания" реверсивного счетчика 21. С выхода элемента ИЛИ 8 сигнал через элемент НЕ 18 проходит на первый вход 24 блока памяти, при этом на его первом выходе образуетсг отрицательный потенциал, который с помощью формирователя 11 подает импульс на вход "становка 1 ф реверсивного счетчика 21, устанавливая все его разряды в единичное положение, блокирует связи блока 24 памяти таким образом, чтобы до конца цикла работы блока изменения на его входах не влияли на состояние его выходов, запрещает прохождение на выходы коммутатора 23 сигналов с прямых выходов триггеров реверсивного счетчика 21 и разрешает прохождение сигналов с его инверсных выходов. По концу генератора 20 импульса на 20 выходе элемента И 1 образуется перепад с высокого потенциала на низкий и на выходе элемента ИЛИ 8 появляется низкий потенциал, триггер пятого разряда регистра 13 меняет свое д 5 состояние, при этом перепад напряжения с прямого выхода триггера. поступает на формирователь импульса 9, с выхода которого сигнал через элемент ИЛИ 7 поступает на вход пятого разряда реверсивного, счетчика 21, устанавливая его триггер в нулевое положение, т.е. производит из содержимого реверсивного счетчика 21 вычитание числа 10000.На инверсном выходе триггера пятого разряда регистра 13 ббразуется низкий потенциал, поступающий на первый вход элемента равнозначности б, при этом на его выходе .устанавливается высокий потенциал, который передает ся через элемент Й 3 на вход элемента И 34. По переднему фронту следующего импульса генератора 20 на выходе элемента 24 появляется положительный потенциал, а на выходе 14 он не появляется, поэтому элемент ИЛИ 8 не срабатывает, срабатывание элемента И 4 по второму входу не запрещается, поэтому в момент срабатывания элемента 16 задержки на выходе элемен-. та И 4 появляется положительный потенциал, приводящий к срабатыванию триггера 15, который положительным потенциалом на своем инверсном выходе возбуждает вход сложение" реверсивного счетчика 21 (и отрицательным потенциалом на своем прямом вы" ходе снимает возбуждение со входа "вычитания"). По концу импульса генератора 20 на выходе элемента 2, ьбразуется перепад с высокого потенциа ла на низкий, и триггер четвертого разряда регистра 14 меняет свое состояние, при этом перепад напряжения с прямого выхода триггера поступает на Формирователь 10, импульса, пройДя 65 который сигнал через элемент ИЛИ 74поступает на вход четвертого разрядареверсивного счетчика 21, при этомпроизводится сложение числа.10000 ссодержимым счетчика.На инверсном выходе триггера четвертого разряда регистра 14 образу"ется низкий потенциал, поступающийна второй вход элемента равнозначности бд, при этом на его выходе устанавливается высокий потенциал, кото"рый передается через элемент И 34, наЪход элемента И 3 и далее на вход эле.элемента И 32, так как на выходе элемента И 3 присутствует высокий по"тенциал в силу равенства 1 третьихЭю еразрядов обоих сравниваемых чисел.При третьем и четвертом импульсахгенератора,20 работа устройства происходит аналогично, т.е. в результате производится сначала сложениечисла 10 с содержимым реверсивногосчетчика 21, а затем вычитание изнего числа 1. После появления поло"жительного потенциала на выходе элемента 64 равнозначности и окончания импульса на выходе элемента 16задержки срабатывает элемент И 5 ивыключает генератор 20.Таким образом, в реверсивном счетчике 21 будет записано число 11000,представляющее собой разность сравниваемых чисел в обратном коде,На инверсных выходах триггеровреверсивного счетчика 21 окажетсязаписанным это число в прямом коде.Оно поступает на один из входов коммутатора 23, на выходе которого иокажется записанной разность сравниваемых чисел 00111.Если на определение разности двухчисел с помощью известного устройства затрачивается не более 2 " импульсов тактовой частоты, то с помощЬюпредлагаемого устройства не более иимпульсов тактовой частоты, где иколичество разрядов большего числа,и выигрыш во времени составляет2" " /и раз.Формула изобретенияУстройство для определения разнос- ти двух и разрядных чисел, содержащее два элемента И, элемент ИЛИ, первый элемент НЕ, триггер, реверсивный счетчик, генератор тактовых импульсов, выход которого соединен о первым входом первого элемента И, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены коммутатор, второй элемент ЯЕ,. блок памяти, элемент задержки, два регистра, два Формирователя импульсов и схема сравнения, каждый 1-й разряд которой (1=1,2 и) содержит три элемента И, элемент ИЛИ, элемент НЕ, два формирователяимпульсов и элемент равнозначности, первый и второй входы которого соединены с инверсными выходами 1-х разрядов соответственно второго и первого регистра, а также с первыми входами соответственно первого 5 и второго элементов И, -х разрядов схемы .сравнения, вторые входы которых соединены с выходом элемента НЕ 1-го разряда схемы сравнения, вход которого соединен с выходом .элемента10 равнозначности и с первым входом третьего элемента И -го разряда схе- мы сравнения, третьи входы первого и второго элементов И 1-го разряда схемй сравнения, соединены с выходом генератора тактовых импульсов, авыходы - соединены с установочными входами разрядов соответственно первого и второго регистров, прямые выходы -х разрядов подключены к входам соответственно первого и второго Фор О мнрователей импульсов 1-х разрядов схемы сравнения, выходы которых соединены соответственно с первым и вторым входами элементов ИЛИ в каждом -ом разряде схемы сравнения, выходы кото- з 5 рых подключены к .входам соответственно 1-х разрядов реверсивного счетчика импульсов, второй вход третьего элемента И -го разряда схемы сравнения (=1,2п) соединен с выходом третьего элемента И (1)-го разряда схемы сравнения, второй вход третьего элемента И л-го разряда схемы сравнения соединен с шиной управления устройства, а выход третьего элемента И первого разряда схемы сравнения соединен с первым входом второго элемента И, выходы первого элемента И -х разрядов схемы сравнения соединены со входами элемента ИЛИ, выход которого соединен с единияным входом триггера и с входом первого элемента БЕ, выход которого соединен с первым входом блока памяти ивторым входом первого элемента И,третий вход которого соединен с выходом элемента задержки и с выходомвторого элемента НЕ, вход которогосоединен со вторыми входами второгоэлемента И и блока памяти, выход первого элемента И соединен с нулевым,входом триггера, инверсный и прямойвыходы которого соединены соответственно со входами "сложения" и "вычитания" реверсивного счетчика импульсов, входы которого "Установка 0" и"Установка 1" соединены с выходамисоответственно первого и второго Фор-.мирователей импульсов, а прямые и инверсные выходы каждого -го разряда реверсивного счетчика соединенысоответственно с прямыми и инверсными инФормационными входами каждого-го разряда коммутатора, первыйи второй входы управления коммутатора подключены соответственно к вхо-.дам первого и второго Формирователяимпульсбв и к первым и вторым выходам блока памяти, вход "Установка О"которого соединен с установочной шиной устройства и первым управляюцимвходом генератора тактовых импульсов,второй вход которого соединен с выходом второго элемента И, а выход -со входом элемента задержки. Источники инФормации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Р 341031, кл. 2 6 Об Г 7/02, 1970. 2. Авторское свидетельство СССР Р 5992 б 4, кл. 2 С Об Г 7/04, 1978.824208дыи 0 ы зьдменаы ггк Зкй 2 ВНИИПИ Заказ 2112/71 Тираж 745, Подписноеиал ППП фПатент", г.Ужгород, ул. Проектная,4

СмотретьЗаявка

2790870, 05.07.1979

ПРЕДПРИЯТИЕ ПЯ А-3697

СЕВАСТОВ ЛЕОЛЬ ИРАКЛИЕВИЧ, ЛОГАЧЕВ АНАТОЛИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 7/62

Метки: п-разрядных, разностидвух, чисел

Опубликовано: 23.04.1981

Код ссылки

<a href="https://patents.su/6-824208-ustrojjstvo-dlya-opredeleniya-raznostidvukh-p-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для определения разностидвух п-разрядных чисел</a>

Предыдущий патент: Устройство для вычисления функций

Следующий патент: Устройство для последовательного сум-мирования частотно импульсных сигналов

Случайный патент: Устройство для загрузки в штабеля рулонов бумаги