Запоминающее устройство с обнаружением и исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

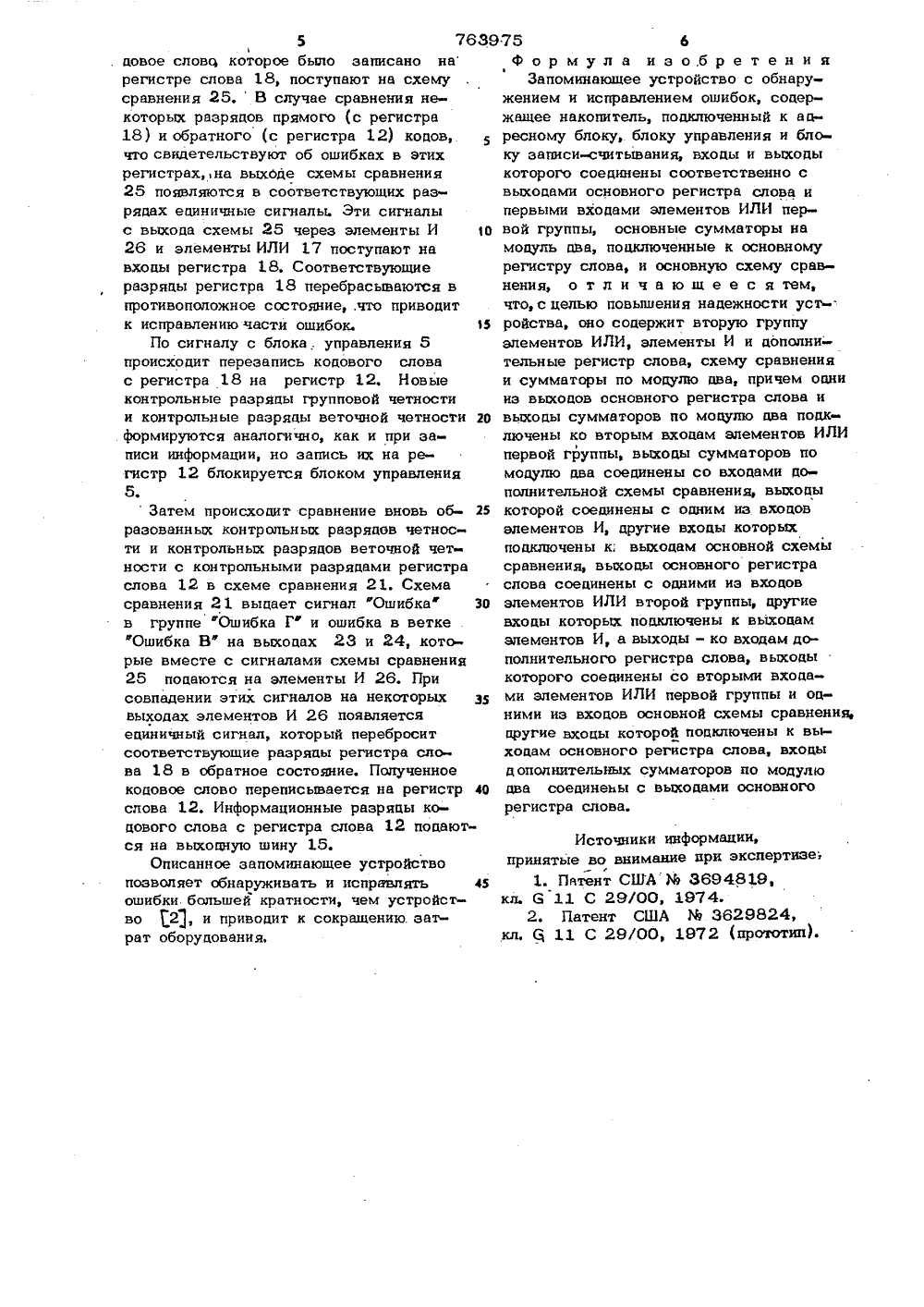

Щ Союз СоветскихСоциалистическихРеспублик ОП ИОАН ИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1 ц 763975(22) Заявлено 13.02,78 (21) 2579287 Л 8-24с присоединением заявки тй(53)М. Кл. 6 11 С 29/00 Гасударстоанный комитет по делам изобретений и открытийКиевский ордена Ленина политехническийинститут им. 50-летия Великой Октябрьскойсоциалистической революции1Изобретение относится к запоминшощим устройствам .Известны запоминающие устройства с обнаружением и исправлением ошибок Ц и С 21.Одно из известных устройств сопержит накопитель, формирователи управляющих сигналов, кодирующий и декодирующий блоки Я,Цедостатком этого устройства являюттпся большие аппаратурные затраты,Из известных устройств наиболееблизким техническим решением к данному изобретению является запоминающее устройство с обнаружением и исправт 5лением ошибок, содержащее накопитель,поцключенный к адресному блоку, блокууправления и блокут записи считывания, .входы и выходы которого соединены соответственно с выходами основного регистра слова и первыми входами элементовИЛИ первой группы, основные сумматорыпо мопулю пва, подключеннье к основному регистру слова, и основную схему сравнения 2 1.Недостатками этого устройства с обнаружением и исправлением ошибок яв. ляются малая обнаруживающая и корректирующая. способность, так как оно позволяет исправлять ошибку только в пределах одного байта и большие затраты оборудования. Указанные недостатки снижают надежность устройства.1 Ьль изобретения - повышение надежности устройства.Поставленная цель достигается тем, что устройство содержит вторую группу элементов ИЛИ, элементы И и цополнительные регистр слова, схему сравнения и сумматоры по модулю цва, причем одни из выходов основного регистра слова и выходы сумматоров, по модулю двапопключены ко вторым входам элементов ИЛИ первой группы, выходы сумматоров по модулю два также соединены со вхоцами дополнительной схемы сравнения, выходы которой соединены,с одними ив входов3975 4 55 3 76элементов И, другие входы которых подключены к выходам основной схемы сравнения, выходы основного регистра словасоединены с одними из входов элементовИЛИ второй группы, другие входы которыхподключены к выходам элементов И, а выходы - ко входам дополнительного регисчра слова, выходы которого соединены совторыми входами элементов ИЛИ первойгруппы и одними из входов основной схемы сравнения, другие входы которойподключены к выходам основного регистр"ра слова, входы дополнительных сумматоров по модулю два соединены с выходами основного регистра слова.На фиг. 1-3 изображена структурнаясхема предложенного устройства,Запоминающее устройство соцержит(см.фиг. 1-3) накопитель 1, вход 2которого подключен к выходу адресного блока 3, имеющего информационныйвход 4, блок управления 5, имеющийвходы 6-9, блок 10 записи-считывания,первую группу элементов ИЛИ 11, основной регистр слова 12, основные сумматоры 13 по модулю два, дополнительныесумматоры 14 по модулю два, шину 15выхоц информационного слова, шину 16вход информационного словаф, вторуюгруппу элементов ИЛИ 17, донолнительный регистр слова 18. В регистре слова12 имеются контрольные разряды 19групповой четности и контрольные разряды 20 веточной" четности.Устройство также содержит допблнительную схему сравнения 21, имеющуювыхоцы 22-24, основную схему сравнения25, элементы И 26. Выходы блока 10соецинены с первыми входами элементовИЛИ 11. Одни из выходов регистраслова 12 и выходы сумматоров 13 и 14подключены ко вторым входам элементовИЛИ 11. Выходы сумматоров 13 и 14соединены со входами схемы сравнения21, выходы которой соединены с однимииз входов элементов И 26, другие входы которых подключены к выходам схемысравнения 25, Выходы регистра слова12 соединены с одними из входов элементов ИЛИ 17, другие входы которыхподключены к выходам элементов И 26,а выходы - ко входам регистра 18, выходы которых соецинены со вторымивхоцами элементов ИЛИ 11 и однимииз входов схемы сравнения 25, другиевходы которой подключены к выходамрегистра слова 12, Входы сумматора 14соединены с выходами регистра слова12,5 10 15 20 25 Зо 35 40 45 50 Запоминающее устройство работает следующим образом.В режиме записи на шину 16 поступает информационное слово, которое через элементы ИЛИ 11 записывается в информационных разрядах регистра слова 12. Информационные разряды этого ре гистра условно разделены на группы.Значения каждой из групп поступают на соответствующий сумматор 13, где формируются значения контрольных разрядов 19 групповой четности. Значения четности цля каждой из групп разрядов записываются через элементы ИЛИ 11 в соответствующие разряды 19 регистра слова 12. Одновременно значения-х разрядов каждой группы поступают на соответствующий-й сумматор 14. Значение бита четности цля каждой 1 -й ветви подается через элементы ИЛИ 11 в-й разряд 20 веточной четности. По сигналу с блока управления 5 осуществляется запись закодированного слова (коцового слова) через блок 10 в ячейку накопителя 1, номер которой задан кодом ацреса на выходе блока 3.При считывании информации образование всех контрольных разрядов групповой четности и неточной четности происходит так же,как и при записи, только блок управления 5 блокирует запись этих разрядов с сумматоров 13 и 14 нарегистр слова 12. Вновь обработанные контрольные разряды групповой четности и контрольные разряды веточной четности подаются в схему сравнения 21;где осуществляет ся сравнение образованных контрольных разрядов групповой четности и веточной четности с первоначальными значениями, которые были записаны в соответствующих разрядах регистра слова 12 при чтенйи из накопителя 1. При несовпадении считанных и вновь образованных контрольных разрядов групповой и веточной четности схема сравнения 2 1 выдает сигнал Ошибка" на выход 24. Если не совпадают р контрольных разрядов веточной четности и один 1 -й разряд групповой четности, то эта ситуация индицируется схемой сравнения 21 как. пачка ошибок в 0 -й группе разрядов, длина которых р.о По сигналу Ошибка с выхода 22схемы сравнения 21 и сигналу с блокауправления 5 происходит инвертированиекодового слова с записью в накопительИсточники информации,принятые во внимание при экспертизе; 1. Патент СШАМ 3694819,кл. б 11 С 29/00, 1974. 2. Патент США % 3629824,кл. Я 11 С 29/00, 1972 (прототип).5 7639довое словс которое было записано нарегистре слова 18, поступают на схемусравнения 25.В случае сравнения некоторых разрядов прямого (с регистра18) и обратного (с регистра 12) кодов,что свидетельствуют об ошибках в этихрегистрахна выходе схемы сравнения25 появляются в соответствующих разрядах единичные сигналы. Эти сигналыс выхода схемы 25 через элементы И О26 и элементы ИЛИ 17 поступают навходы регистра 18. Соответствующиеразряды регистра 18 перебрасываются впротивоположное состояниечто приводитк исправлению части ошибок. 15По сигналу с блока, управления 5происходит перезапись кодового словас регистра 18 на регистр 12, Новыеконтрольные разряды групповой четностии контрольные разряды веточной четности 20формируются аналогично, как и при записи информации, но запись их на регистр 12 блокируется блоком управления5.Затем происходит сравнение вновь образованных контрольных разрядов четности и контрольных разрядов веточной четности с контрольными разрядами регистраслова 12 в схеме сравнения 21. Схемасравнения 21 выдает сигнал "Ошибка 30в группе Ошибка Г" и ошибка в веткефОшибка Вф на выходах 23 и 24, которые вместе с сигналами схемы сравнения25 подаются на элементы И 26. Присовпадении этих сигналов на некоторых З 5выходах элементов И 26 появляетсяединичный сигнал, который переброситсоответствующие разряды регистра слова 18 в обратное состояние. Полученноекодовое слово переписывается на регистр ФОслова 12. Информационные разряды кодового слова с регистра слова 12 подаются на выходную шину 15.Описанное запоминающее устройствопозволяет обнаруживать и исправлять 45ошибки. большей кратности, чем устройство 2, и приводит к сокращению. затрат оборудования,75 6формула изобретенияЗапоминающее устройство с обнаружением и исправлением ошибок, содержащее накопитель, подключенный к адресному блоку,. блоку управления и блоку записи-считывания, входы и выходы которого соединены соответственно с выходами основного регистра слова и первыми входами элементов ИЛИ первой группы, основные сумматоры на модуль два, подключенные к основному регистру слова, и основную схему сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности уст-. ройства, оно содержит вторую группу элементов ИЛИ, элементы И и дополнительные регистр слова, схему сравнения и сумматоры по модулю два, причем одни из выходов основного регистра слова и выходы сумматоров по модулю два подключены ко вторым входам элементов ИЛИ первой группы, выходы сумматоров по модулю два соединены со входами дополнительной схемы сравнения, выходы которой соединены с одним из входов элементов И, другие входы которых подключены к, выходам основной схемы сравнения, выходы основного регистра слова соединены с одними иэ входов элементов ИЛИ второй группы, другие входы которых подключены к выходам элементов И, а выходы - ко входам дополнительного регистра слова, выходы которого соединены со вторыми входами элементов ИЛИ первой группы и одними из входов основной схемы сравнения, другие входы которой подключены к выходам основного регистра слова, входы дополнительных сумматоров по модулю два соединены с выходами основного регистра слова.7639 75 Й/2,5 Составитель В, Рудакоая Техред М. Кузьма Редактор Т. Ор рректор Е. Панн аказ Филиал ППП "Патент", г, Ужгород, ул. Проектна 6292/45 Тираж 662 Подписи ВНИИ ПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская нвб., д. 4/5

СмотретьЗаявка

2579287, 13.02.1978

КИЕВСКИЙ ОРДЕНА ЛЕНИНА ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. 50 ЛЕТИЯ ВЕЛИКОЙ ОКТЯБРЬСКОЙ СОЦИАЛИСТИЧЕСКОЙ РЕВОЛЮЦИИ

ГОРОДНИЙ АЛЕКСАНДР ВАСИЛЬЕВИЧ, КОРНЕЙЧУК ВИКТОР ИВАНОВИЧ, ТКАЧЕНКО ВАЛЕНТИНА ВАСИЛЬЕВНА, СЕРГЕЕВ АЛЕКСАНДР ИОСИФОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: запоминающее, исправлением, обнаружением, ошибок

Опубликовано: 15.09.1980

Код ссылки

<a href="https://patents.su/6-763975-zapominayushhee-ustrojjstvo-s-obnaruzheniem-i-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с обнаружением и исправлением ошибок</a>

Предыдущий патент: Устройство для контроля блоков памяти

Следующий патент: Устройство для разбраковки магнитных элементов

Случайный патент: Энерготехнологическая установка