Устройство для оптимизации структуры сложных систем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 678489

Авторы: Кобчиков, Нежметдинов, Травин

Текст

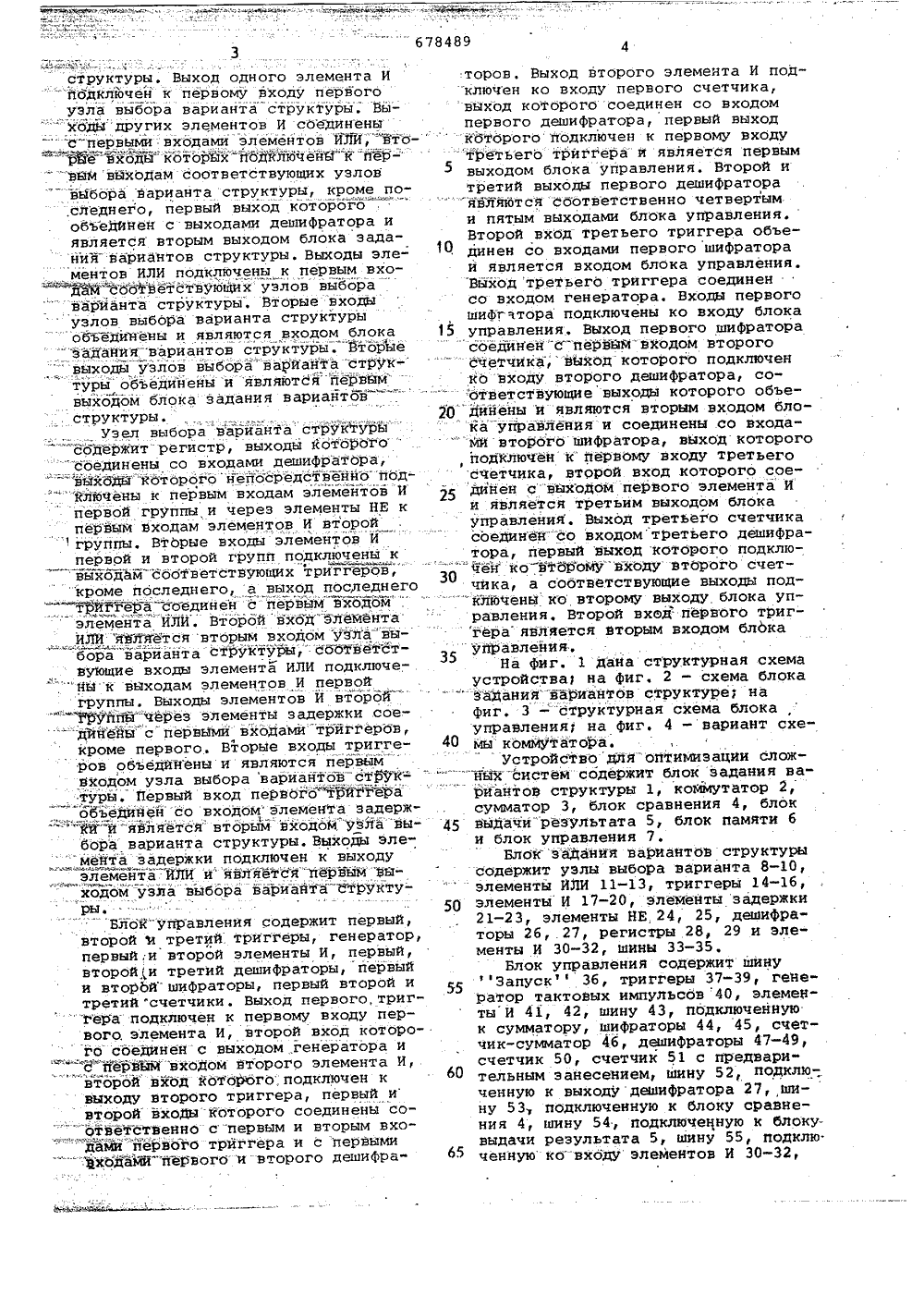

О П И С А Н И Е".ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистических Республик(22) Заявлено 220477(21) 2486361/18-24с присоединением заявки Йф -(51)М. КЛ.2 а 06 Г 15/20 Государственный комитет СССР во делам изобретений и открытий(71) ЗаяВИтЕЛЬ Казанский ордена Трудового Красного Знамени государственныйуниверситет им. В.И, Ульянова-Ленина(54) УСТРОЙСТВО ДЛЯ ОПТИМИЗАЦИИ СТРУКТУРЫ СЛОЖНЫХ СИСТЕМИзобретение относится к областивычислительной техники и может бытьиспользовано для конструированиясложных систем при оптимизации.структуры систем, состоящей из иподсистем различного типа, по критерию минимума суммарной характеристики выбранных вариантов подсистемс учетом связей междуними .Известны устройства, производящие выборку и суммирование значенийпараметров (1, однако они решаютограниченный класс задач.Наиболее близким по техническойсущности к изобретению являетсяIустройство для оптимизации размещения центров радиальной сети по минимуму суммарной стоимости линии связи 2, содержащее блок памяти, сумматор, блок сравнения и блок выдачи,Недостатком известного устройстваявляется невозможность решения.-задачи оптимизации систем со сложнойструктурой,Целью изобретения является расширение класса решаемыхзадач.Поставленная цель достигаетсятем, что в предложенное устройствовведены коммутатор, блок управленияи блок задания вариантов структуры,Первый вход блока задания вариантовструктуры подключен к первому входублока выдачи результатов и первомувходу коммутатора, выхбд которбгосоединен с первым входом сумматора,выход которого подключен"к первомувходу блока сравнения и ко второмувходу блока выдачи резулЬтатов. Выход блока сравнения соединен с третьим входом блока выдачи результата, .выход которого подключен ко второмувходу блока сравнения. Первый, второй; третий, четвертый и пятый вы-,ходы блока управления соединены соответственно со входом блока заданиявариантбв бФуктура - со- вторым вхо-дом коммутатора, со вторым входомсумматора, со вторым входом блокасравнения и с четвертым входом блока выдачи результата. Вход блока управления подключен ко второму выходу блока задания вариантов структуры.Выход блока памяти соединен с треть 25 им ВхОдом коммутатора,Блок задания вариантов структурысодержит регистр, выходы которогочерез дешифратор соединены с первыми входами элементов И, вторые входы которых объединены и являютсявходами блока задания вариантовструктуры. Выход одного элемента ИПодключен к первому входу первогоузла выбора варианта струкТуры, Вы- " хоМИ других элементов И соединеныс"первыми входами элементов ИМИ, "вто-9 евходй которйх подключ еййк -пер-""вым выходам соответствующих узловвыбора варианта структуры, кроме по.следнего, первый выход которогообъедйнен с выходами дешифратора иявляется вторым выходом блока задания вариантов структуры. Выходы элементов ИЛИ подключены к первым вхоДЖГсбответствуюйих узлов выбораварианта структуры, Вторые входыузлов выбора варианта структурыобъединены и являются входом блоказадаййя-вариантов структуры. Вторитевыходй узлов выбора"варйанта струк туры объединейы и являются йервймвыходом блока задания вариайтов, структуры.Узел выбора варианта струк 1 гурысодержит-регистр, выходй котоРого" соединены со входами дешифратьра,.ключены к первым входам элементов Ипервой группы и через элементы НЕ кпервым входам элементов И второйгруппы. Втдрые входы элементов Ипервой и второй групп подключены квйходХм=собтветствующих триггеров,"кроме последнего, а выход последнеготрйггера сбидинен с первым входом"элемента ИЛИ. Второй входэлЕментаИЛИ является вторым входом узлавыбора варйанта стРуктуры, СоевотствуЮщие входы элемента ИЛИ подключе"ны к выходам элементов И первойгруппы. Выходы элементов И второй""груйпй"через элементы задержки сое - "дйнейы с первыми входами трйггеров,кроме первого. Вторые входы триггеров объедийены и являются первымвходом узла выбора вариайтов-стФК-туры. Первый вход первого"ЯУйггеРаобъединЕн со входом элемен"га задерж кй й "яйляется вторым входом "узла выбора варианта структуры. Выходю элемента задержки подключен к выходу" элемейта.ЙЙИ и является Первым выходом -узла выбора вариайта" бТРУктуры,Блок"угравления содержит первый,второй м третий триггеры, генератор,первый,и второй элементы И, первый,второй,и третий дешифраторы, первыйи вторЬй"шифраторы, первый второй итретий "счетчики . Выход первого, триггеРа подключен к первому входу первого, элемента И, второй вход которого соединен с выходом генератора и" с "Керййй входом второго элемента И,второй вход котоРого.подключен квыходу второго триггера, первый ивторой входы кбторого соединены со" ответственно с "первым и вторым входайюйервого трйггера и с первыми"Фходйь 3 И"первого и-второго дешифраторов, Выход второго элемента И подключен ко входу первого счетчика,выход которого соединен со входомпервого дешифратора, первый выходкбгорого подключен к первому входу"третьего триггера и является первымвыходом блока управления, Второй итретий выходы первого дешифратора" -"являйтся соответственно четвертыми пятым выходами блока управления.Второй вход третьего триггера объе 1 О динен со входами первого шифратораи является входом блока управления.Вйход третьего триггера соединенсо входом генератора. ВходЫ первогошифгчтора подключены ко входу блока15 управлейия, Выход первого шифраторасоединен"с"первым"входоМ второгосчетчика, Выход которого подключенко входу второго дешифратора, соответствующие выходы которого объе 20 чинены и являются вторым входом блока управления и соединены со входа" ьФ второго шифратора, выход которого,подключен к первому входу третьегосчетчика, второй вход которого соединен с выходом пеРвого элемейта ии является третьим выходом блокауправления, Выход третьего счетчикасоединен со входомтретьего дешифратора, первый выход которого подклю 0"чен ко вгбройу"входу второгосчетчика, а собтветствующие выходы подклюЧены ко второму выходу блока управления. Второй вход первого триггера является вторым входом блока3 управления,На фиг. 1 дана структурная схемаустройства) на фиг, 2 - схема блока" " залания-вариантов структуре; нафиг, 3 - -структурная схема блока,управления; на фиг. 4 - вариант схе 40 мы комйутатора.устройстводля оптимизации сложййх "систем содержит блок задания вариантоВ структуры 1, коммутатор 2,сумматор 3, блок сравнения 4, блок45 выДачи"результата 5, блок памяти би блок управления 7,Блок-задания вариантой структурысодержит узлы выбора варианта 8-10,элементы ИЛИ 11-13, триггеры 14-16,элементы И 17-20, элементы задержки21-23, элементы НЕ 24, 25, дешифра"торы 26,.27, регистры 28, 29 и элементы И 30-32, шины 33-35,Блок управления содержит шинуЗапуск 1 36, триггеры 37-39, генератор тактовых импульсов 40, элементыИ 41, 42, шину 43 подключеннуюк сумматору, шифраторы 44, 45, счетчик-сумматор 4 б, дешифраторы 47-49,счетчик 50, счетчик 51 с предварительным занесением, шину 52, подклю-,ченную к выходу дешифратора 27, шину 53, подключенную к блоку сравнения 4, шину 54, подключенную к блокувыдачи результата 5, шину 55, подклю.ченную ко входу элементов И 30-32,,шину 56, подключенную к выходу 35блока задания вариантов 10,Устройство работает следующим образом.Перед началом оптимизации в регистр числа подсистем 29 записывается количество оптимизируемых подсис-"тем. Например, при С подсистемах, навыходе 1 = и-С дешифратора 27 появляется разрешающий сигнал, открывающий элемент И 31 для прохождения через него сигналов сдвига по"шине 33с выхода 55 дешифратора 49 блока управления на вход соответствующегоузла выбора вариантаструктуры, Сигнал с 1"го выхода дешифратора 27 пошине 34 через шифратор 45 поступает 15на счетчик с предварительным занесе-нием 51. При этом разрешающий сигналпоявляется на 1-м выходе дешифратора 48. Этот сигнал поступает на все-вертикальные ряды элементов И комму Отатора, имеющиеиндекс вида у/ай инаХ-й вход шифратора 44, а с еговыхода - в счетчик-сумматор 46, свыхода которого через 1-й выход дешифратора 47 разрешающий сигнал поступает на все горизонтальные ряййэлементов И коммутатора, имеющиеиндекс гз/1+1,1,Таким образом, на входы элементаИ 1,1/1+1, . коммутатора подаетсяразрешающйй сигнал с блбка 2 с выхода триггеров (Т; -1) -го триггера1-го узла и,(Т;+ -1)-го триггеровследующего (+1)-го узла выбора вариантов, с блока управления (с выходов 3. дешифраторов 47 и 48). уп-равляющий вход данного элемента Иподключен к выходу регистра блокапамяти 6, содержащего значение характеристики общих элементов перво-"го варианта подсистемы 1 с первым 40вариантом подсистемы 3.+1., Это значение характеристйкй"общих элементовс выхбда элемента И подается на сумматор 3, Причем в соответствии сфункционалом значения характеристики общих элементов различных подсистем поступают со знаком минус ,а значение характеристики вариантаподсистемы - со знаком плюс.Сигнал Запуск устанавливает 50,через соответствующие элементИЛИр элемент задержки (для узла 1-гойыбора вариантов 12 и 23) первые .т.риггеры всехузлов выбора вариантов в 1, создавая тем самым на 55ваходе блока задания вариантовс.труктуры первую комбинацию вариантсв подсистем. Одновременно сигналЗапуск устанавливает триггер 4в положение 1 и запускает гене- -р тор тактовых импульсов 5, а также устанавливает триггер 38 в по-ложение 1. После этого импульсь 1 генератора тактовых импульсов4 Й через элемент И 41 начинают прохэдить на вход счетчика-сумматора " 8946 . Первый импульс генератора складывается с числом, подаваемым с ши- фратора 44, которое до этого устанавливало напряжение-на 1-м выходе дешифратора 47, после чего напряжение появляется на (1+1)-ом выходе этого дешифратора. Это напряжение подается на все гбризонтальные ряды элементов И с индексом гз/1+2,(, благодаря чему открывается элемент И 1,1/1+2, , и на сумматор поступает для сложения с предыдущим значение характеристикиобщих элементов первого варианта подсистемы 1 с первым вариантом следующей подсистемы 1+2 и т,д. до 1-го импульса генератора тактовых импульсов, который открывает последний элемент И данного вертикального ряда, После этого на блок вычисления поступает значениехарактерйстики первого варианта подсистемы 1, После следующего импульса генератора сигнал с последнего п+1-го выхода дешифратора 47 поступает на вход счетчика с предварительным занесением 51 и складывается с числом, поступившим через деширратор 27 от регистра числа подсистем 29. В результате напряжение появляется на следующем (1+1) выходе дешифратора 48 и поступает на (1+1)-й вход шифратора 44. Следующий импульс генератора вызывает появление напряжения на (3.+2)-ом выходе дешифратора 47. При этом открываютсяэлементы 1+1/1+2,1 коммутатора, и на сумматорпоступает значение характеристики общих элементов первого варианта подсистемы (1+1) с первым вариантом подсистемы 1+2, и т.д. до суммирования последнего значения характеристики первого варианта последней подсистемы. После этого на (и+1)-м выходе дешифратора 48 появляется напряжение, устанавливающее триггер 37 в положение 0, а триггер 38 в положение1В результате сигналы генератора тактовых импульсов прекращают проходить через элемент И 41 и начинают проходить через элеМент И 42 на вход счетчика 50. Сигналы с выходов дешифратора 49,объединенных кодовыми шинами 52 и 53 используются соответственно для управления блоком сравнения 4 и блоком 5, Значение суммарной характеристики с выхода блока вычисления суммарной,характеристики поступает на вход схемы сравнения, где сравййвается со значением суммарной характеристики предыдущей комбинации вариантов, поступающим из регистра записи суммарной характеристики блока выдачи результата. ЕСли новое значение боЛьше предйдущего, то сигнал на выходе схем сравнения открйвает первый элемент И блока выдачи результата, через коФормула изобретения 15 7 67тбрый в регистр записи комбинациис блока задания вариантов структурыпоступает новая комбинация и второйэлемент И блока выдачи результата,через который в регистр записи суммарной характеристйки с выхода сумматора поступает новое значение суммарной характеристики выбранной комбинации вариантов. Если новое значение суммарной характеристики большестарого, в регистрах сохраняютсястарые значения. После того как счетчик 50 отсчитает число сигналов, необходимое для управления схемой сравнения и блоком управления, следующий сигнал генератора тактовых импульсов вызывает -появление напряжения сдвига на последнем выходе дешиФратора 49, которое устанавливаеттриггер 37 в положение ф 1, а триггер 38 в положение фОф, Одновременйо напряжение сдвига по шине 34через открытый элемент И 31 и элемент ИЛИ 11 поступаЕт на вход"первого триггера 1-го узла выбора варианта 9, устанавливая его в состояниефОф, При этом на выходе триггера14 "пбявляется сигнал, который черезэлемент И 14, открытый при нулевомсостоянии 1-го выхода дешифратбра26 и элемент задержки устанавливает11 1следующий триггер в состояние 1открывая тем самым элементы И коммутатора, связанные с регистрамиблока памятй, где хранятся данныесоответствующие второму вариайтуданной подсистемы и т.д. до последнего Х-го варианта установленного"нарегистре числа вариантов 28, Навыходе дешифратора этого регистраприсутствует разрешающий сигнал,открывающий элемент И 17, через который сигнал запуска, пройдя черезэлемент ИЛИ,12 и элемент задержки23, сноваустанавливает первый триггер 14 в состояние .ф 1 ф. Через элемент ИЛИ 13 сигйал постУПает на входследующего (1+1)-го узла выбора варианта и переводит его первый триггер из состояния 1 фф в состояниеО, При этом следующий триггерустанавливаетсяв состояние ф 1, иоткрываются элементы И коммутатора,связанные с ячейками, соответствующими второму варианту второй подсистемы.После перебора всех вариантовпервой подсистемы сигнал сдвига вызывает"переход к третьему вариантувторой подсистемы и т.д. до последнего записанйого в регистречиславариантов второй подсистемы, Послеэтого сигнал сдвига переходит наследующий (3.+2) -й узел выбора варианта структурй и т.д. до оконча-ния перебора, когда сигнал с выходаи-го узла выбора варианта поступаетна второй вход триггера 39 и устанавливает его в состояние О н,8489 8т ем самым выключ ает ген ер атор т ак -овых импульсов 40, После этого устройство работу заканчивает, При этомв регистрах записи комбинации и записи суммарной характеристики блокавыдачи результата записаны искомаякомбинация и соответствующее ей значение суммарной характеристики, которые выдаются на индикаторы.Предложенное устройство благодаря наличию новых блоков и связей 10 между ними обеспечивает решение задачи оптимального выбора структурысистемы. 1, Устройство для оптимизацииструктуры сложных систем, содержащее блок памяти, сумматор, . блоксравнения и блок выдачи результата,о т л и ч а ю щ е е с я тем; что,с целью расширения класса решаемыхзадач, в устройство введены коммутатор блок управления и блок заданиявариайтов структуры, причем первыйвыход блоказадания вариантов структуры подключен к первому входу блокавыдачи результата и первому входукоммутатора,.выход которого соединен с первым входом сумматора, выход которого подключен к первомувходу блока сравнения и ко второмувходу блока выдачи результата, выход блока сравнения соединен с треть.им входом блока выдачи результата,выход"кЪторого подключен ко второмувходу блока;сравнения, первый, второй, третий, четвертый и пятый выходы блока уйравпения соединены соответственно со входом блока задания 40 вариантов структуры, со вторым входом комйутатора, со вторым входомсумматора, со вторым входом блокасравнения и счетвертым входом блокавыдачи результатов, вход блока уп-45 равления подключен ко второму выходу блока задания вариантов структуры, выход блока памяти соединен стретьим входом коммутатора.2. Устройство по п, 1, о т л и ч а ю щ е е с я тем, что блок задания"вариантов структуры содержитрегистр, выходы которого через дешифратор соединеныс йеРвыми вход,ами элементов И, вторые входы котс рых объединены и являются входом,блока задания вариантов структур,выход одного элемента И подключе,нк первому входу первого узла выб сраварианта структуры, выходы други) элементов И соединены с пеРвыми входами элементов ИЛИ, вторые входьторых подключены к первым выход,мсоответствующих узлов выбора валящаята структуры, кроме последнего, п р65вый выход которого объедйнен с в,ыходами дешиФратора и является втордм6784 20 выходОм блока задания варианта структуры, выходы элементов ИЛИ подключены к первым входам соответствующих узлов выбора варианта структуры, в.орые входы всех узлов выбора варианта структуры объединены и являются входом блока задания вариантовструктуры, вторые выходы узлов выбора вариантов структуры объединены и являются первым выходом блока задания вариантов структуры.3. Устройство по пп. 1,2, о т - 10 л и ч а ю щ е е с я тем, что узел выбора вариантов структуры содержит регистр, выходы которого соединены со входами дешифратора, выходы которого непосредственно подключены - 15 к первым входам элементов И первой группы и через элементы НЕ к первым входам элементов И второй группы, вторые входы элементов И первой и второй групп подключены к выходам соответствующих триггеров, кроме последнего, а выход последнего триггера соединен с первым входом элемента ИЛИ, второй вход элемента ИЛИ является вторым входом узла выбора варианта структуры, соответствующие входы элемента ИЛИ подключены к выходам элементов И первой группы, выходы элементов И второй группы через элементы задержки соединены с первыми входами триггеров кроме первого, вторые входы триггеровобъединены и являются первым входом узла выбора варианта структуры, первый вход первого триггера объединен со входом элемента задержки и являет-. ся вторым входом узла"выбора варианта структуры, выход элемента задержки подключен к выходу элемента ИЛИ и является первым выходом узла выбора варианта структуры. 404. Устройство по и. 1, о т л и - ч а ю щ е е с я тем, что блок Управления содержит первый, второй и третий триггеры, генератор, первый и второй элементы И, первый, второй 45 и третий дешифраторы, первый и вто-, ,рой шифраторы, первый, второй и третий счетчики, прйчем выход первого триггера подключен к первому входу 8910Фпервого элемента И, второй вход Которого соединен с выходом генератора и с первым входом второго элемента И, второй вход которого подключен к выходу второго триггера, первый и второй входы которого соединены соответственно с первым и вторым входами первого триггера и с первыми выходами первого и второго дешифраторов, выход второго элемента И подключен ко входу первого счетчика, выход которого соединен со входом первого дешифратора, первый выход которого подключен к первому входу третьего триггера и является первым выходом блока управления, второй и третий выходы первого дешифратора являются соответственно четвертыми пятым выходами блока управления, второй вход третьего триггера объединен со входами первого шифратора и является входом блока управления, выход третьего триггера соединен со входом генератора, выход первого шифратора соединен с первым входом второго счетчика, выход которого подключен ко входу второго дешифратора, соответствующие выходы, которого объединены и являются вторым выходом блока управления и соединены со входами второго шифратора, выход которого подключен к первому входу третьего счетчика, второй вход которого соединен с выходом первого элемента И и является третьим выходом блока управления, выход третьего счетчика соединен со входомтретьего дешифратора, первый выход которого подключен ко второму входу второго счетчика, а соответствующие выходы подключены ко второму выходу блока управления, второй вход первого триггера является вторым входом блока управления.Источники инФормации, принятые вовнимание при экспертизе1, Авторское свидетельство СССРР 337785, МКИ 6 06 Р 15/36 1970.2. Авторское свидетельство СССРР 445046, МКИ С 06 Г 15/20,30,09 . 1974.ин оррект Власенко Тираж 780 ЦНИИПИ Государственног по делам изобретений13035, Москва, Ж, Рауш каз 4561/38, Ужгород, ул. Проектная,иал ППППат Подписноео комитета СССРи открытийская иаб., д. 4

СмотретьЗаявка

2486361, 22.04.1977

КАЗАНСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ГОСУДАРТСВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. УЛЬЯНОВА-ЛЕНИНА

ТРАВИН НИКОЛАЙ АЛЕКСАНДРОВИЧ, КОБЧИКОВ АЛЕКСАНДР ВСЕВОЛОДОВИЧ, НЕЖМЕТДИНОВ ТАНСЫН КАВМЕВИЧ

МПК / Метки

МПК: G06F 15/173, G06F 17/00

Метки: оптимизации, систем, сложных, структуры

Опубликовано: 05.08.1979

Код ссылки

<a href="https://patents.su/6-678489-ustrojjstvo-dlya-optimizacii-struktury-slozhnykh-sistem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для оптимизации структуры сложных систем</a>

Предыдущий патент: Цифровой функциональный преобразователь

Следующий патент: Устройство для вычисления тригонометрических функций

Случайный патент: 163915