Модуль однородной вычислительной структуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

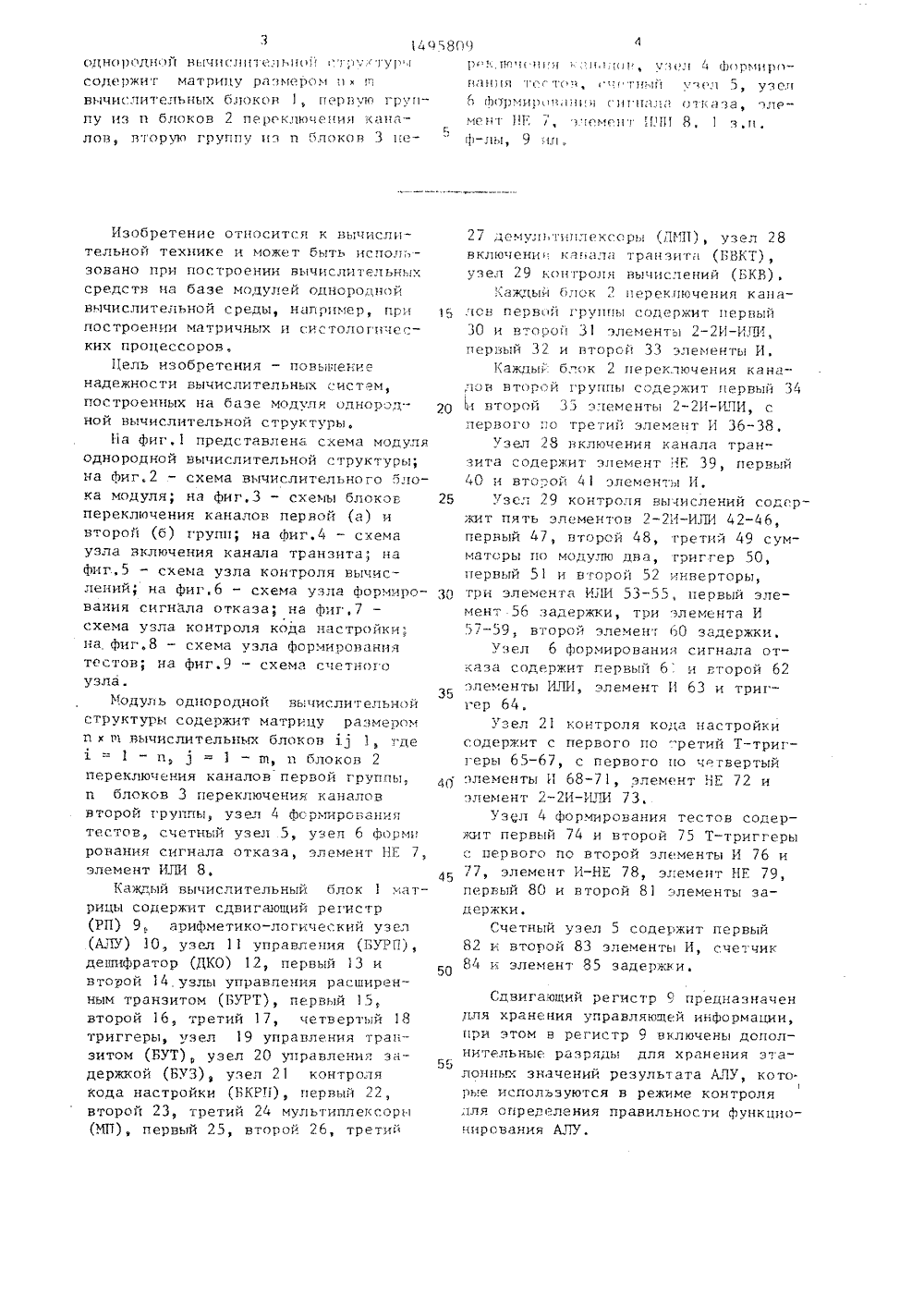

СОЮЗ СОЕЕТСНИХсоциАлистичеснихРЕСПУБЛИН 19) (111 51)4 0 06 Р 15/ ГОСУДДРСПО ИЭОПРИ /ННТ тве комитет ОТКРЫТИ ИЯМ ОПИСАНИЕ ИЗ Н АВТОРСКОМУ СВИДЕТЕ ОБРЕ ЬСТВУ НИЯ 2ДНОЙ ВЫЧИСЛИТЕЛЬ(21) 4289380/24-24(56) Авторское свидетельство СССР 19 691846, кл, С 06 Р 7/00, 1978.Бачериков Г.И. и др, Иультиконвейерные вычислительные структуры .на однородных средах. - Львов, ФМИ АН УССР, 1985, препринт 1 102,(54) 1107 УПЬ ОДННОЙ СТРУКТУР 1(57) Изобретентельной технике тся к вычисли т быть исполь высоколроизьных систем,ппение надежно оенияслител зовано для пост водительных выч 1 ель изобретени сти вычислитель ных на базе мод по ж си лей олени уктурь тем, ислительнои с то модуль стигаетс елпервому, второму и к третьемувыходам узла переключения каналов первой группы, при этом узел переключения кацапов второй группы содержит два элемента 2-2 И-ИЛИ и три элемента И, причем в каждом блоке переключения гсаналов второй группы первый информационный вход блока переключения каналов второй группы подключен к первгпм входам первого и второго элементов 11, второй, третий и четвертый ицформаггионные входы блока переключения каналов второй группы подклкчены соответственно к первому входу первого элемента 2-2 И-ИЛИ, к первому входу второго элемента 2-2 И-ИЛИ ивторому входу первого элемента 2-2 И-ИЛИ, гтервый управляюпгий вход блока переключеггия каналов второй группы подключен к второму входу зторога элемента 2-2 И-ИЛИ и к второму входу первого элемента И, выход аторого подключен к первому входу третьего элемента И, второй управ - ггггипгтгй вход блока переключения каналов второй группы подключен к третье му входу второго элемента 2-2 И в И и к втсрому входу второго элемента И, третий н четвертый управляюгпие вхадьг блока переключс.ция каналов второй гругцтьг подключены соответственно к третьему и к четвертому входам первого элемента 2-2 И-ИЛИ выход которого подключен к четвертому входу второго элемента 2-2 И-ИЛИ выход которога цодкггючен к второму входу третьего элемента И и к первому выходу блока переключения каналов второй группы, выходы второго и третьего элементов И подключены саатО 5 3 О ветственна к второму и к гретьему вь.ходам блока переключения кацапов второй группы, гри этом узел включе 5 О ция кацапа транзита содержит два элемента И и элемент НЕ, причем первый, второй управляюптие входы и вход режима узла включения канала транзита подключен соответственна к первому15 входу первого элемента И, к первому входу второго элемента И и к входу элемента НЕ, выход которого подключен к вторым входам первого и второго ход узла переключения кацапов первой группы подключен к четвертым входам первого и второго эпемецтов 2-И-ИП выходы второго элемента15 2-2 И-ИЛИ, первого и второго элементов И подключены соответственно к элемецтогн И, гп.хоггы ка-орых подключены соответственно к первому и второму вгпхсдам узла включения транзита, причем узел контроля вычислений содержит пять элементов 2-2 ИЛИ триггер, два элемента задержки, три сумматора па модулю два, два элемента НЕ, три элемента ИЛ и три элемента И, причем первый информационный вход узла контроля вычислений подключен к первым входам первого, второготретьего элементов 2"2 И-ИЛИ, выходы которых г;одкпючегтц соответственно к.первому, второму и третьему выходам узла контроля вычислений, второй игтфармациоггный вход которог о подключетг к первым входам четвертагс лемента 2 - 2 ИЛИ пятого элемента 2-2 И-ИЛИ и первого элемента ИЛИ, выход которого подключен к первому входу первого элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого ггодктпочегг к информационному входу триг гера, инверсный выход которога подключен к входу первого элемента задержки, выход которого подключен к первому входу второго элемента И, третий информационный вход узла контроля вычислений подключен к вторым входам первого элемента ИЛИ, четвертого и пятого элементов 2-2 ИИЛИ, четвертый информационный вход узла контроля вычислений подключен к второму входу второго элемента ИГП 1, пятый информационный вход узла контроля вычислений подключен кпервому входу первого сумматора па модулю два и к второму входу первого элемента 2-2 И-ИЛИ, пгестой информационный вход узла контроля вычислений подключен к первому входу второго сумматора по модулю два и к второму входу второго элемента 2-2 И-ИЛИ, седьмой информационный вход узла контроля вычислений подключен к первому входу третьего сумматора по модулю два и к второму входу третьего элемента 2-2 И-ИИ, второй уггравляюпгий вход узла контроля вь 1 числений подключен к входу первого элемента НЕ, к первому вхсду третьего элемента И, к входу установки в "О" триггера и к третьим входам первого, второго и третьего элег ентов 2 в 2 ИЙЛИ, третий, четвертый и первый вход режима, тактовый вход, входы нулевого и единичного потенциалов узлаК 0111 1) С)51 111 и 1 1 С 1 Е Н 11 1 т Э 5К т т тЕ 1 Ь С О О Т - ВЕТСГ 1 т 1 Э К Р. ТЕМУ, ЧЕ ГЭСРТттыт, входам четвертого элемент 2-211-1.111, к второму, третьему и четвертому входам пятого элемента 2-211-111 И, вы 5 хад катарго Одключен к второму входу второго сумматора по модулю два и к входу второго элемента НЕ, Выход котарага подключен к Второму входу третьего сумматора, выход которого подключен к первому входу третьего элемента ИЛИ, выход.которога подключен к второму входу первого элемента И, выход третьего элемента И подключен к третьему входу Второго элемента ИЛИ, выход четвертого элемента 2-2 И-ИЛИ подключен к второму входу первого сумматора по модулю два, вьход которого подключен к второму входу третьего элемента ИЛИ, третий вход которого подключен к выходу второго сумматора па модулю два, прямой выход триггера объединен с помощью монтажного ИЛИ с выходом 25 первого элемента НЕ и подключен к входу второго элемента задержки, к второму Входу второго элемента И, к четвертым входам первого, второго и третьего элементов 2-2 И-ИЛИ и к пята му выходу узла контроля вычислений, четвертый и шестой выходы .которого подключены соответственно к выходам второго элемента задержки и второго элемента И, причем узел формирования сигнала отказа содержит два элемента ИЛИ, элемент И и триггер, при этом первый вход узла формирования сигнала отказа подключен к первому входунта И и к ду установки В 0" ф 0 триггера, прямой выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к выходу узла формирования сигнала таза, вь 1 ходь с второго по г и-й которого подключены соответственно к входам с первого по (1 и)-й Второго элемента ИЛИ, выход которого подключен к второму входу элемента И, выход которого подключен к информационному входу триггера, (и и+1)-й50 вход узла формирования сигнала отказа подключен кп-му входу второго элемента ИЛИ и к второму входу первого элемента ИЛИ, при этом узел55 контроля кода настройки содержит три триггера, элемент 2-2 И-ИЛИ, четыре элемента И и элемент НЕ, причем первый и второй информационные входы Узл ка 11 г 1 эаля 1 ОД 1 1 тГтэс)ки гОДк 1 тэч ны саа гветствегно к 1 ернъл входам первого эл мента 11 11 элемента 2-2 ИИЛ 11, выход которого надключе 1 к 1 ерЭЭМ 1 т ЭЛХОДтт УЗа КО 11 Т 1 ЭОЛ 51 Кода пав стройки, первый управляющий вход которого подключен к входам устанавтт этки э 0 первого , второго и т р е т ь е га триггеров, второй управляюп 11 вход узта кант 1 эаля нога настройки подключен к второму входу элемента 2-2 И-ИЛИ и к первому входу второго элемента. И, выход котарага подключен к информационному Входу первого триггера, инверсный выход которого подключен к информационному входу второго триггера и к первому входу третьего элемента И, инверсный выход которогопадклкэчен к первому входу четвертого элемента И и к первому входу второго элемента И, выход первого элемента И подключен к информационному входу третьего триггера, прямой Выход которого подключен к второму выходу узла контроля кода настройки и к второму входу четвертого элемента И, выход которого подключен к входу элемента НЕ, к четвертому выходу узла контроля кода настройки и к третьему входу элемента 2-2 И-ИЛИ, выход элемента НЕ подключен к третье му выходу узла контроля кода настройки, к четвертому входу элемента 2-2 И-ИЛИ и к третьему входу второго элемента И, прямой выход второго триггера и инверсный выход третьего триггера подключены соответственно к вторым входам третьего и первого элементов И, причем узел формирования тестов содержит два триггера, три элемента И, два элемента задержки и элемент НЕ, причем управляющий вход узла формирования тестов подключен к первым входам первого и второго элементов И, вход запуска узла формирования тестов подключен к первому входу третьего элемента И И К ВХОдаМ уСтаНОВКИ В 0 т ПЕРВОГО и второго триггеров, тактовый вход узла формирования тестов подключен к второму входу третьего элемента И, выход которого подключен к информационному входу первого триггера, прямой вход которого подключен к первому выходу узла формирования тестов и к второму входу второго элемента И, инверсный выход которого подключен к третьему входу третьего эле 19 5809мента И и к входу элемента Ш:, в - ход котороо подключен к входу первого элемента задержки, инверсный выход первого триггера подключен к5 второму входу первого элемента И и к информационному входу второго триггера, прямой выход которого подключен к третьему входу второго элемента И и к третьему входу первого элемента И, выход которого подключен к входу второго элемента .апержки, вь - ходгервого и второго элементов а ерж - 3 и подключены соответстгеццо к второму и/ третьему выходам узла формирования тестов, при этом счетный узел содержитс цк, лва элемента И и:емецт ;ад ржкц, ричс первыйуравляю взОрОЙ упранляюпИЙ исчецый цхс;и сетцос узла подключены соо"втствеццс к первому, второму и третьему входам первого элемента И, выход которого подключен к вхогу элемента задержки, вьход которого цодкпючец к счетному входу счетчика, первый и второй выходы котсрого подключены соответственнок первому и второму входам второгоэлемента И выход которого подключенк входу установки в О счетчика ик выходу счетного узла,Составитель В,не А, 11 андо ехре иск Заказ 42 б 8/47 Тираж 66811 НИИПИ Государственного комитета по из113 П 35, Москва, Ж,одписно бретениям КНТ ССС ткрытиям д. 4/5/ 9 Од нсод ив ычст 1 ь(1( т, ,:у 11 1 содержит матрицу ра.меромтвычислительных б.оков 1, цервук группу из и блоков 2 переключения каналов ВОрую Групп из п блокОВ 3 е 5809р . ю, о,4 с 1 к 11 ро- ГсиясГ то,"и ць , зе 1 5, узел 6 1 ар.ро, ггнала о 1 кза, эемет НГ 7, э.ееИ 8. 1 з,ц, ф-ль, 9 .иИзобретение относится к вычислительной технике и может быть испол;. -зовано при построении вычислительныхсредств на базе модулей однороднойвычислительной среды, нагример, припостроении матричных и систологвеских процессоров.Цель изобретения - повышениенадежности вычислительных систем,построенных на базе модуля однородной вычислительной структуры,На Фиг,1 представлена схема модуляоднородной вычислительной структуры;на Фиг,2 - схема вычислительного блока модуля; на фиг,З - схемь блоковпереключения каналов первой (а) ивторой (б) групп; на фиг,4 - схемаузла включения канала транзита; нзФиг,5 - схема узла контроля вычислений; на фиг,6 - схема узла формирования сигнала отказа; на Фиг.7схема узла контроля кода настройки;,на фиг,8 - схема узла формированиятестов; на Фиг.9 - схема счетногоузла.Модуль однородной вычислительнойструктуры содержит матрицу размероми к щ вычислительных блоков Ц 1, где1 = 1 - п, 1 =- гп, и блоков 2переключения каналов первой группы,п блоков 3 переключения каналоввторои группы, узел 4 Фор 1 ированиятестов, счетный узел 5, узел 6 формпрования сигнала отказа, элемент НЕ 7,.элемент ИЛИ 8,Каждый вычислительный блок 1 матрицы содержит сдвигающий регистр(АЛУ) 1 О, узел 11 управления (БУРН),дешифратор (ДКО) 12, первый 13 ивторой 14 узлы управления расширенным транзитом (БУРТ), пе.рвый 15,второй 16, третий 17, четвертый 18триггеры, узел 19 управления тразитом (БУТ), узел 20 управления задержкой (БУЗ), узел 21 контролякода настройки (БКР 1), первый 22,второп 23, третий 24 мультиплексоры(МП), первый 25, второй 26, третий 27 демул тицлексоры (ПМП) узел 28включения каила транзита (БВКТ),узел 29 контроля вычислений (БКВ),Каждый блок 2 церекнючения каца 5 :ов первой группы содержит первый30 и второй 31 элементы 2-2 И-ИЛИ,первый 32 и второй 33 элементы И,Каждый б;,ок 2 перек,зючения канадов второй группы содеэжит первый 34Й второй 35 э.ементы 2-2 И-ИЛИ, спервого по третий элемент И 36-38.Узел 28 включения канала транзита содержит элемент НЕ 39, первый,0 и второй 41 элементы И,25 Узел 29 контроля вы ислений содержит пять элементов 2 - 2 И-ИЛИ 42-46,первый 47, второй 48, третий 49 сумматоры по модулю два, григгер 50,первый 51 и второй 52 инверторы,80 гри элемента ИЛИ 53-55, первый элемент 56 задержки, три элемента И57-59, .второй элемент 60 задержки.Узел 6 Формирования сигнала отказа содержит гервый 6: и второй 62элементы ИЛИ, элемент И 63 и триггер 64,Узел 21 контроля кода настройкисодержит с первого по "ретий Т-триг.еры 65-67, с первого по четвертыйэлементы И 68-71, элемент НЕ 72 иэлемент 2-2 И-ИД 73.Узел 4 формирования тестов содержит первый 74 и второй 75 Т-триггерыс первого по второй элементы И 76 и77, элемент И-НЕ 78, элемент НЕ 79,первый 80 и второй 81 элементы задержки,Счетный узел 5 содержит первый82 и второй 83 элементы И, сче.чик84 и элемент 85 задержки,Сдвигающий регистр 9 предназначендля хранения управляющей информации, цри этом в регистр 9 включены дополнительные разрядь для хранения эталонных значений результата АЛУ, кото.1рье используются в режиме контролядля определения правильности функционирования АЛУ, 1495809Учел 21 контроля кода настройки предназначен для контроля регистра 9 в режиме программирования, В случае возникновения неисправности типа сопэг. О или сопэг. 1 в одном из разрядов регистра 9 узел 21 контроля блокирует регистр 8 и восстанавли - вает возможность занесения программы в последующие вычислительные блоки, формируя при этом сигнал отказа, который воспринимается узлом 29 контроля вычислений. Узел 28 включения канала транзита при поступлении сигнала контроля производит принудительное включение канала транзита по контуру мультиплексора 24, узел 19 управления транзитом Р-триггер 17 - узел 14 управления расширенным транзитом.- Р-триггер 18 -ф узел 29 контроля вычислений путем подачи соответствующих управляющих воздействий на узел 19 управления транзитом и узел 14 управления расширенным транзитом, необходимость которого обуславливается наличием операций "Генерация константы" и "Расширенный транзит", при которых характер передачи данных по транзитному каналу значительно затрудняет воэможность контроля канала. Поэтому в режиме "Контроль происходит принудительное включение канала транзита по указанному контуру, Узел 29 контроля вычислений производит контроль операционно-транзитного канала вычислительного блока в режиме "Контроль" путем сравнения реакции операционно-транзитного канала на. тестовое воздействие и эталонных значений, которые хранятся в регистре 9.Для обеспечения режима контроля вычислительных блоков, объединенных в модуль, предусмотрен узел 4 формирования тестов, который генерирует тест как для проверки регистра 9, так и для проверки операционно-транзитного канала. Тестовое воздействие подается на все вычислительные блоки одновременно, Схема подключения внешних входов модуля с использованием блоков переключения каналов 1 и 2 обеспечивает подключение внешнего контакта модуля входа в зависимости от режима работы либо к входу настройки, либо к информационному вхо-, ду вычислительных блоков, кроме того, при отказе (обрыв, коро гкое замыкание) внешней связи в граничных столбцах матрицы или при отказе регистра9 в одной из вычислительных блоковлевого граничного столбца по сигналус соответствующего узла 21 контроля .5подключается информационный (резервный) выход предыдущего модуля иинформационный (резервный) вход данного модуля, Узел 6 формированиясигнала отказа соединен с контрольными выходами всех вычислительныхблоков модуля и формирует сигнал отказа модуля, причем каждый последующий отказ вызывает срабатывание указанного узла и выдачу сигнала отказа.Счетный узел 5 необходим для обеспечения работы узла 21 контроля коданастройки и обеспечивает последовательное срабатывание указанных узлов 20 во всех вычислительных блоках модуляоднородной вычислительной структуры.Вычислительный блок работаетследующим образом. 25 Для настройки на выполнение конкретной операции вычислительный блокпереводится в режим программированияс помощью сигнала на управление вводом программы, равного единице. Перед ЗО занесением программы происходит одновременное тестирование всех вычислительных блоков, имеющихся в модуле.Тест регистра 9 представляет собойчередующуюся последовательность ну - 35,леи и единиц, которая подается навнешние контакты выходов ВЗ . модуля1Таким образом, каждый последующиймодуль является псевдогенераторомтестов для каждого последующего. Поэтому происходит проверка не толькорегистра 9 каждого вычислительногоблока модуля, но и контактов А 1;и ВЗ При использовании одного модуля тестовая последовательность по дается извне, Блоки переключенияканалов первоЙ и второй групп присигналах управления вводом программыи контроля, равных единице, обеспечивают подключение контакта А 1 . к1 5 О входу ввоца программы ВП вычислительного блока 1., а выхода тестовойпоследовательности ТП узла 4 - к внешнему контакту ВЗ;. Если отсутствуютобрывы (короткие замыкания) во внешних контактах модуля А 1; и ВЗ ., атакже отказы в виде сопяТ 1 и сапамиф в регистре 9, то через 1 тактов(где 1 - число разрядов в регистре9) тестовая последовательность по 1 ог 80 с5О 5 20 25 30 35 40 45 50 55 явпяется на выходе регистра 9 и регистрируется узлом 21 контроляСчетный узел последовательно прашивает (контрольный сигнал КС:) узлы 21 контроля всех вычислительных блоков. Если узел 21 контроля зарегистрировал тестовую последовательность на выходе регистра 9, последний считается исправным и контур обхода регистра 9 с помощью цепей узла 21 контроля не подключается. Если при контрольном сигнале КС:1 узел 21 контроля не зарегистрировал тестовую последовательность, он блокирует выход регистра 9 и подключает контур обхода, Это дает возможность заносить код настройки в регистр 9 последующих блоков при отказе ре - гистра 9 всех блоков модуля однородной вычислительной структуры, сигнал контроля СК с внешнего контакта модуля снимается и производится запись кодов настройки в вычислительные блоки, При снятии сигнала конт - роля узел 2 переключения канала подключает вывод программы к внешне му контакту ВЗ Если произошел отказ внешнего контакта ВЗ, или внешнего контакта А 1 этот отказ интерпретируется узлом 21 контроля;зычислительного левого граничного столбца как отказ собственного регистра 9, Помимо включения контура блокировки регистра 9 с помощью блоков 1 и 2 переключения каналов происходит подключение выхода РВв преды - дущем модуле однородной вычислительной структуры и резервного внешнего контакта входа данного модуля, Тем самым сохраняется возможность занесения программы и вычислительные блоки, После записи программы снимается сигнал управления вводом программы, Снятие сигнала управления вводом программы приводит к переключению с помощью блоков 1 и 2 переключения каналов внешнего контактов А 1 , АЗ , В 1., ВЗ на информационные1 ф 1 фвходы (вьсходы) а 1, аЗ (в вЗ) соответс. твенноРабота модуля однородной вычислительной структуры в режиме вычислений ничем не отличается от работы прототипа,Для проверки правильности выполнения конкретной функции, на которую настроен данный вь 1 числительный блок, вводится режим "Контроль", которьй устанавливается подачей ыа внешний кс нтакт модуляигначд контроля СК=11 о сигналу кон сроля СК= у зе т 21 контроля отключае 1 вых 1 ды операцион -но-транзитного узла каждого блока отдемультиплексоров 22-2 л и подклю саетк входам указанных демультидлексороввыход узпа с формирования тестов,Узел 28 включения кана 1 а транзитанас:траивает канал транзита на передачу данных с вьо;ода мультиплексора24 на входы жала 21 ко строля, Узелч начинает формировать тестовую по -следовательнос гь в виде сигнала 101 и тактовые сигналы ТТ 1, ТТ 2, которыевоспринимаются узлом 2контроля,Сигналы ТТ 1, ТТ 2 появляются с задержкой соответственно третьего ичетвертого тактов после начала формирования тестовой последовательности,По сигналам ТС 1 и ТС 2 в узле 2 контроля происходит сравнение информациис выхода узла 20 управления задержкойи эталонной информации хранящейся вдоле ЭИ регистра 9, а также сравнение информации на выходах 0-триггеров17 и 18 с эталоном, формируемым узлом21 контроля, На основании результатовконтроля формируется сигнал контрольного входа в узле 21 контроля, атакже сигнал на второй выход СБ 2,Сигнал на контрольном выходе КВ:указывает наличие нарушений в функционировании операционно-транзитной части вьгчислительного блока, Данный сигнал поступает в узел формирования сигнала отказа, который на основании сигнала контрольного выхода КВ:1 от какого-либо вычислительного блока модуля формируетсигнал на внешнем контакте модуля диагностического вы",ода,Таким образом, за четыре такта происходит контроль всех вычислительных блоков моцулей однородной вычислительной структуры, При этом для операции "Сложение" И, И-НЕ, ЗП обеспечивается полный контроль всех узлов вычислительных блоков, участвующих в выполнении данной операпии, Для операции ИСКЛЮЧАЮЩЕЕ ИЛИ данный метод не позволяет выявлять отказы, приводяшие к сопвС Д на выходах одного из элементов 10, 13, 15, б, 20. При контроле операции "Расширенный транзит" неконтролируемым остается мультиплексор 23, при операции "Генерация константы" цанный методконтроля не поэноляет контролиро 7 атьузел 11 управления.Рассмотрим работу первого и второго блоков переключения каналов5Число данных блоков в модуле однородной вычислительной структуры равночислу строк п матрицы вычислительныхблоков, По сигналу управления вводапрограммы УВП=1 с помощью элементов2-2 И-ИЛИ 30 и И 32 происходит подключение соответствующего внешнего контакта А 1. к входу настройки вычисли 1тельного блока, а с помощью элемента2 - 2 И-ИЛИ 34 (при отсутствии сигналаконтГ ") и элемента 2-2 И в И 35 -подключение первого выхода вычислительного блока к соответствующемувнешнему контакту ВЗ;. С помощьюэлемента 2-2 И-ИЛИ 31 подготавливается цепь для передачи сигнала отказарегистра вычислительного блока (1,1)(ОРП) в блок 2 переключения каналовближайшего левого модуля, в котором,в свою очередь, с помощью элементовИ 37 и 38 подготавливается цепьвключения внешнего контакта модуляинформационного (резервного) выхода,При возникновении отказа регистра 9вычислительного блока (д, 1) или отказе внешнего контакта А 1 илиотказе внешнего контакта ВЗ. в бли 1жайшем левом модуле однородной вычислительной структуры сигнал отказаОРП подключает внешний контакт модуля резервного выхода ближайшего левого модуля с помощью элемента И 38и элемента ИЛИ 8 и внешнего контактаА 1 рассматриваемого модуля однород 1ной вычислительной структуры с помощью элемента 2-2 И-ИЛИ 30. При снятии сигнала управления вводом про-граммы УВПэлементы 2-2 И-ИЛИ 32,И 33 и 2-2 И-ИЛИ 35 подключают ксоответствующим внешним контактаммодуля информационный вход а 1 и информационный выход в 3,При снятии сигнала управления, вводом кодов настройки блоки 1 и 2переключения каналов не обеспечиваютвосстановление цепей передачи инфор"50мации между модулями, В этом случаес помощью перепрограммирования (режим перепрограммирования в случаеотказов внешнего контакта модуля55обеспечивается работой блока 2переключения каналов и блока 3 переключения каналов 3 ) можно обойтиотказавший вычислительный блок,Узел 4 Формирования тостов рабо 11тает только в режиме Контроль11 Гри сигнале контроля СК:1 открывается вентиль (элемент И 76) и на прямом выходе триггера 74, который является формирователем тестовой последовательности, с приходом тактовых импульсов Формируется последовательность нулей и единицПри наличии сигнала управления вводом программы (УВП=О) на выходе элемента И-НЕ 78 присутствует уровень логической и блокировка элемента И 76 возможна только снятием сигнала контроля СК, что и делается после завершения проверки регистром 9 всех вычислительных блоков, находящихся в данном модуле однородной вычислительной структуры.При контроле регистра 9 выходы ТТ 1 и ТТ 2 узла 4 не используются. Режиму контроля операционно-транзит - ного узла соответствуют сигналы контроля СК=1 и управления вводом программы УВП=О (УВП=1), В этом случае на выходе тестовой последовательности (ТП) появляется последовательность 101, после чего с помощью элемента И-НЕ 78 происходит блокировка элемента И 76 и генерация тестовойпоследовательности прекращается,На выходах тестового такта ТТ (ТТ 2)появляется единичный сигнал соответственно через третий и четвертыйтакты после. подачи сигналов контроляСК:1 и управления вводом программыУВП=О, Счетный узел 5 производитвыдачу сигнала (уровень логической"1") через каждые 1 тактов.Узел 21 контроля кода настройкиработает следующим образом,Работа данного узла начинаетсяс приходом сигнала контроля СК=1,по которому ббнуляются триггеры 6567, Это означает, что на выходе элемента И 71 и элемента НЕ 72 присутствует уровень логической "1 , триггер 65 открыт для приема информациис выхода регистра 9, Тестовая последовательность с выхода ТП узла 4формирования тестовой последовательности в случае отсутствия отказоввида сопят О и соиз 1 в регистре 9и отказов внешнего контакта ВЗ, иА 1, через 1 тактов появится на выходе регистра 9 вычислительного блока(1, 1). Последовательность 101устанавливаетв состояние "1" поя 49мы 11 хс,11 "риг 1 Ррб 5 и 66ч 1.п 1 иводят к появ 1 Рн 1 к 0 11;1 1 ыхлсэлемент;И 71, Таким Обэа:ом 01 Р О,что означает отсутствие откаов.Срабатывание тригера 67 е приводитк изменениям при программированииданного вычислительного блока. Вслучае возникновения отка.ов из перечисленной группы на выходе регистра9 постоянно присутствует или сигналсоиз О, ии соиз 1. Это приводитк тому, что триггеры 65 и 66 формируют сигнал 1 ка выходе элементаИ 71, Через 1 + 1 с тактов установитсяв "1 триггер 67 вычислительногоблока (1 1).Зто приводит к выда е сигналаОРП=1 что подключит вход наст 1 ойкивычислительного блока через цепиузла 21 контроля к первому выходувычислительного блока (., 1), чтообеспечит воэможность занесенияпрограммы в следующие вычислительныеблоки.Узел 29 контроля вычислений работает следующим образом, Сигналом"Контрольп (СК=1) с помощью элементов2-2 И-ИЛИ 44-46 от входов цемультиплексоров 25-27 отключаются выходь:узла 20 управления задерхдсой узла19 утравления транзитом узла 14управления расширенным транзитомсоответственно и подключается входТП, Таким Образом, тестсвое ваэдей,ствие на вьчислительный блок (., 1)поступает из соседних вьчи лителькыхблоков, Это позволяет проверить демультиплексоры и мультиплексоры,а также связи между вычислительнымиблоками, Реакция на тестовое воздействие сравнивается с эталонной ин -формацией хранящейся в регистре 9.Сравнение с первым эталоном (ЭИ 1)стробируется тактовым сигналом тестового такта ТТ 1, Сравнение с эталоном ЭИ 2 стробируется сигналом тестового такта ТТ 2, Сравнение эталоас реакцией происходят с помощьюсумматора по модулю два 47, Для проверки капала транзита в качествегенератора тестов используется элемент 2-2 И-ИЛИ 43,С помощью сумматора по модулюдва 48 проверяется какал транзитас задержкой на один такт., а с помощью сумматора по модулю цва 49транзит с задержкой на два такта,В случае несовпадения этагона 5809 1 7.Ч 1 К 111 1 1 Р Р 1)111 С 111 И 1 Р 111111 Т -110 М Е 11 ка;1 с 1 а 1 Г.О 1 Р1 ГРта 1И 5 1появ;1 ЯРР 51 Риг 1 а.котРый 11 о1 епи И .Я, ИП 55 ус 1 анавливаетв единицу триггер 50, Олемект 56задержки обеспеч 51 вает крат.современный единичный импульс ка выходе элемента И 59, который является контрольным вьходом панноо вычислительного блока, по елям 1. 57, И 3 П 1 55обеспечивается срабатьвание указаннс го триггера лри отказах, зафиксированных у лом 21 контроля, Наличиевхода СБ 2 и выхода СБ, 2 позволяетпри снятии сигнала контроля (СК=О)определи"ь путем последовательногосдв 5 га содержимого регистров 50,какой именно вычислительный блок матрицы отказал Гсли отказал вычислителькый блок (1, 1), после снятияиг".чала СК сигнал отказа на внепкемконтакте модуля диагно:тического выхода появится на ит в (г-+и(и такте.Ф о р м у л а и з о б р е т е н и я1, ".1 одуль однородной вычислительной структуры, содержащий матрицувычислительных блоков размером иУ,.де и и 1 - количество строк и столбцов в матрице, первый информационныйвыход вычислительного блока -й стро -ки 1-го столбца матрицы подключен д" к входу настройки вычислительногоблока З.-й строки Ц + )-го столбцаматрицы (где 1 = 1.и, 1 = 1,п - 1), вход признака настройкимодуля подключен к первым управляющим входам вычислительных блоковмаТрицы, тактовый вход модуля подключен 1 к тактовым входам вычислительныхблоков матрицы, второй информационный выход вычислительного блока 1-йстроки 1-го столбца матрицы подключен к информационному входу вычислительного блока .-й строки Ц + 1)-гостолбца матрицы, третий информационный выход вычислителького блока 1-йстроки 1 с-го столбца (где 1 с = 2, , щ)матриць годключек к втсрому информац 5 окному входу вычислительного блока1-й строки (1 с)-го столбца матрицы,третий икформационный вход вычислительного блока 1-й строки г-гостолбца матрицы (где 1 = 1.и;г = 1.) подключен к четвертомуинформационному выходу вычислител.нов119 1 о блк д (1 + 1 1 тркц г о с 1 б 1 д мдтрц 11 ы четвертьР инфрмд 1 цоннь 1 Р Выходь В 1 ИсхПтеье 11 х блоков ГьерВой строки с первого по 1 т-й столбов матрицы подключены соответственно к выходам с первого цо ш-й первой группы модуля, четверть 1 й информационный вход Вычислительного блока р-й строки г-го столбца матрицы (где р=2п) подключен к пятому информационному выходу вычислительного блока (р)-й строки г-го столбца матрицы, четвертье информационные входы вычислительных блоков первой строки с первого по ш-й столбцов матрицы подключены соответственно к информационным входам с первого по ш-й первой группы модуля, третьи информационные входы вычислительных блоков п-й строки с первого по ш-й столбцов матрицы подключены соответственно к информационным входам с первого по ш-й второй группы модуля, пятые информационные выходы вычислительных блоков и-й строки с первого по ш-й столбцов матрицы подключены соответственно к выходам с первого по ш-й второй группы модуля, о т л и ч а ю щ и й с я тем, что, с целью повышения надежности, контролепригоцности и сокращения Времени программирования модуля в него введены с первого по и-й блоки переключения каналов первой группы, с первого по п-й блоки переключения каналов второй группы, узел формирования тестов, счетный узел, узел формирования сигналов отказа, элемент ИЛИ и элемент НЕ, причем информационные входы с первого по и-й третьей группы модуля подключены соответственно к первым информационным входам блоков переключения каналов с перього по п-й первой группы, информационные входы с первого по п-й четвертой группы модуля подключены соответственно к первым информационным входам блоков переключения каналов с первого по и-й второй группы, первые выходы блоков переключения каналов с первого по и-й первой группы подключены соответственно к выходам с первого по п-й третьей груПпы модуля, первые выходы блоков переключения каналов с первого по п-й второй группы подключены соответственно к выходам с перного по и-й четвертой группы, информационный вход которого подключен; 1 ( о 1к вторым ицф эмд 1 Пнн 1,м входам блоков переключения каналов 1 рвй группы, вхоп рцэндкд ндстройкц модуляподключен к первым управляющим Входдм Всех блоков переключения каналовперВой ц второй групп, к первомууправляющему входу счетного узла ик входу элемента 11 Г, вьход которогоподключен к вторым управляющим входам блоков переключения каналов первой и второй групп и к управляющемувходу узла формирования тестов шестой ;: седьмон цнформд 1 ионные выходывычислительного блока а-й строк 1Ь-го столбца матрицы (где а = 1,п, Ь = 1,, ш) подключенысоответственно к пятому и 11 естомуинформационным входам вычислительногоблока (Ъ + 1)-го столбца а-й строкиматрицы, шестой и седьмой информационные Выходы вычислительного блокаш-го столбца сстроки матрицы(где с = 1, , п) подключены 25 соответственно к пятому и шестомуинформационным Вхсдам вычислительногоблока первого столбца (с+)-й строкиматрицы, второй и третий выходы а-гоблока переключения каналов первойгруппы подключены соответственно квходу настройки и к первому информационному входу ВыП 1 слительного блокапервого столбца д-й строки матрицы,третий, Восьмой ц девятый информационные выходы вычислительного блока 35первого столбца д-й строки матрицыподключены соответс.твенно к третьемуинформационному, третьему управляющему и четвертому управляющему Входам 4 О а-го блока переключения каналов первой группы, первый и второй информационные Выходы и второй информационный вход вычислительного блока ш-гостолбца а - й строки матрицы подключены соответственно к второму информационному, третьему информационномувходам и к второму выходу а-го блокапереключения каналов второй группы,тактоцый вход модуля подключен ксчетнсму входу счетного узла и к тактовому входу узла формирования тестов, первый выход тестовой последовательности которого подключен к четвертым информационным входам блоков переключения каналов второйгруппы и первым входам тестовой последовательности вычислительных блоков матрицы, вход признака контроля модуля подключен к входу запуска3 г 9 58с) 510 ду режим Второго узла управлениярлспиренцым транзитом, выход третьего мультиплексора подключен к первомувходу режима узла управления транзитом, выход которого подключен кинформационному входу третьего триггера вь;ход которого подключен квторому ходу режима в-орога узла 2 25 УЗЛЯ фсРМИРОГ 11 И 1 ТЕСТВ К ГТСЗ)РУУП Ря ВЛЯЮПЕМУ ВХОДУ с.: ЧЕ ГНЗ с У 5,1,к перому входу узла форчиролняСИГЦЛЯ ОтКаЗа, К ТРЕТЬИМ УГРЛВЛЯсПИМвходам блоков переключеня каналовВторой группы и к вторым управляющимвходам вычислительных блоков матрицывыход с.четного узла подключен к тре-,тьим управляющим входам гь:чисгитетьньгх блоков матрицы, выходы признак 1прохождения теста которьх цодк."ючецьсоответственно к входам с второгопо ( и + 1)-й узла формированияСИГНаЛа ОтКаЗа, ВЫХОД КОТО:ОГО ПОДключен к выходу резульття контролямодуля, второй и третий Выходы тест вой последовательности :злл формирования тесто подключены ссстветственно к вторым и к третьим входамтестовой последовательности вычислительных блоков матрицы, третьи выходы блоков переключения каналов подключены к входам злементя ИЛИ выходкоторого подключен к вь 1 ходу модуля,выход признака режима контроля вычислительного блока п-го столбца а-й строки матрицы подключен к четвертомууправляющему входу а-го блока переключения каналов второй группы, входы нулевого и единичного потенциаловмодуля подключены к входам нулевого и единичного пОтенциалОВ вь числительных блоков матрицы,2, 1"1 одуль по п,1, о т л и ч я нщ и й с я тем, что каждый вычислительный блок матрицы содержит сдвигающий регистр узел управления, деифратор первый, второй и третиймультиплексоры, первый, второй и тре -тий демультиплексоры, арпфметикс-логический узел, узел управления транзитом,г,ервый и второй узлы управления расширенным транзитом, узел управлениязадержкой, с первого по четвертыйтриггеры узел контроля кода настройки, узел контроля вычислений и узелвключения канала транзтя причем вкаждол вычислительном блоке матрицыпервый информационный вход вычислительного блока подключен к первыминформационным входам мультиплексоров с первого по третий и к первомувходу режима узла управления, второй,третий и четвертый информационныевходы вычислительного блока подключены соответственно к вторьи, третьими четвертым иГфсзрмационым входаммультиплексоров с первого по третий,33 35 40 45 50 55 Выход гер 01 с 1 му.ьтппяк с.Оря 1 ОСКГгсгчец к и рцо ухо)у режима первогоупя упрявлс ция рясширсццым тряцзи 1 ом и с пс рво;у ицгорм,ционному входу рифме тик о - ло гич е с ко го узла,ВЬГХС.Д КООРО 1 О ГОДКЛЮЧСН К 1 ТОРОМУвходу режима первого у.лл управления1 лсгиреццьм транзе 1 том ВыхОд которо -го подк.гючец к информационному входупервого триггера, вьгход которогоодскчец к информационному входуВторого -.риггеря и к и:рвому входурежьля у.пл управения задержкой,Гторой вход которого подключен квыходу в орого триггер 1, выход второго мультплексора подключен к второмч информационному Входу арифметико-логического узла и к первому вхоуправления расширенным транзитом,выхсд которого подключен к информационному входу четвертого триггера, первый управлявший вход вычислительного блока подключен к входу сдвига сдвигавшего регистра и к первому управляющему входу узл контроля Вычислений, первый выход сдвигающего регистра подключен к второму входу режима узла управления и к третьему входу режима узла упраления задержКОй, ВтОРОй, тРЕткй, ЧЗТВЕГТЫй И ПЯ- тый выходы сдвигающего регистра подключецы соответственно к входу дсшнфратора, к управляющему входу первого мультиплексора, к управляющему входу второго мультиплексора и к управляющему входу третьего мульТИПЛЕКСОРа, ШЕСтОй ВЬХД СДВИГаЮЩЕГО регистра подключен к т 1 етьему входу режима узла управления и к управляю-. щему входу первого демультиплексора, с;ЕдЬМОй И ВОСЬМОЙ ВЫХОДЫ СдИГаЮщЕГО регистра подклкчены соответственно к управляющим входам второго и третьего демультиплексоро, первый, второй и третий выходы дешифратора подключены соответственно к входу кода операции арифметико-логического узла, к третьему входу режима первоо узла правления расширенньм транзитом и к четвертому входу ре-.жима у а у 1; ВНя, 11 ,)1) КОТРО Г) 110 ПК 15)Н К РТ)РОМУ ВХОДУ 1) 81ВТОРО 1,; 1 Р; В) 5"Ъ ",ХО ЦУ УЗЛа кон тРал Я к О.ца 1 а т 1 Йк 111 Р т Вс 1 т:111режима узла уравнения трапНтом,второй вьхол узла управления подклю 5чен к Входу считывания-записи сдвигношего регистра, первые выходы де - мультиплексоров с первого по третий объединены с помощью монтажного ИЛИ и подключены к второму информационному выходу вычислительного блока, вторые выходы демультиплексорав с рервого по третий объединены с помощью монтажного ИЛИ и подключены к третьему инФормационному выходу вы числительного блока, третьи выходы демультиплексоров с первого по тре - тий объединены с помощью монтажного ИЛИ и подключены к четвертому информационному вьходу вычислительного 2 О блока, четвертые выходы демультиплексоров с первого по третий объединены с помощью монтажного ИЛИ и подключены к пятому информационному выходу вычислительного блока, тактовый вход 25 которого подключен к синхровходам сдвигающего регистра и арифметикологического узла и узла контролявычислений, первьй, второй и третийвходы тестовой последовательности ЗОвычислительного блока подключенысоответственно к первому, второму и третьему информапианним входам узла контроля вычислений, первый, второй и третий выходы которого подключены соответственно к информационным входам первого, второго и третьего демультиплексоров, второй управляющийвход вычислительного блока подключенк входу режима узла включения канала 4 Отранзита, к второму управляющемуВХОду уЗЛа КОНтрОЛя ВьЧИСЛЕНИй И Кпервому управляющему входу узлаконтроля кода настройки, первый,второй и третий выходы которого подключены соответственно к первому,шестому и восьмому информационнымвыходам вычислительного блока, пятыйи шестой информационные входы которого подключены соответственно к первому информационному входу узлаконтроля кода настройки и к четвертому информационному входу узлаконтроля вычислений, вход настройкивычислительного блока подключен к55второму информационному входу узлаконтроля кода настройки и к информационному входу сдвигающего регистра,выход переноса которого подключен к ВЬХОД КОТОРОГО 1 ОПК НЮЧРН К и ЕВ 51 ТОМ информационному Вьходу Вычислительного блока и к входу режима узла конт - роля Вычислений, четвертий, пятый и шестой выходи которого подключены соответственно к седьмому инфармациоцному в 1 ходу, выходу признака режима контроля и к выходу признакапрохождения тесга вычислительного блока, третий и четвертый вьходы дешифратора 1 адключеьи соответственно к первому и второму управляющим входам узла включения канала транзита, первый и второй Виходы которого подключены соответственна к третьим входам режима узла управления транзитам и второго узла управления расширенным транзитом, девятый и десятьй входы слвигающего регистра, выход узла управления задержкой, выхадь третьего и четвертого триггеров подключени соответственно к третьемуи четвертому управлякщим входам, пятому, шестому и седьмому информационным входам узла контроля вычислений, входы нулевого и единичного потенциалов вычислительного блока подключенысоответственно к входам нулевого и единичнога потенциалов узла кантро - ля вичи .лений, при этом каждый блок переключения каналов первой группы содержит два элемента 2-2 И-ИЛИ и два элемента И, причем В каждом блоке переключения каналов первои группы первый, второй и третий информационные ьходы блока переключения каналов первой группы подключены соответствен - но к первому входу первого элемента 2-2 И-ИЛИ, к второму входу первого элемента 2-2 И-ИЛИ и к первому входу второго элемента 2-2 И-ИЛИ, первый управляющий вход блока переключения каналов первой группы подключен к первому входу первого элемента И, к второму входу второго элемента 2 в 2 И в , второй управляющий вход блока переключения каналов первой группы подключен к первому входу второго элемента И и к третьему входу второго элемента 2-2 И-ИЛИ, третий управляющий вход блока переключения каналов первой группы подключен к третьему входу первого элемента 2-2 И в И, выход которого подключен к вторым входам первого и второго элементов И, четвертый управляющий

СмотретьЗаявка

4289380, 30.06.1987

ПРЕДПРИЯТИЕ ПЯ А-7162, ЛЕНИНГРАДСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

ЛЕЩЕНКО ЕВГЕНИЙ ГЕННАДЬЕВИЧ, КУРОЧКИН ЮРИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 15/80

Метки: вычислительной, модуль, однородной, структуры

Опубликовано: 23.07.1989

Код ссылки

<a href="https://patents.su/14-1495809-modul-odnorodnojj-vychislitelnojj-struktury.html" target="_blank" rel="follow" title="База патентов СССР">Модуль однородной вычислительной структуры</a>

Предыдущий патент: Двухпроцессорная вычислительная система

Следующий патент: Устройство для перебора кодов

Случайный патент: Нулевой фильтр