Преобразователь уровня напряжения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 2004073

Авторы: Кокорин, Серебренников, Шумков

Текст

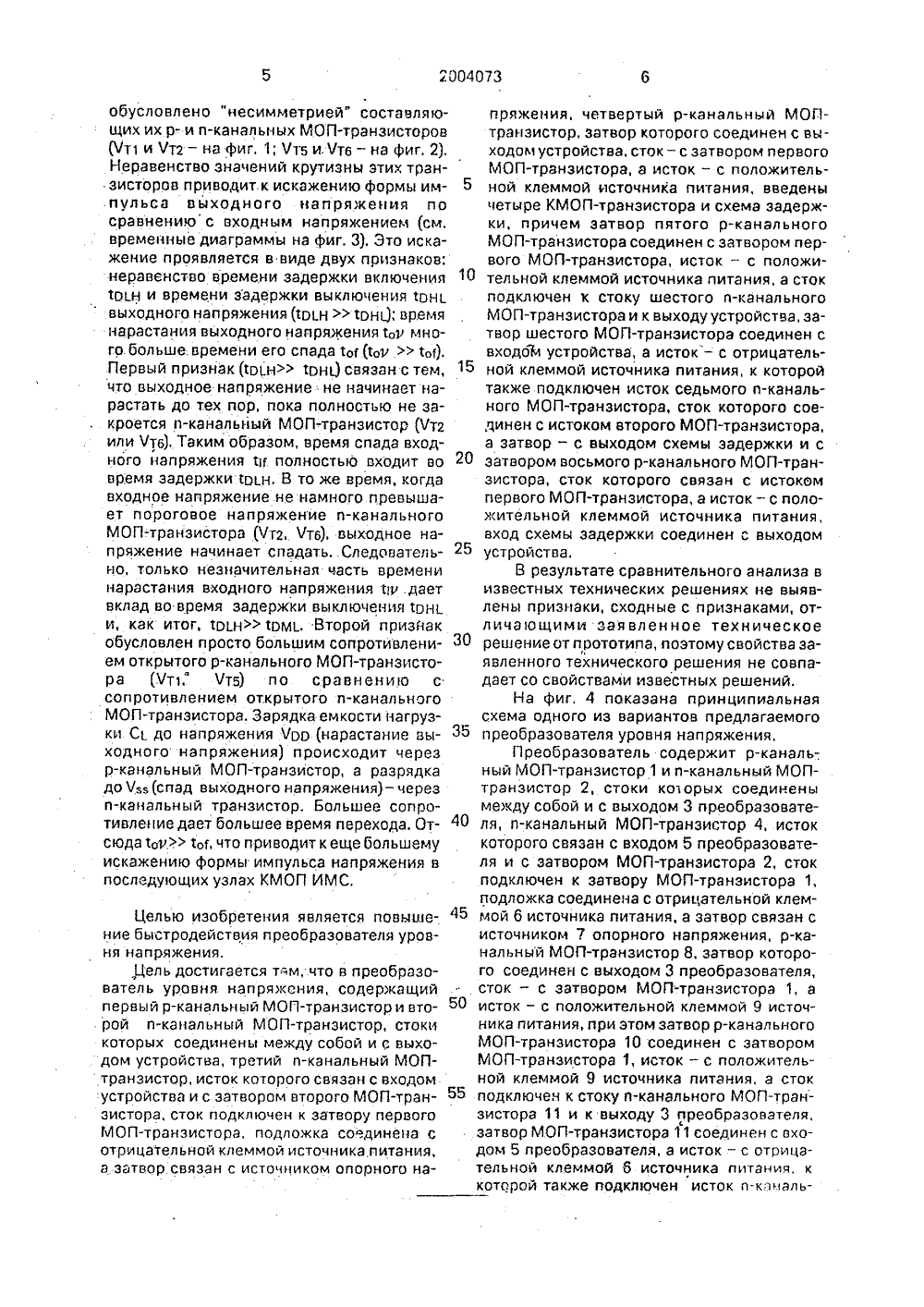

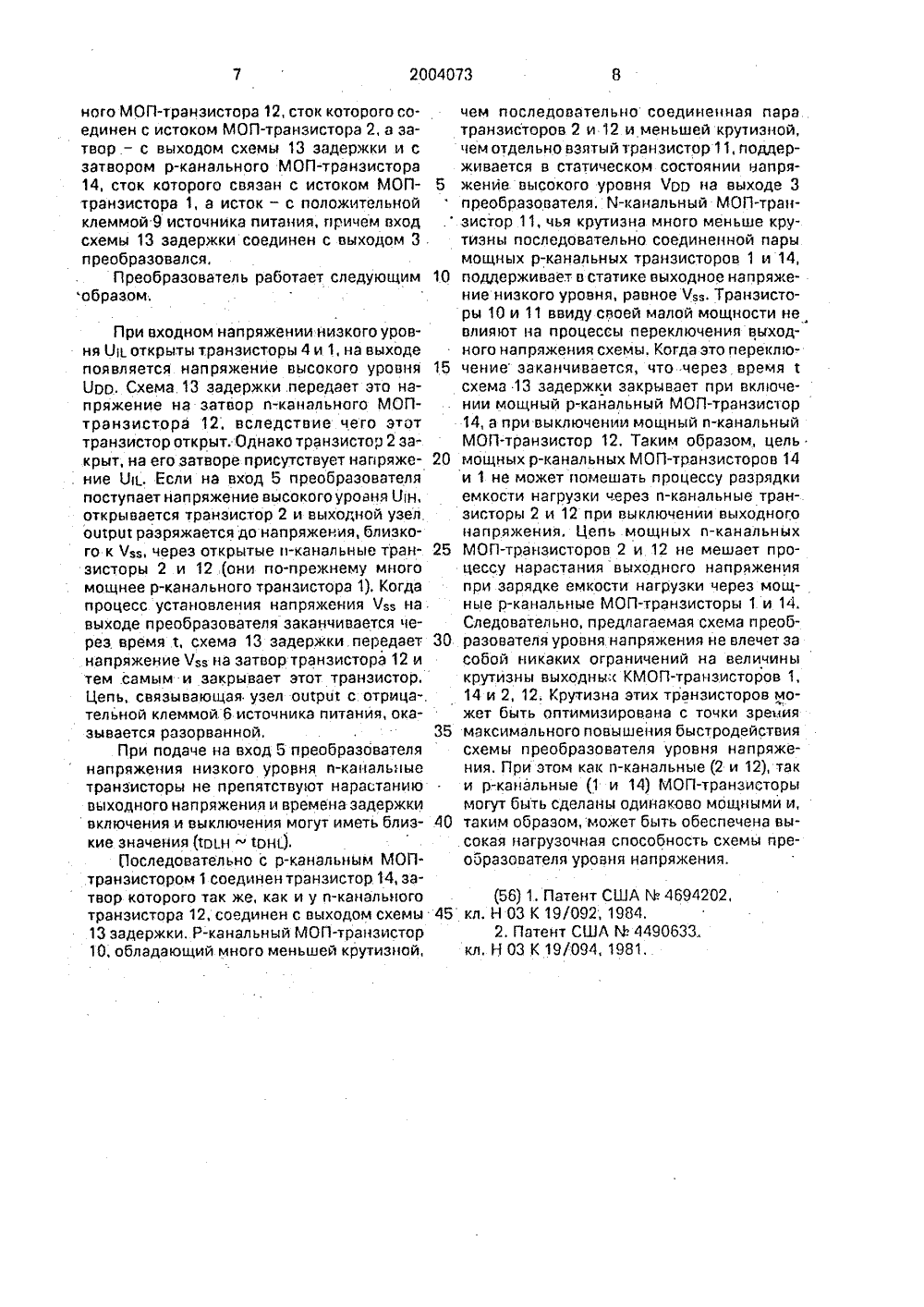

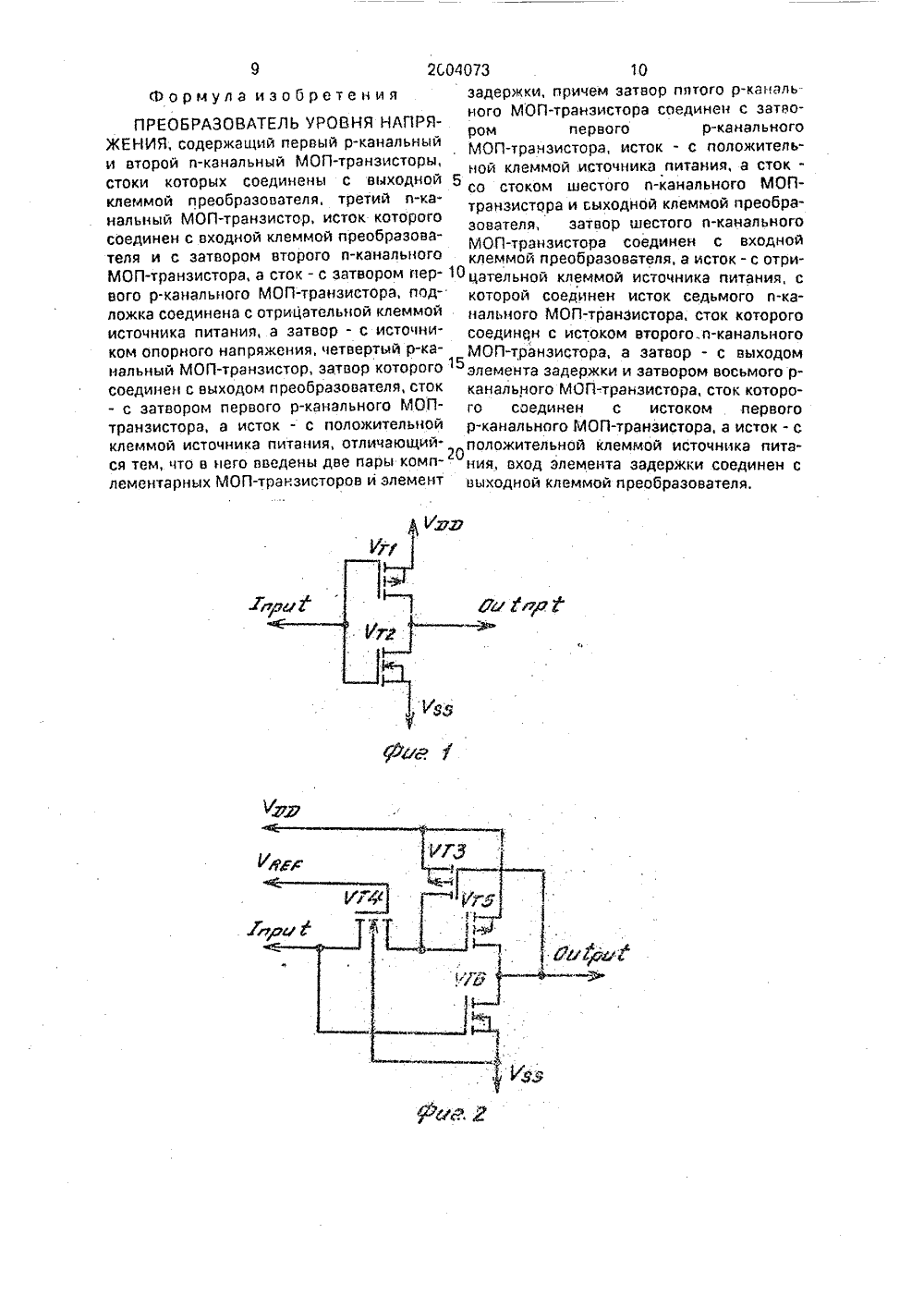

ОПИСАНИЕ ИЗОБРЕТЕН К ПАТЕ Ф омнтет Россииской Федерации о патентам и товарным знакам(57) Изобретение относится к интегральным микросхемам, построенным на базе комплементарных МОП-транзисторов (КМОП), а более конкретно к КМОП-преобразователям уровня напряжения. Сущность изобретения: преобразователь уровня напряжения содержит р-канальный МОП-транзистор 1 и и-канальный МОП-транзистор 2, стою которых соединены с выходом 3 преобразователя, и-канальный МОП-транзистор 4, исток которого связан с входом 5 преобразователя и с затвором МОП-транзистора 2, сток подключен к затвору МОП-транэистора 1, подложка соединена с отрицательной клеммой 6 источника питания, а затвор в) ЕУ дц 2004073 Ч 1 (БЦ 5 Б 03 Е 19 0175 Н 03 К 19 09 связан с источником 7 опорного напряжения, р-канальный МОП-транзистор В, затвор которого соединен с выходом 3 преобразователя, сток - с затвором МОП-транзистора 1, а исток - с положительной клеммой 9 источника питания, при этом затвор р-канального МОП-транзистора 10 соединен с затвором МОП-транзистора 1, исток - с положительной клеммой 9 источника литания, а сток подключен к стоку и-канального МОП-транзистора 11 и к выходу 3 преобразователя, затвор МОП -транзистора 11 соединен с входом 5 преобразователя а исток - с отрицательной клеммой 6 источника питания, к которой также подключен исток д-канального МОП-транзистора 12, сток которого соединен с истоком МОП-трайзистора 2, а затвор - с выходом схемы 13 задержки и с затвором р-канального МОП-транзистора 14, сток которого связан с истоком МОП-транзистора 1, а исток- с положительной клеммой 9 источника питания, причем вход схемы 13 задержки соединен с выходом 3 преобразователя. 4 ил.Изобретение относится к интегральныммикросхемам, построенным на базе комплементарных МОП-транзисторов КМОП), аболее конкретно к КМОП-преобразователям уровня напряжения. 5Схемы преобраэователейуровня напряжения предназначенные для формированиявыходного сигнала с напряжениями высокого Оон и низкого Оо уровней, отличных отсоответствующих значений для входного 10напряжения (Он и ВД, при этом амплитудасигнала на выходе преобразователя уровнянапряжения может существенно превышать амплитуду входного сигнала, Один изнаиболее распространенных случаев применения КМОП-преобразователей уровнянапряжения - это схемы согласования ТТЛсхем и КМОП ИМС (в этом случае О +0,8В; О н+ 2,4 В; Оо - ОВ; Оон=+ Ч.с, где+Чсс - напряжение питания КМОП ИМС,Чсс-+5, +9, +12 В ,),Известна наиболее простая схема преобразователя уровня напряжения, реализуемая на двух КМОП-транзисторах - схемаКМОП-инвертора (фиг. 1), у которой крутизна и-канального МОП-транзистора Чт 2) значительно превышает крутизну р-канальногоМОП-транзистора Чт 1). Отношение значений крутизны этих транзисторов выбираюттаким, чтобы при входном напрякении высокого уровня Он открытый и-канальныйтранзистор Чт 2 полностью шунтировал частично открытый р-канальный транзисторЧт 1, т.е, выходное напряжение при этом было близко к нулю Ч,) Щ Такая схема пре- Збобразователя уровня напряжения, .обладаяпредельной простотой, имеет недостатки, аименно большой статический ток потребления при входном напрякении высокогоуровня и низкое быстродействие, так как ч 0допускает работу только при низких частотах входного напрякения, Первый недостаток связан с тем, что входное напряжениевысокого уровня Вн может отличаться отнапряжения питания КМОП ИМС +Чсс на 4величину, превышающую абсолютное значение порогового напряжения р-канального МОП-транзистора Ортн), В этом случаер-канальный МОП-транзистор Чт 1) не будет полностью закрыт и через него и черезполностью открытый и-канальный транзистор Чт 2 протекает большой статическийток потребления 1 сс. Для случая согласования ТТЛ - КМОП величина асс тем больше,чем больше напряжение питания +Чсс.Наиболее близким по технической сущности к изобретению является преобразователь уровня напряжения, содержащий первый р-канальный МОП-транзистор и второй и-канальный МОП-транзистор, стоки которых соединены между собой и с выходом устройства, третий и-канальный МОП-транзистор, исток которого связан с входом устройства и с затвором второго МОП-транзистора, сток подключен к затвору первого МОП-транзистора, подложка соединена с отрицательной клеммой источника питания и с истоком второго МОП-транзистора, а затвор связан с источником опорного напряжения, четвертый рканальный МОП транзистор, затвор которого соединен с выходом устройства, сток - с затвором первого МОП-транзистора, а исток - с положительной клеммой источника литания и с истоком первого МОП-транзистора 12).В этом преобразователе устранен первый недостаток схемы, показанной на фиг.1. В схемудобаоленил еще одна пара КМОП- транзисторов. Кроме того, требуется специальный формирователь опорного напряжения Член, В основе схемы имеется все тот же КМОП-инвертор с соотношением, составленным транзисторами Чтб и Чтб, причем и-канальный МОП-транзистор (Чтб) по-прежнему значительно мощнее р-канального (Чтя). Такое ке отношение имеют величины крутизны транзисторов Чт 4 и Чтз (Чт 4 много мощнее Чтз), Напряжение Чгор необходимо выбирать таким, чтобы при минимальном входном напряжении высокого уровня Он и-канальный МОП-тран- зистор Чт 4 был бы полностью закрыты, а при максимальном входном напряжении низкого уровня О1 этот же транзистор был бы полностью открыт, В последнем случае Чт 4 должен шунтировать открытый р-канальный транзистор Чтз, обеспечивал формирование на затворе транзистора Чт 5 низкого напряжения. При поцаче на вход схемы напряжения высокого уровня Цн открывается и-канальный МОП-транзистор Чтб, что обеспечивает переход выходного напрякения на уровень, близкий к Ч. При этом р-канальный МОП-транзистор Чтз оказывается открытым, и через него затвор р-канального МОП-транзистора Чт 5 заряжается до напряжения Чоо (входной и-канальный МОП- транзистор Чт 4 в этом случае закрыт). Таким образом, транзистор Чтв оказывается полностью закрытым при входном напряжении высокого уровня Ьн независимо от того, какова величина этого напряжения, т,е, эта схема имеет низкий статический ток потребления, характерный для КМОП-схем,Недостатком этой схемы преобразователя уровня напряжения также является низкое быстродействие, которое, как и в случае схемы, представленной на фиг. 1, 2004073обусловлено "несимметрией" составляющих их р- и п-канальных МОП-транзисторов О/т 1 и Чтг - на фиг, 1; Чт 5 и Чт 6 - на фиг. 2), Неравенство значений крутизны этих транзисторов приводит к искажению формы им.пульса выходного напряжения по сравнение с входным напряжением (см.временные диаграммы на фиг. 3). Это искажение проявляется в виде двух признаков; неравенство времени задержки включения тон и времени задержки выключения тонвыходного напряжения то 1.н тонД; времянарастания выходного напряжения тор много больше. времени его спада тог (тои то).Первый признак (тон тонд связан с тем, что выходное напряжение не начинает нарастать до тех пор, пока полностью не закроется и-канальный УОП-транзистор Рlт 2 или Чт 6), Таким образом, время спада входного напряжения тг полностью входит во время задержки он. В то же время, когда входное напряжение не намного превышает пороговое напряжение и-канального МОП-транзистора (Чтг, Чтб), выходное напряжение начинает спадатьСледовательно, только незначительная часть времени нарастания входного напряжения ту.дает вклад во время задержки выключения он и, как итог, то 1.нсом 1 Второй призйак обусловлен просто большим сопротивлением открытого р-канального МОП-транзистора (Чть" Чтб) по сравнению с сопротивлением открытого и-канального МОП-транзистора. Зарядка емкости нагрузки С до напряжения Чоо (нарастание выходного напряжения) происходит через р-канальный МОП-транзистор, а разрядка до Ч (спад выходного напряжения) - через и-канальный транзистор. Большее сопротивление дает большее время перехода. Отсюда тою ой, что приводит к еще большему искажению формьг импульса напряжения в последующих узлах КУОП ИУС,Целью изобретения является повышение быстродействия преобразователя уровня напряжения.,Цель достигается тдм, что в преобразователь уровня напряжения, содержащий первый р-канальный МОП-транзистор и второй и-канальный МОП-транзистор, стоки которых соединены между собой и с выходом устройства, третий п-канальный МОП- транзистор, исток которого связан с входом устройства и с затворам второго МОП-транзистора, сток подключен к затвору первого МОП-транзистора, подложка со.динена с отрицательной клеммой источника питания, а затвор. связан с источником опорного напряжения, четвертый р-канальный МОП- транзистор, затвор которого соединен с выходом устройства, сток - с затвором первого УОП-транзистора, а исток - с положительной клеммой источника питания, введены четыре КМОП-транзистора и схема задержки, причем затвор пятого р-канального УОП-транзистора соединен с затвором первого МОП-транзистора, исток - с положи тельной клеммой источника питания, а стокподключен к стоку шестого и-канального МОП-транзистора и к выходу устройства, затвор шестого МОП-транзистора соединен с входами устройства, а исток - с отрицатель ной клеммой источника питания, к которойтакже подключен исток седьмого и-канального МОП-транзистора, сток которого соединен с истоком второго МОП-транзистора, а затвор - с выходом схемы задержки и с 20 затвором восьмого р-канального МОП-транзистора, сток которого связан с истоком первого МОП-транзистора, а исток - с положительной клеммой источника питания, вход схемы задержки соединен с выходом 25 устройства.В результате сравнительного анализа визвестных технических решениях не выявлены признаки, сходные с признаками, отличающими заявленное техническое 30 решение от прототипа, поэтому свойства заявленного технического решения не совпадает со свойствами известных решений.На фиг, 4 показана принципиальнаясхема одного из вариантов предлагаемого преобразователя уровня напряжения,Преобразователь содержит р-каналь-,ный УОП-транзистор 1 и и-канальный УОП- транзистор 2, стоки которых соединены между собой и с выходом 3 преобраэовате ля, и-канальный МОП-транзистор 4, истоккоторого связан с входом 5 преобразователя и с затвором МОП-транзистора 2, сток подключен к затвору МОП-транзистора 1, подложка соединена с отрицательной клем мой б источника питания, а затвор связан систочником 7 опорного напряжения, р-канальный МОП-транзистор 8, затвор которого соединен с выходом 3 преобразователя, сток - с затвором МОП-транзистора 1, а 50 исток - с положительной клеммой 9 источника питания, при этом затвор р-канального МОП-транзистора 10 соединен с затвором УОП-транзистора 1, исток - с положительной клеммой 9 источника питания, а сток 55 подключеч к стоку и-канального УОП-транзистора 11 и к выходу 3 преобразователя, затвор МОП-транзистора 11 соединен с входом 5 преобразователя, а исток - с отрицательной клеммой 6 источника питания, к которой также подключен исток и-клналь 2004073ного МОП-транзистора 12, сток которого соединен с истоком МОП-транзистора 2, а затвор - с выходом схемы 13 задержки и с затвором р-канального МОП-транзистора 14, сток которого связан с истоком МОПтранзистора 1, а исток - с положительнойклеммой 9 источника питания, причем оходсхемы 13 задержки соединен с выходом 3преобразовался. Преобразователь работает следующимобразом. 10 При входном напряжении низкого уровня 01 открыты транзисторы 4 и 1, на выходе появляется напряжение высокого уровня Ооо. Схема. 13 задержки .передает это напряжение на затвор и-канального МОП- транзистора 12, вследствие чего этот транзистор открыт. Однако транзистор 2 за 15 20 крыт, на его затворе присутствует напряжение В. Если на вход 5 преобразователя поступает напряжение высокого уровня Вн, открывается транзистор 2 и выходной узел оотрц 1 разряжается до напряжения, блиэкого к Ч, через открытые и-канальные транэисторы 2 и 12.(они по-прежнему много мощнее р-канального транзистора 1). Когда процесс установления напряжения Чз на выходе преобразователя заканчивается через время т, схема 13 задержки передает напряжение Ч на затвор транзистора 12 и тем .самым и закрывает этот транзистор. Цепь, связывающая. узел ооро 1 с отрицательной клеммой.6 источника питания, ока 35 зыоается разорванной,При подаче на вход 5 преобразователя напряжения низкого урорня и-канальные транзисторы не препятствуют нарастанию выходного напряжения и времена задержки 40 включения и выключения могут иметь близкие значения (тон сонд,Последовательно с р-канэльным МОП- транзистором 1 соединен транзистор 14, затвор которого так же, как и у и-канального транзистора 12, соединен с выходом схемы 4513 задержки. Р-канальный МОП-транзистор1 О, обладающий много меньшей крутизной,чем последовательно соединенная пара транзисторов 2 и 12 и меньшей крутизной, чем отдельно взятый транзистор 11, поддерживается в статическом состоянии иапряжение высокого уровня Чоп на выходе 3 преобразователя. Ы-канальный МОП-транзистор 11, чья крутизна много меньше крутизны последовательно соединенной пары мощных р-канальных транзисторов 1 и 14, поддерживает о статике выходное напряжение низкого уровня, рэоное Чв. Транзисторы 10 и 11 ввиду своей малой мощности не влияют на процессы переключения выходного напряжения схемы. Когда это переключение заканчивается, что через время 1 схема 13 задержки закрывает при включении мощный р-канальный МОП-транзистор 14, а при выключении мощный и-канальный МОП-транзистор 12, Таким образом, цель мощных р-канальных МОП-транзисторов 14 и 1 не может помешать процессу разрядки емкости нагрузки через и-канальные транзисторы 2 и 12 при выключении выходного напряжения. Цепь мощных и-канальных МОП-транзисторов 2 и 12 не мешает процессу нарастания выходного напряжения при зарядке емкости нагрузки через мощные р-канальные МОП-транзисторы 1 и 14. Следовательно, предлагаемая схема преобразователя уровня напряжения не влечет за собой никаких ограничений на величины крутизны выходных КМОП-транзисторов 1, 14 и 2, 12. Крутизна этих транзисторов может быть оптимизирована с точки зреиия максимального повышения быстродействия схемы преобразователя уровня напряжения, При этом как и-канальные (2 и 12), так и р-канальные (1 и 14) МОП-транзисторы могут быть сделаны одинаково мощными и, таким образом, может быть обеспечена высокая нагрузочная способность схемы преобразователя уровня напряжения.26040 Формула изобретенияПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ, содержащий первый р-канальный и второй и-канальный МОП-транзисторы, стоки которых соединены с выходной 5 клеммой преобразователя, третий и-канальный МОП-транзистор, исток которого соединен с входной клеммой преобразователя и с затвором второго и-канального МОП-транзистора, а сток - с затвором пер вого р-канального МОП-транзистора, подложка соединена с отрицательной клеммой источника питания, а затвор - с источником опорного напряжения, четвертый р-канальный МОП-транзистор, затвор которого 15 соединен с выходом преобразователя, сток - с затвором первого р-канального МОП- транзистора, а исток - с положительной клеммой источника питания, отличающий 10 ся тем, что в него введены две пары комплементарных МОП-транзисторов и элемент 73 10задержки, причем затвор пятого р-канального МОП-транзистора соединен с затвором первого р-канального МОП-транзистора, исток - с положительной клеммой источника питания, а стокса стоком шестого и-канального МОП- транзистора и сыходной клеммой преобразователя, затвор шестого п-канального МОП-транзистора соединен с входной клеммой преобразователя, а исток - с отрицательной клеммой источника питания, с которой соединен исток седьмого и-канального МОП-транзистора, сток которого соединен с истоком второго.п-канального МОП-транзистора, а затвор - с выходом элемента задержки и затвором восьмого рканального МОП-транзистора, сток которого соединен с истоком первого р-канального МОП-транзистора, а исток - с положительной клеммой источника питания, вход элемента задержки соединен с выходной клеммой преобразователя.

СмотретьЗаявка

05016344, 28.10.1991

Научно-производственный кооператив "Аксон"

Шумков Илья Евгеньевич, Кокорин Владимир Васильевич, Серебренников Владимир Николаевич

МПК / Метки

МПК: H03K 19/0175, H03K 19/094

Метки: уровня

Опубликовано: 30.11.1993

Код ссылки

<a href="https://patents.su/6-2004073-preobrazovatel-urovnya-napryazheniya.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь уровня напряжения</a>

Предыдущий патент: Частотное пороговое устройство

Следующий патент: Счетное устройство

Случайный патент: Способ получения кормовой добавки для животных