Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1667092

Автор: Петров

Текст

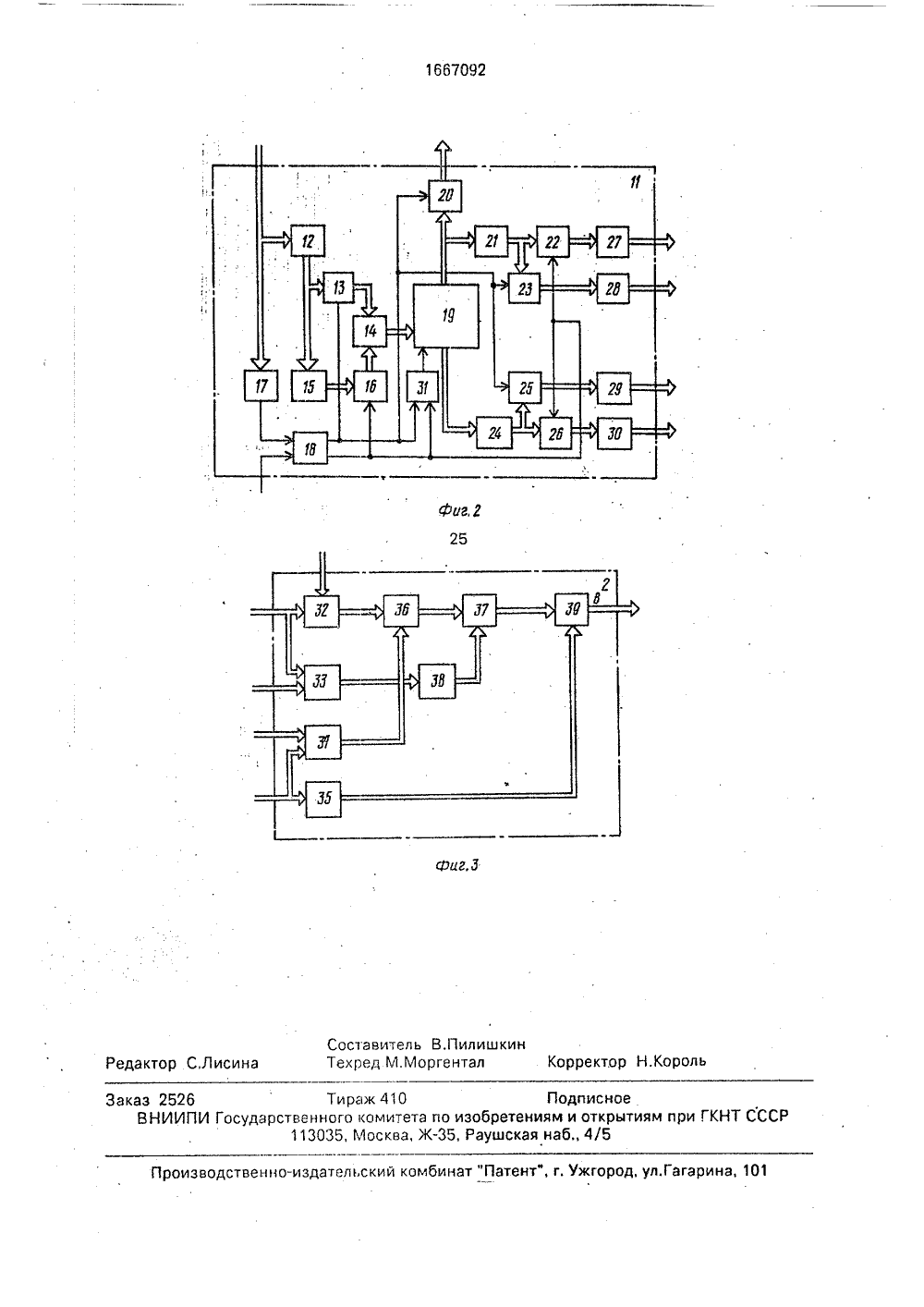

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) (11) 092 А 1 1)5 6 06 Р 15 ПИСА НИ ВТОРСКО ческий инс тво СССР00, 1986.тво СССР00, 1985. ОДЕЛИРОВАНИЯПЕРАЦИИ ПРОИЯ ПОЛЕЗНЫХСКРЕТНОЙ СЕПАИСТИКЕся к технике модеих процессов обоОСУДАРСТВЕННЫЙ КОМИТЕТО ИЗОБРЕТЕНИЯМ,И ОТКРЫТИЯМРИ ГКНТ СССР ИЕ ИЗОБРСВИДЕТЕЛЬСТВУ(54) УСТРОЙСТВО ДЛЯ М РАЗДЕЛИТЕЛЬНОЙ О ЦЕССА ОБОГАЩЕН ИСКОПАЕМЫХ ПО ДИ РАЦИОННОЙ ХАРАКТЕР (57) Изобретение относи лирования технологичес гащения полезных ископаемых и может быть использовано при исследовании разделительных операций в реальном масштабе времени. Цель изобретения расширение функциональных возможностей за счет воспроизведения значений дискретно заданной сепарационной характеристики разделительной операции процесса обогащения полезных ископаемых в реальном масштабе времени. Для моделирования генератором 1 случайных чисел воспроизводится случайное число - аргумент дискретной сепарационной характеристики, и по заданным дискретным значениям самой сепарационной характеристики в блоках 2 и 11 вычисляется текущее моделируемое значение сепарационной характеристики. 3 ил.15 20 25 30 35 40 45 50 55 Изобретение относится к моделированию технологических процессов обогаще. ния полезных ископаемых и может быть использовано в качестве приставки к вычислительной машине при проведении исследований разделительных операций в реальном масштабе времени.Цель изобретения - расширение функциональных возможностей путем воспроизведения значений дискретно заданной сепарационной характеристики разделительной операции процесса обогащения полезных ископаемых в реальном масштабе времени.Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике(фиг,1) содержит генератор 1 случайных чисел, выход которого подключен к первой выходной шине всего устройства, к первому входу блока 2 вычисления текущего значения сепарационной характеристики, к первому входу схемы 3 сравнения и через дешифратор 4 - к установочному входу счетчика 5 адреса.Дешифратор 4 преобразует многоразрядное число на своем входе в одиночный импульс на выходе, Выход счетчика 5 адреса подключен к информационному входу коммутатора б и первому входу схемы 7 сравнения. Второй вход схемы 7 сравнения соединен с выходом регистра 8 адреса. Этот же выход регистра 8 адреса подключен к информационному входу коммутатора 9. Разрешающие входы коммутаторов 6 и 9 соответственно соединены с первым и вторым выходами схемы сравнения,Импульс на первом выходе схемы 7 Сравнения воспроизводится в том случае, когда содержимое счетчика 5 адреса не превосходит содержимое регистра 8 адреса. Импульс на втором выходе схемы 7 сравнения воспроизводится в том случае, когда содержимое счетчика 5 адреса превосходит содержимое регистра 8 адреса,Выходы коммутаторов б и 9 через блок элементов ИЛИ 10 соединены с адресным входом блока 11 памяти значений сепара ционной характеристики. Второй вход блока 11 памяти соединен с первым выходом схемы 3 сравнения, Первый выход блока 11 памяти соединен с вторым входом схемы 3 сравнения. Второй выход схемы сравнения подключен к счетному входу счетчика 5 адреса.Импульс на первом выходе схемы 3 сравнения воспроизводится, если число, прогенерированное генератором 1 случайных чисел не меньше числа на первом выходе блока 11 памяти. В противном случае вырабатывается импульс на второй выходной шине схемы 3 сравнения и, соответственно, на счетном входе счетчика 5 адреса,Второй, третий, четвертый и пятый выходы блока 11 памяти подключены к соответствующим входам блока 2 вычисления, Выход блока 2 вычисления соединен с второй выходной шиной всего устройства. Адресный вход блока 11 памяти (фиг.2) подключен через линию 12 задержки и информационный вход коммутатора 13 к первому входу блока элементов ИЛИ 14, через линию 12 задержки, сумматор-вычитатель 15 и информационный вход коммутатора 16 - к второму входу блока элементов ИЛИ 14 и через дешифратор 17 (назначение которого аналогично назначению дешифратора 4) - к установочному входу в нулевое состояние триггера 18, Установочный в единичное состояние вход триггера 18 соединен с вторыв входом блока 11 памяти,Выход блока элементов ИЛИ 14 под= ключен к адресному входу запоминающего устройства 19, Первый информационный выход запоминающего устройства 19 соединен через инфоромационный вход коммутатора 20 с первой выходной шиной блока 11 памяти и через регистр 21 памяти - с информационными входами коммутаторов 22 и 23. Второй информационный выход запоминающего устройства 19 через регистр 24 памяти подключен к информационным входам коммутаторов 25 и 26, Выходы коммутаторов.22, 23, 25 и 26 через регистры 27, 28, 29 и 30 памяти соединены. соответственно, с второй, третьей, четвертой и пятой выходными шинами блока 11 памяти. Разрешающие входы коммутаторов 13, 20, 23 и 25 подключены к нулевому выходу триггера 18, а коммутаторов 16, 22 и 26 - к единичному выходу триггера 18 через элемент ИЛИ 31 подключены к управляющему входу запоминающего устройства 19.Запоминающее устройство 19 позволяет хранить два вектора данных: дискретные значения аргумента сепарационной характеристики и соответствующие им тактовые дискретные значения сепарационной характеристики. При этом поступление адресана вход запоминающего устройства 19 обес-печивает выДачу на первый его выходной шине аргумента сепарационной характеристики, а на второй выходной шине - значений сепарационной характеристики. Адрес формируется в счетчике 5 адреса, Импульс на установочном входе счетчика 5 адреса обеспечивает установку его в нулевое состояние, соответствующее адресу в запомина 1667092.510 15 20 ти поступает на вход дешифратора 17, кото 25 30 40 50 ющем устройстве 19, по которому записаны второе значение аргумента и как таковое второе значение сепарационной характеристики, Регистр 8 адреса всегда содержит адрес, по которому в запоминающем устройстве 19 хранится последнее значение аргумента и самое последнее значение сепарационной характеристики.Первый и второй входы блока 2 вычисления (фиг,З) подключены соответственно к первому и второму входам первого блока 32 вычитания. Второй и третий входы блока 2 соединены соответственно с первым и вторым входами второго блока 33 вычитания.Четвертый и пятый входы блока 2 подключены соответственно к.первому и второму входам третьего блока 34 вычитания. Пятый вход, кроме того, соединен с входом первой линии задержки 35 блока вычисления 2, Выходы первого и третьего блоков 32 и 34 подключены, соответственно, к первому и второму входам блока 36 умножения, выход которого соединен с первым входом блока 37 деления. Второй вход блока 37 через вторую линию задержки блока 2 вычисления подключен к выходу второго блока 33 вычитания. Выход блока 37 и выход первой линии 35 задержки соединен соответственно с первым и вторым входами блока 39 суммирования, выход которого является выходом всего блока 2 вычисления.Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике работает следу ющим образом.Генератор 1 случайных чисел воспроизводит случайное число - текущее значение аргумента сепарационной характеристики, которое поступает на первую выходную шину всего устройства, на первую. входную шину блока 2, на первый вход схемы 3 сравнения и после преобразования в одиночный импульс дешифратором 4 - на установочный вход счетчика 5 адреса. Импульс 4 на установочном входе счетчика 5 адреса переводит его в состояние, соответствующее адресу в запоминающем устройстве 19, по которому записаны второе значение аргумента заданной сепарационной характеристики и как таковое второе значение сепарационной характеристики.Установленный начальный адрес подается на информационный вход коммутатора 6 и первый вход схемы 7 сравнения, на вто рой вход которой, также как и на информа- ционный вход коммутатора 9, поступает содержимое регистра 8 адреса - адрес в запоминающем устройстве 19, по которому записаны последнее значение аргумента и как таковое последнее значение сепарационной характеристики,Если содержимое счетчика 5 адреса не превосходит содержимое регистра 8 адреса, то на первом выходе схемы 7 сравнения вырабатывается сигнал, который открывает коммутатор 6 и обеспечивает поступление адреса из счетчика 5 адреса через коммутатор 6 и блок элементов ИЛИ 10 на адресный вход блока 11 памяти. Н противном случае,когда содержимое счетчика 5 адреса превосходит адрес, хранящийся в регистре 8 адреса, вырабатывается сигнал на втором выходе схемы 7 сравнения, который открывает коммутатор 9 и обеспечивает поступление адреса иэ регистра 8 адреса черезкоммутатор 9 и блок элементов ИЛИ 10 наадресный вход блока 11 памяти.Адрес на адресном входе блока 11 памярый преобразуетего в сигнал, поступающий на вход триггера 18 и устанавливающий его в нулевое состояние, Этот же адрес поступает через линию 12 задержки на вход коммутатора 13 и вход сумматора-вычитателя 15, Линия 12 задержки обеспечивает синхронизацию работы блока 11 памяти, необходимость в которой обусловливается необходимостью перевода триггера 18 в нулевое состояние до начала обработки блоком 11 памяти адреса, поступающего на его адресный вход. Сумматор-вычитатель 15 при поступлении на его вход адреса от линии 12 задержки формирует адрес, предшествующий поступающему на его вход Так как триггер 18 находится в нулевом состоянии, что обеспечивает открытие коммутатора 13, адрес с адресного входа блока 11 памяти через линию 12 задержки, коммутатор 13 и блок элементов ИЛИ 14 поступает на вход запоминающего устройства 19. В запоминающем устройстве 19 хранятся два вектора данных: вектор заданных значений аргумента сепарационной характеристики и. соответствующий ему вектор значений сепарационной характеристики. При поступлении адреса на вход запоминающего устройства 19 и сигнала от триггера 18, проходящего через элемент ИЛИ 31 на управляющий вход запоминающего .устройства 19, на первом его выходе воспроизводится соответствующее этому адресу значение аргумента сепарационной характеристики, а на втором выходе запоминающего устройства 19 - соответствующее поданному адресу и выбранному по нему значение аргумента - значение сепарационной характеристики. Аргумент и значение сепарационной характеристики записывается в регистры 21 и24 памяти соответственно, Так как триггер 18 находится в нулевом состоянии и, следовательно, коммутаторы 23 и 25 открыты, содержимое регистров 21 и 24 памяти переписывается в регистры 28 и 29.Значение аргумента сепарационной характеристики с первого выхода запоминающего устройства 11 через коммутатор 20 подается на второй вход схемы 3 сравнения (коммутатор 20 открыт, так как на его разрешающем входе имеется сигнал, поданный с нулевого выхода триггера 18). Если текущее значение сепарационной характеристики, прогенерированное генератором 1 случайных чисел, меньше заданного значения аргумента сепарационной характеристики, извлеченного из запоминающего устройства 19, то вырабатывается сигнал на второй выходной шине схемы 3 сравнения, поступающий на счетный вход счетчика 5 адреса.Этот сигнал переводит счетчик 5 адреса в состояние, соответствующее последующему адресу запоминающего устройства.19 в сравнении с ранее записанным в счетчике адреса 5 адресном. Б противном случае (текущее значение аргумента сепарационной характеристики не меньше заданного значения ее аргумента) вырабатывается сигнал на первом выходе схемы 3 сравнения, По этому сигналу триггер 18 переводится в единичное состояние, открывается коммутатор 16 и адрес, вычисленный сумматором-вычи тателем 15, через коммутатор 16 и блок элементов. ИЛИ 14 поступает на вход запоминающего устройства 19,Одновременно сигнал с единичноговыхода триггера 18 через элемент ИЛИ 31 поступает на управляющий вход запоминающего устройства 19, Соответствующее этому адресу значение аргумента сепарационной характеристики через регистр 21 памяти и коммутатор 22 (коммутатор 22 открыт, так как триггер 18 находится в единичном состоянии) записывается в регистр 27 памяти. Заданное значение сепарационной характеристики через регистр 24 памяти и коммутатор 26, также открытый в связи с тем, что триггер 18 находится в единичном состоянии, записывается в регистр 30 памяти. Таким образом, в регистрах 27 - 30 памяти хранятся числа Х(1 с - 1), ХЯ, УЯ, У(К - 1) соответственно, необходимые для отыскивания текущего значения сепарационной характеристики, где Х - текущее (прогенерированное генератором случайных чисел) значение аргумента сепарационной характеристики;Х(К - 1), Х(Е) - заданные дискретные значения аргументов сепарационной характеристики (Х(К - 1)(= Хс; Х(с);ф(К), У(1) - заданные дискретные значения сепарационной характеристики, соответствующие Х(К - 1) и ХЯ;У - текущее (воспроизводимое) значе ние сепарационной характеристики (У(1-1)сФ У= У(К,10 15 20 25 30 35 40 45 50 55 Блок 2 вычисления по текущему значению аргумента, прогенерированному генератором 1 случайных чисел и содержимым регистров 27-30 памяти вычисляет текущее значение сепарационной характеристики, которое подается на вторую выходную шину всего устройства, При этом блоки 32, 33 и 34 вычисляют соответственно разности (Х - Х(3-1)1, Х(с) - Х( - 1)1 и (У(с) - У(с - 1), Блок 36 вычисляет произведение (Х - Х(1 - 1 (У(1) - У(М - 1, блок 37 осуществляет деление х-1- ПНЯ -У-Я х -х- ца блок 39 к этой дроби прибавляет У(Е - 1).При этом линии 35 и 38 задержки предназначены для синхронизации вычислений. Формула изобретения 1. Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике, содержащее дешифратор и блок памяти значений сепарационной характеристики, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей за счет воспроизведения значений дискретно заданной сепарационной характеристики разделительной операции процесса обогащения полезных ископаемых в реальном масштабе времени, введены блок вычисления текущего значения сепарационной характеристики две схемы сравнения, счетчик адреса, регистр адреса, два коммутатора, блок элементов ИЛИ и генератор случайных чисел, выход которого подключен к первой выходной шине устройства, к первому входу блока вычисления текущего значения сепарационной характеристики, к первому входу первой схемы сравнения и через дешифратор - к установочному входу счетчика адреса, выходом соединенного с информационным входом первого коммутатора и первым входом второй схемы сравнения, второй вход которой подключен к выходу регистра адреса, соединенного с информационным входом второго коммутатора, при этом разрешающие входы первого и второго коммутаторов соответственно подключены к выходам "Меньше" и "Больше" второй схемы сравнения, а выходы первого и второго коммутаторов через блокэлементов ИЛИ соединены с адресным входом блока памяти значений сепарационной характеристики, тактовый вход которого подключен к выходу "Больше" первой схемы сравнения, выходом "Меньше" соединенной со счетным входом счетчика адреса, при этом первый информационный выход блока памяти значений сепарационной характеристики подключен к второму информационному входу первой схемы сравнения, а с второго по пятый информационные выходы блока памяти значений сепарационной характеристики подключены соответственно к одноименным входам блока вычисления текущего значения сепарационной характеристики, выход которого соединен с второй выходной шиной устройства,2. Устройство поп.1, отл ича ю ще ес я тем, что блок памяти значений сепарационной характеристики содержит триггер, дешифратор, сумматор-вычитатель, шесть регистров памяти. семь коммутаторов, элемент ИЛИ и блок элементов ИЛИ, линию задержки и запоминающее устройство, при этом адресный вход блока памяти значений сепарационной характеристики подключен через линию задержки и информационный вход первого коммутатора к первому входу блока элементов ИЛИ, через линию задержки, сумматор-вычитатель и информационный вход второго коммутатора - к второму входу блока элементов ИЛИ и через дешифратор - к установочному в нулевое состояние входу триггера, установочный в единичное состояние вход которого соединен с тактовым входом блока памяти значений сепарационной характеристики, а выход блока элементов ИЛИ подключен к адресному входу запоминающего устройства, первый информационный выход которого соединен с информационным входом третьего коммутатора, выход которого соединен с первой выходной шиной блока памяти значений сепарационной характеристики и через первый регистр памяти - с информационными входами четвертого и пятого коммутаторов, второй информационный выход запоминающего устройства через второй регистр памяти подключен к информационным входам шестого и седьмого коммутаторов, а выходы с четвертого по седьмой коммутаторов через соответст венно третий - шестой регистры памяти соединены с второго по пятый информационными выходами блока памяти значений сепарационной характеристики, причем разрешающие входы первого, третьего, пятого и шестого коммутаторов подключены к нулевому выходу триггера, разрешающие входы второго, четвертого и седьмого коммутаторов - . с единичным выходом триггера, а тактовый вход запоминающего устройства 10 через элемент ИЛИ соединен с нулевым и единичным выходами триггера, 3, Устройство по п.1,.о т л и ч а ю щ е едержит три блока вычитания, блок умножения, блок деления, блок суммирования и две линии задержки, при этом первый вход блока вычисления текущего значения 20 сепарационной характеристики подключен к первому входу первого блока вычитания, второй вход которого соединен с вторым входом блока вычисления текущего значения сепарационной характеристики, подключенного к первому входу второго блока вычитания, второй вход которого соединен с третьим входом блока вычисления текущего значения сепарационной характеристики, четвертый вход которого подключен к 25 30 первому входу третьего блока вычитания,второй вход которого соединен с пятым входом блока вычисления текущего значения сепарационной характеристики, связанным также с входом первой линии задержки бло 35 ка вычисления текущего значения сепарационной характеристики, а выходы первого и третьего блоков вычитания соединены соответственно с первым и вторым входами блока умножения; выход которого подключен к первому входу блока деления, второй вход которого через вторую линию задержки блока вычисления текущего значения сепарационной характеристики соединен с выходом второго блока вычитания, а выход,40 блока деления подключен к первому входу блока суммирования, второй вход которого через первую линию задержки блока вычисления текущего значения сепарационной характеристики соединен с пятым входом блока вычисления текущего значения сепарационной характеристики, выход которогоподключен к выходу блока суммирования,с я тем, что блок вычисления текущего зна 15 чения сепарационной характеристики со1667092 2 Фи Составитель В.ПилишкинРедактор С,Лисина Техред М,Моргентал Корректор Н.Корол изводственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 аз 2526 ВНИИП Тираж 410 Подписноеосударственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4718962, 14.07.1989

ИРКУТСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ПЕТРОВ АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: дискретной, ископаемых, моделирования, обогащения, операции, полезных, процесса, разделительной, сепарационной, характеристике

Опубликовано: 30.07.1991

Код ссылки

<a href="https://patents.su/6-1667092-ustrojjstvo-dlya-modelirovaniya-razdelitelnojj-operacii-processa-obogashheniya-poleznykh-iskopaemykh-po-diskretnojj-separacionnojj-kharakteristike.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике</a>

Предыдущий патент: Многоканальное устройство для подключения абонентов к общей магистрали

Следующий патент: Вычислительная система

Случайный патент: Множительно-делительное устройство