Устройство для обнаружения ошибок в параллельном коде

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1564733

Автор: Музыченко

Текст

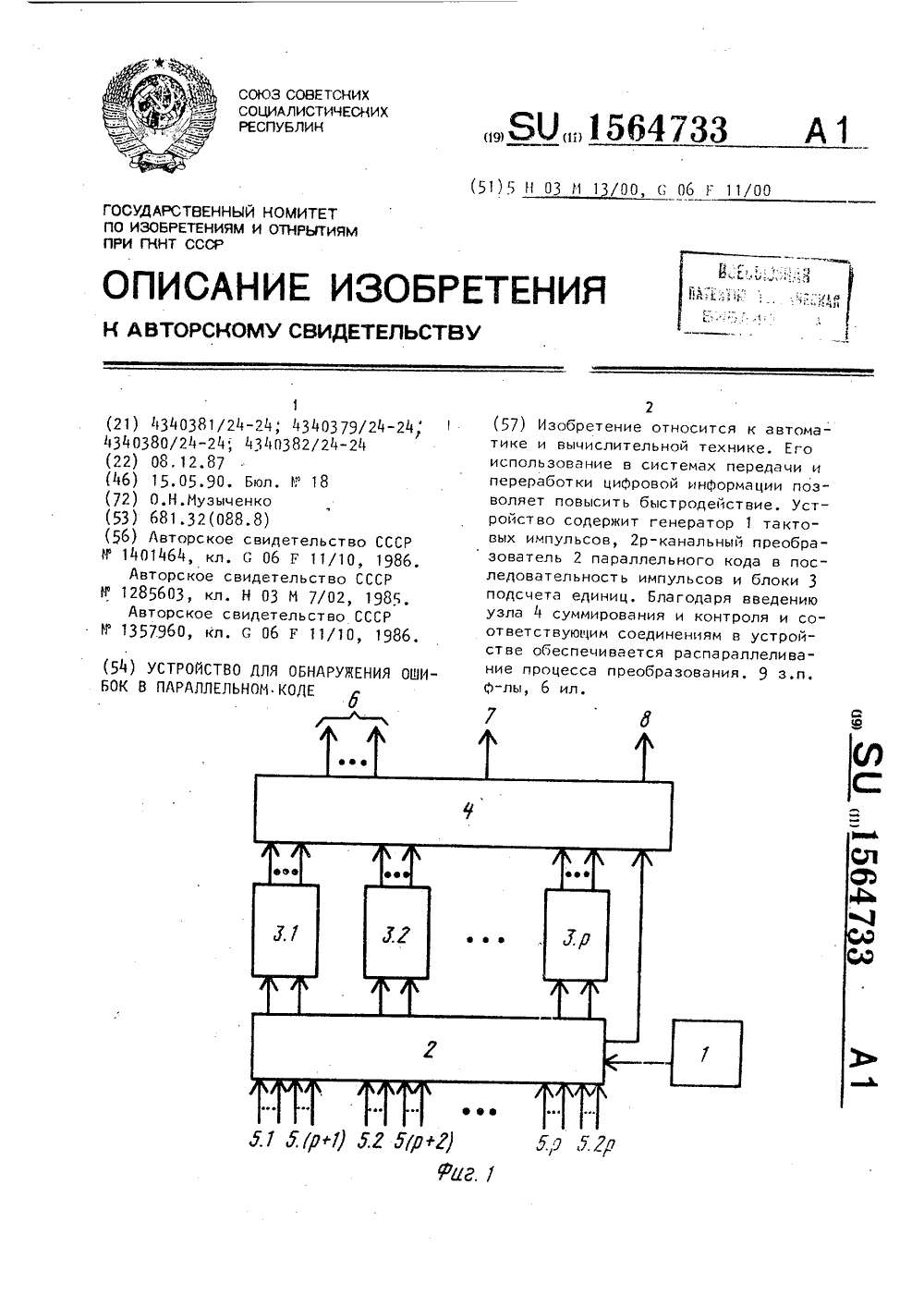

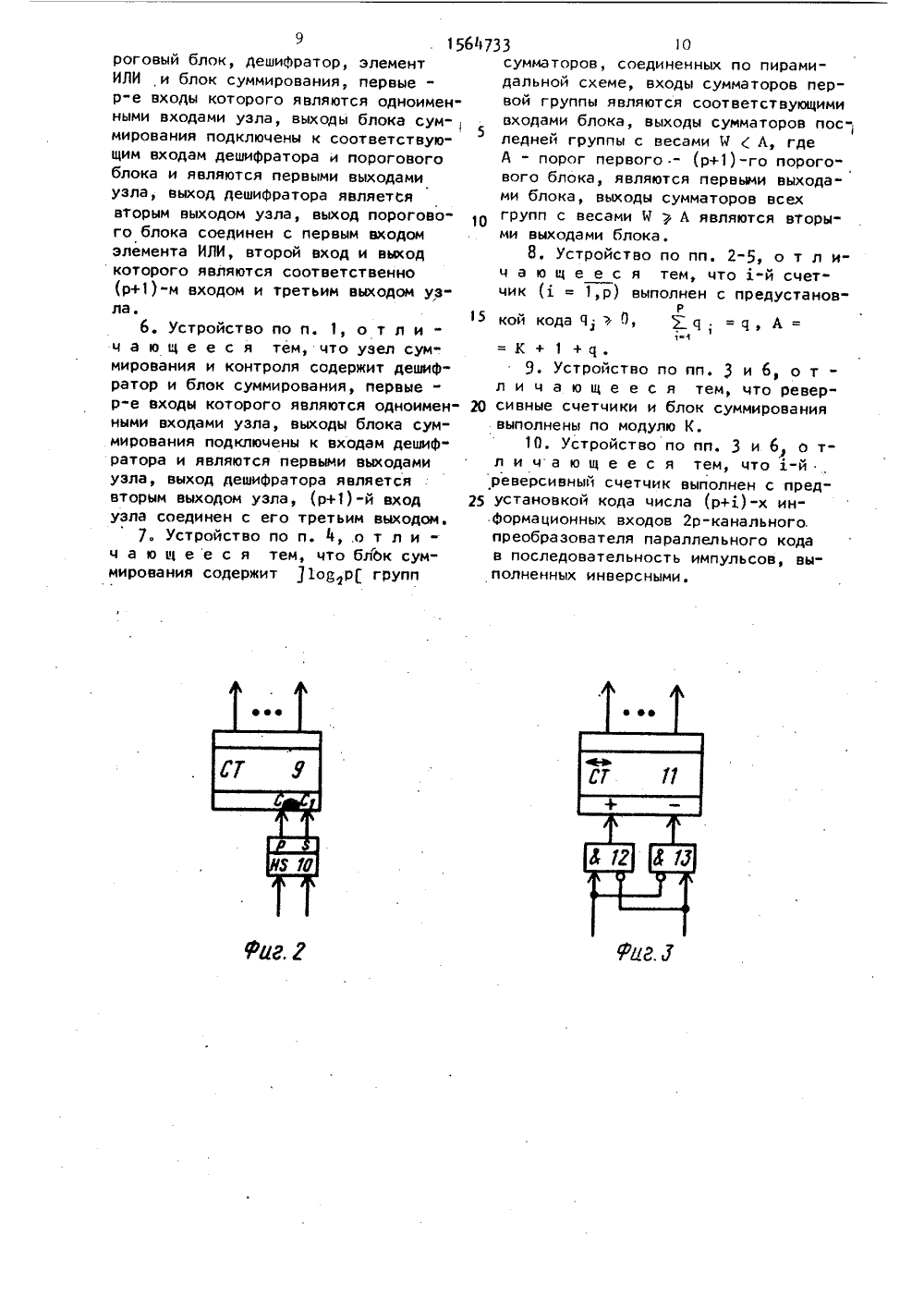

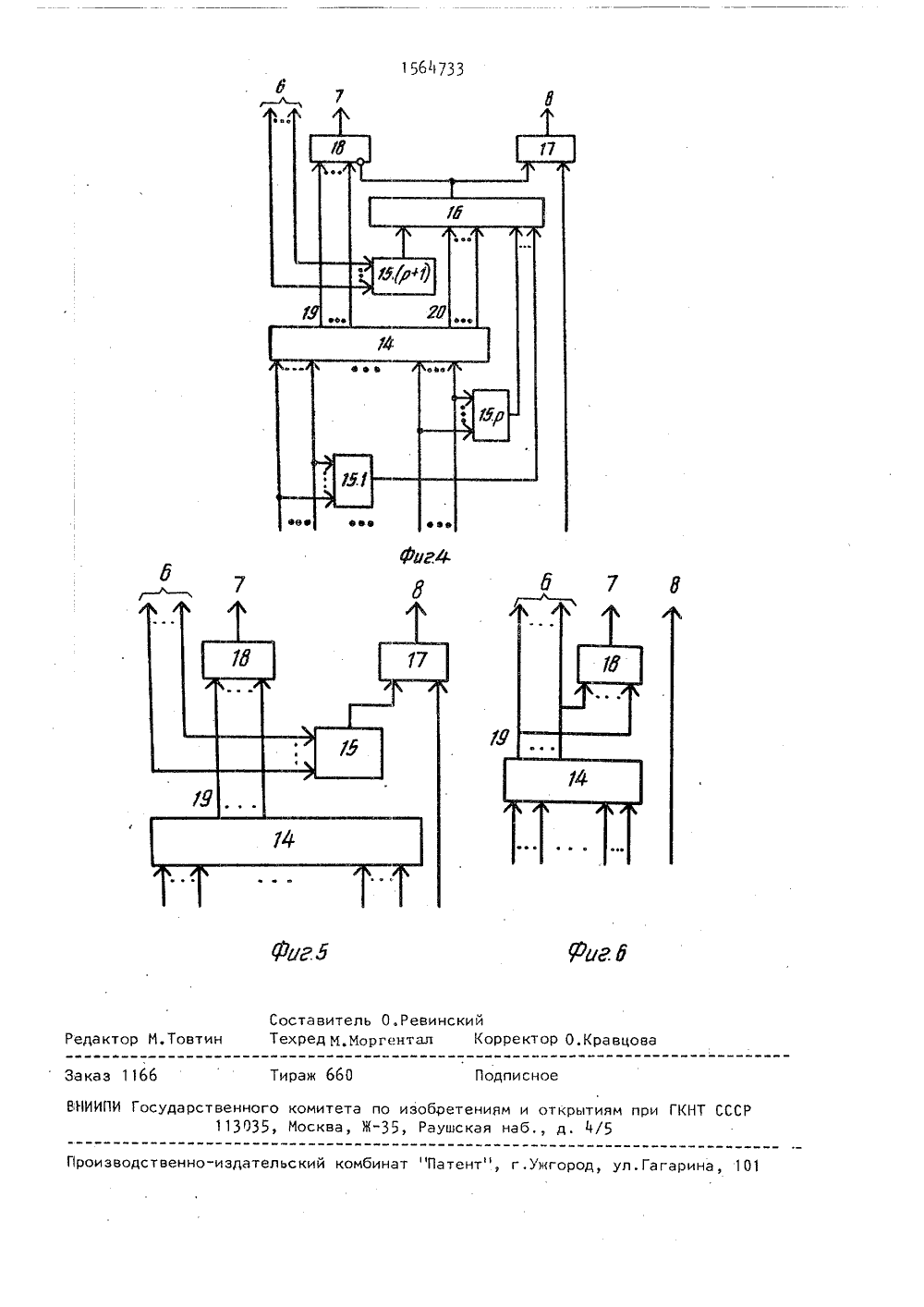

+ 1 + ц, При этом блок 14 не является модульным,В том случае, когда узел 4 имеетвыполнение по Фиг. 6, реверсивныйсчетчик 11 блока 3. 1 может быть выполнен с предустановкой кода числавходных разрядов в группе 5(р + )входов, при этом входы выполнены инверсными, Для режимов работы по модулю К блок 14 суммирования и реверсивные счетчики 11 выполнены функцио.нирующими по модулю К.Пороговые блоки 15 в вариантахфиг. 4, 5 имеют порог А. Если выбрать исходное состояние счетчикови =2,-К, тоА=2, приэтом пороговые блоки 15,д вырождаются в соединение с прямоговыхода последнего разряда счетчика9 или 11.Дешифратор 18 в варианте фиг, 4представляет собой элемент И, прямыевходы которого подключены к тем выходам блока 14, веса которых равныномерам единичных разрядов в двоичномпредставлении веса кода К + , а инверсные входы - к остальным выходамблока 14 и выходу элемента ИЛИ 16.Дешифратор 18 по вариантам фиг. 5 и6 имеет такое же выполнение и подключение, кроме соединения с элементом 16 ИЛИ,Узел 4 выполняется по фиг 4 приК,1пг- по фиг. 5 при-(К и 3 р.- 2 р) и по Фиг, б йри К(пр),где и - число входов устройства,К - вес контролируемого равновесного кода.Устройство работает следующимобразом,В исходном состоянии преобразователь 2 и счетчики в блоках 3 сброшены. При этом, если блок 4 выполненпо Фиг. 4 - 6, а блок 3 - по Фиг. 2,в счетчике 9.д записан код ч;0если блок 4 выполнен по Фиг. б; аблок 3 - по фиг3, то в реверсивныесчетчики1. записан код числа вхо"дов 5.(р + ).На входы 5 подается преобразуемыйкод и в случае выполнения преобразователя 2 на регистрах сдвига - записывается в эти, регистры,При поступлении тактовых импульсов с выхода генератора 1 на тактовый вход преобразователя 2 последнийпреобразует параллельный код на вхоИзобретение относится к автоматие и вычислительной технике и можетыть использовано при, создании сист 1 ем передачи и переработки цифровойинформации.Цель изобретения - повышение быстродействия.На Фиг. 1 изображена блок-схемаустройства, на Фиг2 и 3 - варианты выполнения блока подсчета единицФна Фиг. 4-5 - варианты выполнениязла суммирования и контроля.Устройство содержит (фиг. 1) геератор 1 тактовых импульсов, 2 р-каальный преобразователь 2 параллель,ого кода в последовательность импульсов, р блоков 3 подсчета единици узел 4 суммирования и контроля,На Фиг. 1 обозначены входы 5, информационные выходы б, контрольныйвыход 7 и выход 8 окончания работы.Преобразователь 2, имеющий 2 ргрупп входов (р = 1,2) обеспечивает преобразование входного кода, 25,азбитого на 2 р групп символов, в2 р последовательностей импульсов,число которых в каждой последовательности равно числу единиц в соответствующей группе символов. Выполнениепреобразователя 2 такое же, как впрототипе, например, на 2 р регистрахсцвига,Блок 3 подсчета единиц может бытьреализован (фиг. 2) на счетчике 9 иполусумматоре 10, при этом его выходЫ суммы и переполнения соединены сосчетными входами соответственно перврго и второго разрядов счетчика 9.Б 1 ок 3 подсчета единиц может бытьреализован (Фиг, 3) иначе на ревер"40сивном счетчике 11 и первом и второмэлементах ЗАПРЕТ 12, 13.Узел 4 суммирования и контроляможет включать в себя (Фиг, 4-6) блок14 суммирования, пороговые блоки 15,45первый и второй элементы ИЛИ 16 р 17и дешиФратор 18.Блок 14. суммирования строится изсумматоров по пирамидальной схеме.При этом те выходы сумматоров, кото 50рые соответствуют весам Ч 4 А (А -порог блоков 15), являются первымивыходами 19 блока; выходы сумматоров с весами И Ъ А - вторые выходы 20.Счетчики 9 (для случаев фиг. 4-6)могут быть выполнены и с предуста"новкой кода с; Ъ О,р где- номер блока 3 (1 = 1,р), 2 ц =.1, А = К +15 156дах 5. и 5.(р + 1.) в последовательности импульсов на своих -ом и(р + )-ом выходах, причем число импульсов равно числу единиц в коде насоответствующих входах 5. Указаннаяпара последовательностей поступаетна входы -го блока 3 подсчета единиц.Если этот блок 3. выполнен пофиг. 2, то при поступлении импульсалишь на один вход полусумматора 10к содержимому счетчика 9 прибавляется единица, а при поступлении импульсов на оба входа полусумматора 10 ксодержимому счетчика 9 прибавляетсячисло два.Если блок 3. выполнен по Фиг. 3,то при поступлении импульса лишь наодин вход блока он проходит черезсоответствующий элемент 12 или 13 насоответствующий вход счетчика 11,Если же в блок 3. приходит два импульса, то на счетчик 11 импульсы непроходят. Коды с выходов блоков 3.поступают в узел 4, где блок 14 определяет код суммы входных кодов.Работа продолжается таким образом до окончания преобразования входного кода преобразователем 2. Еслиузел 4 выполнен по Фиг. 4 или 5, тоэто справедливо для случая, когдачисло единиц входного кода не превышает К. Для этого требуется и/2 ртактов работы (и - число разрядоввходного кода),По окончании преобразования преобразователь 2 самоблокируется и наего выходе конца преобразования появляется единичный сигнал, который,проходя на выход 8, свидетельствуетоб окончании работы. На выходах 19блока 14 будет при этом код числаединиц входного кода. Если он равенкоду числа.К, то на выходе 7 будетединичный сигнал, если этот код неравен коду числа К - нулевой. Этоткод подается на выходы 6.Если число единиц во входномкоде больше К, то работа заканчивается до окончательного преобразованиявходного кода. 8 варианте узла 4 поФиг. 4 работа идет до появления единичного сигнала на выходе хотя бы од"ного порогового блока 15. или на выходах 20 блока 14 или на выходе блока 15.(р+1). При этом сигнал с элемента ИЛИ 16 проходит на выход 8 изапирает дешиФратор 18. В варианте уз 4733ла 4 по фиг. 5 работа будет идти допоявления сигнала на выходе блока 5,проходящего на выход 8; на выходе 7сигнал будет нулевым. То же будет и 5при выполнении узлапо Фиг. б,так как по окончании работы преобразователя 2 (сигнал на выходе 8) навыходе 7 будет нулевой сигнал.При работе устройства в режимеподсчета количества единиц по модулюК оно работает следующим образом, Висходном состоянии преобразователь 2и счетчики в блоках 3 сброшены, приэтом в реверсивные счетчики 11. записан,код числа входов 5.(р+) помодулю К. На входы 5 подан контролируемый код. При поступлении тактовыхимпульсов с генератора 1 преобразо ватель 2 преобразует параллельныйкод на входах 5. и 5.(р+) в последовательности импульсов на своих-ом и (р+1.)-ом выходах, с которыхони поступают на входы блока 325 Последний выполняется по Фиг, 3. Припоступлении импульса с -го выходапреобразователя 2 на первый входблока 3. к содержимому его счетчика11 прибавляется единица, при поступлении импульса с (р+)-го выходапреобразователя 2 на второй вход блока 3. от содержимого его счетчика11 вычитается единица. Если импульсыпоступают одновременно на оба входаблока 3., то состояние его счетчика 11 не меняется, Работа продолжается до окончания преобразованиявходного кода преобразователем 2.Коды с выходов блоков 3 суммируются 40 по модулю К в узле 4. По окончаниипреобразования входного кода преобразователь 2 самоблокируется и наего выходе конца преобразования появляется единичный сигнал, проходящий 45 на выход 8 устройства, что свидетельствует об окончании работы. На вы-ходах 6 блока 4 при этом будет код,числа единиц на входах по модулю К,Устройство может работать также ив режиме Формирования остатка входного кода по модулю К. Для этого навходы 5 и 5.(р+) подаются разрядывходного кода, имеющие одинаковыезначения остатка веса по модулю К,а 1-ый разряд кода на выходах блока 553 подсчета единиц имеет вес (2 И,)1-1вас 1 К = Игде И; - значение остат 3ка по модулю К весов разрядов входного кода, подаваемых на входы 57 1564733 и 5. (р+1). При этом 1-ый выход блока 3.соединяется с входами блока 14 с весами, равными весам единичных разрядов в двоичном представлении числа ы.Тогда по окончании преобразования входного кода преобразователем 2 на выходах блока 14 формируется код остатка по модулю К входного кода.При малом числе разрядов входного кода с одинаковыми значениями остатков весов по модулю К, входы 5, соответствующие разрядам с наибольшими значениями остатков весов, могут соединяться с входами нескольких групп так, чтобы сумма остатков весов по модулю К для этих групп была равна остатку по модулю К веса соответствующего входа, 20Таким образом, устройство позволяет осуществлять подсчет и контроль количества единиц входного кода по модулю К, а также формировать и контролировать остаток входного кода по 25 модулю К, обеспечивая повышение быстродействия так как требует,Ф 1 гртактов работы.30Формула изобретения 1. Устройство для обнаружения ошибок в параллельном коде, содержащее генератор тактовых импульсов, выход которого соедийен с тактовым входом 2 р-канального преобразователя параллельного кода в последовательность импульсов (р = 1,2), первые(2 р) -е информационные входы которого 40 являютая одноименными входами устройства, а первый - р-й выходы подключены к первым входам соответственно первого - р-го блоков подсчета единиц, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в устройство введен узел суммирования и контроля, (р+1)-й - (2 р)-й выходы 2 р-канального преобразователя параллельного кода е иоследова тельность импульсов соединены с вторыми входами соответственно первого - р-го блоков подсчета единиц, выходы которых и выход окончания работы 2 р-канального преобразователя параллельного кода в последовательность импульсов подключены соответственно к первым - р-м и (р+1)-му входам узла суммирования и контроля,первые, второй и третий выходы которого являются соответственно инФормационными выходами, контрольнымвыходом и выходом окончания работыустройства.2, Устройство ио п. 1, о т л ич а ю щ е е с я тем, что блок подсчета единиц содержит счетчик и полусумматор, первый и второй входы которого являются одноименными входамиблока, выходы суммы и переполненияполусумматора соединены со счетнымивходами соответственно первого ивторого разрядов счетчика, выходыкоторого являются выходами блока.3, Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок подсчета единиц содержит реверсивныйсчетчик и первый и второй элементыЗАПРЕТ, разрешающий вход первого изапрещающий вход второго элементовЗАПРЕТ обьединены и являются первымвходом блока, разрешающий вход второго и запрещающий вход первого элементов ЗАПРЕТ обьединены и являютсявторым входом блока, выходы первогои второго элементов ЗАПРЕТ подключены к суммирующему и вычитающемувходам реверсивного счетчика, выходыкоторого являются выходами блока,4. Устройство по и, 1, о т л ич а ю щ е е с я тем, что узел суммирования и контроля содержит первый - (р+1)-й пороговые блоки, дешифратор, первый и второй элементыИЛИ и блок суммирования первые -р-е входы которого обьединены с соответствующими входами соответственно первого - р-го пороговых блоков и являются первыми - р-ми входами узла, первые выходы блока суммирования подключены к соответствующимвходам дешифратора и (р+1) -го порогового блока и являются первымивыходами узла, вторые выходы блокасуммирования и выходы всех пороговых блоков соединены с входами первого элемента ИЛИ, выход которогоподключен к первому входу второгоэлемента ИЛИ и стробирующему входудешифратора, выход которого являетсявторым выходом узла, второй вход ивыход второго элемента ИЛИ являютсясоответственно (р+1) -м входом итретьим выходом узла,5. Устройство ио и. 1, о т л ич а ю щ е е с я тем, что узел суммирования и контроля содержит ио9 15 роговый блок, дешифратор, элемент ИЛИ и блок суммирования, первыер-е входы которого являются одноименными входами узла, выходы блока сум-мирования подключены к соответствующим входам дешифратора и порогового блока и являются первыми выходами узла, выход дешифратора является вторым выходом узла, выход порогово" го блока соединен с первым входом элемента ИЛИ, второй вход и выход которого являются соответственно (р+1)-м входом и третьим выходом узла.6. Устройство по и. 1, о т л ич а ю щ е е с я тем, что узел сум" мирования и контроля содержит дешифратор и блок суммирования, первые " р-е входы которого являются одноименными входами узла, выходы блока суммирования подключены к входам дешифратора и являются первыми выходами узла, выход дешифратора является вторым выходом узла, (р+1)-й вход узла соединен с его третьим выходом.7. Устройство по и, 4, .о т л ич а ю щ е е с я тем, что блОк суммирования содержит 1 од р групп 64733 1 Осумматоров, соединенных по пирамидальной схеме, входы сумматоров первой группы являются соответствующими 5входами блока, выходы сумматоров посюледней группы с весами У ( А, гдеА - порог первого - (р+1)-го порогового блока, являются первыми выходами блока, выходы сумматоров всехгрупп с весами И ) А являются вторыми выходами блока.8. Устройство по пп. 2-5, о т л ич а ю щ е е с я тем, что "й счетчик (д = 1,р) выполнен с предустанов 15 кой кода Ч 3, 9,ц . = Ч, А =вК + 1 + с 19 Устройство по пп, 3 и б, о тл и ч а ю щ е е с я тем, цто ревер сиенце счетчики и блок суммированиявыполнены по модулю К.1 О. Устройство по пп. 3 и 6 О тл и ч а ю щ е е с я тем, цто -йреверсивный счетчик выполнен с пред установкой кода числа (р+)-х информационных входов 2 р-канального.преобразователя параллельного кодав последовательность импульсов, выполненных инверсными.116 Тираж 660 одписн ГКНТ С роизводственно-издательский комбинат Патент", г,ужгород, ул.Гагарина РИИИПИ Государственного ком 113035, Носета по изобоетени а, Ж, Раушская и открытия б., д. 4/5

СмотретьЗаявка

4340381, 08.12.1987

ВОЙСКОВАЯ ЧАСТЬ 31303

МУЗЫЧЕНКО ОЛЕГ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/08, H03M 13/05

Метки: коде, обнаружения, ошибок, параллельном

Опубликовано: 15.05.1990

Код ссылки

<a href="https://patents.su/6-1564733-ustrojjstvo-dlya-obnaruzheniya-oshibok-v-parallelnom-kode.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибок в параллельном коде</a>

Предыдущий патент: Дешифратор

Следующий патент: Радиостанция

Случайный патент: Способ определения зоны поглощения в процессе бурения