Устройство для вычисления экспоненциальной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1465884

Авторы: Золотовский, Коробков

Текст

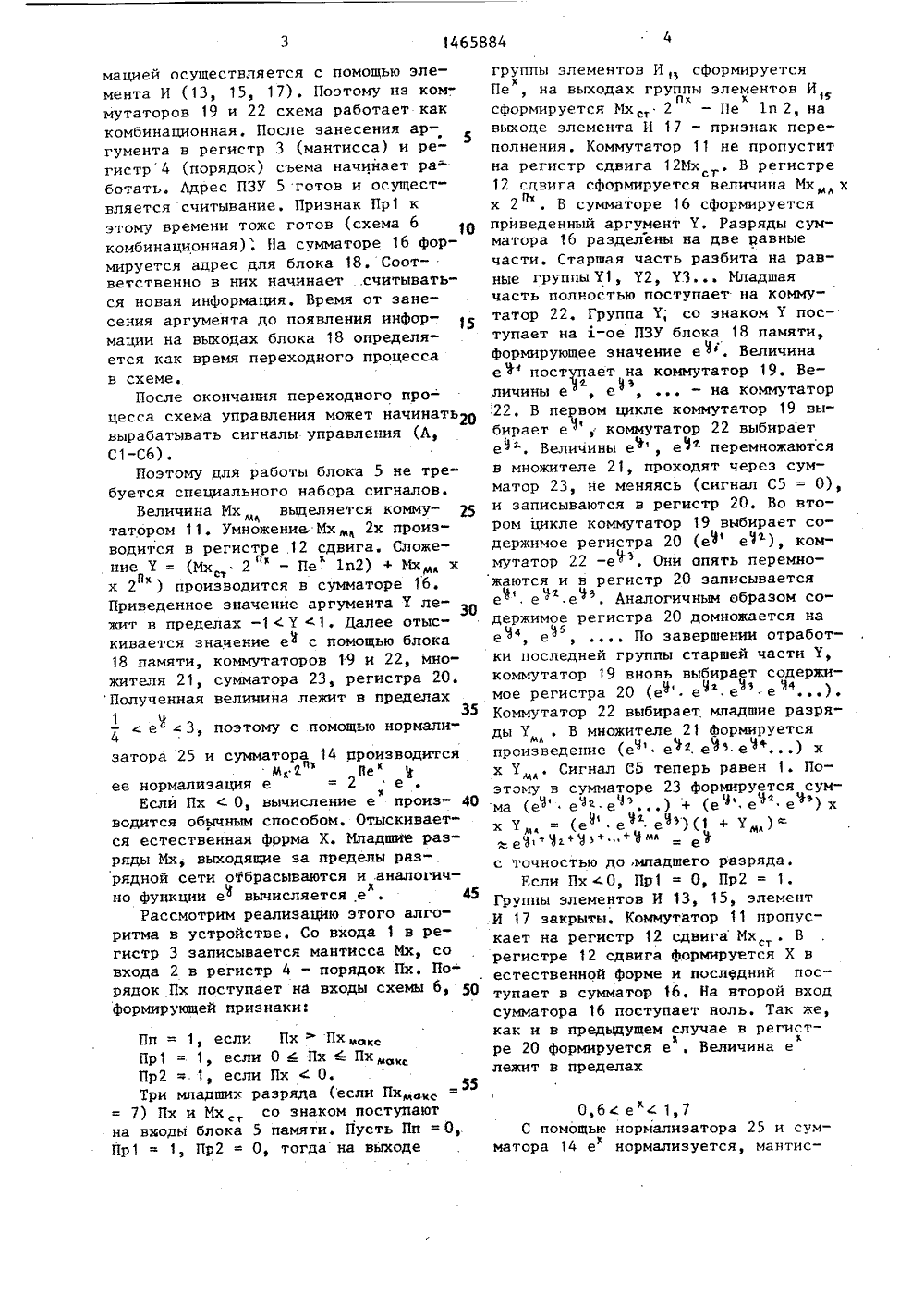

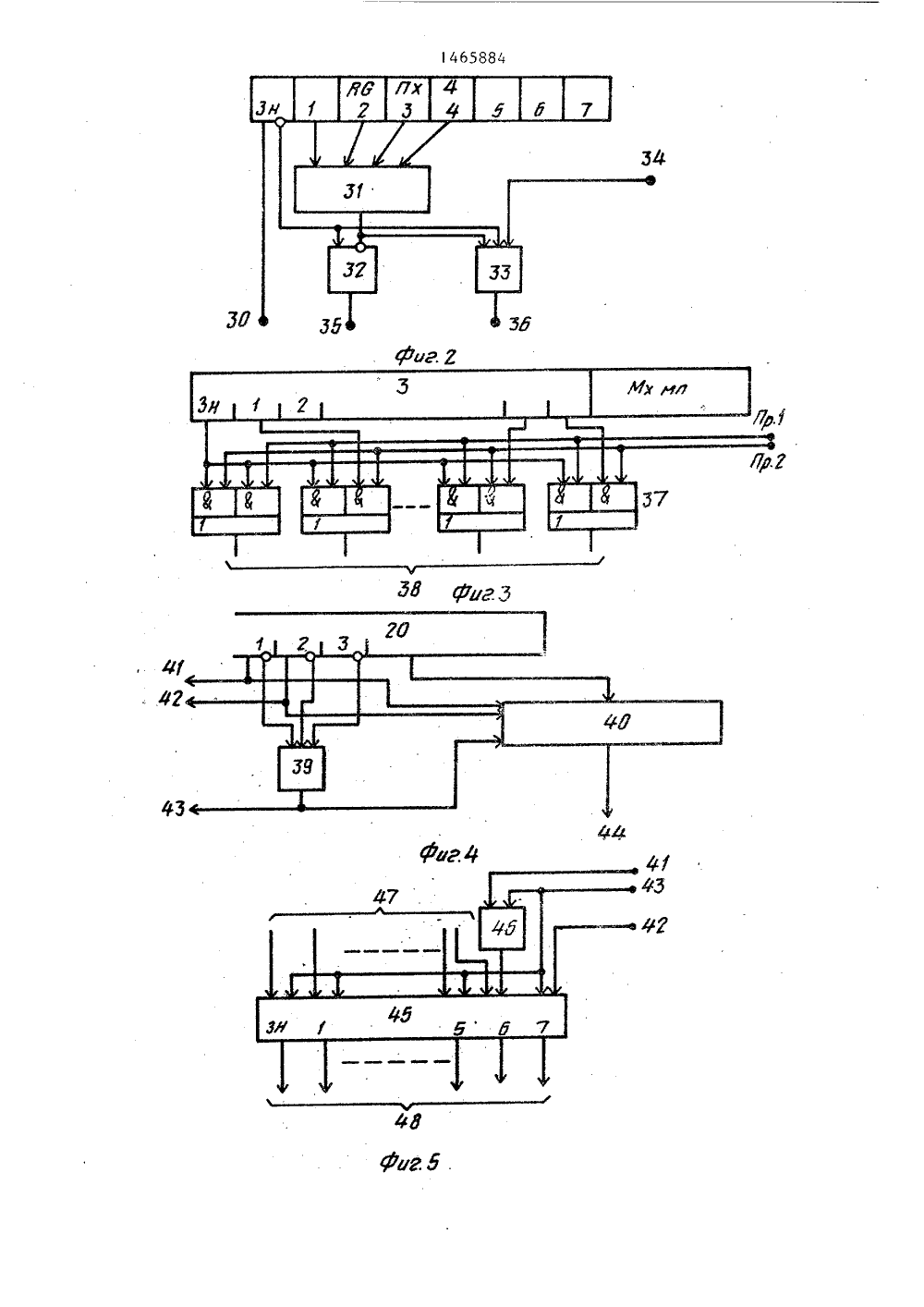

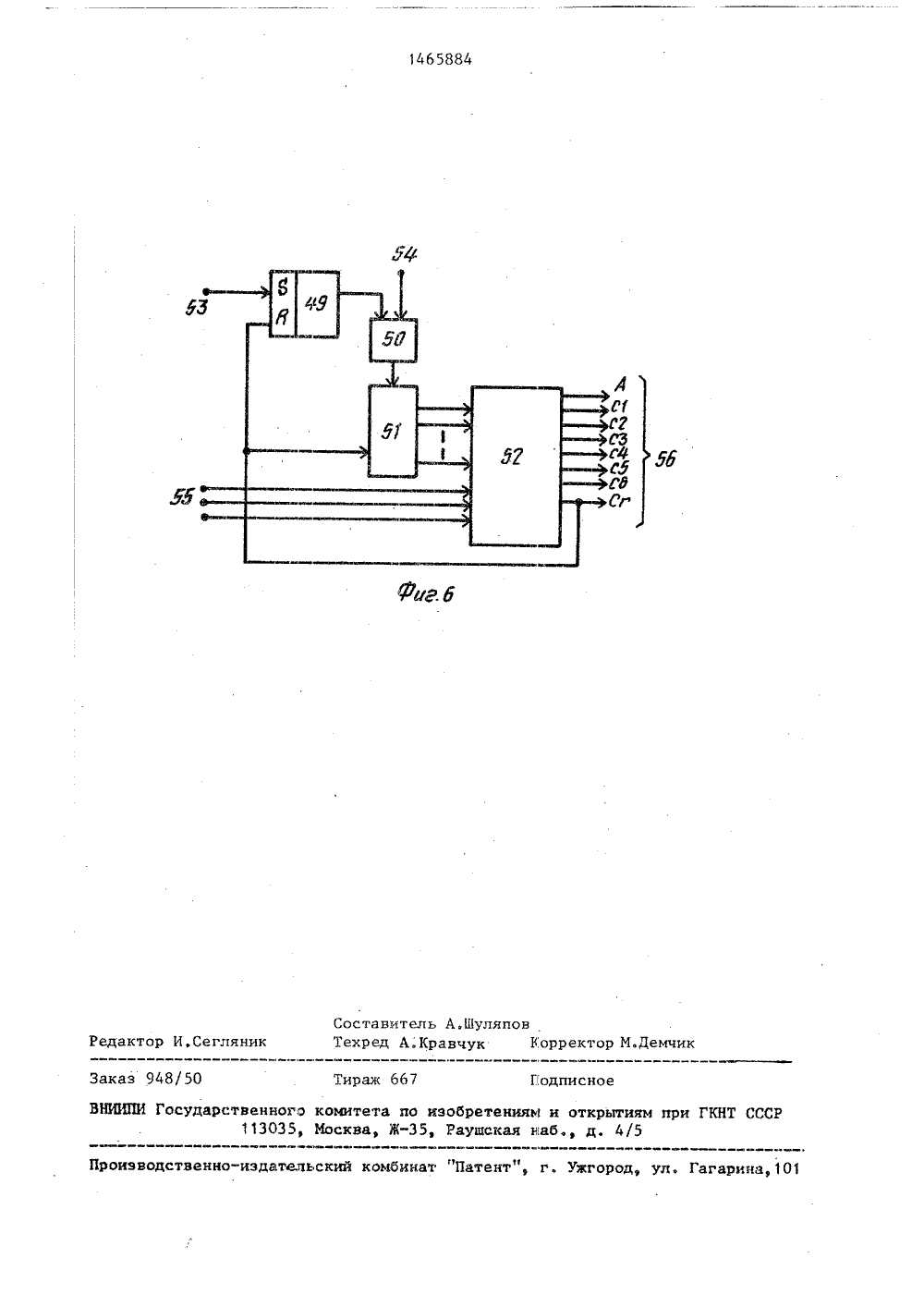

СОЮЗ СОВЕТСНИСОЦИАЛИСТИЧЕСНРЕСПУБЛИН 1 4 С 06 Г 75 ЕТЕНИЯ ески обков тво СССР 56, 1986о СССР 56, 1986. СУДАРСТВЕННЫЙ НОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТНРЫТИИ ГКНТ СССР ОПИСАНИЕ етоРСНОвэ СВИДКтельС(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЭКСПОНЕНЦИАЛЬНОЙ ФУНКЦИИ(57) Изобретение относится к вычислительной технике и может быть иск пользовано в вычислителях для вычисления функции у = е- с плавающей за+Хпятой. Цель изобретения - расширение диапазона вычисления зкспоненциальной функции. Устройство содержит вход 1 мантиссы, вход 2 порядка, первый и второй регистры 3 и 4, первый блок1465884 памяти 5, схему 6 формирования признака, элемент ИЛИ 7 блок 8 управления, выход 9 признака переполнения,выход 10 готовности данных, первыйкоммутатор 11, регистр сдвига.12,первую группу элементов И 13, сумма-,.тор 14 порядка, вторую группу элементов И 15, первый сумматор 16, элеИзобретение относится к вычислительной технике и может -быть использовано в вычислителях для вычисленияфункции у = е- с плавающей запятой.5Цель изобретения - расширение диапазона вычисления экспоненциальнойфункции.На Фиг.1 показана функциональнаясхема устройства для вычисления экспоненциальной функции, на фиг.2 -схема формирования признаков; наФиг.З - коммутатор; на Фиг.4 - нормализатор, на Фиг.5 - сумматор порядка;на Фиг.б - схема блока управления.Устройство (Фиг.1) содержит вход1 мантиссы, вход 2 порядка, первый ивторой регистры 3 и 4 первый блокпамяти 5, схему 6 Формирования признака, элемент ИЗИ 7 х блок 8 управ Оления, выход 9 признака переполнения,выход 10 готовности данных, первыйкоммутатор 11, регистр сдвига 12,первую группу элементов И 13, сумматор 14 порядка, вторую группу элемен тов И 15, первый сумматор 16, элемент И 17, второй блок памяти 18,второй коммутатор 19 третий регистрф 20, множитель 21, третий коммутатор2, второй сумматор 23, третью группу элементов И 24, нормализатор 25,пятый и четвертый регистры 26 и 27,выходы мантиссы и порядка 28 и 29.Схема 6 Формирования признака(фиг.2) содержит выход 30 порядкаменьше нуля, элемент ИЛИ 31, элементы И 32 и 33, вход 34 знака, выход35 нормального порядка, выход 36 максимального порядка,Коммутатор 11 (фиг.З) содержитэлементы ИИЛИ 37 и выход 38 комчу 40татора. мент И 17, второй блок памяти 18,второй коммутатор 19, третий регистр20, множитель 21, третий коммутатор22, второй сумматор 23, третью группу элементов И 24, нормализатор 25,пятый и четвертый регистры 26 и 27,выходы мантиссы и порядка 28 и 29.6 ил. Нормализатор 25 (фиг4) содержитэлемент И 39, сдвигатель 40, первый,второй, третий.и четвертый выходы41-44 нормализатора.Сумматор 14 .порядка (фиг.5) содержит сумматор 45, элемент ИЛИ 46,вход 47 сумматора, выход 48 сумматора,Блок 8 управления (фиг,б) содержиттриггер 49, элемент И 50, счетчик 51,блок памяти 52, вход запуска 53, тактовый вход 54, входы управления 55,выходы управления 56..хФункция е вычисляется следующимобразом.Если порядок О Пх 6 Пхимаксмантисса Мх с О, то мантисса Мх делится на две части; старшую Мхст хдлиной не менее 7 значащих разрядови младшую Мх , остальные разряды.Приближенно вычисляется порядокискомой Функции Пе из выражениях 1 РхвПе = (1 2 Мхс 2 . ормированиехПе производится в блоке 5 памяти.Вычисляется приведенное значение аргумента по алгоритму,У = Мх 2 - Пе 1 п 2 = (Мх хПхстх 2" -Пе 1 п 2) +Мхм 2В каждый отдельный момент временииз ПЗУ 5 считывается сразу три величины. По первому выходу считываетсяхпорядок функций ена втором разность у и на третьем -. признак пере-полнения. Вся эта информация появляется сразу, как только подается адрес на адресные входы. Смена информации осуществляется сменой адреса,Следовательно, управления ПЗУ нетребуется, Управление выходной информацией осуществляется с помощью элемента И (13, 15, 17). Поэтому из ком" мутаторов 19 и 22 схема работает как комбинационная, После занесения аргумента в регистр 3 (мантисса) и регистр 4 (порядок) съема начинает ра= ботать. Адрес ПЗУ 5 готов и осуществляется считывание. Признак Пр 1 к этому времени тоже готов (схема 6 комбинационная); На сумматоре 16 Формируется адрес для блока 18, Соответственно в них начинает считываться новая информация, Время от занесения аргумента до появления информации на выхоДах блока 18 определяется как время переходного процесса в схеме.После окончания переходного про- цесса схема управления может начинать 20 вырабатывать сигналы управления (А, С 1-С 6).Поэтому для работы блока 5 не требуется специального набора сигналов.Величина Мх выделяется коммумтатором 11, Умножение Мх2 х производится в регистре 12 сдвига. Сложе,ние У = (Мх 2 " - Пе 1 п 2) + Мххмд х 2 " ) производится в сумматоре 16.Приведенное значение аргумента У лежит в пределах -1 с У с 1, Далее отыскивается значение е" с помощью блока 18 памяти, коммутаторов 19 и 22, множителя 21, сумматора 23, регистра 20. Полученная велииина лежит в пределах 1 35с е с 3 поэтому с помощью нормали" 4 фзатора 25 и сумматора 14 производитсяМЙ" Ве"ее нормализация е = 2 ехЕсли Пх с О, вычисление е произ водится обычным способом. Отыскивается естественная Фррма Х. Младшие разряды Мх, выходящие эа пределы раз-.рядной сети отбрасываются и .аналогично Функции е" вычисляется е . 45лРассмотрим реализацию этого алгоритма в устройстве. Со входа 1 в регистр 3 записывается мантисса Мх, со входа 2 в регистр 4 - порядок Пх, Порядок Пх поступает на входы схемы 6, 50 формирующей признаки: Пп = 1, если ПхПхПР 1 = 1, если 0 й Пх с Пхм ,Пр 2 щ 1, если Пх с О.Три младших разряда (если Пх ,.557) Пх и Мх, со знаком поступаютна входы блока 5 памяти. Пусть Пп = О,Пр 1 = 1, Пр 2О, тогда на выходе группы элементов И ц сформируетсяхПе , на выходах группы элементов ИОх К % сформируется Мх 2 - Пе 1 п 2, на выходе элемента И 17 - признак переполненияКоммутатор 11 не пропустит на регистр сдвига 12 Мх , В регистресГ12 сдвига сформируется величина Мх хПхмл х 2 . В сумматоре 16 сформируется приведенный аргумент У, Разряды сумматора 16 разделены на две равные части. Старшая часть разбита на равные группы 71, У 2, У 3 Младшая часть полностью поступает на коммутатор 22, Группа У; со знаком 7 поступает на -ое ПЗУ блока 18 памяти, формирующее значение е "ф, Величина еф постпает на коммутатор 19. Величины е , е ,- на коммутаторй22. В певом цикле коммутатор 19 выбирает е ,: коммутатор 22 выбирает е". Величины е, е" перемножаются в множителе 21, проходят через сумматор 23, не меняясь (сигнал С 5 = 0), и записываются в регистр 20. Во втором цикле коммутатор 19 выбирает содержимое регистра 20 (е" е"), коммутатор 22 -е". Они апять перемножаются и в регистр 20 записываетсяЦ 93е , е,е . Аналогичным образом содержимое регистра 20 домножается на е ", е ,По завершении отработЧ 5ки последней группы старшей части У, коммутатор 19 вновь выбирает содержимое регистра 20 (ефе". е е "), Коммутатор 22 выбирает младшие разряды У . В множителе 21 формируется произведение (е е.е е"ф) х х У . Сигнал С 5 теперь равен 1. Поэтому в сумматоре 23 формируется сумма (ече" е" ) + (е", е е ) х х У,= (ее еф)(1 + У,),++фмюс точностью до,младшего разряда.Если Пх сО, Пр 1 = О, Пр 2 = Группы элементов И 13, 15, элемент И 17 закрыты. Коммутатор 11 пропускает на регистр 12 сдвига Мх, . В регистре 12 сдвига формируется Х в естественной Форме и последний поступает в сумматор 16. На второй вход сумматора 16 поступает воль. Так же, как и в предыдушем случае в регист%ре 20 формируется е . Величина е лежит в пределах О, 6 с. е "с. 1, 7С помощью нормалиэатора 25 и сумматора 14 е" нормализуется, мантис1465 Устройство для вычисления экспоненциальной функции, содержащее первый и второй регистры, первый и второй сумматоры, первый блок памяти, 10 регистр сдвига, коммутатор и элемент И, причем выходы младших разрядов первого регистра. соединены с первым информационным входом регистра сдвига, второй информационный вход которого соединен с выходом первого коммутатора, выход регистра сдвига соединен с входом первого слагаемого перого сумматора, о т л и ч а ю щ е ея тем, что, с целью расширения ди пазона вычисления экспоненциальной ункции, в него введены регистры с ретьего по пятый, второй блок памяи, второй и третий коммутаторы, мнотель, сумматор порядка, нормализа ор, блок управления, схема формиро:. ания признаков, .группы элементов Ипервой по третью и элемент ИЛИ, ричем вход .мантиссы устройства соеинеи с информационным входом первоо регистра, выход знакового разряда оторого соединен с входом первого оля адресного входа первого блока памяти и информационными. входами перого коммутатора, выход знакового азряда первого регистра соединен с первым входом схемы формирования при" иаков, первый выход которого соеди- нен с первым входом элемента ИЛИ, выход которого соединен с входом при 40 нака переполнения блока управлениявыходом признака переполнения устойства, вьгкод знакового разряда второго регистра соединен с вторым входом схемы формирования признака перф 45 Вым управляющим входом регистра сдви- . га, выходы младших разрядов .второго регистра соединены с входом второго Поля адресного вхОда первого блока памяти, третьим входом схемы формирования признака, с вторым управляю 50 щим входом регистра сдвига, второй Выход схемы формирования признака соединен с входом первого признака блока управления, первым управляющим55 5са Ме" записывается в регистр 26Х9порядок Пе - в регистр 27. Формула изобретения5 884 6входом первого коммутатора, управляющими входами элементов И первой и второй групп и управляющим входом элемента И, третий выход схемы формирования признаков соединен с входом второго признака блока управления и вторым управляющим входом первого коммутатора, выход порядка функции е йервого блока памяти соединен с ин- формационным входом сумматора порядка, выход которого соединен с информационным входом четвертого регистра, выход которого соединен с выходом порядка функции е устройства, выход разности первого блока памяти соединен с входом второго слагаемого первого сумматора, выходы знака и старших разрядов которого соединены с адресным входом второго блока памяти, выход старших разрядов которого соединен с первым информационным входом второго коммутатора, выход которого соединен с первым информационным входом множителя, выход которого соединен с входом первого слагаемого второго сумматора, выход которого соединен с входом третьего регистра, выход которогб соединен с входом нормализатора, входом элементов И третьей группы и вторым информационным вкодом второго коммутатора, выходы младших разрядов второго блока памяти соединены с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом знака первого сумматора, выходы младших разрядов которого соединены с третьим информационным входом третьего коммутатора, выход которого соединен с вторым информационным входом множителя, выход нормалиэатора соединен синформационным входом пятого регистра, выход которого соединен с вы" ходом мантиссы устройства, выходы с первого по восьмой блока управления соединены соответственно с управляющими входами третьего коммутатора, множителя, третьего, четвертого и пятого регистров, элементов И третьей группы, второго коммутатора и выходом готовности результата устройства, выход переполнения первого блока памяти соединен с входом элемента И, выход которого соединен с вторым входом элемента ЕЛИ.

СмотретьЗаявка

4149815, 19.11.1986

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЗОЛОТОВСКИЙ ВИКТОР ЕВДОКИМОВИЧ, КОРОБКОВ РОАЛЬД ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, функции, экспоненциальной

Опубликовано: 15.03.1989

Код ссылки

<a href="https://patents.su/6-1465884-ustrojjstvo-dlya-vychisleniya-ehksponencialnojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления экспоненциальной функции</a>

Предыдущий патент: Устройство для деления чисел

Следующий патент: Генератор псевдослучайных последовательностей

Случайный патент: Элемент настройки резонаторов12